Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 4MHz                                                                         |

| Connectivity               | UART/USART                                                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 128 x 8                                                                      |

| RAM Size                   | 224 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                    |

| Data Converters            | -                                                                            |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                               |

| Supplier Device Package    | 20-SSOP                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf628t-04i-ss |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| Name                                                 | Function | Input Type | Output Type                         | Description                                                                                                                                                                         |

|------------------------------------------------------|----------|------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0                                              | RA0      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN0      | AN         |                                     | Analog comparator input                                                                                                                                                             |

| RA1/AN1                                              | RA1      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN1      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

| RA2/AN2/VREF                                         | RA2      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN2      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | VREF     | _          | AN                                  | VREF output                                                                                                                                                                         |

| RA3/AN3/CMP1                                         | RA3      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | AN3      | AN         | —                                   | Analog comparator input                                                                                                                                                             |

|                                                      | CMP1     | _          | CMOS                                | Comparator 1 output                                                                                                                                                                 |

| RA4/T0CKI/CMP2                                       | RA4      | ST         | OD                                  | Bi-directional I/O port                                                                                                                                                             |

|                                                      | TOCKI    | ST         | —                                   | Timer0 clock input                                                                                                                                                                  |

|                                                      | CMP2     | _          | OD                                  | Comparator 2 output                                                                                                                                                                 |

| RA5/MCLR/Vpp                                         | RA5      | ST         | —                                   | Input port                                                                                                                                                                          |

|                                                      | MCLR     | ST         | _                                   | Master clear                                                                                                                                                                        |

|                                                      | VPP      | _          | _                                   | Programming voltage input. When configured<br>as MCLR, this pin is an active low RESET to<br>the device. Voltage on MCLR/VPP must not<br>exceed VDD during normal device operation. |

| RA6/OSC2/CLKOUT                                      | RA6      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC2     | XTAL       | —                                   | Oscillator crystal output. Connects to crystal<br>or resonator in Crystal Oscillator mode.                                                                                          |

|                                                      | CLKOUT   | —          | CMOS                                | In ER/INTRC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1                                                                                                   |

| RA7/OSC1/CLKIN                                       | RA7      | ST         | CMOS                                | Bi-directional I/O port                                                                                                                                                             |

|                                                      | OSC1     | XTAL       | —                                   | Oscillator crystal input                                                                                                                                                            |

|                                                      | CLKIN    | ST         |                                     | External clock source input. ER biasing pin.                                                                                                                                        |

| RB0/INT                                              | RB0      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | INT      | ST         | —                                   | External interrupt.                                                                                                                                                                 |

| RB1/RX/DT                                            | RB1      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | RX       | ST         |                                     | USART receive pin                                                                                                                                                                   |

|                                                      | DT       | ST         | CMOS                                | Synchronous data I/O.                                                                                                                                                               |

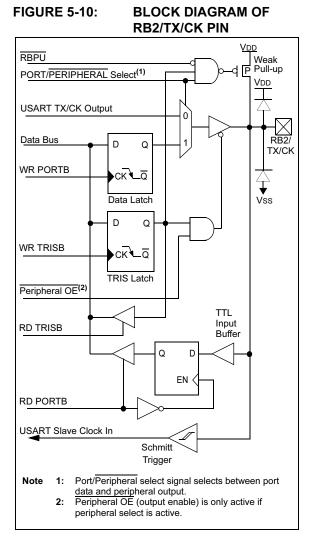

| RB2/TX/CK                                            | RB2      | TTL        | CMOS                                | Bi-directional I/O port.                                                                                                                                                            |

|                                                      | TX       | _          | CMOS                                | USART transmit pin                                                                                                                                                                  |

|                                                      | СК       | ST         | CMOS                                | Synchronous clock I/O. Can be software programmed for internal weak pull-up.                                                                                                        |

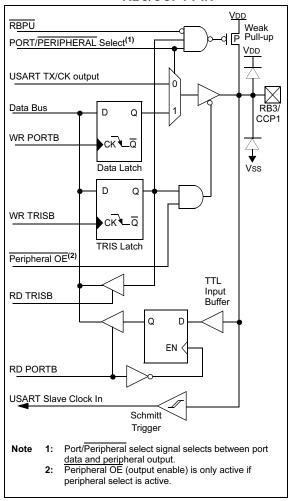

| RB3/CCP1                                             | RB3      | TTL        | CMOS                                | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                      |

|                                                      | CCP1     | ST         | CMOS                                | Capture/Compare/PWM I/O                                                                                                                                                             |

| Legend: O = Output<br>— = Not used<br>TTL = TTL Inpu |          | I = In     | MOS Output<br>put<br>pen Drain Outp | P = Power<br>ST = Schmitt Trigger Input<br>AN = Analog                                                                                                                              |

TABLE 2-1: PIC16F62X PINOUT DESCRIPTION

#### 3.2.2 SPECIAL FUNCTION REGISTERS

The SFRs are registers used by the CPU and Peripheral functions for controlling the desired operation of the device (Table 3-1). These registers are static RAM.

The special registers can be classified into two sets (core and peripheral). The SFRs associated with the "core" functions are described in this section. Those related to the operation of the peripheral features are described in the section of that peripheral feature.

| Address | Name    | Bit 7      | Bit 6                                                              | Bit 5           | Bit 4          | Bit 3         | Bit 2          | Bit 1        | Bit 0       | Value on<br>POR<br>Reset <sup>(1)</sup> | Details<br>on Page |

|---------|---------|------------|--------------------------------------------------------------------|-----------------|----------------|---------------|----------------|--------------|-------------|-----------------------------------------|--------------------|

| Bank 0  |         |            |                                                                    |                 |                |               |                |              |             |                                         |                    |

| 00h     | INDF    | Addressir  | ng this locatio                                                    | n uses conte    | nts of FSR to  | address data  | a memory (n    | ot a physica | l register) | xxxx xxxx                               | 25                 |

| 01h     | TMR0    | Timer0 M   | odule's Regis                                                      | • /             | XXXX XXXX      | 43            |                |              |             |                                         |                    |

| 02h     | PCL     | Program    | Counter's (PC                                                      | ) Least Sign    | ificant Byte   |               |                |              |             | 0000 0000                               | 13                 |

| 03h     | STATUS  | IRP        | RP1                                                                | RP0             | TO             | PD            | Z              | DC           | С           | 0001 1xxx                               | 19                 |

| 04h     | FSR     | Indirect d | ata memory a                                                       | ddress point    | er             |               |                |              | -           | xxxx xxxx                               | 25                 |

| 05h     | PORTA   | RA7        | RA6                                                                | RA5             | RA4            | RA3           | RA2            | RA1          | RA0         | xxxx 0000                               | 29                 |

| 06h     | PORTB   | RB7        | RB6                                                                | RB5             | RB4            | RB3           | RB2            | RB1          | RB0         | XXXX XXXX                               | 34                 |

| 07h     | _       | Unimplen   | mplemented                                                         |                 |                |               |                |              |             |                                         |                    |

| 08h     | _       | Unimplen   | nented                                                             |                 |                | _             |                |              |             |                                         |                    |

| 09h     | _       | Unimplen   | plemented                                                          |                 |                |               |                |              |             |                                         |                    |

| 0Ah     | PCLATH  | _          | _                                                                  | _               | Write buffer   | for upper 5 b | oits of progra | im counter   |             | 0 0000                                  | 25                 |

| 0Bh     | INTCON  | GIE        | PEIE                                                               | T0IE            | INTE           | RBIE          | T0IF           | INTF         | RBIF        | 0000 000x                               | 21                 |

| 0Ch     | PIR1    | EEIF       | CMIF                                                               | RCIF            | TXIF           | _             | CCP1IF         | TMR2IF       | TMR1IF      | 0000 -000                               | 23                 |

| 0Dh     | _       | Unimplen   | nented                                                             | —               | _              |               |                |              |             |                                         |                    |

| 0Eh     | TMR1L   | Holding r  | Holding register for the Least Significant Byte of the 16-bit TMR1 |                 |                |               |                |              |             |                                         | 46                 |

| 0Fh     | TMR1H   | Holding r  | egister for the                                                    | Most Signifi    | cant Byte of t | he 16-bit TM  | R1             |              |             | XXXX XXXX                               | 46                 |

| 10h     | T1CON   | _          | _                                                                  | T1CKPS1         | T1CKPS0        | T1OSCEN       | T1SYNC         | TMR1CS       | TMR10N      | 00 0000                                 | 46                 |

| 11h     | TMR2    | TMR2 mo    | odule's registe                                                    | r               |                |               |                |              |             | 0000 0000                               | 50                 |

| 12h     | T2CON   | _          | TOUTPS3                                                            | TOUTPS2         | TOUTPS1        | TOUTPS0       | TMR2ON         | T2CKPS1      | T2CKPS0     | -000 0000                               | 50                 |

| 13h     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | _                                       | _                  |

| 14h     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | _                                       | _                  |

| 15h     | CCPR1L  | Capture/0  | Compare/PWN                                                        | /I register (LS | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 16h     | CCPR1H  | Capture/0  | Compare/PWN                                                        | /I register (M  | SB)            |               |                |              |             | xxxx xxxx                               | 61                 |

| 17h     | CCP1CON | _          | —                                                                  | CCP1X           | CCP1Y          | CCP1M3        | CCP1M2         | CCP1M1       | CCP1M0      | 00 0000                                 | 61                 |

| 18h     | RCSTA   | SPEN       | RX9                                                                | SREN            | CREN           | ADEN          | FERR           | OERR         | RX9D        | 0000 -00x                               | 67                 |

| 19h     | TXREG   | USART T    | ransmit data                                                       | register        |                |               |                |              |             | 0000 0000                               | 74                 |

| 1Ah     | RCREG   | USART F    | Receive data r                                                     | egister         |                |               |                |              |             | 0000 0000                               | 77                 |

| 1Bh     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | —                                       | _                  |

| 1Ch     | _       | Unimplen   | nented                                                             |                 |                |               |                |              |             | —                                       | _                  |

| 1Dh     | —       | Unimplen   | nented                                                             |                 |                |               |                |              |             | —                                       | —                  |

| 1Eh     | —       | Unimplen   | nented                                                             |                 | 1              | 1             |                |              | 1           | —                                       | —                  |

| 1Fh     | CMCON   | C2OUT      | C10UT                                                              | C2INV           | C1INV          | CIS           | CM2            | CM1          | CM0         | 0000 0000                               | 53                 |

TABLE 3-1: SPECIAL REGISTERS SUMMARY BANK 0

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

| Address | Name   | Bit 7            | Bit 6                    | Bit 5       | Bit 4        | Bit 3                  | Bit 2         | Bit 1         | Bit 0        | Value on<br>POR<br>Reset <sup>(1)</sup> | Details on<br>Page |

|---------|--------|------------------|--------------------------|-------------|--------------|------------------------|---------------|---------------|--------------|-----------------------------------------|--------------------|

| Bank 2  |        |                  |                          |             |              |                        |               |               |              |                                         |                    |

| 100h    | INDF   | Addressin ister) | g this locatior          | n uses cont | ents of FSF  | to address             | s data mem    | ory (not a pl | hysical reg- | XXXX XXXX                               | 25                 |

| 101h    | TMR0   | RBPU             | INTEDG                   | TOCS        | TOSE         | PSA                    | PS2           | PS1           | PS0          | 1111 1111                               | 43                 |

| 102h    | PCL    | Program 0        | Counter's (PC            | ) Least Sig | nificant Byt | e                      |               |               |              | 0000 0000                               | 25                 |

| 103h    | STATUS | IRP              | IRP RP1 RP0 TO PD Z DC C |             |              |                        |               |               |              |                                         | 19                 |

| 104h    | FSR    | Indirect da      | ata memory a             | ddress poir |              | 0001 1xxx<br>xxxx xxxx | 25            |               |              |                                         |                    |

| 105h    | _      | Unimplem         | iented                   |             |              | _                      | _             |               |              |                                         |                    |

| 106h    | PORTB  | RB7              | RB6                      | RB5         | RB4          | RB3                    | RB2           | RB1           | RB0          | xxxx xxxx                               | 34                 |

| 107h    | _      | Unimplem         | ented                    |             | •            |                        | •             |               |              | _                                       | _                  |

| 108h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              |                                         | _                  |

| 109h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 10Ah    | PCLATH |                  | _                        | _           | Write        | buffer for u           | pper 5 bits o | of program of | counter      | 0 0000                                  | 25                 |

| 10Bh    | INTCON | GIE              | PEIE                     | T0IE        | INTE         | RBIE                   | T0IF          | INTF          | RBIF         | 0000 000x                               | 21                 |

| 10Ch    | _      | Unimplem         | Unimplemented            |             |              |                        |               |               |              |                                         | _                  |

| 10Dh    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 10Eh    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 10Fh    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 110h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 111h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 112h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 113h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 114h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 115h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

| 116h    | _      | Unimplem         | ented                    |             |              |                        |               |               |              |                                         | _                  |

| 117h    | —      | Unimplem         | ented                    |             |              |                        |               |               |              |                                         | _                  |

| 118h    | —      | Unimplem         | ented                    |             |              |                        |               |               |              |                                         | _                  |

| 119h    | —      | Unimplem         | ented                    |             |              |                        |               |               |              |                                         | _                  |

| 11Ah    | _      | Unimplem         | ented                    |             |              |                        |               |               |              |                                         | —                  |

| 11Bh    | _      | Unimplem         | ented                    |             |              |                        |               |               |              |                                         | —                  |

| 11Ch    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | —                  |

| 11Dh    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | —                  |

| 11Eh    | _      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | —                  |

| 11Fh    | —      | Unimplem         | ented                    |             |              |                        |               |               |              | _                                       | _                  |

TABLE 3-3: SPECIAL FUNCTION REGISTERS SUMMARY BANK 2

Legend: — = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented.

**Note** 1: For the Initialization Condition for Registers Tables, refer to Table 14-7 and Table 14-8 on page 98.

## PIC16F62X

| Name            | Functio<br>n | Input<br>Type | Output<br>Type | Description                                                                                                                                                                        |

|-----------------|--------------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RA0/AN0         | RA0          | ST            | CMOS           | Bi-directional I/O port                                                                                                                                                            |

|                 | AN0          | AN            | _              | Analog comparator input                                                                                                                                                            |

| RA1/AN1         | RA1          | ST            | CMOS           | Bi-directional I/O port                                                                                                                                                            |

|                 | AN1          | AN            | _              | Analog comparator input                                                                                                                                                            |

| RA2/AN2/VREF    | RA2          | ST            | CMOS           | Bi-directional I/O port                                                                                                                                                            |

|                 | AN2          | AN            | _              | Analog comparator input                                                                                                                                                            |

|                 | VREF         | _             | AN             | VREF output                                                                                                                                                                        |

| RA3/AN3/CMP1    | RA3          | ST            | CMOS           | Bi-directional I/O port                                                                                                                                                            |

|                 | AN3          | AN            | _              | Analog comparator input                                                                                                                                                            |

|                 | CMP1         | _             | CMOS           | Comparator 1 output                                                                                                                                                                |

| RA4/T0CKI/CMP2  | RA4          | ST            | OD             | Bi-directional I/O port                                                                                                                                                            |

|                 | TOCKI        | ST            | —              | External clock input for TMR0 or comparator output. Outpu<br>is open drain type                                                                                                    |

|                 | CMP2         | _             | OD             | Comparator 2 output                                                                                                                                                                |

| RA5/MCLR/Vpp    | RA5          | ST            | _              | Input port                                                                                                                                                                         |

|                 | MCLR         | ST            |                | Master clear                                                                                                                                                                       |

|                 | Vpp          | ΗV            | _              | Programming voltage input. When configured as MCLR,<br>this pin is an active low RESET to the device. Voltage on<br>MCLR/VPP must not exceed VDD during normal device<br>operation |

| RA6/OSC2/CLKOUT | RA6          | ST            | CMOS           | Bi-directional I/O port.                                                                                                                                                           |

|                 | OSC2         | XTAL          | —              | Oscillator crystal output. Connects to crystal resonator in Crystal Oscillator mode.                                                                                               |

|                 | CLKOUT       | _             | CMOS           | In ER/INTRC mode, OSC2 pin can output CLKOUT, which has 1/4 the frequency of OSC1                                                                                                  |

| RA7/OSC1/CLKIN  | RA7          | ST            | CMOS           | Bi-directional I/O port                                                                                                                                                            |

|                 | OSC1         | XTAL          | _              | Oscillator crystal input                                                                                                                                                           |

|                 | CLKIN        | ST            | _              | External clock source input. ER biasing pin.                                                                                                                                       |

TABLE 5-1: PORTA FUNCTIONS

Legend: ST = Schmitt Trigger input HV = High Voltage OD = Open Drain AN = Analog

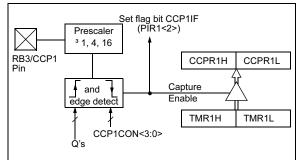

#### FIGURE 5-11: BLOCK DIAGRAM OF RB3/CCP1 PIN

| Name                                    | Function | Input Type     | Output<br>Type                 | Description                                                                                                                                                                       |

|-----------------------------------------|----------|----------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RB0/INT                                 | RB0      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                    |

|                                         | INT      | ST             | _                              | External interrupt.                                                                                                                                                               |

| RB1/RX/DT                               | RB1      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed for internal weak pull-up.                                                                                                    |

|                                         | RX       | ST             | _                              | USART Receive Pin                                                                                                                                                                 |

|                                         | DT       | ST             | CMOS                           | Synchronous data I/O                                                                                                                                                              |

| RB2/TX/CK                               | RB2      | TTL            | CMOS                           | Bi-directional I/O port                                                                                                                                                           |

|                                         | ТХ       | _              | CMOS                           | USART Transmit Pin                                                                                                                                                                |

|                                         | СК       | ST             | CMOS                           | Synchronous Clock I/O. Can be software programmed for internal weak pull-up.                                                                                                      |

| RB3/CCP1                                | RB3      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed fo internal weak pull-up.                                                                                                     |

|                                         | CCP1     | ST             | CMOS                           | Capture/Compare/PWM/I/O                                                                                                                                                           |

| RB4/PGM                                 | RB4      | TTL            | CMOS                           | Bi-directional I/O port. Can be software programmed fo internal weak pull-up.                                                                                                     |

|                                         | PGM      | ST             | _                              | Low voltage programming input pin. Interrupt-on-pin<br>change. When low voltage programming is enabled, the<br>interrupt-on-pin change and weak pull-up resistor are<br>disabled. |

| RB5                                     | RB5      | TTL            | CMOS                           | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

| RB6/T1OSO/T1CKI/<br>PGC                 | RB6      | TTL            | CMOS                           | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

|                                         | T10SO    | _              | XTAL                           | Timer1 Oscillator Output                                                                                                                                                          |

|                                         | T1CKI    | ST             | —                              | Timer1 Clock Input                                                                                                                                                                |

|                                         | PGC      | ST             | _                              | ICSP Programming Clock                                                                                                                                                            |

| RB7/T1OSI/PGD                           | RB7      | TTL            | CMOS                           | Bi-directional I/O port. Interrupt-on-pin change. Can be software programmed for internal weak pull-up.                                                                           |

|                                         | T1OSI    | XTAL           | _                              | Timer1 Oscillator Input                                                                                                                                                           |

|                                         | PGD      | ST             | CMOS                           | ICSP Data I/O                                                                                                                                                                     |

| Legend: O = Out<br>— = Not<br>TTL = TTL | used     | CM(<br>I<br>OD | OS = CMOS<br>= Input<br>= Open | S Output P = Power<br>ST = Schmitt Trigger Input<br>Drain Output AN = Analog                                                                                                      |

PORTE FUNCTIONS

SUMMARY OF REGISTERS ASSOCIATED WITH PORTB<sup>(1)</sup> TABLE 5-4:

| Address   | Name   | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR | Value on<br>All Other<br>RESETS |

|-----------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------------|---------------------------------|

| 06h, 106h | PORTB  | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | XXXX XXXX       | uuuu uuuu                       |

| 86h, 186h | TRISB  | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | 1111 1111       | 1111 1111                       |

| 81h, 181h | OPTION | RBPU   | INTEDG | TOCS   | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111       | 1111 1111                       |

Legend: u = unchanged, x = unknown **Note 1:** Shaded bits are not used by PORTB.

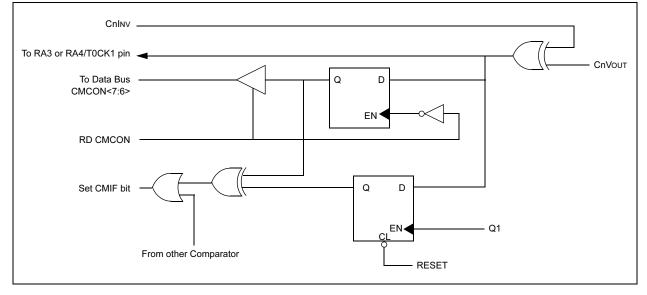

#### 9.5 Comparator Outputs

The comparator outputs are read through the CMCON register. These bits are read only. The comparator outputs may also be directly output to the RA3 and RA4 I/O pins. When the CM<2:0> = 110, multiplexors in the output path of the RA3 and RA4/T0CK1 pins will switch and the output of each pin will be the unsynchronized output of the comparator. The uncertainty of each of the comparators is related to the input offset voltage and the response time given in the specifications. Figure 9-3 shows the comparator output block diagram.

The TRISA bits will still function as an output enable/ disable for the RA3 and RA4/T0CK1 pins while in this mode.

- Note 1: When reading the PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will convert an analog input according to the Schmitt Trigger input specification.

- 2: Analog levels on any pin that is defined as a digital input may cause the input buffer to consume more current than is specified.

#### FIGURE 9-3: COMPARATOR OUTPUT BLOCK DIAGRAM

### 11.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin RB3/CCP1. An event is defined as:

- · Every falling edge

- Every rising edge

- · Every 4th rising edge

- Every 16th rising edge

An event is selected by control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). When a capture is made, the Interrupt Request Flag bit CCP1IF (PIR1<2>) is set. It must be cleared in software. If another capture occurs before the value in register CCPR1 is read, the old captured value will be lost.

#### 11.1.1 CCP PIN CONFIGURATION

In Capture mode, the RB3/CCP1 pin should be configured as an input by setting the TRISB<3> bit.

| Note: | If the RB3/CCP1 is configured as an out-     |

|-------|----------------------------------------------|

|       | put, a write to the port can cause a capture |

|       | condition.                                   |

## TABLE 11-2:CAPTURE MODE OPERATION<br/>BLOCK DIAGRAM

#### 11.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 11.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep bit CCP1IE (PIE1<2>) clear to avoid false interrupts and should clear the flag bit CCP1IF following any such change in Operating mode.

#### 11.1.4 CCP PRESCALER

There are four prescaler settings, specified by bits CCP1M3:CCP1M0. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. This means that any RESET will clear the prescaler counter.

Switching from one capture prescaler to another may generate an interrupt. Also, the prescaler counter will not be cleared, therefore the first capture may be from a non-zero prescaler. Example 11-1 shows the recommended method for switching between capture prescalers. This example also clears the prescaler counter and will not generate the "false" interrupt.

#### EXAMPLE 11-1: CHANGING BETWEEN CAPTURE PRESCALERS

| CLRF  | CCP1CON     | ;Turn CCP module off    |

|-------|-------------|-------------------------|

| MOVLW | NEW_CAPT_PS | ;Load the W reg with    |

|       |             | ; the new prescaler     |

|       |             | ; mode value and CCP ON |

| MOVWF | CCP1CON     | ;Load CCP1CON with this |

|       |             | ; value                 |

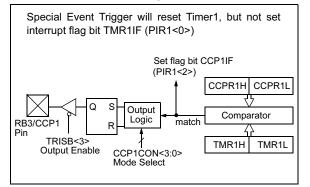

#### 11.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the RB3/CCP1 pin is:

- Driven High

- Driven Low

- · Remains Unchanged

The action on the pin is based on the value of control bits CCP1M3:CCP1M0 (CCP1CON<3:0>). At the same time, interrupt flag bit CCP1IF is set.

#### FIGURE 11-1: COMPARE MODE OPERATION BLOCK DIAGRAM

#### 11.2.1 CCP PIN CONFIGURATION

The user must configure the RB3/CCP1 pin as an output by clearing the TRISB<3> bit.

Note: Clearing the CCP1CON register will force the RB3/CCP1 compare output latch to the default low level. This is not the data latch.

### 12.0 UNIVERSAL SYNCHRONOUS/ ASYNCHRONOUS RECEIVER/ TRANSMITTER (USART) MODULE

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module is one of the two serial I/O modules. (USART is also known as a Serial Communications Interface or SCI). The USART can be configured as a full duplex asynchronous system that can communicate with peripheral devices such as CRT terminals and personal computers, or it can be configured as a half duplex synchronous system that can communicate with peripheral devices such as A/D or D/ A integrated circuits, Serial EEPROMs etc. The USART can be configured in the following modes:

- Asynchronous (full duplex)

- Synchronous Master (half duplex)

- Synchronous Slave (half duplex)

Bit SPEN (RCSTA<7>), and bits TRISB<2:1>, have to be set in order to configure pins RB2/TX/CK and RB1/ RX/DT as the Universal Synchronous Asynchronous Receiver Transmitter.

### REGISTER 12-1: TXSTA: TRANSMIT STATUS AND CONTROL REGISTER (ADDRESS: 98h)

|       | R/W-0                                             | R/W-0                                                                                                                                                                                       | R/W-0                         | R/W-0           | U-0          | <b>R</b> /W-0 | R-1            | ,<br>R/W-0 |  |  |  |  |  |

|-------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----------------|--------------|---------------|----------------|------------|--|--|--|--|--|

|       | CSRC                                              | TX9                                                                                                                                                                                         | TXEN                          | SYNC            | —            | BRGH          | TRMT           | TX9D       |  |  |  |  |  |

|       | bit 7                                             |                                                                                                                                                                                             |                               |                 |              |               |                | bit 0      |  |  |  |  |  |

| bit 7 | CSRC: Cloc                                        | k Source Sel                                                                                                                                                                                | ect bit                       |                 |              |               |                |            |  |  |  |  |  |

|       | Asynchronou<br>Don't car                          |                                                                                                                                                                                             |                               |                 |              |               |                |            |  |  |  |  |  |

|       |                                                   | er mode (Clo                                                                                                                                                                                | ck generated<br>k from extern | internally from | m BRG)       |               |                |            |  |  |  |  |  |

| bit 6 | 1 = Selects 9                                     | <ul> <li><b>X9</b>: 9-bit Transmit Enable bit</li> <li>= Selects 9-bit transmission</li> <li>= Selects 8-bit transmission</li> <li><b>XEN</b>: Transmit Enable bit<sup>(1)</sup></li> </ul> |                               |                 |              |               |                |            |  |  |  |  |  |

| bit 5 | 1 = Transmit                                      | <b>TXEN</b> : Transmit Enable bit <sup>(1)</sup><br>1 = Transmit enabled<br>0 = Transmit disabled                                                                                           |                               |                 |              |               |                |            |  |  |  |  |  |

| bit 4 | SYNC: USA<br>1 = Synchro<br>0 = Asynchro          |                                                                                                                                                                                             | ect bit                       |                 |              |               |                |            |  |  |  |  |  |

| bit 3 | Unimpleme                                         | nted: Read a                                                                                                                                                                                | is '0'                        |                 |              |               |                |            |  |  |  |  |  |

| bit 2 | BRGH: High                                        | Baud Rate S                                                                                                                                                                                 | Select bit                    |                 |              |               |                |            |  |  |  |  |  |

|       | Asynchronou<br>1 = High s<br>0 = Low s            | speed                                                                                                                                                                                       |                               |                 |              |               |                |            |  |  |  |  |  |

|       | <u>Synchronou</u>                                 | Synchronous mode<br>Unused in this mode                                                                                                                                                     |                               |                 |              |               |                |            |  |  |  |  |  |

| bit 1 | <b>TRMT</b> : Trans<br>1 = TSR em<br>0 = TSR full |                                                                                                                                                                                             | gister STATU                  | S bit           |              |               |                |            |  |  |  |  |  |

| bit 0 | <b>TX9D</b> : 9th bi                              | t of transmit                                                                                                                                                                               | data. Can be                  | PARITY bit.     |              |               |                |            |  |  |  |  |  |

|       | Note 1: S                                         | REN/CREN                                                                                                                                                                                    | overrides TX                  | EN in SYNC      | node.        |               |                |            |  |  |  |  |  |

|       | Legend:                                           |                                                                                                                                                                                             |                               |                 |              |               |                |            |  |  |  |  |  |

|       | R = Reada                                         | ble bit                                                                                                                                                                                     | VV = V                        | Vritable bit    | U = Unimp    | lemented b    | oit, read as ' | )'         |  |  |  |  |  |

|       | -n = Value                                        | at POR                                                                                                                                                                                      | '1' = E                       | Bit is set      | '0' = Bit is | cleared       | x = Bit is ur  | nknown     |  |  |  |  |  |

| BAUD     | Fosc = 20 MHz |        | SPBRG              | 16 MHz  |        | SPBRG              | 10 MHz |        | SPBRG              |

|----------|---------------|--------|--------------------|---------|--------|--------------------|--------|--------|--------------------|

| RATE (K) | KBAUD         | ERROR  | value<br>(decimal) | KBAUD   | ERROR  | value<br>(decimal) | KBAUD  | ERROR  | value<br>(decimal) |

| 9600     | 9.615         | +0.16% | 129                | 9.615   | +0.16% | 103                | 9.615  | +0.16% | 64                 |

| 19200    | 19.230        | +0.16% | 64                 | 19.230  | +0.16% | 51                 | 18.939 | -1.36% | 32                 |

| 38400    | 37.878        | -1.36% | 32                 | 38.461  | +0.16% | 25                 | 39.062 | +1.7%  | 15                 |

| 57600    | 56.818        | -1.36% | 21                 | 58.823  | +2.12% | 16                 | 56.818 | -1.36% | 10                 |

| 115200   | 113.636       | -1.36% | 10                 | 111.111 | -3.55% | 8                  | 125    | +8.51% | 4                  |

| 250000   | 250           | 0      | 4                  | 250     | 0      | 3                  | NA     | _      | _                  |

| 625000   | 625           | 0      | 1                  | NA      | _      | _                  | 625    | 0      | 0                  |

| 1250000  | 1250          | 0      | 0                  | NA      | _      | _                  | NA     | _      | _                  |

#### TABLE 12-5: BAUD RATES FOR ASYNCHRONOUS MODE (BRGH = 1)

| BAUD     | Fosc = 7.16 | Fosc = 7.16 MHz |                    | 5.068 MHz |         | SPBRG              | 4 MHz    |         | SPBRG              |

|----------|-------------|-----------------|--------------------|-----------|---------|--------------------|----------|---------|--------------------|

| RATE (K) | KBAUD       | ERROR           | value<br>(decimal) | KBAUD     | ERROR   | value<br>(decimal) | KBAUD    | ERROR   | value<br>(decimal) |

| 9600     | 9.520       | -0.83%          | 46                 | 9598.485  | 0.016%  | 32                 | 9615.385 | 0.160%  | 25                 |

| 19200    | 19.454      | +1.32%          | 22                 | 18632.35  | -2.956% | 16                 | 19230.77 | 0.160%  | 12                 |

| 38400    | 37.286      | -2.90%          | 11                 | 39593.75  | 3.109%  | 7                  | 35714.29 | -6.994% | 6                  |

| 57600    | 55.930      | -2.90%          | 7                  | 52791.67  | -8.348% | 5                  | 62500    | 8.507%  | 3                  |

| 115200   | 111.860     | -2.90%          | 3                  | 105583.3  | -8.348% | 2                  | 125000   | 8.507%  | 1                  |

| 250000   | NA          | _               | _                  | 316750    | 26.700% | 0                  | 250000   | 0.000%  | 0                  |

| 625000   | NA          | _               | _                  | NA        | _       | _                  | NA       | _       | _                  |

| 1250000  | NA          |                 | —                  | NA        | —       | _                  | NA       | —       |                    |

| BAUD        | Fosc = 3.579 | 9 MHz    | SPBRG              | 1 MHz   |          | SPBRG              | 32.768 MHz |       | SPBRG              |

|-------------|--------------|----------|--------------------|---------|----------|--------------------|------------|-------|--------------------|

| RATE<br>(K) | KBAUD        | ERROR    | value<br>(decimal) | KBAUD   | ERROR    | value<br>(decimal) | KBAUD      | ERROR | value<br>(decimal) |

| 9600        | 9725.543     | 1.308%   | 22                 | 8.928   | -6.994%  | 6                  | NA         | NA    | NA                 |

| 19200       | 18640.63     | -2.913%  | 11                 | 20833.3 | 8.507%   | 2                  | NA         | NA    | NA                 |

| 38400       | 37281.25     | -2.913%  | 5                  | 31250   | -18.620% | 1                  | NA         | NA    | NA                 |

| 57600       | 55921.88     | -2.913%  | 3                  | 62500   | +8.507   | 0                  | NA         | NA    | NA                 |

| 115200      | 111243.8     | -2.913%  | 1                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 250000      | 223687.5     | -10.525% | 0                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 625000      | NA           | _        | _                  | NA      | _        | _                  | NA         | NA    | NA                 |

| 1250000     | NA           | —        | —                  | NA      | —        | —                  | NA         | NA    | NA                 |

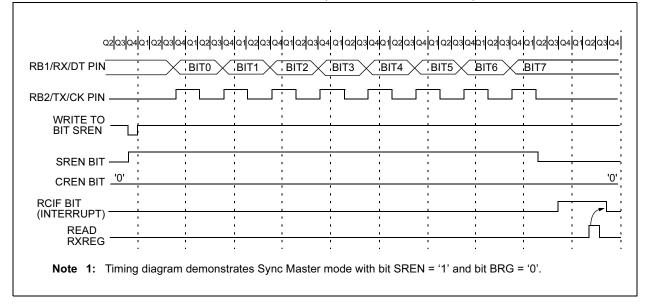

#### FIGURE 12-14: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

### 12.5 USART Synchronous Slave Mode

Synchronous Slave mode differs from the Master mode in the fact that the shift clock is supplied externally at the RB2/TX/CK pin (instead of being supplied internally in Master mode). This allows the device to transfer or receive data while in SLEEP mode. Slave mode is entered by clearing bit CSRC (TXSTA<7>).

#### 12.5.1 USART SYNCHRONOUS SLAVE TRANSMIT

The operation of the Synchronous Master and Slave modes are identical except in the case of the SLEEP mode.

If two words are written to the TXREG and then the SLEEP instruction is executed, the following will occur:

- a) The first word will immediately transfer to the TSR register and transmit.

- b) The second word will remain in TXREG register.

- c) Flag bit TXIF will not be set.

- d) When the first word has been shifted out of TSR, the TXREG register will transfer the second word to the TSR and flag bit TXIF will now be set.

- e) If enable bit TXIE is set, the interrupt will wake the chip from SLEEP and if the global interrupt is enabled, the program will branch to the interrupt vector (0004h).

Steps to follow when setting up a Synchronous Slave Transmission:

- 1. Enable the synchronous slave serial port by setting bits SYNC and SPEN and clearing bit CSRC.

- 2. Clear bits CREN and SREN.

- 3. If interrupts are desired, then set enable bit TXIE.

- 4. If 9-bit transmission is desired, then set bit TX9.

- 5. Enable the transmission by setting enable bit TXEN.

- 6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

- 7. Start transmission by loading data to the TXREG register.

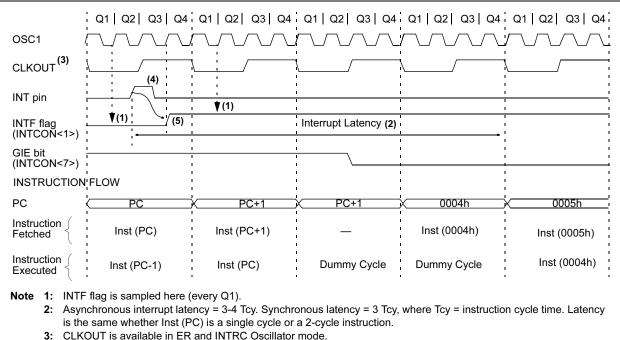

#### 14.6.1 **RB0/INT INTERRUPT**

External interrupt on RB0/INT pin is edge triggered: either rising if INTEDG bit (OPTION<6>) is set, or falling, if INTEDG bit is clear. When a valid edge appears on the RB0/INT pin, the INTF bit (INTCON<1>) is set. This interrupt can be disabled by clearing the INTE control bit (INTCON<4>). The INTF bit must be cleared in software in the interrupt service routine before re-enabling this interrupt. The RB0/INT interrupt can wake-up the processor from SLEEP, if the INTE bit was set prior to going into SLEEP. The status of the GIE bit decides whether or not the processor branches to the interrupt vector following wake-up. See Section 14.9 for details on SLEEP, and Figure 14-17 for timing of wake-up from SLEEP through RB0/INT interrupt.

#### 14.6.2 TMR0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF (INTCON<2>) bit. The interrupt can enabled/disabled by setting/clearing T0IE he (INTCON<5>) bit. For operation of the Timer0 module, see Section 6.0.

#### 14.6.3 PORTB INTERRUPT

An input change on PORTB <7:4> sets the RBIF (INTCON<0>) bit. The interrupt can be enabled/ disabled by setting/clearing the RBIE (INTCON<4>) bit. For operation of PORTB (Section 5.2).

| Note: | If a change on the I/O pin should occur       |

|-------|-----------------------------------------------|

|       | when the read operation is being executed     |

|       | (start of the Q2 cycle), then the RBIF inter- |

|       | rupt flag may not get set.                    |

#### 14.6.4 COMPARATOR INTERRUPT

See Section 9.6 for complete description of comparator interrupts.

#### **FIGURE 14-15:** INT PIN INTERRUPT TIMING

4: For minimum width of INT pulse, refer to AC specs.

- 5: INTF is enabled to be set anytime during the Q4-Q1 cycles.

## PIC16F62X

| MOVWF            | Move W to f                                                                                           |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] MOVWF f                                                                                       |  |  |  |  |

| Operands:        | $0 \leq f \leq 127$                                                                                   |  |  |  |  |

| Operation:       | $(W) \rightarrow (f)$                                                                                 |  |  |  |  |

| Status Affected: | None                                                                                                  |  |  |  |  |

| Encoding:        | 00 0000 1fff ffff                                                                                     |  |  |  |  |

| Description:     | Move data from W register to register 'f'.                                                            |  |  |  |  |

| Words:           | 1                                                                                                     |  |  |  |  |

| Cycles:          | 1                                                                                                     |  |  |  |  |

| Example          | MOVWF REG1                                                                                            |  |  |  |  |

|                  | Before Instruction<br>REG1 = $0xFF$<br>W = $0x4F$<br>After Instruction<br>REG1 = $0x4F$<br>W = $0x4F$ |  |  |  |  |

| OPTION           | Load Option Register                                                                                                                                                                                                                                                                                  |       |      |      |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|------|--|

| Syntax:          | [ label ]                                                                                                                                                                                                                                                                                             | OPTIO | N    |      |  |

| Operands:        | None                                                                                                                                                                                                                                                                                                  |       |      |      |  |

| Operation:       | $(W) \rightarrow C$                                                                                                                                                                                                                                                                                   | PTION |      |      |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                  |       |      |      |  |

| Encoding:        | 00                                                                                                                                                                                                                                                                                                    | 0000  | 0110 | 0010 |  |

| Description:     | The contents of the W register are<br>loaded in the OPTION register.<br>This instruction is supported for<br>code compatibility with PIC16C5X<br>products. Since OPTION is a<br>readable/writable register, the<br>user can directly address it. Using<br>only register instruction such as<br>MOVWF. |       |      |      |  |

| Words:           | 1                                                                                                                                                                                                                                                                                                     |       |      |      |  |

| Cycles:          | 1                                                                                                                                                                                                                                                                                                     |       |      |      |  |

| Example          |                                                                                                                                                                                                                                                                                                       |       |      |      |  |

|                  | To maintain upward compatibil-<br>ity with future PICmicro <sup>®</sup> prod-<br>ucts, do not use this<br>instruction.                                                                                                                                                                                |       |      |      |  |

| NOP              | No Operation  |      |      |      |  |  |  |

|------------------|---------------|------|------|------|--|--|--|

| Syntax:          | [ label ]     | NOP  |      |      |  |  |  |

| Operands:        | None          | None |      |      |  |  |  |

| Operation:       | No operation  |      |      |      |  |  |  |

| Status Affected: | None          |      |      |      |  |  |  |

| Encoding:        | 00            | 0000 | 0xx0 | 0000 |  |  |  |

| Description:     | No operation. |      |      |      |  |  |  |

| Words:           | 1             |      |      |      |  |  |  |

| Cycles:          | 1             |      |      |      |  |  |  |

| Example          | NOP           |      |      |      |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                 |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                        |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                                  |  |  |  |  |  |

| Operation:       | TOS $\rightarrow$ PC,<br>1 $\rightarrow$ GIE                                                                                                                                                                          |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                  |  |  |  |  |  |

| Encoding:        | 00 0000 0000 1001                                                                                                                                                                                                     |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top of Stack (TOS)<br>is loaded in the PC. Interrupts<br>are enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-<br>cycle instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                     |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                                     |  |  |  |  |  |

| Example          | RETFIE                                                                                                                                                                                                                |  |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                                |  |  |  |  |  |

| SUBWF               | Subtract W from f                                                                                                                                                                     |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:             | [ <i>label</i> ] SUBWF f,d                                                                                                                                                            |

| Operands:           | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                    |

| Operation:          | (f) - (W) $\rightarrow$ (dest)                                                                                                                                                        |

| Status<br>Affected: | C, DC, Z                                                                                                                                                                              |