#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 47                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 10x10b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 64-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 64-QFN (9x9)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam3n1bb-mur |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

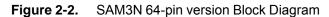

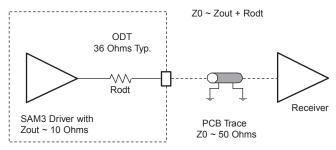

# 1. SAM3N Description

Atmel's SAM3N series is a member of a family of Flash microcontrollers based on the high performance 32-bit ARM Cortex-M3 RISC processor. It operates at a maximum speed of 48 MHz and features up to 256 Kbytes of Flash and up to 24 Kbytes of SRAM. The peripheral set includes 2x USARTs, 2x UARTs, 2x TWIs, 3x SPI, as well as 1 PWM timer, 6x general purpose 16-bit timers, an RTC, a 10-bit ADC and a 10-bit DAC.

The SAM3N series is ready for capacitive touch thanks to the QTouch library, offering an easy way to implement buttons, wheels and sliders.

The SAM3N device is an entry-level general purpose microcontroller. That makes the SAM3N the ideal starting point to move from 8- /16-bit to 32-bit microcontrollers.

It operates from 1.62V to 3.6V and is available in 48-pin, 64-pin and 100-pin QFP, 48-pin and 64-pin QFN, and 100-pin BGA packages.

The SAM3N series is the ideal migration path from the SAM3S for applications that require a reduced BOM cost. The SAM3N series is pin-to-pin compatible with the SAM3S series. Its aggressive price point and high level of integration pushes its scope of use far into cost-sensitive, high-volume applications.

# 1.1 Configuration Summary

The SAM3N4/2/1/0/00 differ in memory size, package and features list. Table 1-1 summarizes the configurations of the 9 devices.

Table 1-1.Configuration Summary

| Device   | Flash      | SRAM      | Package           | Number<br>of PIOs | ADC         | Timer             | PDC<br>Channels | USART | DAC |

|----------|------------|-----------|-------------------|-------------------|-------------|-------------------|-----------------|-------|-----|

| SAM3N4A  | 256 Kbytes | 24 Kbytes | LQFP48<br>QFN48   | 34                | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N4B  | 256 Kbytes | 24 Kbytes | LQFP64<br>QFN64   | 47                | 10 channels | 6 <sup>(2)</sup>  | 10              | 2     | 1   |

| SAM3N4C  | 256 Kbytes | 24 Kbytes | LQFP100<br>BGA100 | 79                | 16 channels | 6                 | 10              | 2     | 1   |

| SAM3N2A  | 128 Kbytes | 16 Kbytes | LQFP48<br>QFN48   | 34                | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N2B  | 128 Kbytes | 16 Kbytes | LQFP64<br>QFN64   | 47                | 10 channels | 6( <sup>(2)</sup> | 10              | 2     | 1   |

| SAM3N2C  | 128 Kbytes | 16 Kbytes | LQFP100<br>BGA100 | 79                | 16 channels | 6                 | 10              | 2     | 1   |

| SAM3N1A  | 64 Kbytes  | 8 Kbytes  | LQFP48<br>QFN48   | 34                | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N1B  | 64 Kbytes  | 8 Kbytes  | LQFP64<br>QFN64   | 47                | 10 channels | 6 <sup>(2)</sup>  | 10              | 2     | 1   |

| SAM3N1C  | 64 Kbytes  | 8 Kbytes  | LQFP100<br>BGA100 | 79                | 16 channels | 6                 | 10              | 2     | 1   |

| SAM3N0A  | 32 Kbytes  | 8 Kbytes  | LQFP48<br>QFN48   | 34                | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N0B  | 32 Kbytes  | 8 Kbytes  | LQFP64<br>QFN64   | 47                | 10 channels | 6 <sup>(2)</sup>  | 10              | 2     | 1   |

| SAM3N0C  | 32 Kbytes  | 8 Kbytes  | LQFP100<br>BGA100 | 79                | 16 channels | 6                 | 10              | 2     | 1   |

| SAM3N00A | 16 Kbytes  | 4 KBytes  | LQFP48<br>QFN48   | 34                | 8 channels  | 6 <sup>(1)</sup>  | 8               | 1     | _   |

| SAM3N00B | 16 Kbytes  | 4 KBytes  | LQFP64<br>QFN64   | 47                | 10 channels | 6 <sup>(2)</sup>  | 10              | 2     | 1   |

Notes: 1. Only two TC channels are accessible through the PIO.

2. Only three TC channels are accessible through the PIO.

# SAM3N Summary

# Table 3-1. Signal Description List (Continued)

| Signal Name              | Function                     | Туре                 | Active<br>Level | Voltage<br>Reference | Comments |

|--------------------------|------------------------------|----------------------|-----------------|----------------------|----------|

|                          | Serial Perip                 | heral Interface - SF | 2               |                      |          |

| MISO                     | Master In Slave Out          | I/O                  |                 |                      |          |

| MOSI                     | Master Out Slave In          | I/O                  |                 |                      |          |

| SPCK                     | SPI Serial Clock             | I/O                  |                 |                      |          |

| SPI_NPCS0                | SPI Peripheral Chip Select 0 | I/O                  | Low             |                      |          |

| SPI_NPCS1 -<br>SPI_NPCS3 | SPI Peripheral Chip Select   | Output               | Low             |                      |          |

|                          | Two-Wire                     | e Interface- TWIx    |                 |                      | 1        |

| TWDx                     | TWIx Two-wire Serial Data    | I/O                  |                 |                      |          |

| TWCKx                    | TWIx Two-wire Serial Clock   | I/O                  |                 |                      |          |

|                          |                              | Analog               |                 |                      |          |

| ADVREF                   | ADC and DAC Reference        | Analog               |                 |                      |          |

|                          | 10-bit Analog-to             | -Digital Converter   | ADC             |                      |          |

| AD0 - AD15               | Analog Inputs                | Analog               |                 |                      |          |

| ADTRG                    | ADC Trigger                  | Input                |                 | VDDIO                |          |

|                          | Digital-to-Analog C          | converter Controlle  | r- DACC         |                      |          |

| DAC0                     | DACC channel analog output   | Analog               |                 |                      |          |

| DATRG                    | DACC Trigger                 | Input                |                 | VDDIO                |          |

|                          | Fast Flash Pr                | ogramming Interfa    | се              |                      |          |

| PGMEN0-PGMEN2            | Programming Enabling         | Input                |                 |                      |          |

| PGMM0-PGMM3              | Programming Mode             | Input                |                 |                      |          |

| PGMD0-PGMD15             | Programming Data             | I/O                  |                 |                      |          |

| PGMRDY                   | Programming Ready            | Output               | High            | - VDDIO              |          |

| PGMNVALID                | Data Direction               | Output               | Low             |                      |          |

| PGMNOE                   | Programming Read             | Input                | Low             |                      |          |

| PGMCK                    | Programming Clock            | Input                |                 |                      |          |

| PGMNCMD                  | Programming Command          | Input                | Low             |                      |          |

Notes: 1. Schmitt Triggers can be disabled through PIO registers.

2. Some PIO lines are shared with System IOs.

3. See Section 5.3 "Typical Powering Schematics" for restriction on voltage range of Analog Cells.

## 4.1.4 100-ball TFBGA Pinout

| A1  | PB1     | C6  | PB7     | F1  | PA18    | H6  | PC4     |

|-----|---------|-----|---------|-----|---------|-----|---------|

| A2  | PC29    | C7  | PC16    | F2  | PC26    | H7  | PA11    |

| A3  | VDDIO   | C8  | PA1     | F3  | VDDOUT  | H8  | PC1     |

| A4  | PB9     | C9  | PC17    | F4  | GND     | H9  | PA6     |

| A5  | PB8     | C10 | PA0     | F5  | VDDIO   | H10 | PB4     |

| A6  | PB13    | D1  | PB3     | F6  | PA27    | J1  | PC15    |

| A7  | PB11    | D2  | PB0     | F7  | PC8     | J2  | PC0     |

| A8  | PB10    | D3  | PC24    | F8  | PA28    | J3  | PA16    |

| A9  | PB6     | D4  | PC22    | F9  | TST     | J4  | PC6     |

| A10 | JTAGSEL | D5  | GND     | F10 | PC9     | J5  | PA24    |

| B1  | PC30    | D6  | GND     | G1  | PA21    | J6  | PA25    |

| B2  | ADVREF  | D7  | VDDCORE | G2  | PC27    | J7  | PA10    |

| B3  | GNDANA  | D8  | PA2     | G3  | PA15    | J8  | GND     |

| B4  | PB14    | D9  | PC11    | G4  | VDDCORE | J9  | VDDCORE |

| B5  | PC21    | D10 | PC14    | G5  | VDDCORE | J10 | VDDIO   |

| B6  | PC20    | E1  | PA17    | G6  | PA26    | K1  | PA22    |

| B7  | PA31    | E2  | PC31    | G7  | PA12    | K2  | PC13    |

| B8  | PC19    | E3  | VDDIN   | G8  | PC28    | K3  | PC12    |

| B9  | PC18    | E4  | GND     | G9  | PA4     | K4  | PA20    |

| B10 | PB5     | E5  | GND     | G10 | PA5     | K5  | PC5     |

| C1  | PB2     | E6  | NRST    | H1  | PA19    | K6  | PC3     |

| C2  | VDDPLL  | E7  | PA29    | H2  | PA23    | K7  | PC2     |

| C3  | PC25    | E8  | PA30    | H3  | PC7     | K8  | PA9     |

| C4  | PC23    | E9  | PC10    | H4  | PA14    | К9  | PA8     |

| C5  | PB12    | E10 | PA3     | H5  | PA13    | K10 | PA7     |

# Table 4-2. 100-ball TFBGA SAM3N4/2/1/0/00C Pinout

# 4.2 SAM3N4/2/1/0/00B Package and Pinout

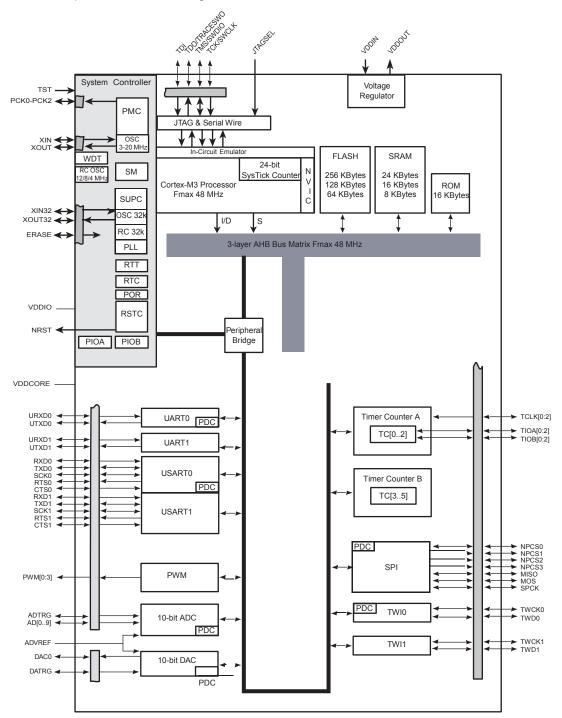

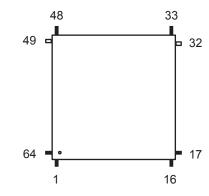

Figure 4-3. Orientation of the 64-pad QFN Package

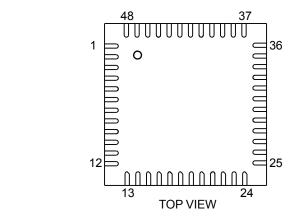

Figure 4-4. Orientation of the 64-lead LQFP Package

### 4.2.1 64-Lead LQFP and QFN Pinout

64-pin version SAM3N devices are pin-to-pin compatible with SAM3S products. Furthermore, SAM3N products have new functionalities shown in italic in Table 4-3.

|  | Table 4-3. | 64-pin SAM3N4/2/1/0/00B Pinout |

|--|------------|--------------------------------|

|--|------------|--------------------------------|

| 1  | ADVREF          |   | 17 | GND                            | 33 | TDI/PB4     | 49 | TDO/TRACESWO/PB5 |

|----|-----------------|---|----|--------------------------------|----|-------------|----|------------------|

| 2  | GND             |   | 18 | VDDIO                          | 34 | PA6/PGMNOE  | 50 | JTAGSEL          |

| 3  | PB0/AD4         |   | 19 | PA16/PGMD4                     | 35 | PA5/PGMRDY  | 51 | TMS/SWDIO/PB6    |

| 4  | PB1AD5          |   | 20 | PA15/PGMD3                     | 36 | PA4/PGMNCMD | 52 | PA31             |

| 5  | PB2/AD6         | ĺ | 21 | PA14/PGMD2                     | 37 | PA27/PGMD15 | 53 | TCK/SWCLK/PB7    |

| 6  | PB3/AD7         |   | 22 | PA13/PGMD1                     | 38 | PA28        | 54 | VDDCORE          |

| 7  | VDDIN           | ĺ | 23 | PA24/PGMD12                    | 39 | NRST        | 55 | ERASE/PB12       |

| 8  | VDDOUT          | ĺ | 24 | VDDCORE                        | 40 | TST         | 56 | PB10             |

| 9  | PA17/PGMD5/AD0  |   | 25 | PA25/PGMD13                    | 41 | PA29        | 57 | PB11             |

| 10 | PA18/PGMD6/AD1  | ĺ | 26 | PA26/PGMD14                    | 42 | PA30        | 58 | VDDIO            |

| 11 | PA21/PGMD9/AD8  |   | 27 | PA12/PGMD0                     | 43 | PA3         | 59 | PB13/DAC0        |

| 12 | VDDCORE         | ĺ | 28 | PA11/PGMM3                     | 44 | PA2/PGMEN2  | 60 | GND              |

| 13 | PA19/PGMD7/AD2  | ĺ | 29 | PA10/PGMM2                     | 45 | VDDIO       | 61 | XOUT/PB8         |

| 14 | PA22/PGMD10/AD9 |   | 30 | PA9/PGMM1                      | 46 | GND         | 62 | XIN/PGMCK/PB9    |

| 15 | PA23/PGMD11     |   | 31 | PA8/XOUT32/PGMM<br>0           | 47 | PA1/PGMEN1  | 63 | PB14             |

| 16 | PA20/PGMD8/AD3  |   | 32 | PA7/XIN32/XOUT32/<br>PGMNVALID | 48 | PA0/PGMEN0  | 64 | VDDPLL           |

Note: The bottom pad of the QFN package must be connected to ground.

# 4.3 SAM3N4/2/1/0/00A Package and Pinout

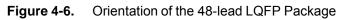

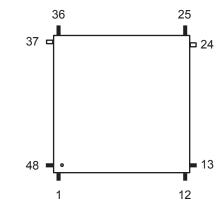

Figure 4-5. Orientation of the 48-pad QFN Package

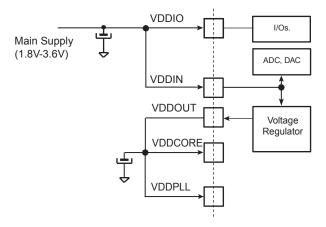

# Figure 5-1. Single Supply

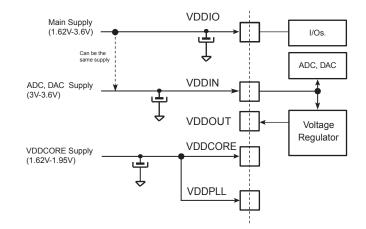

## Figure 5-2. Core Externally Supplied

### Note: Restrictions

With Main Supply < 3V, ADC and DAC are not usable. With Main Supply >= 3V, all peripherals are usable.

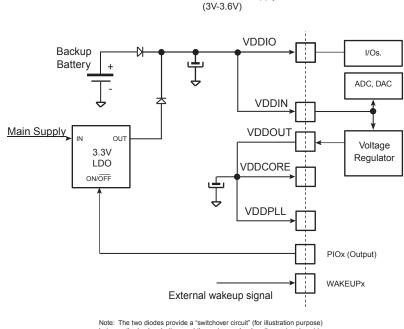

Figure 5-3 below provides an example of the powering scheme when using a backup battery. Since the PIO state is preserved when in backup mode, any free PIO line can be used to switch off the external regulator by driving the PIO line at low level (PIO is input, pull-up enabled after backup reset). External wake-up of the system can be from a push button or any signal. See Section 5.6 "Wake-up Sources" for further details.TFBGA

ADC, DAC Supply

### **Figure 5-3.** Core Externally Supplied (backup battery)

Note: The two diodes provide a "switchover circuit" (for illustration purpose) between the backup battery and the main supply when the system is put in backup mode.

## 5.4 Active Mode

Active mode is the normal running mode with the core clock running from the fast RC oscillator, the main crystal oscillator or the PLL. The power management controller can be used to adapt the frequency and to disable the peripheral clocks.

### 5.5 Low Power Modes

The various low-power modes of the SAM3N are described below:

### 5.5.1 Backup Mode

The purpose of backup mode is to achieve the lowest power consumption possible in a system that is performing periodic wakeups to carry out tasks but not requiring fast startup time (<0.1ms). Total current consumption is 3  $\mu$ A typical.

The Supply Controller, zero-power power-on reset, RTT, RTC, Backup registers and 32 kHz oscillator (RC or crystal oscillator selected by software in the Supply Controller) are running. The regulator and the core supply are off.

Backup mode is based on the Cortex-M3 deep sleep mode with the voltage regulator disabled.

The SAM3N can be awakened from this mode through WUP0-15 pins, the supply monitor (SM), the RTT or RTC wake-up event.

Backup mode is entered by using WFE instructions with the SLEEPDEEP bit in the System Control Register of the Cortex-M3 set to 1. (See the Power management description in The ARM Cortex M3 Processor section of the product datasheet).

Exit from Backup mode happens if one of the following enable wake-up events occurs:

• WKUPEN0-15 pins (level transition, configurable debouncing)

- Supply Monitor alarm

- RTC alarm

- RTT alarm

### 5.5.2 Wait Mode

The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a powered state for a startup time of less than 10  $\mu$ s. Current Consumption in Wait mode is typically 15  $\mu$ A (total current consumption) if the internal voltage regulator is used or 8  $\mu$ A if an external regulator is used.

In this mode, the clocks of the core, peripherals and memories are stopped. However, the core, peripherals and memories power supplies are still powered. From this mode, a fast start up is available.

This mode is entered via Wait for Event (WFE) instructions with LPM = 1 (Low Power Mode bit in PMC\_FSMR). The Cortex-M3 is able to handle external or internal events in order to wake up the core (WFE). By configuring the WUP0-15 external lines as fast startup wake-up pins (refer to Section 5.7 "Fast Start-Up"). RTC or RTT Alarm wake-up events can be used to wake up the CPU (exit from WFE).

Entering Wait Mode:

- Select the 4/8/12 MHz fast RC oscillator as Main Clock

- Set the LPM bit in the PMC Fast Startup Mode Register (PMC\_FSMR)

- · Execute the Wait-For-Event (WFE) instruction of the processor

- Note: Internal Main clock resynchronization cycles are necessary between the writing of MOSCRCEN bit and the effective entry in Wait mode. Depending on the user application, Waiting for MOSCRCEN bit to be cleared is recommended to ensure that the core will not execute undesired instructions.

### 5.5.3 Sleep Mode

The purpose of sleep mode is to optimize power consumption of the device versus response time. In this mode, only the core clock is stopped. The peripheral clocks can be enabled. The current consumption in this mode is application dependent.

This mode is entered via Wait for Interrupt (WFI) or Wait for Event (WFE) instructions with LPM = 0 in PMC\_FSMR.

The processor can be woke up from an interrupt if WFI instruction of the Cortex M3 is used, or from an event if the WFE instruction is used to enter this mode.

### 5.5.4 Low Power Mode Summary Table

The modes detailed above are the main low power modes. Each part can be set to on or off separately and wake up sources can be individually configured. Table 5-1 below shows a summary of the configurations of the low power modes.

Table 5-1.

Low Power Mode Configuration Summary

| Mode           | SUPC,<br>32 kHz<br>Oscillator<br>RTC RTT<br>Backup<br>Registers,<br>POR<br>(Backup<br>Region) | Regulator | Core<br>Memory<br>Peripherals           | Mode Entry                                          | Potential Wake Up<br>Sources                                                                                                                                                     |                 | PIO State<br>while in Low<br>Power Mode | PIO State<br>at Wake Up                             | Consumption               | Wake Up<br>Time <sup>(1)</sup> |

|----------------|-----------------------------------------------------------------------------------------------|-----------|-----------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------|-----------------------------------------------------|---------------------------|--------------------------------|

| Backup<br>Mode | ON                                                                                            | OFF       | OFF<br>(Not powered)                    | WFE<br>+SLEEPDEEP<br>bit = 1                        | WUP0-15 pins<br>BOD alarm<br>RTC alarm<br>RTT alarm                                                                                                                              | Reset           | Previous<br>state saved                 | PIOA &<br>PIOB &<br>PIOC<br>Inputs with<br>pull ups | 3 μΑ typ <sup>(4)</sup>   | < 0.1 ms                       |

| Wait<br>Mode   | ON                                                                                            | ON        | Powered<br>(Not clocked)                | WFE<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 1        | Any Event from: Fast<br>startup through<br>WUP0-15 pins<br>RTC alarm<br>RTT alarm                                                                                                | Clocked<br>back | Previous<br>state saved                 | Unchanged                                           | 5 μΑ/15 μΑ <sup>(5)</sup> | < 10 µs                        |

| Sleep<br>Mode  | ON                                                                                            | ON        | Powered <sup>(7)</sup><br>(Not clocked) | WFE or WFI<br>+SLEEPDEEP<br>bit = 0<br>+LPM bit = 0 | Entry mode = WFI<br>Interrupt Only; Entry<br>mode = WFE Any<br>Enabled Interrupt<br>and/or Any Event<br>from: Fast start-up<br>through WUP0-15<br>pins<br>RTC alarm<br>RTT alarm | Clocked<br>back | Previous<br>state saved                 | Unchanged                                           | (6)                       | (6)                            |

Notes: 1. When considering wake-up time, the time required to start the PLL is not taken into account. Once started, the device works with the 4/8/12 MHz Fast RC oscillator. The user has to add the PLL start-up time if it is needed in the system. The wake-up time is defined as the time taken for wake up until the first instruction is fetched.

- 2. The external loads on PIOs are not taken into account in the calculation.

- 3. Supply Monitor current consumption is not included.

- 4. Total Current consumption.

- 5. 5 μA on VDDCORE, 15 μA for total current consumption (using internal voltage regulator), 8 μA for total current consumption (without using internal voltage regulator).

- 6. Depends on MCK frequency.

- 7. In this mode the core is supplied and not clocked but some peripherals can be clocked.

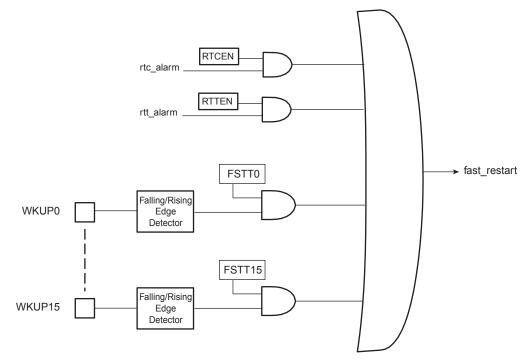

# 5.7 Fast Start-Up

The SAM3N allows the processor to restart in a few microseconds while the processor is in wait mode. A fast start up can occur upon detection of a low level on one of the 19 wake-up inputs (WKUP0 to 15 + SM + RTC + RTT).

The fast restart circuitry, as shown in Figure 5-5, is fully asynchronous and provides a fast startup signal to the Power Management Controller. As soon as the fast start-up signal is asserted, the PMC automatically restarts the embedded 4 MHz fast RC oscillator, switches the master clock on this 4 MHz clock and reenables the processor clock.

### Figure 5-5. Fast Start-Up Sources

# 6. Input/Output Lines

The SAM3N has several kinds of input/output (I/O) lines such as general purpose I/Os (GPIO) and system I/Os. GPIOs can have alternate functionality due to multiplexing capabilities of the PIO controllers. The same PIO line can be used whether in IO mode or by the multiplexed peripheral. System I/Os include pins such as test pins, oscillators, erase or analog inputs.

# 6.1 General Purpose I/O Lines

GPIO Lines are managed by PIO Controllers. All I/Os have several input or output modes such as pull-up or pull-down, input Schmitt triggers, multi-drive (open-drain), glitch filters, debouncing or input change interrupt. Programming of these modes is performed independently for each I/O line through the PIO controller user interface. For more details, refer to the product PIO controller section.

The input output buffers of the PIO lines are supplied through VDDIO power supply rail.

The SAM3N embeds high speed pads able to handle up to 45 MHz for SPI clock lines and 35 MHz on other lines. See AC Characteristics Section in the Electrical Characteristics Section of the datasheet for more details. Typical pull-up and pull-down value is 100 k $\Omega$  for all I/Os.

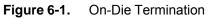

Each I/O line also embeds an ODT (On-Die Termination), (see Figure 6-1). It consists of an internal series resistor termination scheme for impedance matching between the driver output (SAM3N) and the PCB trace impedance preventing signal reflection. The series resistor helps to reduce I/O switching current (di/dt) thereby reducing in turn, EMI. It also decreases overshoot and undershoot (ringing) due to inductance of interconnect between devices or between boards. In conclusion ODT helps diminish signal integrity issues.

# 6.2 System I/O Lines

System I/O lines are pins used by oscillators, test mode, reset and JTAG to name but a few. Described below are the SAM3N system I/O lines shared with PIO lines:

These pins are software configurable as general purpose I/O or system pins. At startup the default function of these pins is always used.

### 9.1.3.4 Flash Speed

The user needs to set the number of wait states depending on the frequency used.

For more details, refer to the AC Characteristics sub section in the product Electrical Characteristics Section.

#### 9.1.3.5 Lock Regions

Several lock bits used to protect write and erase operations on lock regions. A lock region is composed of several consecutive pages, and each lock region has its associated lock bit.

| Product | Number of lock bits | Lock region size     |

|---------|---------------------|----------------------|

| SAM3N4  | 16                  | 16 kbytes (64 pages) |

| SAM3N2  | 8                   | 16 kbytes (64 pages) |

| SAM3N1  | 4                   | 16 kbytes (64 pages) |

#### Table 9-1. Lock bit number

If a locked-region's erase or program command occurs, the command is aborted and the EEFC triggers an interrupt.

The lock bits are software programmable through the EEFC User Interface. The command "Set Lock Bit" enables the protection. The command "Clear Lock Bit" unlocks the lock region.

Asserting the ERASE pin clears the lock bits, thus unlocking the entire Flash.

### 9.1.3.6 Security Bit Feature

The SAM3N features a security bit, based on a specific General Purpose NVM bit (GPNVM bit 0). When the security is enabled, any access to the Flash, either through the ICE interface or through the Fast Flash Programming Interface, is forbidden. This ensures the confidentiality of the code programmed in the Flash.

This security bit can only be enabled, through the command "Set General Purpose NVM Bit 0" of the EEFC User Interface. Disabling the security bit can only be achieved by asserting the ERASE pin at 1, after a full Flash erase is performed. When the security bit is deactivated, all accesses to the Flash are permitted.

It is important to note that the assertion of the ERASE pin should always be longer than 200 ms.

As the ERASE pin integrates a permanent pull-down, it can be left unconnected during normal operation. However, it is safer to connect it directly to GND for the final application.

### 9.1.3.7 Calibration Bits

NVM bits are used to calibrate the brownout detector and the voltage regulator. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the calibration bits.

#### 9.1.3.8 Unique Identifier

Each device integrates its own 128-bit unique identifier. These bits are factory configured and cannot be changed by the user. The ERASE pin has no effect on the unique identifier.

FSTT0 - FSTT15 are possible Fast Startup Sources, generated by WKUP0-WKUP15 Pins, but are not physical pins.

The reset circuitry is based on a zero-power power-on reset cell and a brownout detector cell. The zero-power power-on reset allows the Supply Controller to start properly, while the software-programmable brownout detector allows detection of either a battery discharge or main voltage loss.

The Slow Clock generator is based on a 32 kHz crystal oscillator and an embedded 32 kHz RC oscillator. The Slow Clock defaults to the RC oscillator, but the software can enable the crystal oscillator and select it as the Slow Clock source.

The Supply Controller starts up the device by sequentially enabling the internal power switches and the Voltage Regulator, then it generates the proper reset signals to the core power supply.

It also enables to set the system in different low power modes and to wake it up from a wide range of events.

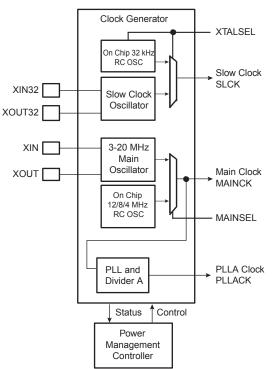

# 10.5 Clock Generator

The Clock Generator is made up of:

- One Low Power 32768Hz Slow Clock Oscillator with bypass mode

- One Low-Power RC Oscillator

- · One 3-20 MHz Crystal or Ceramic resonator Oscillator, which can be bypassed

- One Fast RC Oscillator factory programmed, 3 output frequencies can be selected: 4, 8 or 12 MHz. By default 4 MHz is selected.

- One 60 to 130 MHz programmable PLL, capable to provide the clock MCK to the processor and to the peripherals. The input frequency of PLL is from 3.5 to 20 MHz.

### Figure 10-2. Clock Generator Block Diagram

# **SAM3N Summary**

## 10.8 SysTick Timer

- 24-bit down counter

- Self-reload capability

- Flexible System timer

## 10.9 Real-time Timer

- · Real-time Timer, allowing backup of time with different accuracies

- 32-bit Free-running back-up Counter

- Integrates a 16-bit programmable prescaler running on slow clock

- Alarm register capable to generate a wake-up of the system through the Shut Down Controller

## 10.10 Real Time Clock

- Low power consumption

- Full asynchronous design

- Two hundred year calendar

- Programmable Periodic Interrupt

- · Alarm and update parallel load

- · Control of alarm and update Time/Calendar Data In

# 10.11 General Purpose Backup Registers

· Eight 32-bit general-purpose backup registers

# 10.12 Nested Vectored Interrupt Controller

- Thirty Two maskable external interrupts

- Sixteen priority levels

- · Processor state automatically saved on interrupt entry, and restored on

- · Dynamic reprioritization of interrupts

- Priority grouping

- selection of pre-empting interrupt levels and non pre-empting interrupt levels

- · Support for tail-chaining and late arrival of interrupts

- back-to-back interrupt processing without the overhead of state saving and restoration between interrupts.

- Processor state automatically saved on interrupt entry and restored on interrupt exit, with no instruction overhead

- Multi-drive option enables driving in open drain

- Programmable pull up on each I/O line

- Pin data status register, supplies visibility of the level on the pin at any time

- Selection of the drive level

- Synchronous output, provides Set and Clear of several I/O lines in a single write

# 11. Peripherals

# **11.1** Peripheral Identifiers

Table 11-1 defines the Peripheral Identifiers of the SAM3N4/2/1/0/00. A peripheral identifier is required for the control of the peripheral interrupt with the Nested Vectored Interrupt Controller and for the control of the peripheral clock with the Power Management Controller.

| Table 11-1.         Peripheral Identifiers |

|--------------------------------------------|

|--------------------------------------------|

| Instance ID | Instance Name | NVIC Interrupt | PMC Clock Control | Instance Description        |

|-------------|---------------|----------------|-------------------|-----------------------------|

| 0           | SUPC          | X              |                   | Supply Controller           |

| 1           | RSTC          | X              |                   | Reset Controller            |

| 2           | RTC           | X              |                   | Real Time Clock             |

| 3           | RTT           | X              |                   | Real Time Timer             |

| 4           | WDT           | X              |                   | Watchdog Timer              |

| 5           | PMC           | X              |                   | Power Management Controller |

| 6           | EEFC          | X              |                   | Enhanced Flash Controller   |

| 7           | -             | -              |                   | Reserved                    |

| 8           | UART0         | X              | X                 | UART 0                      |

| 9           | UART1         | X              | X                 | UART 1                      |

| 10          | -             | -              | -                 | Reserved                    |

| 11          | PIOA          | X              | X                 | Parallel I/O Controller A   |

| 12          | PIOB          | X              | X                 | Parallel I/O Controller B   |

| 13          | PIOC          | X              | X                 | Parallel I/O Controller C   |

| 14          | USART0        | X              | X                 | USART 0                     |

| 15          | USART1        | X              | X                 | USART 1                     |

| 16          | -             | -              | -                 | Reserved                    |

| 17          | -             | -              | -                 | Reserved                    |

| 18          | -             | -              | -                 | Reserved                    |

| 19          | TWIO          | X              | X                 | Two Wire Interface 0        |

| 20          | TWI1          | x              | X                 | Two Wire Interface 1        |

| 21          | SPI           | X              | X                 | Serial Peripheral Interface |

| 22          | -             | -              | -                 | Reserved                    |

| 23          | TC0           | x              | X                 | Timer/Counter 0             |

| 24          | TC1           | X              | X                 | Timer/Counter 1             |

# 11.2.2 PIO Controller B Multiplexing

| I/O Line | Peripheral A | Peripheral B | Peripheral C | Extra Function | System Function  | Comments            |

|----------|--------------|--------------|--------------|----------------|------------------|---------------------|

| PB0      | PWM0         |              |              | AD4            |                  |                     |

| PB1      | PWM1         |              |              | AD5            |                  |                     |

| PB2      | URXD1        | NPCS2        |              | AD6/WKUP12     |                  |                     |

| PB3      | UTXD1        | PCK2         |              | AD7            |                  |                     |

| PB4      | TWD1         | PWM2         |              |                | TDI              |                     |

| PB5      | TWCK1        |              |              | WKUP13         | TDO/<br>TRACESWO |                     |

| PB6      |              |              |              |                | TMS/SWDIO        |                     |

| PB7      |              |              |              |                | TCK/SWCLK        |                     |

| PB8      |              |              |              |                | XOUT             |                     |

| PB9      |              |              |              |                | XIN              |                     |

| PB10     |              |              |              |                |                  |                     |

| PB11     |              |              |              |                |                  |                     |

| PB12     |              |              |              |                | ERASE            |                     |

| PB13     |              | PCK0         |              | DAC0           |                  | 64/100-pin versions |

| PB14     | NPCS1        | PWM3         |              |                |                  | 64/100-pin versions |

# Table 11-3. Multiplexing on PIO Controller B (PIOB)