#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M3                                                          |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 48MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                               |

| Number of I/O              | 79                                                                       |

| Program Memory Size        | 64KB (64K x 8)                                                           |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 8K x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.62V ~ 3.6V                                                             |

| Data Converters            | A/D 16x10b; D/A 1x10b                                                    |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-TFBGA                                                                |

| Supplier Device Package    | 100-TFBGA (9x9)                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsam3n1cb-cur |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

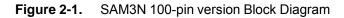

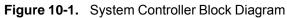

## 2. SAM3N Block Diagram

### 4.1.4 100-ball TFBGA Pinout

| A1  | PB1     | C6  | PB7     | F1  | PA18    | H6  | PC4     |

|-----|---------|-----|---------|-----|---------|-----|---------|

| A2  | PC29    | C7  | PC16    | F2  | PC26    | H7  | PA11    |

| A3  | VDDIO   | C8  | PA1     | F3  | VDDOUT  | H8  | PC1     |

| A4  | PB9     | C9  | PC17    | F4  | GND     | H9  | PA6     |

| A5  | PB8     | C10 | PA0     | F5  | VDDIO   | H10 | PB4     |

| A6  | PB13    | D1  | PB3     | F6  | PA27    | J1  | PC15    |

| A7  | PB11    | D2  | PB0     | F7  | PC8     | J2  | PC0     |

| A8  | PB10    | D3  | PC24    | F8  | PA28    | J3  | PA16    |

| A9  | PB6     | D4  | PC22    | F9  | TST     | J4  | PC6     |

| A10 | JTAGSEL | D5  | GND     | F10 | PC9     | J5  | PA24    |

| B1  | PC30    | D6  | GND     | G1  | PA21    | J6  | PA25    |

| B2  | ADVREF  | D7  | VDDCORE | G2  | PC27    | J7  | PA10    |

| B3  | GNDANA  | D8  | PA2     | G3  | PA15    | J8  | GND     |

| B4  | PB14    | D9  | PC11    | G4  | VDDCORE | J9  | VDDCORE |

| B5  | PC21    | D10 | PC14    | G5  | VDDCORE | J10 | VDDIO   |

| B6  | PC20    | E1  | PA17    | G6  | PA26    | K1  | PA22    |

| B7  | PA31    | E2  | PC31    | G7  | PA12    | K2  | PC13    |

| B8  | PC19    | E3  | VDDIN   | G8  | PC28    | K3  | PC12    |

| B9  | PC18    | E4  | GND     | G9  | PA4     | K4  | PA20    |

| B10 | PB5     | E5  | GND     | G10 | PA5     | K5  | PC5     |

| C1  | PB2     | E6  | NRST    | H1  | PA19    | K6  | PC3     |

| C2  | VDDPLL  | E7  | PA29    | H2  | PA23    | K7  | PC2     |

| C3  | PC25    | E8  | PA30    | H3  | PC7     | K8  | PA9     |

| C4  | PC23    | E9  | PC10    | H4  | PA14    | К9  | PA8     |

| C5  | PB12    | E10 | PA3     | H5  | PA13    | K10 | PA7     |

# Table 4-2. 100-ball TFBGA SAM3N4/2/1/0/00C Pinout

## 4.3 SAM3N4/2/1/0/00A Package and Pinout

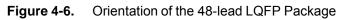

Figure 4-5. Orientation of the 48-pad QFN Package

### 4.3.1 48-Lead LQFP and QFN Pinout

| 1  | ADVREF         | 13 | VDDIO                   | 25 | TDI/PB4     | 37 | TDO/TRACESWO/<br>PB5 |

|----|----------------|----|-------------------------|----|-------------|----|----------------------|

| 2  | GND            | 14 | PA16/PGMD4              | 26 | PA6/PGMNOE  | 38 | JTAGSEL              |

| 3  | PB0/AD4        | 15 | PA15/PGMD3              | 27 | PA5/PGMRDY  | 39 | TMS/SWDIO/PB6        |

| 4  | PB1/AD5        | 16 | PA14/PGMD2              | 28 | PA4/PGMNCMD | 40 | TCK/SWCLK/PB7        |

| 5  | PB2/AD6        | 17 | PA13/PGMD1              | 29 | NRST        | 41 | VDDCORE              |

| 6  | PB3/AD7        | 18 | VDDCORE                 | 30 | TST         | 42 | ERASE/PB12           |

| 7  | VDDIN          | 19 | PA12/PGMD0              | 31 | PA3         | 43 | PB10                 |

| 8  | VDDOUT         | 20 | PA11/PGMM3              | 32 | PA2/PGMEN2  | 44 | PB11                 |

| 9  | PA17/PGMD5/AD0 | 21 | PA10/PGMM2              | 33 | VDDIO       | 45 | XOUT/PB8             |

| 10 | PA18/PGMD6/AD1 | 22 | PA9/PGMM1               | 34 | GND         | 46 | XIN/P/PB9/GMCK       |

| 11 | PA19/PGMD7/AD2 | 23 | PA8/XOUT32/PG<br>MM0    | 35 | PA1/PGMEN1  | 47 | VDDIO                |

| 12 | PA20/AD3       | 24 | PA7/XIN32/PGMN<br>VALID | 36 | PA0/PGMEN0  | 48 | VDDPLL               |

### Table 4-4. 48-pin SAM3N4/2/1/0/00A Pinout

Note: The bottom pad of the QFN package must be connected to ground.

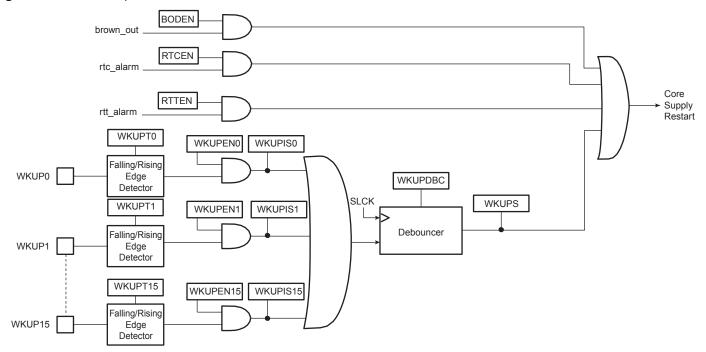

- Supply Monitor alarm

- RTC alarm

- RTT alarm

#### 5.5.2 Wait Mode

The purpose of the wait mode is to achieve very low power consumption while maintaining the whole device in a powered state for a startup time of less than 10  $\mu$ s. Current Consumption in Wait mode is typically 15  $\mu$ A (total current consumption) if the internal voltage regulator is used or 8  $\mu$ A if an external regulator is used.

In this mode, the clocks of the core, peripherals and memories are stopped. However, the core, peripherals and memories power supplies are still powered. From this mode, a fast start up is available.

This mode is entered via Wait for Event (WFE) instructions with LPM = 1 (Low Power Mode bit in PMC\_FSMR). The Cortex-M3 is able to handle external or internal events in order to wake up the core (WFE). By configuring the WUP0-15 external lines as fast startup wake-up pins (refer to Section 5.7 "Fast Start-Up"). RTC or RTT Alarm wake-up events can be used to wake up the CPU (exit from WFE).

Entering Wait Mode:

- Select the 4/8/12 MHz fast RC oscillator as Main Clock

- Set the LPM bit in the PMC Fast Startup Mode Register (PMC\_FSMR)

- · Execute the Wait-For-Event (WFE) instruction of the processor

- Note: Internal Main clock resynchronization cycles are necessary between the writing of MOSCRCEN bit and the effective entry in Wait mode. Depending on the user application, Waiting for MOSCRCEN bit to be cleared is recommended to ensure that the core will not execute undesired instructions.

#### 5.5.3 Sleep Mode

The purpose of sleep mode is to optimize power consumption of the device versus response time. In this mode, only the core clock is stopped. The peripheral clocks can be enabled. The current consumption in this mode is application dependent.

This mode is entered via Wait for Interrupt (WFI) or Wait for Event (WFE) instructions with LPM = 0 in PMC\_FSMR.

The processor can be woke up from an interrupt if WFI instruction of the Cortex M3 is used, or from an event if the WFE instruction is used to enter this mode.

### 5.6 Wake-up Sources

The wake-up events allow the device to exit backup mode. When a wake-up event is detected, the Supply Controller performs a sequence which automatically reenables the core power supply and the SRAM power supply, if they are not already enabled.

### Figure 5-4. Wake-up Source

| SYSTEM_IO<br>bit number | Default function<br>after reset | Other function | Constraints for<br>normal start     | Configuration                                                      |

|-------------------------|---------------------------------|----------------|-------------------------------------|--------------------------------------------------------------------|

| 12                      | ERASE                           | PB12           | Low Level at startup <sup>(1)</sup> | In Matrix User Interface Registers                                 |

| 7                       | TCK/SWCLK                       | PB7            | -                                   | (Refer to the System I/O                                           |

| 6                       | TMS/SWDIO                       | PB6            | -                                   | Configuration Register in the Bus<br>Matrix section of the product |

| 5                       | TDO/TRACESWO                    | PB5            | -                                   | datasheet.)                                                        |

| 4                       | TDI                             | PB4            | -                                   |                                                                    |

| -                       | PA7                             | XIN32          | -                                   |                                                                    |

| -                       | PA8                             | XOUT32         | -                                   | See footnote <sup>(2)</sup> below                                  |

| -                       | PB9                             | XIN            | -                                   | Or a facturate (3) heless                                          |

| -                       | PB8                             | XOUT           | -                                   | See footnote <sup>(3)</sup> below                                  |

Table 6-1.

System I/O Configuration Pin List.

Notes: 1. If PB12 is used as PIO input in user applications, a low level must be ensured at startup to prevent Flash erase before the user application sets PB12 into PIO mode.

2. In the product Datasheet Refer to: Slow Clock Generator of the Supply Controller section.

3. In the product Datasheet Refer to: 3 to 20 MHZ Crystal Oscillator information in the PMC section.

### 6.2.1 Serial Wire JTAG Debug Port (SWJ-DP) Pins

The SWJ-DP pins are TCK/SWCLK, TMS/SWDIO, TDO/SWO, TDI and commonly provided on a standard 20-pin JTAG connector defined by ARM. For more details about voltage reference and reset state, refer to Table 3-1 on page 7.

At startup, SWJ-DP pins are configured in SWJ-DP mode to allow connection with debugging probe. Please refer to the Debug and Test Section of the product datasheet.

SWJ-DP pins can be used as standard I/Os to provide users more general input/output pins when the debug port is not needed in the end application. Mode selection between SWJ-DP mode (System IO mode) and general IO mode is performed through the AHB Matrix Special Function Registers (MATRIX\_SFR). Configuration of the pad for pull-up, triggers, debouncing and glitch filters is possible regardless of the mode.

The JTAGSEL pin is used to select the JTAG boundary scan when asserted at a high level. It integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

By default, the JTAG Debug Port is active. If the debugger host wants to switch to the Serial Wire Debug Port, it must provide a dedicated JTAG sequence on TMS/SWDIO and TCK/SWCLK which disables the JTAG-DP and enables the SW-DP. When the Serial Wire Debug Port is active, TDO/TRACESWO can be used for trace.

The asynchronous TRACE output (TRACESWO) is multiplexed with TDO. So the asynchronous trace can only be used with SW-DP, not JTAG-DP. For more information about SW-DP and JTAG-DP switching, please refer to the Debug and Test Section.

### 6.3 Test Pin

The TST pin is used for JTAG Boundary Scan Manufacturing Test or Fast Flash programming mode of the SAM3N series. The TST pin integrates a permanent pull-down resistor of about 15 k $\Omega$  to GND, so that it can be left unconnected for normal operations. To enter fast programming mode, see the Fast Flash Programming Interface (FFPI) section. For more on the manufacturing and test mode, refer to the "Debug and Test" section of the product datasheet.

### 6.4 NRST Pin

The NRST pin is bidirectional. It is handled by the on-chip reset controller and can be driven low to provide a reset signal to the external components or asserted low externally to reset the microcontroller. It will reset the Core and the peripherals except the Backup region (RTC, RTT and Supply Controller). There is no constraint on the length of the reset pulse and the reset controller can guarantee a minimum pulse length. The NRST pin integrates a permanent pull-up resistor to VDDIO of about 100 k $\Omega$ . By default, the NRST pin is configured as an input.

### 6.5 ERASE Pin

The ERASE pin is used to reinitialize the Flash content (and some of its NVM bits) to an erased state (all bits read as logic level 1). It integrates a pull-down resistor of about 100 k $\Omega$  to GND, so that it can be left unconnected for normal operations.

This pin is debounced by SCLK to improve the glitch tolerance. When the ERASE pin is tied high during less than 100 ms, it is not taken into account. The pin must be tied high during more than 220 ms to perform a Flash erase operation.

The ERASE pin is a system I/O pin and can be used as a standard I/O. At startup, the ERASE pin is not configured as a PIO pin. If the ERASE pin is used as a standard I/O, startup level of this pin must be low to prevent unwanted erasing. Please refer to Section 11.2 "Peripheral Signals Multiplexing on I/O Lines" on page 42. Also, if the ERASE pin is used as a standard I/O output, asserting the pin to low does not erase the Flash.

#### 7.5 Master to Slave Access

All the Masters can normally access all the Slaves. However, some paths do not make sense, for example allowing access from the Cortex-M3 S Bus to the Internal ROM. Thus, these paths are forbidden or simply not wired, and shown as "-" in Table 7-3.

| Table 7-3. | SAM3N Master to Slave Access |   |  |  |  |

|------------|------------------------------|---|--|--|--|

|            | Masters                      | 0 |  |  |  |

|        | Masters           | 0                 | 1               | 2   |

|--------|-------------------|-------------------|-----------------|-----|

| Slaves |                   | Cortex-M3 I/D Bus | Cortex-M3 S Bus | PDC |

| 0      | Internal SRAM     | -                 | х               | Х   |

| 1      | Internal ROM      | Х                 | -               | х   |

| 2      | Internal Flash    | Х                 | -               | -   |

| 3      | Peripheral Bridge | -                 | х               | Х   |

#### 7.6 Peripheral DMA Controller

- · Handles data transfer between peripherals and memories

- Low bus arbitration overhead

- One Master Clock cycle needed for a transfer from memory to peripheral

- Two Master Clock cycles needed for a transfer from peripheral to memory

- · Next Pointer management for reducing interrupt latency requirement

The Peripheral DMA Controller handles transfer requests from the channel according to the following priorities (Low to High priorities):

| Instance name | Channel T/R | 100 & 64 Pins | 48 Pins |

|---------------|-------------|---------------|---------|

| TWI0          | Transmit    | x             | х       |

| UART0         | Transmit    | x             | х       |

| USART0        | Transmit    | x             | Х       |

| DAC           | Transmit    | x             | N/A     |

| SPI           | Transmit    | x             | х       |

| TWIO          | Receive     | x             | х       |

| UART0         | Receive     | x             | х       |

| USART0        | Receive     | x             | х       |

| ADC           | Receive     | x             | х       |

| SPI           | Receive     | x             | х       |

Table 7-4. Peripheral DMA Controller

# SAM3N Summary

## 9. Memories

### 9.1 Embedded Memories

### 9.1.1 Internal SRAM

The SAM3N4 product embeds a total of 24-Kbytes high-speed SRAM.

The SAM3N2 product embeds a total of 16-Kbytes high-speed SRAM.

The SAM3N1 product embeds a total of 8-Kbytes high-speed SRAM.

The SRAM is accessible over System Cortex-M3 bus at address 0x2000 0000.

The SRAM is in the bit band region. The bit band alias region is from  $0x2200\ 0000$  and 0x23FF FFFF.

RAM size must be configurable by calibration fuses.

### 9.1.2 Internal ROM

The SAM3N product embeds an Internal ROM, which contains the SAM Boot Assistant (SAM-BA), In Application Programming routines (IAP) and Fast Flash Programming Interface (FFPI).

At any time, the ROM is mapped at address 0x0080 0000.

### 9.1.3 Embedded Flash

### 9.1.3.1 Flash Overview

The Flash of the SAM3N4 (256 Kbytes) is organized in one bank of 1024 pages of 256 bytes (Single plane).

The Flash of the SAM3N2 (128 Kbytes) is organized in one bank of 512 pages of 256 bytes (Single Plane).

The Flash of the SAM3N1 (64 Kbytes) is organized in one bank of 256 pages of 256 bytes (Single plane).

The Flash contains a 128-byte write buffer, accessible through a 32-bit interface.

9.1.3.2 Flash Power Supply

The Flash is supplied by VDDCORE.

## 9.1.3.3 Enhanced Embedded Flash Controller

The Enhanced Embedded Flash Controller (EEFC) manages accesses performed by the masters of the system. It enables reading the Flash and writing the write buffer. It also contains a User Interface, mapped on the APB.

The Enhanced Embedded Flash Controller ensures the interface of the Flash block with the 32bit internal bus. Its 128-bit wide memory interface increases performance.

The user can choose between high performance or lower current consumption by selecting either 128-bit or 64-bit access. It also manages the programming, erasing, locking and unlocking sequences of the Flash using a full set of commands.

One of the commands returns the embedded Flash descriptor definition that informs the system about the Flash organization, thus making the software generic.

**SAM3N Summary**

#### 9.1.3.9 Fast Flash Programming Interface

The Fast Flash Programming Interface allows programming the device through either a serial JTAG interface or through a multiplexed fully-handshaked parallel port. It allows gang programming with market-standard industrial programmers.

The FFPI supports read, page program, page erase, full erase, lock, unlock and protect commands.

The Fast Flash Programming Interface is enabled and the Fast Programming Mode is entered when TST and PA0 and PA1are tied low.

#### 9.1.3.10 SAM-BA Boot

The SAM-BA Boot is a default Boot Program which provides an easy way to program in-situ the on-chip Flash memory.

The SAM-BA Boot Assistant supports serial communication via the UART0.

The SAM-BA Boot provides an interface with SAM-BA Graphic User Interface (GUI).

The SAM-BA Boot is in ROM and is mapped in Flash at address 0x0 when GPNVM bit 1 is set to 0.

#### 9.1.3.11 GPNVM Bits

The SAM3N features three GPNVM bits that can be cleared or set respectively through the commands "Clear GPNVM Bit" and "Set GPNVM Bit" of the EEFC User Interface.

| GPNVMBit[#] | Function            |

|-------------|---------------------|

| 0           | Security bit        |

| 1           | Boot mode selection |

#### 9.1.4 Boot Strategies

The system always boots at address 0x0. To ensure a maximum boot possibilities the memory layout can be changed via GPNVM.

A general purpose NVM (GPNVM) bit is used to boot either on the ROM (default) or from the Flash.

The GPNVM bit can be cleared or set respectively through the commands "Clear General-purpose NVM Bit" and "Set General-purpose NVM Bit" of the EEFC User Interface.

Setting the GPNVM Bit 1 selects the boot from the Flash, clearing it selects the boot from the ROM. Asserting ERASE clears the GPNVM Bit 1 and thus selects the boot from the ROM by default.

FSTT0 - FSTT15 are possible Fast Startup Sources, generated by WKUP0-WKUP15 Pins, but are not physical pins.

### **10.1** System Controller and Peripherals Mapping

Please refer to Figure 8-1, "SAM3N4/2/1/0/00 Product Mapping" on page 30.

All the peripherals are in the bit band region and are mapped in the bit band alias region.

### 10.2 Power-on-Reset, Brownout and Supply Monitor

The SAM3N embeds three features to monitor, warn and/or reset the chip:

- Power-on-Reset on VDDIO

- Brownout Detector on VDDCORE

- Supply Monitor on VDDIO

#### 10.2.1 Power-on-Reset

The Power-on-Reset monitors VDDIO. It is always activated and monitors voltage at start up but also during power down. If VDDIO goes below the threshold voltage, the entire chip is reset. For more information, refer to the Electrical Characteristics section of the datasheet.

#### 10.2.2 Brownout Detector on VDDCORE

The Brownout Detector monitors VDDCORE. It is active by default. It can be deactivated by software through the Supply Controller (SUPC\_MR). It is especially recommended to disable it during low-power modes such as wait or sleep modes.

If VDDCORE goes below the threshold voltage, the reset of the core is asserted. For more information, refer to the Supply Controller (SUPC) and Electrical Characteristics sections of the datasheet.

#### 10.2.3 Supply Monitor on VDDIO

The Supply Monitor monitors VDDIO. It is inactive by default. It can be activated by software and is fully programmable with 16 steps for the threshold (between 1.9V to 3.4V). It is controlled by the Supply Controller (SUPC). A sample mode is possible. It allows to divide the supply monitor power consumption by a factor of up to 2048. For more information, refer to the SUPC and Electrical Characteristics sections of the datasheet.

### 10.3 Reset Controller

The Reset Controller is based on a Power-on-Reset cell, and a Supply Monitor on VDDCORE.

The Reset Controller is capable to return to the software the source of the last reset, either a general reset, a wake-up reset, a software reset, a user reset or a watchdog reset.

The Reset Controller controls the internal resets of the system and the NRST pin input/output. It is capable to shape a reset signal for the external devices, simplifying to a minimum connection of a push-button on the NRST pin to implement a manual reset.

The configuration of the Reset Controller is saved as supplied on VDDIO.

### 10.4 Supply Controller (SUPC)

The Supply Controller controls the power supplies of each section of the processor and the peripherals (via Voltage regulator control)

The Supply Controller has its own reset circuitry and is clocked by the 32 kHz slow clock generator.

## 3 SAM3N Summary

The reset circuitry is based on a zero-power power-on reset cell and a brownout detector cell. The zero-power power-on reset allows the Supply Controller to start properly, while the software-programmable brownout detector allows detection of either a battery discharge or main voltage loss.

The Slow Clock generator is based on a 32 kHz crystal oscillator and an embedded 32 kHz RC oscillator. The Slow Clock defaults to the RC oscillator, but the software can enable the crystal oscillator and select it as the Slow Clock source.

The Supply Controller starts up the device by sequentially enabling the internal power switches and the Voltage Regulator, then it generates the proper reset signals to the core power supply.

It also enables to set the system in different low power modes and to wake it up from a wide range of events.

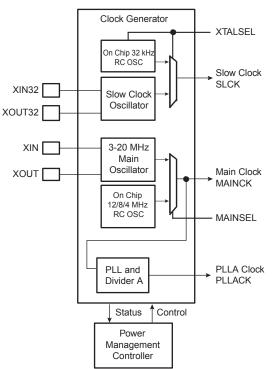

### 10.5 Clock Generator

The Clock Generator is made up of:

- One Low Power 32768Hz Slow Clock Oscillator with bypass mode

- One Low-Power RC Oscillator

- · One 3-20 MHz Crystal or Ceramic resonator Oscillator, which can be bypassed

- One Fast RC Oscillator factory programmed, 3 output frequencies can be selected: 4, 8 or 12 MHz. By default 4 MHz is selected.

- One 60 to 130 MHz programmable PLL, capable to provide the clock MCK to the processor and to the peripherals. The input frequency of PLL is from 3.5 to 20 MHz.

#### Figure 10-2. Clock Generator Block Diagram

- Two multi-purpose input/output signals

- Two global registers that act on all three TC Channels

- Quadrature decoder

- Advanced line filtering

- Position/revolution/speed

- 2-bit Gray Up/Down Counter for Stepper Motor

### 12.6 Pulse Width Modulation Controller (PWM)

- Four channels, one 16-bit counter per channel

- · Common clock generator, providing thirteen different clocks

- One Modulo n counter providing eleven clocks

- Two independent linear dividers working on modulo n counter outputs

- Independent channel programming

- Independent enable/disable commands

- Independent clock selection

- Independent period and duty cycle, with double buffering

- Programmable selection of the output waveform polarity

### 12.7 10-bit Analog-to-Digital Converter

- Up to 16-channel ADC

- 10-bit 384 Ksamples/sec. or 8-bit 583 Ksamples/sec. Successive Approximation Register ADC

- ±2 LSB Integral Non Linearity, ±1 LSB Differential Non Linearity

- Integrated 8-to-1 multiplexer, offering eight independent 3.3V analog inputs

- · External voltage reference for better accuracy on low voltage inputs

- · Individual enable and disable of each channel

- Multiple trigger source

- Hardware or software trigger

- External trigger pin

- Timer Counter 0 to 2 outputs TIOA0 to TIOA2 trigger

- Sleep Mode and conversion sequencer

- Automatic wakeup on trigger and back to sleep mode after conversions of all enabled channels

### 12.8 Digital-to-Analog Converter (DAC)

- 1 channel 10-bit DAC

- Up to 500 ksamples/s conversion rate

- · Flexible conversion range

- Multiple trigger sources

- One PDC channel

s4 SAM3N Summary

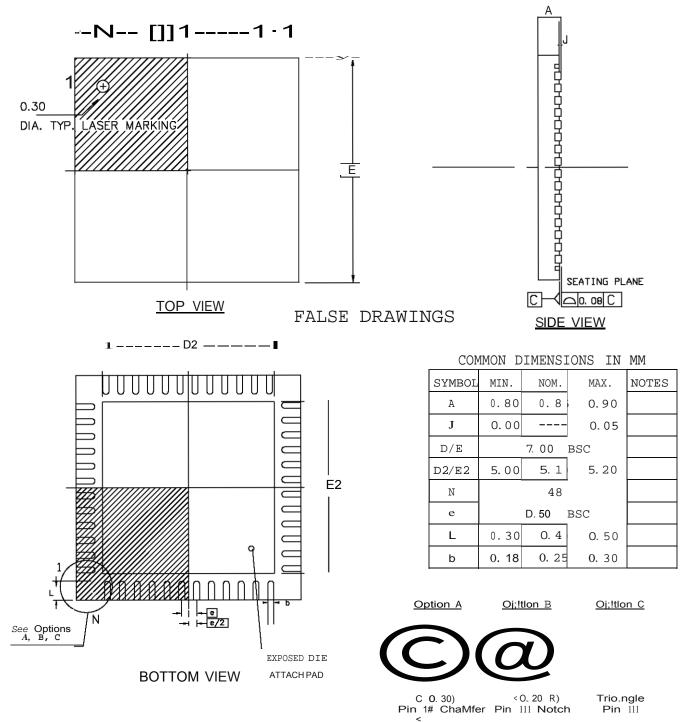

| Table 13-3. 40-pad QFN Fackage Dimensions (in min) |      |            |                |           |           |       |  |

|----------------------------------------------------|------|------------|----------------|-----------|-----------|-------|--|

| Currence l                                         |      | Millimeter |                |           | Inch      |       |  |

| Symbol                                             | Min  | Nom        | Max            | Min       | Nom       | Max   |  |

| А                                                  | _    | _          | 090            | _         | _         | 0.035 |  |

| A1                                                 | _    | _          | 0.050          | _         | _         | 0.002 |  |

| A2                                                 | _    | 0.65       | 0.70           | _         | 0.026     | 0.028 |  |

| A3                                                 |      | 0.20 REF   |                |           | 0.008 REF |       |  |

| b                                                  | 0.18 | 0.20       | 0.23           | 0.007     | 0.008     | 0.009 |  |

| D                                                  |      | 7.00 bsc   |                |           | 0.276 bsc |       |  |

| D2                                                 | 5.45 | 5.60       | 5.75           | 0.215     | 0.220     | 0.226 |  |

| Е                                                  |      | 7.00 bsc   |                | 0.276 bsc |           |       |  |

| E2                                                 | 5.45 | 5.60       | 5.75           | 0.215     | 0.220     | 0.226 |  |

| L                                                  | 0.35 | 0.40       | 0.45           | 0.014     | 0.016     | 0.018 |  |

| е                                                  |      | 0.50 bsc   |                |           | 0.020 bsc |       |  |

| R                                                  | 0.09 | _          | _              | 0.004     | -         | -     |  |

|                                                    |      | Toleranc   | es of Form and | Position  |           |       |  |

| aaa                                                |      | 0.10       |                |           | 0.004     |       |  |

| bbb                                                |      | 0.10       |                |           | 0.004     |       |  |

| CCC                                                |      | 0.05       |                |           | 0.002     |       |  |

Table 13-3.

48-pad QFN Package Dimensions (in mm)

# 14. Ordering Information

Table 14-1.

| Ordering Code | MRL | Flash<br>(Kbytes) | Package  | Package Type | Temperature<br>Operating Range |

|---------------|-----|-------------------|----------|--------------|--------------------------------|

| ATSAM3N4CA-AU | А   | 256               | LQFP100  | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N4CA-CU | А   | 256               | TFBGA100 | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N4BA-AU | А   | 256               | LQFP64   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N4BA-MU | А   | 256               | QFN64    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N4AA-AU | А   | 256               | LQFP48   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N4AA-MU | А   | 256               | QFN48    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N2CA-AU | А   | 128               | LQFP100  | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N2CA-CU | А   | 128               | TFBGA100 | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N2BA-AU | А   | 128               | LQFP64   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N2BA-MU | А   | 128               | QFN64    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N2AA-AU | А   | 128               | LQFP48   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N2AA-MU | А   | 128               | QFN48    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1CA-AU | А   | 64                | LQFP100  | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1CB-AU | В   | 64                | LQFP100  | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1CA-CU | А   | 64                | TFBGA100 | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1CB-CU | В   | 64                | TFBGA100 | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1BA-AU | А   | 64                | LQFP64   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1BB-AU | В   | 64                | LQFP64   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1BA-MU | А   | 64                | QFN 64   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1BB-MU | В   | 64                | QFN 64   | Green        | Industrial<br>-40°C to 85°C    |

### Table 14-1.

| Ordering Code  | MRL | Flash<br>(Kbytes) | Package  | Package Type | Temperature<br>Operating Range |

|----------------|-----|-------------------|----------|--------------|--------------------------------|

| ATSAM3N1AA-AU  | А   | 64                | LQFP48   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1AB-AU  | В   | 64                | LQFP48   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1AA-MU  | А   | 64                | QFN48    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N1AB-MU  | В   | 64                | QFN48    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N0CA-AU  | А   | 32                | LQFP100  | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N0CA-CU  | А   | 32                | TFBGA100 | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N0BA-AU  | А   | 32                | LQFP64   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N0BA-MU  | А   | 32                | QFN64    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N0AA-AU  | А   | 32                | LQFP48   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N0AA-MU  | А   | 32                | QFN48    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N00BA-AU | А   | 16                | LQFP64   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N00BA-MU | А   | 16                | QFN64    | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N00AA-AU | А   | 16                | LQFP48   | Green        | Industrial<br>-40°C to 85°C    |

| ATSAM3N00AA-MU | A   | 16                | QFN48    | Green        | Industrial<br>-40°C to 85°C    |

## **Revision History**

| Doc. Rev.<br>11011BS | Comments                                                                           | Change<br>Request Ref. |

|----------------------|------------------------------------------------------------------------------------|------------------------|

|                      | Overview:                                                                          |                        |

|                      | All mentions of 100-ball LFBGA changed into 100-ball TFBGA                         | 8044                   |

|                      | Section 8. "Product Mapping", Heading was 'Memories'. Changed to 'Product Mapping' | 7685                   |

|                      | Section 4.1.4 "100-ball TFBGA Pinout", whole pinout table updated                  | 7201                   |

|                      | Updated package dimensions in 'Features'                                           | 7965                   |

| Doc. Rev | Comments    | Change<br>Request Ref. |

|----------|-------------|------------------------|

| 11011AS  | First issue |                        |