Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                            |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                     |

| Number of I/O              | 37                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                               |

| Data Converters            | A/D 20x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 48-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 48-QFN (7x7)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd51g19a-mut  |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 24.4.                                                                                                                                                                                | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 491                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 24.5.                                                                                                                                                                                | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        |

| 24.6.                                                                                                                                                                                | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 493                                                                                                                                                    |

| 24.7.                                                                                                                                                                                | Programming Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 521                                                                                                                                                    |

| 24.8.                                                                                                                                                                                | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 526                                                                                                                                                    |

| 24.9.                                                                                                                                                                                | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 536                                                                                                                                                    |

|                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 055                                                                                                                                                    |

|                                                                                                                                                                                      | ICTRL – Nonvolatile Memory Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                        |

| 25.1.                                                                                                                                                                                | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 655                                                                                                                                                    |

|                                                                                                                                                                                      | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

|                                                                                                                                                                                      | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |

|                                                                                                                                                                                      | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

|                                                                                                                                                                                      | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        |

|                                                                                                                                                                                      | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

|                                                                                                                                                                                      | Register Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                        |

| 25.8.                                                                                                                                                                                | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 679                                                                                                                                                    |

| 26 ICM                                                                                                                                                                               | Integrity Check Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 700                                                                                                                                                    |

|                                                                                                                                                                                      | - Integrity Check Monitor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                        |

|                                                                                                                                                                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

|                                                                                                                                                                                      | Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                        |

|                                                                                                                                                                                      | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                        |

|                                                                                                                                                                                      | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

|                                                                                                                                                                                      | Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                        |

|                                                                                                                                                                                      | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

|                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                        |

|                                                                                                                                                                                      | Register Summary - ICM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

|                                                                                                                                                                                      | Register Summary - ICM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                        |

| 26.8.                                                                                                                                                                                | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 720                                                                                                                                                    |

| 26.8.<br>27. PAC                                                                                                                                                                     | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 720<br>741                                                                                                                                             |

| 26.8.<br><b>27. PAC</b><br>27.1.                                                                                                                                                     | Register Description<br>- Peripheral Access Controller<br>Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 720<br>741<br>741                                                                                                                                      |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.                                                                                                                                                   | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 720<br>741<br>741<br>741                                                                                                                               |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.                                                                                                                                          | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features<br>Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                   | 720<br>741<br>741<br>741<br>741                                                                                                                        |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.                                                                                                                                 | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features<br>Block Diagram<br>Product Dependencies                                                                                                                                                                                                                                                                                                                                                                                                           | 720<br>741<br>741<br>741<br>741<br>741                                                                                                                 |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.                                                                                                                        | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features<br>Block Diagram<br>Product Dependencies<br>Functional Description                                                                                                                                                                                                                                                                                                                                                                                 | 720<br>741<br>741<br>741<br>741<br>741<br>743                                                                                                          |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.                                                                                                               | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features<br>Block Diagram<br>Product Dependencies<br>Functional Description<br>Register Summary                                                                                                                                                                                                                                                                                                                                                             | 720<br>741<br>741<br>741<br>741<br>743<br>746                                                                                                          |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.                                                                                                               | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features<br>Block Diagram<br>Product Dependencies<br>Functional Description                                                                                                                                                                                                                                                                                                                                                                                 | 720<br>741<br>741<br>741<br>741<br>743<br>746                                                                                                          |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.                                                                                                      | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features<br>Block Diagram<br>Product Dependencies<br>Functional Description<br>Register Summary                                                                                                                                                                                                                                                                                                                                                             | 720<br>741<br>741<br>741<br>741<br>743<br>746<br>747                                                                                                   |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC                                                                                           | Register Description<br>- Peripheral Access Controller<br>Overview<br>Features<br>Block Diagram<br>Product Dependencies<br>Functional Description<br>Register Summary<br>Register Description                                                                                                                                                                                                                                                                                                                                     | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>746<br>780                                                                                            |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.                                                                                  | Register Description.   - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.                                                                                                                                                                                                                                                                                                  | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>746<br>747<br>780<br>780                                                                              |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.                                                                         | Register Description.   - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.   Overview.                                                                                                                                                                                                                                                                                      | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>746<br>747<br>780<br>780<br>780                                                                       |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.<br>28.3.                                                                | Register Description.   - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.   Overview.   Features.                                                                                                                                                                                                                                                                          | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>746<br>747<br>780<br>780<br>780<br>781                                                                |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.<br>28.3.<br>28.4.                                                       | Register Description.   - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.   Overview.   Features.   Block Diagram.                                                                                                                                                                                                                                                         | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>743<br>743<br>743<br>743<br>743<br>780<br>780<br>781<br>781                                           |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.<br>28.3.<br>28.4.<br>28.5.                                              | Register Description.   - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.   Overview.   Features.   Block Diagram.   Signal Description.                                                                                                                                                                                                                                   | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>746<br>747<br>780<br>780<br>780<br>781<br>781                                                         |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.<br>28.3.<br>28.4.<br>28.5.<br>28.6.                                     | Register Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>746<br>747<br>780<br>780<br>780<br>781<br>781<br>781<br>782                                           |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.<br>28.3.<br>28.4.<br>28.3.<br>28.4.<br>28.5.<br>28.6.<br>28.7.          | Register Description.   C - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.   Overview.   Features.   Block Diagram.   Signal Description.   Product Dependencies.   Functional Description.                                                                                                                                                                               | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>743<br>743<br>743<br>743<br>743<br>743<br>743<br>780<br>780<br>780<br>780<br>781<br>781<br>782<br>796 |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.<br>28.3.<br>28.4.<br>28.3.<br>28.4.<br>28.5.<br>28.6.<br>28.7.<br>28.8. | Register Description.   C - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.   Overview.   Features.   Block Diagram.   Signal Description.   Product Dependencies.   Functional Description.   Product Dependencies.   Functional Description.   Register Summary.   Register Summary.   Register Summary.   Register Summary.   Register Summary.   Register Description. | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>746<br>747<br>780<br>780<br>780<br>780<br>781<br>781<br>781<br>782<br>796<br>798                      |

| 26.8.<br>27. PAC<br>27.1.<br>27.2.<br>27.3.<br>27.4.<br>27.5.<br>27.6.<br>27.7.<br>28. OSC<br>28.1.<br>28.2.<br>28.3.<br>28.4.<br>28.5.<br>28.6.<br>28.7.<br>28.8.<br>28.8.<br>28.8. | Register Description.   C - Peripheral Access Controller.   Overview.   Features.   Block Diagram.   Product Dependencies.   Functional Description.   Register Summary.   Register Description.   CCTRL – Oscillators Controller.   Overview.   Features.   Block Diagram.   Signal Description.   Product Dependencies.   Functional Description.   CTRL – Oscillators Controller.   Overview.   Features.   Block Diagram.   Signal Description.   Product Dependencies.   Functional Description.   Register Summary.         | 720<br>741<br>741<br>741<br>741<br>743<br>743<br>743<br>746<br>747<br>780<br>780<br>780<br>780<br>780<br>781<br>781<br>781<br>782<br>796<br>798<br>798 |

# **Bit 0 – BOD33RDY** BOD33 Ready Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the BOD33 Ready Interrupt Enable bit, which disables the BOD33 Ready interrupt.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | The BOD33 Ready interrupt is disabled.                                                    |

| 1     | The BOD33 Ready interrupt is enabled, and an interrupt request will be generated when the |

|       | BOD33 Ready Interrupt flag is set.                                                        |

# RTC – Real-Time Counter

### 21.12.3 Event Control in Clock/Calendar mode (CTRLA.MODE=2)

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x04                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31    | 30       | 29  | 28   | 27      | 26  | 25    | 24       |

|--------|-------|----------|-----|------|---------|-----|-------|----------|

|        |       |          |     |      |         |     |       |          |

| Access |       |          |     |      |         |     |       |          |

| Reset  |       |          |     |      |         |     |       |          |

|        |       |          |     |      |         |     |       |          |

| Bit    | 23    | 22       | 21  | 20   | 19      | 18  | 17    | 16       |

|        |       |          |     |      |         |     |       | TAMPEVEI |

| Access |       |          |     |      |         |     |       | R/W      |

| Reset  |       |          |     |      |         |     |       | 0        |

|        |       |          |     |      |         |     |       |          |

| Bit    | 15    | 14       | 13  | 12   | 11      | 10  | 9     | 8        |

|        | OVFEO | TAMPEREO |     |      |         |     | ALARM | EOn[1:0] |

| Access | R/W   | R/W      |     |      |         |     | R/W   | R/W      |

| Reset  | 0     | 0        |     |      |         |     | 0     | 0        |

|        |       |          |     |      |         |     |       |          |

| Bit    | 7     | 6        | 5   | 4    | 3       | 2   | 1     | 0        |

|        |       |          |     | PERE | Dn[7:0] |     |       |          |

| Access | R/W   | R/W      | R/W | R/W  | R/W     | R/W | R/W   | R/W      |

| Reset  | 0     | 0        | 0   | 0    | 0       | 0   | 0     | 0        |

| Reset  | U     | U        | U   | U    | U       | 0   | U     | U        |

### Bit 16 – TAMPEVEI Tamper Event Input Enable

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Tamper event input is disabled, and incoming events will be ignored.                 |

| 1     | Tamper event input is enabled, and all incoming events will capture the CLOCK value. |

### Bit 15 - OVFEO Overflow Event Output Enable

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | Overflow event is disabled and will not be generated.               |

| 1     | Overflow event is enabled and will be generated for every overflow. |

### Bit 14 – TAMPEREO Tamper Event Output Enable

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | Tamper event output is disabled, and will not be generated                    |

| 1     | Tamper event output is enabled, and will be generated for every tamper input. |

### Bits 9:8 – ALARMEOn[1:0] Alarm n Event Output Enable [n = 1..0]

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 0     | Alarm n event is disabled and will not be generated.                    |

| 1     | Alarm n event is enabled and will be generated for every compare match. |

- The SRAM address of where the descriptor memory section is located must be written to the Description Base Address (BASEADDR) register

- The SRAM address of where the write-back section should be located must be written to the Write-Back Memory Base Address (WRBADDR) register

- Priority level x of the arbiter can be enabled by setting the Priority Level x Enable bit in the Control register (CTRL.LVLENx=1)

### **DMA** Channel Initialization

Before a DMA channel is enabled, the DMA channel and the corresponding first transfer descriptor must be configured, as outlined by the following steps:

- DMA Channel Configuration

- The channel number of the DMA channel to configure must be written to the Channel Control A register (CHCTRLA) register

- Trigger action must be selected by writing the Trigger Action bit field in the Channel Control A register (CHCTRLA.TRIGACT)

- Trigger source must be selected by writing the Trigger Source bit field in the Channel Control A register (CHCTRLA.TRIGSRC)

- Transfer Descriptor

- The size of each access of the data transfer bus must be selected by writing the Beat Size bit group in the Block Transfer Control register (BTCTRL.BEATSIZE)

- The transfer descriptor must be made valid by writing a one to the Valid bit in the Block Transfer Control register (BTCTRL.VALID)

- Number of beats in the block transfer must be selected by writing the Block Transfer Count (BTCNT) register

- Source address for the block transfer must be selected by writing the Block Transfer Source Address (SRCADDR) register

- Destination address for the block transfer must be selected by writing the Block Transfer Destination Address (DSTADDR) register

### **CRC** Calculation

If CRC calculation is needed, the CRC engine must be configured before it is enabled, as outlined by the following steps:

- The CRC input source must selected by writing the CRC Input Source bit group in the CRC Control register (CRCCTRL.CRCSRC)

- The type of CRC calculation must be selected by writing the CRC Polynomial Type bit group in the CRC Control register (CRCCTRL.CRCPOLY)

- If I/O is selected as input source, the beat size must be selected by writing the CRC Beat Size bit group in the CRC Control register (CRCCTRL.CRCBEATSIZE)

### **Register Properties**

The following DMAC registers are enable-protected, meaning that they can only be written when the DMAC is disabled (CTRL.DMAENABLE=0):

- Descriptor Base Memory Address register (BASEADDR)

- Write-Back Memory Base Address register (WRBADDR)

# **DMAC – Direct Memory Access Controller**

| Value | Name | Description    |

|-------|------|----------------|

| 0x2A  | CH10 | DMA channel 10 |

| 0x2B  | CH11 | DMA channel 11 |

| -     |      |                |

| 0x2C  | CH12 | DMA channel 12 |

| 0x2D  | CH13 | DMA channel 13 |

| 0x2E  | CH14 | DMA channel 14 |

| 0x2F  | CH15 | DMA channel 15 |

| 0x30  | CH16 | DMA channel 16 |

| 0x31  | CH17 | DMA channel 17 |

| 0x32  | CH18 | DMA channel 18 |

| 0x33  | CH19 | DMA channel 19 |

| 0x34  | CH20 | DMA channel 20 |

| 0x35  | CH21 | DMA channel 21 |

| 0x36  | CH22 | DMA channel 22 |

| 0x37  | CH23 | DMA channel 23 |

| 0x38  | CH24 | DMA channel 24 |

| 0x39  | CH25 | DMA channel 25 |

| 0x3A  | CH26 | DMA channel 26 |

| 0x3B  | CH27 | DMA channel 27 |

| 0x3C  | CH28 | DMA channel 28 |

| 0x3D  | CH29 | DMA channel 29 |

| 0x3E  | CH30 | DMA channel 30 |

| 0x3F  | CH31 | DMA channel 31 |

### Bits 3:2 – CRCPOLY[1:0] CRC Polynomial Type

These bits select the CRC polynomial type.

| Value   | Name  | Description        |

|---------|-------|--------------------|

| 0x0     | CRC16 | CRC-16 (CRC-CCITT) |

| 0x1     | CRC32 | CRC32 (IEEE 802.3) |

| 0x2-0x3 |       | Reserved           |

### Bits 1:0 - CRCBEATSIZE[1:0] CRC Beat Size

These bits define the size of the data transfer for each bus access when the CRC is used with I/O interface.

| Value | Name  | Description         |

|-------|-------|---------------------|

| 0x0   | BYTE  | 8-bit bus transfer  |

| 0x1   | HWORD | 16-bit bus transfer |

| 0x2   | WORD  | 32-bit bus transfer |

| 0x3   |       | Reserved            |

### 22.8.10 Interrupt Status

| Name:     | INTSTATUS  |

|-----------|------------|

| Offset:   | 0x24       |

| Reset:    | 0x00000000 |

| Property: | -          |

| Bit    | 31 | 30 | 29 | 28    | 27       | 26 | 25 | 24 |

|--------|----|----|----|-------|----------|----|----|----|

|        |    |    |    | CHINT | ז[31:24] |    |    |    |

| Access | R  | R  | R  | R     | R        | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 23 | 22 | 21 | 20    | 19       | 18 | 17 | 16 |

|        |    |    |    | CHINT | n[23:16] |    |    |    |

| Access | R  | R  | R  | R     | R        | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 15 | 14 | 13 | 12    | 11       | 10 | 9  | 8  |

|        |    |    |    | CHINT | n[15:8]  |    |    |    |

| Access | R  | R  | R  | R     | R        | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 7  | 6  | 5  | 4     | 3        | 2  | 1  | 0  |

|        |    |    |    | CHIN  | Γn[7:0]  |    |    |    |

| Access | R  | R  | R  | R     | R        | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

Bits 31:0 - CHINTn[31:0] Channel n Pending Interrupt [n=31..0]

This bit is set when Channel n has a pending interrupt/the interrupt request is received.

This bit is cleared when the corresponding Channel n interrupts are disabled or the interrupts sources are cleared.

|                 | Name:<br>Offset:<br>Reset:<br>Property: | DTF<br>0x148<br>0x00000000<br>Read-only |    |      |        |    |       |         |

|-----------------|-----------------------------------------|-----------------------------------------|----|------|--------|----|-------|---------|

| Bit             | 31                                      | 30                                      | 29 | 28   | 27     | 26 | 25    | 24      |

| Access<br>Reset |                                         |                                         |    |      |        |    |       |         |

| Bit             | 23                                      | 22                                      | 21 | 20   | 19     | 18 | 17    | 16      |

|                 |                                         |                                         |    |      |        |    | DEFT[ | [17:16] |

| Access          |                                         |                                         |    |      |        |    | R     | R       |

| Reset           |                                         |                                         |    |      |        |    | 0     | 0       |

| Bit             | 15                                      | 14                                      | 13 | 12   | 11     | 10 | 9     | 8       |

|                 |                                         |                                         |    | DEFT | [15:8] |    |       |         |

| Access          | R                                       | R                                       | R  | R    | R      | R  | R     | R       |

| Reset           | 0                                       | 0                                       | 0  | 0    | 0      | 0  | 0     | 0       |

|                 |                                         |                                         |    |      |        |    |       |         |

| Bit             | 7                                       | 6                                       | 5  | 4    | 3      | 2  | 1     | 0       |

|                 |                                         |                                         |    |      | Γ[7:0] |    |       |         |

| Access          |                                         | R                                       | R  | R    | R      | R  | R     | R       |

| Reset           | 0                                       | 0                                       | 0  | 0    | 0      | 0  | 0     | 0       |

### 24.9.56 GMAC Deferred Transmission Frames Register

### Bits 17:0 – DEFT[17:0] Deferred Transmission

This register counts the number of frames experiencing deferral due to carrier sense being active on their first attempt at transmission. Frames involved in any collision are not counted nor are frames that experienced a transmit underrun.

|        | Name:<br>Offset:<br>Reset:<br>Property: | IHCE<br>0x1A8<br>0x00000000<br>Read-only |    |      |        |    |    |    |

|--------|-----------------------------------------|------------------------------------------|----|------|--------|----|----|----|

| Bit    | 31                                      | 30                                       | 29 | 28   | 27     | 26 | 25 | 24 |

|        |                                         |                                          |    |      |        |    |    |    |

| Access |                                         |                                          |    |      |        |    |    |    |

| Reset  |                                         |                                          |    |      |        |    |    |    |

|        |                                         |                                          |    |      |        |    |    |    |

| Bit    | 23                                      | 22                                       | 21 | 20   | 19     | 18 | 17 | 16 |

|        |                                         |                                          |    |      |        |    |    |    |

| Access |                                         |                                          |    |      |        |    |    |    |

| Reset  |                                         |                                          |    |      |        |    |    |    |

| Bit    | 15                                      | 14                                       | 13 | 12   | 11     | 10 | 9  | 8  |

| Dit    | 15                                      | 14                                       | 15 | 12   | 11     | 10 | 5  | 0  |

| Access |                                         |                                          |    |      |        |    |    |    |

| Reset  |                                         |                                          |    |      |        |    |    |    |

| Reset  |                                         |                                          |    |      |        |    |    |    |

| Bit    | 7                                       | 6                                        | 5  | 4    | 3      | 2  | 1  | 0  |

|        |                                         |                                          |    | HCKE | R[7:0] |    |    |    |

| Access | R                                       | R                                        | R  | R    | R      | R  | R  | R  |

| Reset  |                                         | 0                                        | 0  | 0    | 0      | 0  | 0  | 0  |

|        |                                         |                                          |    |      |        |    |    |    |

### 24.9.80 GMAC IP Header Checksum Errors Register

### Bits 7:0 – HCKER[7:0] IP Header Checksum Errors

This register counts the number of frames discarded due to an incorrect IP header checksum, but are between 64 and 1518 Bytes (1536 Bytes if GMAC\_NCFGR.MAXFS=1) and do not have a CRC error, an alignment error, nor a symbol error.

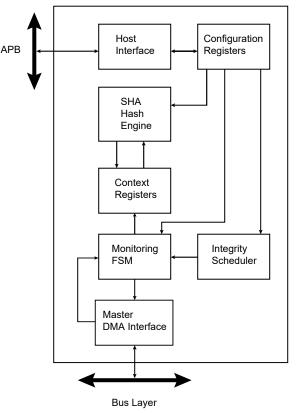

# ICM - Integrity Check Monitor

# 26.3 Block Diagram

Figure 26-1. Integrity Check Monitor Block Diagram

# 26.4 Signal Description

Not applicable.

### 26.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

### 26.5.1 Power Management

The ICM will run only when the source clocks are running, i.e. when the CPU is in Active mode.

### 26.5.2 Clocks

The ICM bus clocks (CLK\_ICM\_AHB and CLK\_ICM\_APB) can be enabled and disabled in the Main Clock module (MCLK) by writing the respective bit in the mask registers (MCLK.AHBMASK.ICM and MCLK.APBCMASK.ICM).

The default states of CLK\_ICM\_AHB and CLK\_ICM\_APB are given by the reset values of the respective mask registers.

### **Related Links**

15.7 Register Summary

ICM - Integrity Check Monitor

### 26.6.3.1 Region Descriptor Structure Overview

| Offset | Name   | Bit Pos. |              |              |           |              |         |       |       |  |  |

|--------|--------|----------|--------------|--------------|-----------|--------------|---------|-------|-------|--|--|

|        |        | 7:0      |              |              |           | RADDR[7:0]   |         |       |       |  |  |

| 000    |        | 15:8     |              |              |           | RADDR[15:8]  | ]       |       |       |  |  |

| 0x00   | RADDR0 | 23:16    | RADDR[23:16] |              |           |              |         |       |       |  |  |

|        |        | 31:24    |              | RADDR[31:24] |           |              |         |       |       |  |  |

|        |        | 7:0      | WCIEN        | BEIEN        | DMIEN     | RHIEN        | EOM     | WRAP  | CDWBN |  |  |

|        | 50500  | 15:8     |              |              | ALGO[2:0] |              | PROCDLY | SUIEN | ECIEN |  |  |

| 0x04   | RCFG0  | 23:16    |              |              |           |              |         |       |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 7:0      |              |              |           | TRSIZE[7:0]  |         |       |       |  |  |

|        |        | 15:8     |              |              |           | TRSIZE[15:8] | ]       |       |       |  |  |

| 0x08   | RCTRL0 | 23:16    |              |              |           |              |         |       |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 7:0      |              |              |           | RADDR[7:0]   |         |       |       |  |  |

|        |        | 15:8     |              |              |           | RADDR[15:8]  | ]       |       |       |  |  |

| 0x0C   | RADDR1 | 23:16    |              |              |           | RADDR[23:16  | 6]      |       |       |  |  |

|        |        | 31:24    |              |              |           | RADDR[31:24  | l]      |       |       |  |  |

|        |        | 7:0      |              |              |           |              |         |       |       |  |  |

|        |        | 15:8     |              |              |           |              |         |       |       |  |  |

| 0x0C   | RNEXT0 | 23:16    |              |              |           |              |         |       |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 7:0      | WCIEN        | BEIEN        | DMIEN     | RHIEN        | EOM     | WRAP  | CDWBN |  |  |

|        |        | 15:8     |              |              | ALGO[2:0] |              | PROCDLY | SUIEN | ECIEN |  |  |

| 0x10   | RCFG1  | 23:16    |              |              |           |              |         |       |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 7:0      |              |              |           | TRSIZE[7:0]  |         |       |       |  |  |

|        |        | 15:8     |              |              |           | TRSIZE[15:8] |         |       |       |  |  |

| 0x14   | RCTRL1 | 23:16    |              |              |           |              |         |       |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 7:0      |              |              |           | RADDR[7:0]   |         |       |       |  |  |

|        |        | 15:8     |              |              |           | RADDR[15:8]  |         |       |       |  |  |

| 0x18   | RADDR2 | 23:16    |              |              |           | RADDR[23:16  |         |       |       |  |  |

|        |        | 31:24    |              |              |           | RADDR[31:24  |         |       |       |  |  |

|        |        | 7:0      |              |              |           |              |         |       |       |  |  |

|        |        | 15:8     |              |              |           |              |         |       |       |  |  |

| 0x18   | RNEXT1 | 23:16    |              |              |           |              |         |       |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 7:0      | WCIEN        | BEIEN        | DMIEN     | RHIEN        | EOM     | WRAP  | CDWBN |  |  |

|        |        | 15:8     | WOILIT       | BEIER        | ALGO[2:0] |              | PROCDLY | SUIEN | ECIEN |  |  |

| 0x1C   | RCFG2  | 23:16    |              |              |           |              | TROODET | SOLI  |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 7:0      |              |              |           | TRSIZE[7:0]  |         |       |       |  |  |

|        |        | 15:8     |              |              |           | TRSIZE[15:8] |         |       |       |  |  |

| 0x20   | RCTRL2 | 23:16    |              |              |           |              | ]       |       |       |  |  |

|        |        | 31:24    |              |              |           |              |         |       |       |  |  |

|        |        | 31.24    |              |              |           |              |         |       |       |  |  |

# 28. OSCCTRL – Oscillators Controller

### 28.1 Overview

The Oscillators Controller (OSCCTRL) provides a user interface to the XOSCn, DFLL48M, and two FDPLL200M.

Through the interface registers, it is possible to enable, disable, calibrate, and monitor the oscillators.

The status of all oscillators are collected in the Status register (STATUS). They can additionally trigger interrupts upon status changes via the INTENSET, INTENCLR, and INTFLAG registers.

## 28.2 Features

- Digital Frequency-Locked Loop (DFLL48M)

- Internal oscillator with no external components

- 48 MHz output frequency

- Operates stand-alone as a high-frequency programmable oscillator in Open Loop mode

- Operates as an accurate frequency multiplier against a known frequency in Closed Loop mode

- Two 8-48 MHz Crystal Oscillators (XOSCn)

- Tunable gain control

- Programmable start-up time

- Crystal or external input clock on XIN I/O

- Clock failure detection with safe clock switch

- Clock failure event output

- Two Digital Phase-Locked Loop (DPLLn)

- 96 MHz to 200 MHz output frequency from a 32 kHz to 3.2 MHz reference clock

- Two DPLLs, each with four selectable reference clocks

- Adjustable digital filter for jitter optimization

- Adjustable DCO filter for a 4-stages differential ring oscillator

- Fractional part used to achieve 1/32th of reference clock step

- Embedded test mode controller

# 31.6 Register Summary

| Offset | Name        | Bit Pos. |           |           |           |           |           |                |           |           |

|--------|-------------|----------|-----------|-----------|-----------|-----------|-----------|----------------|-----------|-----------|

| 0x00   | CTRLA       | 7:0      |           |           |           |           |           |                |           | SWRST     |

| 0x01   |             |          |           |           |           |           |           |                |           |           |

|        | Reserved    |          |           |           |           |           |           |                |           |           |

| 0x03   |             |          |           |           |           |           |           |                |           |           |

|        |             | 7:0      |           |           |           | CHANN     | NEL[7:0]  |                |           |           |

| 0x04   | SWEVT       | 15:8     |           |           |           | CHANN     | EL[15:8]  |                |           |           |

| 0X04   | SWEVI       | 23:16    |           |           |           | CHANNI    | EL[23:16] |                |           |           |

|        |             | 31:24    |           |           |           | CHANNI    | EL[31:24] |                |           |           |

| 0x08   | PRICTRL     | 7:0      | RREN      |           |           |           |           | PRI[4:0]       |           |           |

| 0x09   |             |          |           |           |           |           |           |                |           |           |

|        | Reserved    |          |           |           |           |           |           |                |           |           |

| 0x0F   |             |          |           |           |           |           |           |                |           |           |

| 0x10   | INTPEND     | 7:0      |           |           |           |           |           | ID[4:0]        |           |           |

| 0,110  |             | 15:8     | BUSY      | READY     |           |           |           |                | EVD       | OVR       |

| 0x12   |             |          |           |           |           |           |           |                |           |           |

|        | Reserved    |          |           |           |           |           |           |                |           |           |

| 0x13   |             |          |           |           |           |           |           |                |           |           |

|        |             | 7:0      | CHINT7    | CHINT6    | CHINT5    | CHINT4    | CHINT3    | CHINT2         | CHINT1    | CHINT0    |

| 0x14   | INTSTATUS   | 15:8     |           |           |           |           | CHINT11   | CHINT10        | CHINT9    | CHINT8    |

|        |             | 23:16    |           |           |           |           |           |                |           |           |

|        |             | 31:24    |           |           |           |           |           |                |           |           |

|        |             | 7:0      | BUSYCHx7  | BUSYCHx6  | BUSYCHx5  | BUSYCHx4  | BUSYCHx3  | BUSYCHx2       | BUSYCHx1  | BUSYCHx0  |

| 0x18   | BUSYCH      | 15:8     |           |           |           |           | BUSYCHx11 | BUSYCHx10      | BUSYCHx9  | BUSYCHx8  |

|        |             | 23:16    |           |           |           |           |           |                |           |           |

|        |             | 31:24    |           |           |           |           |           |                |           |           |

|        |             | 7:0      | READYUSR7 | READYUSR6 | READYUSR5 | READYUSR4 | READYUSR3 | READYUSR2      | READYUSR1 | READYUSR0 |

| 0x1C   | READYUSR    | 15:8     |           |           |           |           | READYUSR1 | READYUSR1<br>0 | READYUSR9 | READYUSR8 |

|        |             | 23:16    |           |           |           |           |           |                |           |           |

|        |             | 31:24    |           |           |           |           |           |                |           |           |

|        |             | 7:0      |           |           |           | EVGE      | EN[7:0]   |                |           |           |

| 000    |             | 15:8     | ONDEMAND  | RUNSTDBY  |           |           | EDGS      | EL[1:0]        | PATH      | H[1:0]    |

| 0x20   | CHANNEL0    | 23:16    |           |           |           |           |           |                |           |           |

|        |             | 31:24    |           |           |           |           |           |                |           |           |

| 0x24   | CHINTENCLR0 | 7:0      |           |           |           |           |           |                | EVD       | OVR       |

| 0x25   | CHINTENSET0 | 7:0      |           |           |           |           |           |                | EVD       | OVR       |

| 0x26   | CHINTFLAG0  | 7:0      |           |           |           |           |           |                | EVD       | OVR       |

| 0x27   | CHSTATUS0   | 7:0      |           |           |           |           |           |                | BUSYCH    | RDYUSR    |

|        |             | 7:0      |           |           |           | EVGE      | EN[7:0]   |                |           |           |

| 0x28   | CHANNEL1    | 15:8     | ONDEMAND  | RUNSTDBY  |           |           | EDGS      | EL[1:0]        | PATH      | H[1:0]    |

| 0720   |             | 23:16    |           |           |           |           |           |                |           |           |

|        |             | 31:24    |           |           |           |           |           |                |           |           |

| 0x2C   | CHINTENCLR1 | 7:0      |           |           |           |           |           |                | EVD       | OVR       |

# PORT - I/O Pin Controller

| on.                      |

|--------------------------|

| ted to an internal pull- |

|                          |

- 1. Abort the current transfer.

- 2. Flush the transmit buffer.

- 3. Disable transmitter (CTRLB.TXEN=0)

- This is done after a synchronization delay. The CTRLB Synchronization Busy bit (SYNCBUSY.CTRLB) will be set until this is complete.

- After disabling, the TxD pin will be tri-stated.

- 4. Set the Collision Detected bit (STATUS.COLL) along with the Error interrupt flag (INTFLAG.ERROR).

- 5. Set the Transmit Complete interrupt flag (INTFLAG.TXC), since the transmit buffer no longer contains data.

After a collision, software must manually enable the transmitter again before continuing, after assuring that the CTRLB Synchronization Busy bit (SYNCBUSY.CTRLB) is not set.

### 34.6.3.9 Loop-Back Mode

For loop-back mode, configure the Receive Data Pinout (CTRLA.RXPO) and Transmit Data Pinout (CTRLA.TXPO) to use the same data pins for transmit and receive. The loop-back is through the pad, so the signal is also available externally.

### 34.6.3.10 Start-of-Frame Detection

The USART start-of-frame detector can wake up the CPU when it detects a start bit. In standby sleep mode, the internal fast startup oscillator must be selected as the GCLK\_SERCOMx\_CORE source.

When a 1-to-0 transition is detected on RxD, the 8MHz Internal Oscillator is powered up and the USART clock is enabled. After startup, the rest of the data frame can be received, provided that the baud rate is slow enough in relation to the fast startup internal oscillator start-up time. Refer to *Electrical Characteristics* for details. The start-up time of this oscillator varies with supply voltage and temperature.

The USART start-of-frame detection works both in asynchronous and synchronous modes. It is enabled by writing '1' to the Start of Frame Detection Enable bit in the Control B register (CTRLB.SFDE).

If the Receive Start Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.RXS) is set, the Receive Start interrupt is generated immediately when a start is detected.

When using start-of-frame detection without the Receive Start interrupt, start detection will force the 8MHz Internal Oscillator and USART clock active while the frame is being received. In this case, the CPU will not wake up until the Receive Complete interrupt is generated.

#### 34.6.3.11 Sample Adjustment

In asynchronous mode (CTRLA.CMODE=0), three samples in the middle are used to determine the value based on majority voting. The three samples used for voting can be selected using the Sample Adjustment bit field in Control A register (CTRLA.SAMPA). When CTRLA.SAMPA=0, samples 7-8-9 are used for 16x oversampling, and samples 3-4-5 are used for 8x oversampling.

#### 34.6.3.12 32-bit Extension

For better system bus utilization, 32-bit data receive and transmit can be enabled separately by writing to the Data 32-bit bit field in the Control C register (CTRLC.DATA32B). When enabled, writes and/or reads to the DATA register are 32 bit in size.

If frames are not multiples of 4 Bytes, the length counter (LENGTH.LEN) and length enable (LENGTH.LENEN) must be configured before data transfer begins, LENGTH.LEN must be enabled only when CTRLC.DATA32B is enabled.