Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | ARM® Cortex®-M4F                                                            |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                     |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 256KB (256K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 128K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd51j18a-aut  |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **CMCC - Cortex M Cache Controller**

### 11.10.7 Cache Maintenance 1

|        | Name:<br>Offset:<br>Reset:<br>Property: | MAINT1<br>0x24<br>0x00000000<br>- |       |    |    |    |        |    |

|--------|-----------------------------------------|-----------------------------------|-------|----|----|----|--------|----|

| Bit    | 31                                      | 30                                | 29    | 28 | 27 | 26 | 25     | 24 |

|        |                                         | WAY                               | [3:0] |    |    |    |        |    |

| Access | W                                       | W                                 | W     | W  |    |    |        |    |

| Reset  | 0                                       | 0                                 | 0     | 0  |    |    |        |    |

|        |                                         |                                   |       |    |    |    |        |    |

| Bit    | 23                                      | 22                                | 21    | 20 | 19 | 18 | 17     | 16 |

|        |                                         |                                   |       |    |    |    |        |    |

| Access |                                         |                                   |       |    |    |    |        |    |

| Reset  |                                         |                                   |       |    |    |    |        |    |

|        |                                         |                                   |       |    |    |    |        | _  |

| Bit    | 15                                      | 14                                | 13    | 12 | 11 | 10 | 9      | 8  |

|        |                                         |                                   |       |    |    |    | X[7:4] |    |

| Access |                                         |                                   |       |    | W  | W  | W      | W  |

| Reset  |                                         |                                   |       |    | 0  | 0  | 0      | 0  |

|        |                                         |                                   |       |    |    |    |        |    |

| Bit    | 7                                       | 6                                 | 5     | 4  | 3  | 2  | 1      | 0  |

|        |                                         | INDEX[3:0]                        |       |    |    |    |        |    |

| Access | W                                       | W                                 | W     | W  |    |    |        |    |

| Reset  | 0                                       | 0                                 | 0     | 0  |    |    |        |    |

### Bits 31:28 - WAY[3:0] Invalidate Way

| Value                     | Name | Description                               |

|---------------------------|------|-------------------------------------------|

| 0x0                       | WAY0 | Way 0 is selection for index invalidation |

| 0x1                       | WAY1 | Way 1 is selection for index invalidation |

| 0x2                       | WAY2 | Way 2 is selection for index invalidation |

| 0x3                       | WAY3 | Way 3 is selection for index invalidation |

| $0 \times 4 - 0 \times F$ |      | Reserved                                  |

### Bits 11:4 – INDEX[7:0] Invalidate Index

This field selects the index value for invalidation

### Bit 5 – B12SRDY BOD12 Synchronization Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the BOD12 Synchronization Ready Interrupt Enable bit, which disables the BOD12 Synchronization Ready interrupt.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The BOD12 Synchronization Ready interrupt is disabled.                                 |

| 1     | The BOD12 Synchronization Ready interrupt is enabled, and an interrupt request will be |

|       | generated when the BOD12 Synchronization Ready Interrupt flag is set.                  |

### Bit 4 – BOD12DET BOD12 Detection Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the BOD12 Detection Interrupt Enable bit, which disables the BOD12 Detection interrupt.

| Value | Description                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD12 Detection interrupt is disabled.                                                                                           |

| 1     | The BOD12 Detection interrupt is enabled, and an interrupt request will be generated when the BOD12 Detection Interrupt flag is set. |

### **Bit 3 – BOD12RDY** BOD12 Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the BOD12 Ready Interrupt Enable bit, which disables the BOD12 Ready interrupt.

| Value | Description                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD12 Ready interrupt is disabled.                                                                                      |

| 1     | The BOD12 Ready interrupt is enabled and an interrupt request will be generated when the BOD12 Ready Interrupt flag is set. |

### **Bit 2 – B33SRDY** BOD33 Synchronization Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the BOD33 Synchronization Ready Interrupt Enable bit, which disables the BOD33 Synchronization Ready interrupt.

| Value | Description                                                                                                                                                  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD33 Synchronization Ready interrupt is disabled.                                                                                                       |

| 1     | The BOD33 Synchronization Ready interrupt is enabled, and an interrupt request will be generated when the BOD33 Synchronization Ready Interrupt flag is set. |

### Bit 1 – BOD33DET BOD33 Detection Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the BOD33 Detection Interrupt Enable bit, which disables the BOD33 Detection interrupt.

| Value | Description                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The BOD33 Detection interrupt is disabled.                                                                                           |

| 1     | The BOD33 Detection interrupt is enabled, and an interrupt request will be generated when the BOD33 Detection Interrupt flag is set. |

The action of each tamper channel is configured using the Input n Action bits in the Tamper Control register (TAMPCTRL.INnACT):

- Off: Detection for tamper channel n is disabled.

- Wake: A transition on INn input (tamper channel n) matching TAMPCTRL.TAMPLVLn will be detected and the tamper interrupt flag (INTFLAG.TAMPER) will be set. The RTC value will not be captured in the TIMESTAMP register.

- Capture: A transition on INn input (tamper channel n) matching TAMPCTRL.TAMPLVLn will be detected and the tamper interrupt flag (INTFLAG.TAMPER) will be set. The RTC value will be captured in the TIMESTAMP register.

- Active Layer Protection: A mismatch of an internal RTC signal routed between INn and OUTn pins will be detected and the tamper interrupt flag (INTFLAG.TAMPER) will be set. The RTC value will be captured in the TIMESTAMP register.

In order to determine which tamper source caused a tamper event, the Tamper ID register (TAMPID) provides the detection status of each tamper channel. These bits remain active until cleared by software.

A single interrupt request (TAMPER) is available for all tamper channels.

The RTC also supports an input event (TAMPEVT) for generating a tamper condition within the Event System. The tamper input event is enabled by the Tamper Input Event Enable bit in the Event Control register (EVCTRL.TAMPEVEI).

Up to four polarity external inputs (INn) can be used for tamper detection. The polarity for each input is selected with the Tamper Level bits in the Tamper Control register (TAMPCTRL.TAMPLVLn).

Separate debouncers are embedded for each external input. The debouncer for each input is enabled/ disabled with the Debounce Enable bits in the Tamper Control register (TAMPCTRL.DEBNCn). The debouncer configuration is fixed for all inputs as set by the Control B register (CTRLB). The debouncing period duration is configurable using the Debounce Frequency field in the Control B register (CTRLB.DEBF). The period is set for all debouncers (i.e., the duration cannot be adjusted separately for each debouncer).

When TAMPCTRL.DEBNCn = 0, INn is detected asynchronously. See Figure 21-6 for an example.

When TAMPCTRL.DEBNCn = 1, the detection time depends on whether the debouncer operates synchronously or asynchronously, and whether majority detection is enabled or not. Refer to the table below for more details. Synchronous versus asynchronous stability debouncing is configured by the Debounce Asynchronous Enable bit in the Control B register (CTRLB.DEBASYNC):

- Synchronous (CTRLB.DEBASYNC = 0): INn is synchronized in two CLK\_RTC periods and then must remain stable for four CLK\_RTC\_DEB periods before a valid detection occurs. See Figure 21-7 for an example.

- Asynchronous (CTRLB.DEBASYNC = 1): The first edge on INn is detected. Further detection is blanked until INn remains stable for four CLK\_RTC\_DEB periods. See Figure 21-8 for an example.

Majority debouncing is configured by the Debounce Majority Enable bit in the Control B register (CTRLB.DEBMAJ). INn must be valid for two out of three CLK\_RTC\_DEB periods. See Figure 21-9 for an example.

## DMAC – Direct Memory Access Controller

| Index       | Instance | Channel | Presentation                             |

|-------------|----------|---------|------------------------------------------|

| 0x0F        | SERCOM5  | тх      | Index of DMA TX trigger                  |

| 0x10        | SERCOM6  | RX      | Index of DMA RX trigger                  |

| 0x11        | SERCOM6  | ТХ      | Index of DMA TX trigger                  |

| 0x12        | SERCOM7  | RX      | Index of DMA RX trigger                  |

| 0x13        | SERCOM7  | ТХ      | Index of DMA TX trigger                  |

| 0x14        | CAN0     | DEBUG   | DMA CAN Debug Req                        |

| 0x15        | CAN1     | DEBUG   | DMA CAN Debug Req                        |

| 0x16        | TCC0     | OVF     | DMA overflow/underflow/retrigger trigger |

| 0x1C - 0x17 | TCC0     | MC      | Indexes of DMA Match/Compare triggers    |

| 0x1D        | TCC1     | OVF     | DMA overflow/underflow/retrigger trigger |

| 0x21- 0x1E  | TCC1     | MC      | Indexes of DMA Match/Compare triggers    |

| 0x22        | TCC2     | OVF     | DMA overflow/underflow/retrigger trigger |

| 0x25 - 0x23 | TCC2     | MC      | Indexes of DMA Match/Compare triggers    |

| 0x26        | TCC3     | OVF     | DMA overflow/underflow/retrigger trigger |

| 0x28 - 0x27 | TCC3     | MC      | Indexes of DMA Match/Compare triggers    |

| 0x29        | TCC4     | OVF     | DMA overflow/underflow/retrigger trigger |

| 0x2B - 0x2A | TCC4     | MC      | Indexes of DMA Match/Compare triggers    |

| 0x2C        | TC0      | OVF     | Indexes of DMA Overflow trigger          |

| 0x2E - 0x2D | TC0      | MC      | Indexes of DMA Match/Compare triggers    |

| 0x2F        | TC1      | OVF     | Indexes of DMA Overflow trigger          |

| 0x31 - 0x30 | TC1      | MC      | Indexes of DMA Match/Compare triggers    |

| 0x32        | TC2      | OVF     | Indexes of DMA Overflow trigger          |

| 0x34 - 0x33 | TC2      | MC      | Indexes of DMA Match/Compare triggers    |

| 0x35        | TC3      | OVF     | Indexes of DMA Overflow trigger          |

| 0x37 - 0x36 | TC3      | MC      | Indexes of DMA Match/Compare triggers    |

| 0x38        | TC4      | OVF     | Indexes of DMA Overflow trigger          |

| 0x3A - 0x39 | TC4      | MC      | Indexes of DMA Match/Compare triggers    |

| 0x3B        | TC5      | OVF     | Indexes of DMA Overflow trigger          |

| 0x3D:0x3C   | TC5      | MC      | Indexes of DMA Match/Compare triggers    |

| 0x3E        | TC6      | OVF     | Indexes of DMA Overflow trigger          |

| 0x40 - 0x3F | TC6      | MC      | Indexes of DMA Match/Compare triggers    |

| 0x41        | TC7      | OVF     | Indexes of DMA Overflow trigger          |

This bit will always read '0'.

### Bit 4 – MPE Management Port Enable

Writing a '1' to this bit enables the Management Port.

Writing a '0' to this bit disables the Management Port, and forces MDIO to high impedance state and MDC to low impedance.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Management Port is disabled |

| 1     | Management Port is enabled  |

### Bit 3 – TXEN Transmit Enable

Writing a '1' to this bit enables the GMAC transmitter to send data.

Writing a '0' to this bit stops transmission immediately, the transmit pipeline and control registers is cleared, and the Transmit Queue Pointer Register will be set to point to the start of the transmit descriptor list.

| Value | Description          |

|-------|----------------------|

| 0     | Transmit is disabled |

| 1     | Transmit is enabled  |

### Bit 2 – RXEN Receive Enable

Writing a '1' to this bit enables the GMAC to receive data.

Writing a '0' to this bit stops frame reception immediately, and the receive pipeline is cleared. The Receive Queue Pointer Register is not affected.

| Value | Description         |

|-------|---------------------|

| 0     | Receive is disabled |

| 1     | Receive is enabled  |

### Bit 1 – LBL Loop Back Local

Writing '1' to this bit connects GTX to GRX, GTXEN to GRXDV, and forces full duplex mode.

GRXCK and GTXCK may malfunction as the GMAC is switched into and out of internal loop back. It is important that receive and transmit circuits have already been disabled when making the switch into and out of internal loop back.

| Value | e Description               |  |  |

|-------|-----------------------------|--|--|

| 0     | Loop back local is disabled |  |  |

| 1     | Loop back local is enabled  |  |  |

| Value   | Description           |

|---------|-----------------------|

| 0x00    | Reserved              |

| 0x01-0x | 1255 x 64 byte buffer |

| FF      |                       |

**Bit 11 – TXCOEN** Transmitter Checksum Generation Offload Enable Transmitter IP, TCP and UDP checksum generation offload enable.

| Value | Description                                                                         |  |  |  |  |

|-------|-------------------------------------------------------------------------------------|--|--|--|--|

| 0     | Frame data is unaffected.                                                           |  |  |  |  |

| 1     | The transmitter checksum generation engine calculates and substitutes checksums for |  |  |  |  |

|       | transmit frames.                                                                    |  |  |  |  |

### Bit 10 – TXPBMS Transmitter Packet Buffer Memory Size Select

When written to zero, the amount of memory used for the transmit packet buffer is reduced by 50%. This reduces the amount of memory used by the GMAC.

It is important to write this bit to '1' if the full configured physical memory is available. The value in parentheses represents the size that would result for the default maximum configured memory size of 4KBytes.

| Value                                               | Description                               |  |

|-----------------------------------------------------|-------------------------------------------|--|

| 0                                                   | Top address bits not used. (2KByte used.) |  |

| 1 Full configured addressable space (4KBytes) used. |                                           |  |

### Bits 9:8 - RXBMS[1:0] Receiver Packet Buffer Memory Size Select

The default receive packet buffer size is FULL=RECEIVE\_BUFFER\_SIZE Kbytes. The table below shows how to configure this memory to FULL, HALF, QUARTER or EIGHTH of the default size.

| Value | Name    | Description                              |

|-------|---------|------------------------------------------|

| 0     | EIGHTH  | RECEIVE_BUFFER_SIZE/8 Kbyte Memory Size  |

| 1     | QUARTER | RECEIVE_BUFFER_SIZE/4 Kbytes Memory Size |

| 2     | HALF    | RECEIVE_BUFFER_SIZE/2 Kbytes Memory Size |

| 3     | FULL    | RECEIVE_BUFFER_SIZE Kbytes Memory Size   |

Bit 7 – ESPA Endian Swap Mode Enable for Packet Data Accesses

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | Little endian mode for AHB transfers selected. |

| 1     | Big endian mode for AHB transfers selected.    |

### **Bit 6 – ESMA** Endian Swap Mode Enable for Management Descriptor Accesses

| Val | ue | Description                                    |

|-----|----|------------------------------------------------|

| 0   |    | Little endian mode for AHB transfers selected. |

| 1   |    | Big endian mode for AHB transfers selected.    |

### Bits 4:0 – FBLDO[4:0] Fixed Burst Length for DMA Data Operations

Selects the burst length to attempt to use on the AHB when transferring frame data. Not used for DMA management operations and only used where space and data size allow. Otherwise SINGLE type AHB transfers are used.

|        | Name:<br>Offset:<br>Reset:<br>Property: | TPSF<br>0x040<br>0x00000FFF<br>- |     |       |     |     |          |     |

|--------|-----------------------------------------|----------------------------------|-----|-------|-----|-----|----------|-----|

| Bit    | 31                                      | 30                               | 29  | 28    | 27  | 26  | 25       | 24  |

|        | ENTXP                                   |                                  |     |       |     |     |          |     |

| Access | R/W                                     |                                  |     |       |     |     |          |     |

| Reset  | 0                                       |                                  |     |       |     |     |          |     |

|        |                                         |                                  |     |       |     |     |          |     |

| Bit    | 23                                      | 22                               | 21  | 20    | 19  | 18  | 17       | 16  |

|        |                                         |                                  |     |       |     |     |          |     |

| Access |                                         |                                  |     |       |     |     |          |     |

| Reset  |                                         |                                  |     |       |     |     |          |     |

| Dit    | 45                                      |                                  | 10  | 10    | 44  | 10  | 0        | 0   |

| Bit    | 15                                      | 14                               | 13  | 12    | 11  | 10  | 9        | 8   |

|        |                                         |                                  |     |       |     |     | DR[11:8] |     |

| Access |                                         |                                  |     |       | R/W | R/W | R/W      | R/W |

| Reset  |                                         |                                  |     |       | 1   | 1   | 1        | 1   |

|        |                                         |                                  |     |       |     |     |          |     |

| Bit    | 7                                       | 6                                | 5   | 4     | 3   | 2   | 1        | 0   |

|        |                                         |                                  |     | TPB1A |     |     |          |     |

| Access | R/W                                     | R/W                              | R/W | R/W   | R/W | R/W | R/W      | R/W |

| Reset  | 1                                       | 1                                | 1   | 1     | 1   | 1   | 1        | 1   |

### 24.9.17 GMAC TX Partial Store and Forward Register

Bit 31 – ENTXP Enable TX Partial Store and Forward Operation

**Bits 11:0 – TPB1ADR[11:0]** Transmit Partial Store and Forward Address Watermark value.

PAC - Peripheral Access Controller

## 27.6 Register Summary

| Offset           | Name       | Bit Pos. |       |                |                |           |         |          |          |          |

|------------------|------------|----------|-------|----------------|----------------|-----------|---------|----------|----------|----------|

|                  |            | 7:0      |       |                |                | PERI      | D[7:0]  |          | I        |          |

|                  |            | 15:8     |       |                |                | PERID     | )[15:8] |          |          |          |

| 0x00             | WRCTRL     | 23:16    |       |                |                | KEY       | [7:0]   |          |          |          |

|                  |            | 31:24    |       |                |                |           |         |          |          |          |

| 0x04             | EVCTRL     | 7:0      |       |                |                |           |         |          |          | ERREO    |

| 0x05             |            |          |       |                |                |           |         |          |          |          |

|                  | Reserved   |          |       |                |                |           |         |          |          |          |

| 0x07             |            |          |       |                |                |           |         |          |          |          |

| 0x08             | INTENCLR   | 7:0      |       |                |                |           |         |          |          | ERR      |

| 0x09             | INTENSET   | 7:0      |       |                |                |           |         |          |          | ERR      |

| 0x0A<br><br>0x0F | Reserved   |          |       |                |                |           |         |          |          |          |

|                  |            | 7:0      | HPB0  | RAMDMACIC<br>M | RAMDMAWR       | RAMPPPDSU | RAMCM4S | NVMCTRL2 | NVMCTRL1 | NVMCTRL0 |

| 0x10             | INTFLAGAHB | 15:8     |       | QSPI           | SDHC1          | SDHC0     | PUKCC   | HPB3     | HPB2     | HPB1     |

|                  |            | 23:16    |       |                |                |           |         |          |          |          |

|                  |            | 31:24    |       |                |                |           |         |          |          |          |

|                  |            | 7:0      | GCLK  | SUPC           | OSC32KCTR<br>L | OSCCTRL   | RSTC    | MCLK     | РМ       | PAC      |

| 0x14             | INTFLAGA   | 15:8     | TC1   | TC0            | SERCOM1        | SERCOM0   | FREQM   | EIC      | RTC      | WDT      |

|                  |            | 23:16    |       |                |                |           |         |          |          |          |

|                  |            | 31:24    |       |                |                |           |         |          |          |          |

|                  |            | 7:0      | EVSYS |                | DMAC           | PORT      | CMCC    | NVMCTRL  | DSU      | USB      |

| 0x18             | INTFLAGB   | 15:8     |       | TC3            | TC2            | TCC1      | TCC0    | SERCOM3  | SERCOM2  |          |

| 0210             | INTELAGE   | 23:16    |       |                |                |           |         |          |          | RAMECC   |

|                  |            | 31:24    |       |                |                |           |         |          |          |          |

|                  |            | 7:0      | PDEC  | TC5            | TC4            | TCC3      | TCC2    | GMAC     | CAN1     | CAN0     |

| 0x1C             | INTFLAGC   | 15:8     |       | CCL            | QSPI           | PUKCC     | ICM     | TRNG     | AES      |          |

| 0x10             |            | 23:16    |       |                |                |           |         |          |          |          |

|                  |            | 31:24    |       |                |                |           |         |          |          |          |

|                  |            | 7:0      | ADC0  | TC7            | TC6            | TCC4      | SERCOM7 | SERCOM6  | SERCOM5  | SERCOM4  |

| 0x20             | INTFLAGD   | 15:8     |       |                |                |           | PCC     | 12S      | DAC      | ADC1     |

|                  |            | 23:16    |       |                |                |           |         |          |          |          |

|                  |            | 31:24    |       |                |                |           |         |          |          |          |

| 0x24<br><br>0x33 | Reserved   |          |       |                |                |           |         |          |          |          |

|                  |            | 7:0      | GCLK  | SUPC           | OSC32KCTR<br>L | OSCCTRL   | RSTC    | MCLK     | PM       | PAC      |

| 0x34             | STATUSA    | 15:8     | TC1   | TC0            | SERCOM1        | SERCOM0   | FREQM   | EIC      |          | WDT      |

|                  |            | 23:16    |       |                |                |           |         |          |          |          |

|                  |            | 31:24    |       |                |                |           |         |          |          |          |

| 0x38             | STATUSB    | 7:0      | EVSYS |                | DMAC           | PORT      | CMCC    | NVMCTRL  | DSU      | USB      |

### **PAC - Peripheral Access Controller**

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the PUKCC interrupt flag.

### Bit 11 – ICM Interrupt Flag for ICM

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the ICM, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the ICM interrupt flag.

### Bit 10 – TRNG Interrupt Flag for TRNG

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the TRNG, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the TRNG interrupt flag.

### Bit 9 – AES Interrupt Flag for AES

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the AES, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the AES interrupt flag.

### **Bit 7 – PDEC** Interrupt Flag for PDEC

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the PDEC, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the PDEC interrupt flag.

### Bit 6 – TC5 Interrupt Flag for TC5

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the TC5, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the TC5 interrupt flag.

### Bit 5 – TC4 Interrupt Flag for TC4

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the TC4, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the TC4 interrupt flag.

### Bit 4 – TCC3 Interrupt Flag for TCC3

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the TCC3, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

### 28.6.9 Synchronization

Due to the multiple clock domains, some registers in the DFLL48M must be synchronized when accessed. A register can require:

- Synchronization when written

- Synchronization when read

- No synchronization

When executing an operation that requires synchronization, the relevant synchronization bit in the Synchronization Busy register (DFLLSYNC) will be set immediately, and cleared when synchronization is complete.

The following registers need synchronization:

- ENABLE bit in DFLLCTRLA register write-synchronized

- DFLLCTRLB register read-synchronized

- DFLLVAL register read- and write-synchronized

- DFLLMUL register write-synchronized

Due to the multiple clock domains (XOSC32K, XOSC, GCLK and CK), some registers in the DPLL must be synchronized when accessed. A register can require:

- Synchronization when written

- No synchronization

When executing an operation that requires synchronization, the relevant synchronization bit in the Synchronization Busy register (DPLLnSYNCBUSY) will be set immediately, and cleared when synchronization is complete.

The following bits need synchronization when written:

- Enable bit in control register A (DPLLnCTRLA.ENABLE)

- DPLLn Ratio register (DPLLnRATIO)

- XOSC32KRDY 32KHz Crystal Oscillator Ready: A 0-to-1 transition on the STATUS.XOSC32KRDY bit is detected

- XOSC32KFAIL Clock Failure Detector: A 0-to-1 transition on the STATUS.XOSC32KFAIL bit is detected

All these interrupts are synchronous wake-up source.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs. Each interrupt can be enabled individually by setting the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR). An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled or the OSC32KCTRL is reset. See the INTFLAG register for details on how to clear interrupt flags.

The OSC32KCTRL has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present. Refer to the INTFLAG register for details.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated.

### **Related Links**

18. PM – Power Manager10.2 Nested Vector Interrupt Controller

### 29.6.8 Events

The CFD can generate the following output event:

Clock Failure Detector (XOSC32KFAIL): Generated when the Clock Failure Detector status bit is set in the Status register (STATUS.XOSC32KFAIL). The CFD event is not generated when the Clock Switch bit (STATUS.SWBACK) in the Status register is set.

Writing a '1' to an Event Output bit in the Event Control register (EVCTRL.CFDEO) enables the CFD output event. Writing a '0' to this bit disables the CFD output event. Refer to the Event System chapter for details on configuring the event system.

## EVSYS – Event System

| Value       | Name     | Description             |  |  |

|-------------|----------|-------------------------|--|--|

| 0x33        | TCC1_TRG | TCC1 Trigger Event      |  |  |

| 0x34        | TCC1_CNT | TCC1 Counter            |  |  |

| 0x35 - 0x38 | TCC1_MCx | TCC1 Match/Compare x=03 |  |  |

| 0x39        | TCC2_OVF | TCC2 Overflow           |  |  |

| 0x3A        | TCC2_TRG | TCC2 Trigger Event      |  |  |

| 0x3B        | TCC2_CNT | TCC2 Counter            |  |  |

| 0x3C - 0x3E | TCC2_MCx | TCC2 Match/Compare x=02 |  |  |

| 0x3F        | TCC3_OVF | TCC3 Overflow           |  |  |

| 0x40        | TCC3_TRG | TCC3 Trigger Event      |  |  |

| 0x41        | TCC3_CNT | TCC3 Counter            |  |  |

| 0x42 - 0x43 | TCC3_MCx | TCC3 Match/Compare x=01 |  |  |

| 0x44        | TCC4_OVF | TCC4 Overflow           |  |  |

| 0x45        | TCC4_TRG | TCC4 Trigger Event      |  |  |

| 0x46        | TCC4_CNT | TCC4 Counter            |  |  |

| 0x47 - 0x48 | TCC4_MCx | TCC4 Match/Compare x=01 |  |  |

| 0x49        | TC0_OVF  | TC0 Overflow            |  |  |

| 0x4A - 0x4B | TC0_MCx  | TC0 Match/Compare x=01  |  |  |

| 0x4C        | TC1_OVF  | TC1 Overflow            |  |  |

| 0x4D - 0x4E | TC1_MCx  | TC1 Match/Compare x=01  |  |  |

| 0x4F        | TC2_OVF  | TC2 Overflow            |  |  |

| 0x50 - 0x51 | TC2_MCx  | TC2 Match/Compare x=01  |  |  |

| 0x52        | TC3_OVF  | TC3 Overflow            |  |  |

| 0x53 - 0x54 | TC3_MCx  | TC3 Match/Compare x=01  |  |  |

| 0x55        | TC4_OVF  | TC4 Overflow            |  |  |

| 0x56 - 0x57 | TC4_MCx  | TC4 Match/Compare x=01  |  |  |

| 0x58        | TC5_OVF  | TC5 Overflow            |  |  |

| 0x59 - 0x5A | TC5_MCx  | TC5 Match/Compare x=01  |  |  |

| 0x5B        | TC6_OVF  | TC6 Overflow            |  |  |

| 0x5C - 0x5D | TC6_MCx  | TC6 Match/Compare x=01  |  |  |

| 0x5E        | TC7_OVF  | TC7 Overflow            |  |  |

| 0x5F - 0x60 | TC7_MCx  | TC7 Match/Compare x=01  |  |  |

| 0x61        | PDEC_OVF | PDEC Overflow           |  |  |

## 32. PORT - I/O Pin Controller

### 32.1 Overview

The IO Pin Controller (PORT) controls the I/O pins of the device. The I/O pins are organized in a series of groups, collectively referred to as a PORT group. Each PORT group can have up to 32 pins that can be configured and controlled individually or as a group. The number of PORT groups on a device may depend on the package/number of pins. Each pin may either be used for general-purpose I/O under direct application control or be assigned to an embedded device peripheral. When used for general-purpose I/O, each pin can be configured as input or output, with highly configurable driver and pull settings.

All I/O pins have true read-modify-write functionality when used for general-purpose I/O; the direction or the output value of one or more pins may be changed (set, reset or toggled) explicitly without unintentionally changing the state of any other pins in the same port group by a single, atomic 8-, 16- or 32-bit write.

The PORT is connected to the high-speed bus matrix through an AHB/APB bridge.

### 32.2 Features

- Selectable input and output configuration for each individual pin

- Software-controlled multiplexing of peripheral functions on I/O pins

- Flexible pin configuration through a dedicated Pin Configuration register

- Configurable output driver and pull settings:

- Totem-pole (push-pull)

- Pull configuration

- Driver strength

- Configurable input buffer and pull settings:

- Internal pull-up or pull-down

- Input sampling criteria

- Input buffer can be disabled if not needed for lower power consumption

- Input event:

- Up to four input event pins for each PORT group

- SET/CLEAR/TOGGLE event actions for each event input on output value of a pin

- Can be output to pin

## Bit 2 – RXC Receive Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Receive Complete Interrupt Enable bit, which enables the Receive Complete interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | Receive Complete interrupt is disabled. |

| 1     | Receive Complete interrupt is enabled.  |

**Bit 1 – TXC** Transmit Complete Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Transmit Complete Interrupt Enable bit, which enables the Transmit Complete interrupt.

| Value                                     | Description                              |  |  |  |

|-------------------------------------------|------------------------------------------|--|--|--|

| 0                                         | Transmit Complete interrupt is disabled. |  |  |  |

| 1 Transmit Complete interrupt is enabled. |                                          |  |  |  |

**Bit 0 – DRE** Data Register Empty Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Data Register Empty Interrupt Enable bit, which enables the Data Register Empty interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Data Register Empty interrupt is disabled. |

| 1     | Data Register Empty interrupt is enabled.  |

## Public Key Cryptography Controller (PUKCC)

| Parameter                             | Туре | Direction | Location      | Data Length           | Before<br>Executing the<br>Service                                      | After<br>Executing<br>the Service |

|---------------------------------------|------|-----------|---------------|-----------------------|-------------------------------------------------------------------------|-----------------------------------|

| u2ScalarLength                        | u2   | 1         | -             | _                     | Length of scalar<br>( <u>sam</u> e length as<br>the length of<br>order) | Length of<br>scalar               |

| nu1PointABase (see<br><b>Note 2</b> ) | nu1  | I/O       | Crypto<br>RAM | 3*u2ModLength<br>+ 12 | Input point A<br>(three<br>coordinates<br>(X,Y) affine and<br>Z = 1)    | Resulting<br>signature<br>(R,S,0) |

| nu1ABase                              | nu1  | 1         | Crypto<br>RAM | u2ModLength + 4       | Parameter a of the elliptic curve                                       | Unchanged                         |

| nu1Workspace                          | nu1  | 1         | Crypto<br>RAM | 8*u2ModLength<br>+ 44 | _                                                                       | Corrupted workspace               |

### Note:

- 1. The hash value calculus is defined by the ECDSA norm and depends on the elliptic curve domain parameters. To construct the input parameter, the 4 Most Significant Bytes must be set to zero.

- 2. The resulting signature format is different from the point A format (see Description above for information on the point A format).

#### 43.3.6.11.5 Code Example

```

PUKCL PARAM PUKCLParam;

PPUKCL PARAM pvPUKCLParam = & PUKCLParam;

// ! The Random Number Generator must be initialized and started

// ! following the directives given for the RNG on the chip

PUKCL (u2Option) = 0;

// Depending on the option specified, not all fields should be filled PUKCL

ZpEcDsaGenerate(nulModBase) = <Base of the ram location of P>; PUKCL

ZpEcDsaGenerate(u2ModLength) = <Byte length of P>;

PUKCL _ZpEcDsaGenerate(nulCnsBase) = <Base of the ram location of Cns>;

PUKCL ZpEcDsaGenerate(nulPointABase) = <Base of the A point>;

PUKCL _ZpEcDsaGenerate(nulPrivateKey) = <Base of the Private Key>;

PUKCL _ZpEcDsaGenerate(nulScalarNumber) = <Base of the ScalarNumber>;

PUKCL _ZpEcDsaGenerate(nulOrderPointBase) = <Base of the order of A point>;

PUKCL

_ZpEcDsaGenerate(nulABase) = <Base of the a parameter of the curve>;

PUKCL _ZpEcDsaGenerate(nulWorkspace) = <Base of the workspace>;

ZpEcDsaGenerate(nulHashBase) = <Base of the SHA resulting hash>;

PUKCL

PUKCL ZpEcDsaGenerate(u2ScalarLength)

= < Length of ScalarNumber>;

// vPUKCL Process() is a macro command, which populates the service name

// and then calls the library...

vPUKCL Process(ZpEcDsaGenerateFast, pvPUKCLParam);

if (PUKCL (u2Status) == PUKCL OK)

{

. . .

else // Manage the error

```

### ADC – Analog-to-Digital Converter

### Figure 45-7. ADC Timing for Free Running in 8-bit Resolution

The propagation delay of an ADC measurement is given by:

$PropagationDelay = \frac{1 + Resolution}{f_{ADC}}$

**Example.** In order to obtain 1MSPS in 12-bit resolution with a sampling time length of four CLK\_ADC cycles,  $f_{CLK\_ADC}$  must be 1MSPS \* (4 + 12) = 16MHz. As the minimal division factor of the prescaler is 2, GCLK\_ADC must be 32MHz.

### 45.6.2.9 Accumulation

The results of multiple, consecutive conversions can be accumulated. The number of samples to be accumulated is specified by the Sample Number field in the Average Control register (AVGCTRL.SAMPLENUM). When accumulating more than 16 samples, the result will be too large to fit the 16-bit RESULT register size. To avoid overflow, the result is right shifted automatically to fit within the available register size. The number of automatic right shifts is specified in the table below.

**Note:** To perform the accumulation of two or more samples, the Conversion Result Resolution field in the Control B register (CTRLB.RESSEL) must be set.

| Number of<br>Accumulated<br>Samples | AVGCTRL.<br>SAMPLENUM | Number of<br>Automatic Right<br>Shifts | Final Result<br>Precision | Automatic<br>Division Factor |

|-------------------------------------|-----------------------|----------------------------------------|---------------------------|------------------------------|

| 1                                   | 0x0                   | 0                                      | 12 bits                   | 0                            |

| 2                                   | 0x1                   | 0                                      | 13 bits                   | 0                            |

| 4                                   | 0x2                   | 0                                      | 14 bits                   | 0                            |

| 8                                   | 0x3                   | 0                                      | 15 bits                   | 0                            |

| 16                                  | 0x4                   | 0                                      | 16 bits                   | 0                            |

| 32                                  | 0x5                   | 1                                      | 16 bits                   | 2                            |

| 64                                  | 0x6                   | 2                                      | 16 bits                   | 4                            |

| 128                                 | 0x7                   | 3                                      | 16 bits                   | 8                            |

| 256                                 | 0x8                   | 4                                      | 16 bits                   | 16                           |

| 512                                 | 0x9                   | 5                                      | 16 bits                   | 32                           |

| 1024                                | 0xA                   | 6                                      | 16 bits                   | 64                           |

| Reserved                            | 0xB –0xF              |                                        | 12 bits                   | 0                            |

### Table 45-1. Accumulation

## AC – Analog Comparators

### Bits 14:12 - MUXPOS[2:0] Positive Input Mux Selection

These bits select which input will be connected to the positive input of comparator n. COMPCTRLn.MUXPOS can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value   | Name   | Description |

|---------|--------|-------------|

| 0x0     | PIN0   | I/O pin 0   |

| 0x1     | PIN1   | I/O pin 1   |

| 0x2     | PIN2   | I/O pin 2   |

| 0x3     | PIN3   | I/O pin 3   |

| 0x4     | VSCALE | VDD scaler  |

| 0x5-0x7 | -      | Reserved    |

### Bits 10:8 - MUXNEG[2:0] Negative Input Mux Selection

These bits select which input will be connected to the negative input of comparator n. COMPCTRLn.MUXNEG can only be written while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name    | Description              |

|-------|---------|--------------------------|

| 0x0   | PIN0    | I/O pin 0                |

| 0x1   | PIN1    | I/O pin 1                |

| 0x2   | PIN2    | I/O pin 2                |

| 0x3   | PIN3    | I/O pin 3                |

| 0x4   | GND     | Ground                   |

| 0x5   | VSCALE  | VDD scaler               |

| 0x6   | BANDGAP | Internal bandgap voltage |

| 0x7   | DAC     | DAC output               |

### Bit 6 – RUNSTDBY Run in Standby

This bit controls the behavior of the comparator during standby sleep mode.

This bit is not synchronized

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | The comparator is disabled during sleep.          |

| 1     | The comparator continues to operate during sleep. |

### Bits 4:3 – INTSEL[1:0] Interrupt Selection

These bits select the condition for comparator n to generate an interrupt or event. COMPCTRLn.INTSEL can be written only while COMPCTRLn.ENABLE is zero.

These bits are not synchronized.

| Value | Name    | Description                                            |

|-------|---------|--------------------------------------------------------|

| 0x0   | TOGGLE  | Interrupt on comparator output toggle                  |

| 0x1   | RISING  | Interrupt on comparator output rising                  |

| 0x2   | FALLING | Interrupt on comparator output falling                 |

| 0x3   | EOC     | Interrupt on end of comparison (single-shot mode only) |

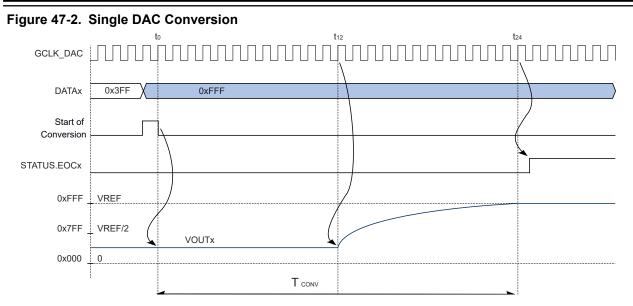

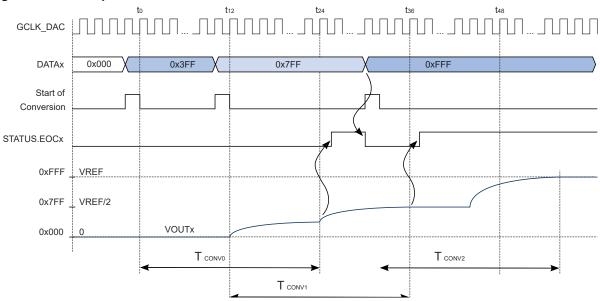

DAC – Digital-to-Analog Converter

Since the DAC conversion is implemented as pipelined procedure, a new conversion can be started after only 12 GCLK\_DAC periods. Therefore if DATAx is written while a conversion is ongoing, start of conversion is postponed until DACx is ready to start next conversion.

The maximum conversion rate (samples per second) is therefore:

$$CR_{max} = \frac{2}{T_{conv}}$$

### Figure 47-3. Multiple DAC Conversions

### **Related Links**

### 19. SUPC – Supply Controller

### 47.6.3 Operating Conditions

- The DAC voltage reference must be below VDDANA.

- The maximum conversion rate of 1MSPS can be achieved only if VDDANA is above 2.4V.

### 48.7.2.7 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x0A    |

| Reset:    | 0x00    |

| Property: | -       |

| Bit    | 7 | 6 | 5   | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|-----|-----|---|---|-----|-----|

|        |   |   | MC1 | MC0 |   |   | ERR | OVF |

| Access |   |   | R/W | R/W |   |   | R/W | R/W |

| Reset  |   |   | 0   | 0   |   |   | 0   | 0   |

### Bit 5 – MC1 Match or Capture Channel x

This flag is set on a comparison match, or when the corresponding CCx register contains a valid capture value. This flag is set on the next CLK\_TC\_CNT cycle, and will generate an interrupt request if the corresponding Match or Capture Channel x Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.MCx) is '1'.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In capture operation, this flag is automatically cleared when CCx register is read.

### **Bit 4 – MC0** Match or Capture Channel x

This flag is set on a comparison match, or when the corresponding CCx register contains a valid capture value. This flag is set on the next CLK\_TC\_CNT cycle, and will generate an interrupt request if the corresponding Match or Capture Channel x Interrupt Enable bit in the Interrupt Enable Set register (INTENSET.MCx) is '1'.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In capture operation, this flag is automatically cleared when CCx register is read.

### Bit 1 – ERR Error Interrupt Flag

This flag is set when a new capture occurs on a channel while the corresponding Match or Capture Channel x interrupt flag is set, in which case there is nowhere to store the new capture.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Error interrupt flag.

### **Bit 0 – OVF** Overflow Interrupt Flag

This flag is set on the next CLK\_TC\_CNT cycle after an overflow condition occurs, and will generate an interrupt request if INTENCLR.OVF or INTENSET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

### 49.8.8 Debug control

| Name:     | DBGCTRL              |

|-----------|----------------------|

| Offset:   | 0x1E                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2     | 1 | 0      |

|--------|---|---|---|---|---|-------|---|--------|

|        |   |   |   |   |   | FDDBD |   | DBGRUN |

| Access |   |   |   |   |   | R/W   |   | R/W    |

| Reset  |   |   |   |   |   | 0     |   | 0      |

### Bit 2 – FDDBD Fault Detection on Debug Break Detection

This bit is not affected by software reset and should not be changed by software while the TCC is enabled.

By default this bit is zero, and the on-chip debug (OCD) fault protection is disabled. When this bit is written to '1', OCD break request from the OCD system will trigger non-recoverable fault. When this bit is set, OCD fault protection is enabled and OCD break request from the OCD system will trigger a non-recoverable fault.

| Value | Description                                                                                   |

|-------|-----------------------------------------------------------------------------------------------|

| 0     | No faults are generated when TCC is halted in debug mode.                                     |

| 1     | A non recoverable fault is generated and FAULTD flag is set when TCC is halted in debug mode. |

### Bit 0 – DBGRUN Debug Running State

This bit is not affected by software reset and should not be changed by software while the TCC is enabled.

| Value | Description                                                                 |

|-------|-----------------------------------------------------------------------------|

| 0     | The TCC is halted when the device is halted in debug mode.                  |

| 1     | The TCC continues normal operation when the device is halted in debug mode. |