Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                            |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                     |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-TQFP                                                                     |

| Supplier Device Package    | 64-TQFP (10x10)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd51j19a-au   |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

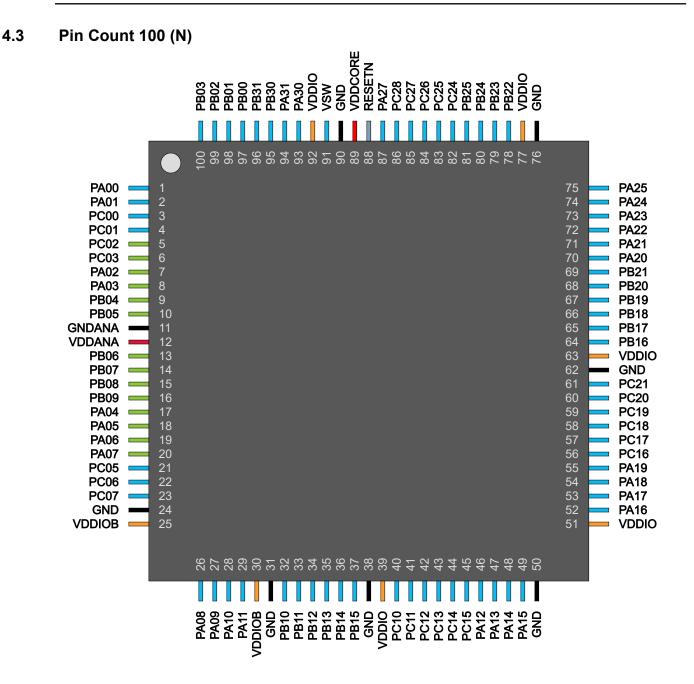

Pinout

### 19.6.2.4 Sleep Mode Operation

The Voltage Reference output and the Temperature Sensor output behavior during sleep mode can be configured using the Run in Standby bit and the On Demand bit in the Voltage Reference register (VREF.RUNSTDBY, VREF.ONDEMAND), see the following table:

| VREF.ONDEMAND | VREF.RUNSTDBY | Voltage Reference Sleep behavior                                                         |

|---------------|---------------|------------------------------------------------------------------------------------------|

| -             | -             | Disable                                                                                  |

| 0             | 0             | Always run in all sleep modes <i>except</i> standby sleep mode                           |

| 0             | 1             | Always run in all sleep modes <i>including</i> standby sleep mode                        |

| 1             | 0             | Only run if requested by the ADC, in all sleep modes <i>except</i> standby sleep mode    |

| 1             | 1             | Only run if requested by the ADC, in all sleep modes <i>including</i> standby sleep mode |

#### 19.6.3 Battery Backup Power Switch

#### 19.6.3.1 Initialization

The Battery Backup Power Switch (BBPS) is disabled at power-up, and the backup domain is supplied by main power.

#### 19.6.3.2 Automatic Battery Backup Power Switch

The supply of the backup domain can be switched automatically to VBAT supply pin by the Battery Backup Power Switch when the BOD33 detects that the VDD supply is below the VDD threshold level (BOD33.LEVEL). It is switched back to VDD supply pin when the BOD33 detects that VDD is above the VDD threshold level (BOD33.LEVEL).

To enable this feature, the following configuration is required: BOD33.ACTION=BKUP.

#### 19.6.3.3 Sleep Mode Operation

The Battery Backup Power Switch is not stopped in any sleep mode.

## 19.6.3.3.1 Entering Battery Backup Mode

Entering backup mode can be triggered by either:

- Wait-for-interrupt (WFI) instruction.

- BOD33 detection: When the BOD33 detects loss of Main Power, the Backup Domain will be powered by battery and the device will enter the backup mode. For this trigger, the following register configuration is required: BOD33.ACTION=BKUP.

#### **Related Links**

#### 18. PM - Power Manager

#### 19.6.3.3.2 Leaving Battery Backup Mode

Leaving backup mode is triggered by the RSTC when a Backup Mode Exit condition occurs. See RSTC module for details.

- BOD33 exit condition: When the BOD33 detects Main Power is restored and BOD33.ACTION=BKUP:

- When BBPS.WAKEEN=1, the device will leave backup mode and wake up.

## 21.12.10 Clock Value in Clock/Calendar mode (CTRLA.MODE=2)

| Name:     | CLOCK                                                       |

|-----------|-------------------------------------------------------------|

| Offset:   | 0x18                                                        |

| Reset:    | 0x0000000                                                   |

| Property: | PAC Write-Protection, Write-Synchronized, Read-Synchronized |

| Bit    | 31   | 30        | 29     | 28  | 27       | 26      | 25     | 24        |

|--------|------|-----------|--------|-----|----------|---------|--------|-----------|

|        |      | YEAR[5:0] |        |     |          |         | MON    | TH[3:2]   |

| Access | R/W  | R/W       | R/W    | R/W | R/W      | R/W     | R/W    | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0        | 0       | 0      | 0         |

|        |      |           |        |     |          |         |        |           |

| Bit    | 23   | 22        | 21     | 20  | 19       | 18      | 17     | 16        |

|        | MON  | TH[1:0]   |        |     | DAY[4:0] |         |        | HOUR[4:4] |

| Access | R/W  | R/W       | R/W    | R/W | R/W      | R/W     | R/W    | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0        | 0       | 0      | 0         |

|        |      |           |        |     |          |         |        |           |

| Bit    | 15   | 14        | 13     | 12  | 11       | 10      | 9      | 8         |

|        |      | HOU       | R[3:0] |     |          | MINUT   | E[5:2] |           |

| Access | R/W  | R/W       | R/W    | R/W | R/W      | R/W     | R/W    | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0        | 0       | 0      | 0         |

|        |      |           |        |     |          |         |        |           |

| Bit    | 7    | 6         | 5      | 4   | 3        | 2       | 1      | 0         |

|        | MINU | TE[1:0]   |        |     | SECO     | ND[5:0] |        |           |

| Access | R/W  | R/W       | R/W    | R/W | R/W      | R/W     | R/W    | R/W       |

| Reset  | 0    | 0         | 0      | 0   | 0        | 0       | 0      | 0         |

## Bits 31:26 - YEAR[5:0] Year

The year offset with respect to the reference year (defined in software).

The year is considered a leap year if YEAR[1:0] is zero.

#### Bits 25:22 – MONTH[3:0] Month

1 – January

```

2 – February

```

...

12 - December

#### Bits 21:17 - DAY[4:0] Day

Day starts at 1 and ends at 28, 29, 30, or 31, depending on the month and year.

## Bits 16:12 - HOUR[4:0] Hour

When CTRLA.CLKREP=0, the Hour bit group is in 24-hour format, with values 0-23. When CTRLA.CLKREP=1, HOUR[3:0] has values 1-12, and HOUR[4] represents AM (0) or PM (1).

# Bits 11:6 – MINUTE[5:0] Minute 0 – 59

© 2018 Microchip Technology Inc.

## **EIC – External Interrupt Controller**

### 23.8.2 Non-Maskable Interrupt Control

| Name:     | NMICTRL              |

|-----------|----------------------|

| Offset:   | 0x01                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4         | 3         | 2   | 1             | 0   |

|--------|---|---|---|-----------|-----------|-----|---------------|-----|

|        |   |   |   | NMIASYNCH | NMIFILTEN |     | NMISENSE[2:0] |     |

| Access |   |   |   | R/W       | R/W       | R/W | R/W           | R/W |

| Reset  |   |   |   | 0         | 0         | 0   | 0             | 0   |

#### Bit 4 – NMIASYNCH Asynchronous Edge Detection Mode

The NMI edge detection can be operated synchronously or asynchronously to the EIC clock.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The NMI edge detection is synchronously operated.  |

| 1     | The NMI edge detection is asynchronously operated. |

#### Bit 3 – NMIFILTEN Non-Maskable Interrupt Filter Enable

| Value | Description             |

|-------|-------------------------|

| 0     | NMI filter is disabled. |

| 1     | NMI filter is enabled.  |

#### Bits 2:0 - NMISENSE[2:0] Non-Maskable Interrupt Sense Configuration

These bits define on which edge or level the NMI triggers.

| Value | Name | Description            |  |  |  |

|-------|------|------------------------|--|--|--|

| 0x0   | NONE | No detection           |  |  |  |

| 0x1   | RISE | ing-edge detection     |  |  |  |

| 0x2   | FALL | Falling-edge detection |  |  |  |

| 0x3   | BOTH | Both-edge detection    |  |  |  |

| 0x4   | HIGH | High-level detection   |  |  |  |

| 0x5   | LOW  | Low-level detection    |  |  |  |

| 0x6 - | -    | Reserved               |  |  |  |

| 0x7   |      |                        |  |  |  |

|                 | Name:<br>Offset:<br>Reset:<br>Property: | RLPITR<br>0x270<br>0x00000000<br>Read-Only |        |            |         |        |    |    |

|-----------------|-----------------------------------------|--------------------------------------------|--------|------------|---------|--------|----|----|

| Bit             | 31                                      | 30                                         | 29     | 28         | 27      | 26     | 25 | 24 |

| Access          |                                         |                                            |        |            |         |        |    |    |

| Reset           |                                         |                                            |        |            |         |        |    |    |

| Bit             | 23                                      | 22                                         | 21     | 20         | 19      | 18     | 17 | 16 |

|                 |                                         |                                            |        |            |         |        |    |    |

| Access<br>Reset |                                         |                                            |        |            |         |        |    |    |

| Bit             | 15                                      | 14                                         | 13     | 12         | 11      | 10     | 9  | 8  |

|                 |                                         |                                            |        | RLPITI     | R[15:8] |        |    |    |

| Access          | R                                       | R                                          | R      | R          | R       | R      | R  | R  |

| Reset           | 0                                       | 0                                          | 0      | 0          | 0       | 0      | 0  | 0  |

| Dit             | 7                                       | C                                          | F      | 4          | 2       | 0      | 4  | 0  |

| Bit             | 7                                       | 6                                          | 5      | 4<br>RLPIT | 3       | 2      | 1  | 0  |

| Access          | R                                       | R                                          | R      | R          | R[7.0]  | R      | R  | R  |

| Reset           |                                         | 0                                          | R<br>0 | К<br>0     | R<br>0  | к<br>0 | 0  | 0  |

| 10301           | 0                                       | Ū                                          | 0      | 0          | 0       | 0      | 0  | v  |

#### 24.9.99 Received LPI Transitions

## Bits 15:0 - RLPITR[15:0] Received LPI Transitions

The value of this bit field is a counter of transitions from receiving normal idle to receiving low power idle.

Cleared on read.

# SAMD5x/E5x Family Data Sheet

ICM - Integrity Check Monitor

| Example    | Comment          |

|------------|------------------|

| 0x98BADCFE | SHA1 algorithm   |

| 0x3070DD17 | SHA224 algorithm |

| 0x3C6EF372 | SHA256 algorithm |

## For UIHVAL3 field:

| Example    | Comment          |

|------------|------------------|

| 0x10325476 | SHA1 algorithm   |

| 0xF70E5939 | SHA224 algorithm |

| 0xA54FF53A | SHA256 algorithm |

## For UIHVAL4 field:

| Example    | Comment          |

|------------|------------------|

| 0xC3D2E1F0 | SHA1 algorithm   |

| 0xFFC00B31 | SHA224 algorithm |

| 0x510E527F | SHA256 algorithm |

## For UIHVAL5 field:

| Example    | Comment          |

|------------|------------------|

| 0x68581511 | SHA224 algorithm |

| 0x9B05688C | SHA256 algorithm |

## For UIHVAL6 field:

| Example    | Comment          |

|------------|------------------|

| 0x64F98FA7 | SHA224 algorithm |

| 0x1F83D9AB | SHA256 algorithm |

## For UIHVAL7 field:

| Example    | Comment          |

|------------|------------------|

| 0xBEFA4FA4 | SHA224 algorithm |

| 0x5BE0CD19 | SHA256 algorithm |

Example of Initial Value for SHA-1 Algorithm

© 2018 Microchip Technology Inc.

# SAMD5x/E5x Family Data Sheet PORT - I/O Pin Controller

Be careful when the event is output to pin. Due to the fact the events are received asynchronously, the I/O pin may have unpredictable levels, depending on the timing of when the events are received. When several events are output to the same pin, the lowest event line will get the access. All other events will be ignored.

## **Related Links**

31. EVSYS - Event System

## 32.6.5 PORT Access Priority

The PORT is accessed by different systems:

- The ARM<sup>®</sup> CPU through the high-speed matrix and the AHB/APB bridge (APB)

- EVSYS through four asynchronous input events

The following priority is adopted:

- 1. APB

- 2. EVSYS input events, except for events with EVCTRL.EVACTn=OUT, where the output pin directly follows the event input signal, independently of the OUT register value.

For input events that require different actions on the same I/O pin, refer to 32.6.4 Events.

# SAMD5x/E5x Family Data Sheet SERCOM USART - SERCOM Synchronous and Asyn...

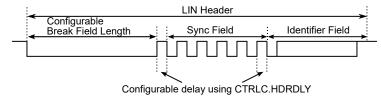

## Figure 34-13. LIN Frame Format

Using the LIN command field (CTRLB.LINCMD), the complete header can be automatically transmitted, or software can control transmission of the various header components.

When CTRLB.LINCMD=0x1, software controls transmission of the LIN header. In this case, software uses the following sequence.

- CTRLB.LINCMD is written to 0x1.

- DATA register written to 0x00. This triggers transmission of the break field by hardware. Note that writing the DATA register with any other value will also result in the transmission of the break field by hardware.

- DATA register written to 0x55. The 0x55 value (sync) is transmitted.

- DATA register written to the identifier. The identifier is transmitted.

When CTRLB.LINCMD=0x2, hardware controls transmission of the LIN header. In this case, software uses the following sequence.

- CTRLB.LINCMD is written to 0x2.

- DATA register written to the identifier. This triggers transmission of the complete header by hardware. First the break field is transmitted. Next, the sync field is transmitted, and finally the identifier is transmitted.

In LIN master mode, the length of the break field is programmable using the break length field (CTRLC.BRKLEN). When the LIN header command is used (CTRLB.LINCMD=0x2), the delay between the break and sync fields, in addition to the delay between the sync and ID fields are configurable using the header delay field (CTRLC.HDRDLY). When manual transmission is used (CTRLB.LINCMD=0x1), software controls the delay between break and sync.

## Figure 34-14. LIN Header Generation

After header transmission is complete, the slave responds with 1-8 data bytes plus checksum.

## 34.6.3.6 RS485

RS485 is available with the following configuration:

- USART frame format (CTRLA.FORM = 0x00 or 0x01)

- RS485 pinout (CTRLA.TXPO=0x3).

The RS485 feature enables control of an external line driver as shown in the figure below. While operating in RS485 mode, the transmit enable pin (TE) is driven high when the transmitter is active.

# SERCOM I2C – Inter-Integrated Circuit

## 36.8.9 Length

Name:LENGTHOffset:0x22Reset:0x0000Property:PAC Write-Protection, Write-Synchronized

| Bit    | 15  | 14  | 13  | 12  | 11    | 10  | 9   | 8     |

|--------|-----|-----|-----|-----|-------|-----|-----|-------|

|        |     |     |     |     |       |     |     | LENEN |

| Access |     |     |     |     |       |     |     | R/W   |

| Reset  |     |     |     |     |       |     |     | 0     |

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1   | 0     |

|        |     |     |     | LEN | [7:0] |     |     |       |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W | R/W   |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0     |

## Bit 8 – LENEN Data Length Enable

In 32-bit Extension mode (CTRLC.DATA32B=1), this bit field enables the length counter.

| Value | Description                 |

|-------|-----------------------------|

| 0     | Length counter is disabled. |

| 1     | Length counter is enabled.  |

## Bits 7:0 – LEN[7:0] Data Length

In 32-bit Extension mode (CTRLC.DATA32B=1) with Data Length counting enabled (LENGTH.LENEN), this bit field configures the data length from 0 to 255 Bytes after which the flag INTFLAG.DRDY is raised.

## USB – Universal Serial Bus

## Bit 5 – DNRSM Down Resume Interrupt Flag

This flag is cleared by writing a one to the flag.

This flag is set when the USB has sent a Down Resume and will generate an interrupt if INTENCLR/ SET.DRSM is one.

Writing a zero to this bit has no effect.

**Bit 4 – WAKEUP** Wake Up Interrupt Flag This flag is cleared by writing a one.

This flag is set when:

I The host controller is in suspend mode (SOFE is zero) and an upstream resume from the device is detected.

I The host controller is in suspend mode (SOFE is zero) and an device disconnection is detected.

I The host controller is in operational state (VBUSOK is one) and an device connection is detected.

In all cases it will generate an interrupt if INTENCLR/SET.WAKEUP is one.

Writing a zero to this bit has no effect.

Bit 3 – RST Bus Reset Interrupt Flag

This flag is cleared by writing a one to the flag.

This flag is set when a Bus "Reset" has been sent to the Device and will generate an interrupt if INTENCLR/SET.RST is one.

Writing a zero to this bit has no effect.

**Bit 2 – HSOF** Host Start-of-Frame Interrupt Flag This flag is cleared by writing a one to the flag.

This flag is set when a USB "Host Start-of-Frame" in Full Speed/High Speed or a keep-alive in Low Speed has been sent (every 1 ms) and will generate an interrupt if INTENCLR/SET.HSOF is one.

The value of the FNUM register is updated.

Writing a zero to this bit has no effect.

#### 40.8.24 Host Control 2 Register: e.MMC

| Name:     | HC2R   |

|-----------|--------|

| Offset:   | 0x3E   |

| Reset:    | 0x0000 |

| Property: | -      |

**Note:** The content of the HC2R register is depending on the mode. This description is for e.MMC mode. For SD/SDIO mode, see 40.8.25 HC2R.

| Bit    | 15     | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|--------|--------|----|----|----|----|----|---|---|

|        | PVALEN |    |    |    |    |    |   |   |

| Access | R/W    | •  |    |    |    |    |   |   |

| Reset  | 0      |    |    |    |    |    |   |   |

|        |        |    |    |    |    |    |   |   |

| Bit    | 7      | 6  | 5  | 4  | 3  | 2  | 1 | 0 |

|        |        |    |    |    |    |    |   |   |

| Access |        |    |    |    |    |    |   |   |

| -      |        |    |    |    |    |    |   |   |

Reset

#### Bit 15 – PVALEN Preset Value Enable

As the operating SDCLK frequency depends on the system implementation, it is difficult to determine these parameters in the standard host driver. When Preset Value Enable (PVALEN) is set to 1, automatic SDCLK frequency generationis performed without considering system-specific conditions. This bit enables the functions defined in PVR.

If this bit is written to 0, the Clock Generator Select bit (CCR.CLKGSEL) and the SDCLK Frequency Select bit (CCR.SDCLKFSEL) in the Clock Control Register (CCR) are selected by the user.

If this bit is set to 1, CCR.SDCLKFSEL and .CLKGSEL and HC2R.DRVSEL are set by the peripheral as specified in the Preset Value Register (PVR).

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | CCR.SDCLK, CCR.SDCLKFSEL controlled by the user. |

| 1     | Automatic selection by Preset Value is enabled.  |

- {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1PointABase, 3\*u2ModLength + 12}, {nu1PointBBase, 3\*u2ModLength + 12}, {nu1Workspace,

WorkspaceLength>} are not in Crypto RAM

- u2ModLength is either: < 12, > 0xffc or not a 32-bit length

- All overlapping between {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength +8}, {nu1PointABase, 3\*u2ModLength + 12}, {nu1PointBBase, 3\*u2ModLength + 12} and {nu1Workspace, 5\*u2ModLength + 32}

## 43.3.6.3.7 Status Returned Values

## Table 43-71. ZpEccAddFast Service Return Codes

| Returned Status | Importance | Meaning                                 |

|-----------------|------------|-----------------------------------------|

| PUKCL_OK        | -          | The computation passed without problem. |

## 43.3.6.4 Fast Point Doubling

## 43.3.6.4.1 Purpose

This service is used to perform a Point Doubling, based on a given elliptic curve over GF(p).

## 43.3.6.4.2 How to Use the Service

## 43.3.6.4.3 Description

These two services process the Point Doubling:

$Pt_C = 2 \times Pt_A$

In this computation, the following parameters need to be provided:

- A the input point is filled in projective coordinates (X,Y,Z) (pointed by {nu1PointABase, 3\*u2ModLength + 12}). This point can be the Infinite Point.

- Cns the Fast Modular Constant filled (pointed by {nu1CnsBase,u2ModLength +8})

- P the modulus filled (pointed by {nu1ModBase,u2ModLength +4})

- The workspace not initialized (pointed by {nu1WorkSpace, 4\*u2ModLength +28}

- The a parameter relative to the elliptic curve (pointed by {nu1ABase,u2ModLength +4})

- The resulting C point is represented in projective coordinates (X,Y,Z) and is stored at the same location than the input point A. This point can be the Infinite Point.

The service name for this operation is <code>ZpEccDblFast</code>. This service uses Fast mode and Fast Modular Reduction for computations.

**Important:** Before using this service, ensure that the constant Cns has been calculated with the setup of the Fast Modular Reduction service.

# SAMD5x/E5x Family Data Sheet

# TRNG – True Random Number Generator

#### 44.8.5 Interrupt Flag Status and Clear

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x0A<br>0x00<br>- |   |   |   |   |   |         |

|--------|-----------------------------------------|------------------------------|---|---|---|---|---|---------|

| Bit    | 7                                       | 6                            | 5 | 4 | 3 | 2 | 1 | 0       |

|        |                                         |                              |   |   |   |   |   | DATARDY |

| Access |                                         |                              |   |   |   |   |   | R/W     |

| Reset  |                                         |                              |   |   |   |   |   | 0       |

## Bit 0 – DATARDY Data Ready

This flag is set when a new random value is generated, and an interrupt will be generated if INTENCLR/ SET.DATARDY=1.

This flag is cleared by writing a '1' to the flag or by reading the DATA register.

Writing a '0' to this bit has no effect.

# ADC – Analog-to-Digital Converter

#### 45.8.16 Interrupt Flag Status and Clear

| Name:     | INTFLAG |  |  |  |

|-----------|---------|--|--|--|

| Offset:   | 0x2E    |  |  |  |

| Reset:    | 0x00    |  |  |  |

| Property: | _       |  |  |  |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2      | 1       | 0      |

|--------|---|---|---|---|---|--------|---------|--------|

|        |   |   |   |   |   | WINMON | OVERRUN | RESRDY |

| Access |   |   |   |   |   | R/W    | R/W     | R/W    |

| Reset  |   |   |   |   |   | 0      | 0       | 0      |

#### Bit 2 – WINMON Window Monitor Interrupt Flag

This flag is cleared by writing a '1' to the flag or by reading the RESULT register.

This flag is set on the next GCLK\_ADC cycle after a match with the window monitor condition, and an interrupt request will be generated if INTENCLR/SET.WINMON is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Window Monitor interrupt flag.

#### Bit 1 – OVERRUN Overrun Interrupt Flag

This flag is cleared by writing a '1' to the flag.

This flag is set if RESULT is written before the previous value has been read by CPU, and an interrupt request will be generated if INTENCLR/SET.OVERRUN=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overrun interrupt flag.

#### Bit 0 – RESRDY Result Ready Interrupt Flag

This flag is cleared by writing a '1' to the flag or by reading the RESULT register.

This flag is set when the conversion result is available, and an interrupt will be generated if INTENCLR/ SET.RESRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Result Ready interrupt flag.

## DAC – Digital-to-Analog Converter

### Bit 2 - EMPTY0 Data Buffer 0 Empty

This flag is cleared by writing a '1' to it or by writing new data to DATA0 or DATABUF0.

This flag is set when the data buffer for DAC0 is empty and will generate an interrupt request if INTENCLR/INTENSET.EMPTY0=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer 0 Empty interrupt flag.

### Bit 1 – UNDERRUN1 DAC1 Underrun

This flag is cleared by writing a '1' to it.

This flag is set when a start conversion event (START1) occurred before new data is copied/written to the DAC1 data buffer and will generate an interrupt request if INTENCLR/INTENSET.UNDERRUN1=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the DAC1 Underrun interrupt flag.

#### Bit 0 – UNDERRUN0 DAC0 Underrun

This flag is cleared by writing a '1' to it.

This flag is set when a start conversion event (START0) occurred before new data is copied/written to the DAC) data buffer and will generate an interrupt request if INTENCLR/INTENSET.UNDERRUN0=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the DAC0 Underrun interrupt flag.

#### Bit 0 – DIR Counter Direction

This bit is used to change the direction of the counter.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the bit and make the counter count up.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The timer/counter is counting up (incrementing).   |

| 1     | The timer/counter is counting down (decrementing). |

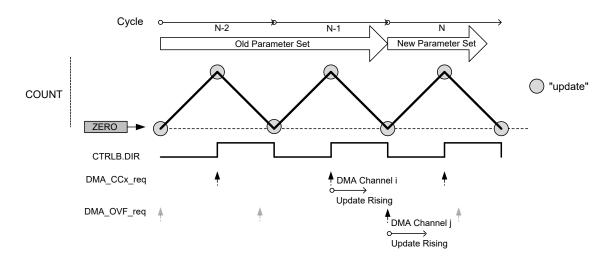

## TCC – Timer/Counter for Control Applications

## Figure 49-39. DMA Triggers in DSBOTH Operation Mode and Circular Buffer Enabled

## 49.6.5.2 Interrupts

The TCC has the following interrupt sources:

- Overflow/Underflow (OVF)

- Retrigger (TRG)

- Count (CNT) refer also to description of EVCTRL.CNTSEL.

- Capture Overflow Error (ERR)

- Debug Fault State (DFS)

- Recoverable Faults (FAULTn)

- Non-recoverable Faults (FAULTx)

- Compare Match or Capture Channels (MCx)

These interrupts are asynchronous wake-up sources. See Sleep Mode Entry and Exit Table in PM/Sleep Mode Controller section for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TCC is reset. See 49.8.12 INTFLAG for details on how to clear interrupt flags. The TCC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

## **Related Links**

10.2 Nested Vector Interrupt Controller

## 49.6.5.3 Events

The TCC can generate the following output events:

• Overflow/Underflow (OVF)

# I2S - Inter-IC Sound Controller

## Bit 0 – SWRST Software Reset Synchronization Status

This bit is cleared when the synchronization of CTRLA.SWRST bit between the clock domains is complete.

This bit is set when the synchronization of CTRLA.SWRST bit between the clock domains is started.

## PCC - Parallel Capture Controller

## 52.5 Product Dependencies

For the Parallel Capture Controller to function as intended, other interconnected modules of the system must be configured accordingly.

#### 52.5.1 I/O Lines

The PCC pins may be multiplexed with the I/O lines Controller. The user must first configure the I/O Controller to assign the PCC pins to their peripheral functions.

#### 52.5.2 PD for Clock from MCLK/GCLK

#### 52.5.2.1 Power Management

The PCC will continue to operate in any Sleep mode where the selected source clock is running. Events connected to the event system can trigger other operations in the system without exiting Sleep modes.

#### 52.5.2.2 Clocks

The PCC bus clock (CLK\_APB\_PCC) is provided by the Main Clock Controller (MCLK) through the AHB-APB D bridge. The clock is enabled and disabled by writing the PCC bit the in the APB D Mask register (MCLK.APBDMASK.PCC). See the register description for the default state of the PCC bus clock.

For capturing operation, the external device has to provide a PCC clock signal (PCC\_CLK) synchronous to the data received ("pixel clock") through a pin. See the PORT section and the Multiplexing table for details.

Writing any of the registers does not require the PCC\_CLK to be enabled.

**Important:** The CLK\_APB\_PCC clock frequency must be at least twice the PCC\_CLK frequency.

## **Related Links**

15.7 Register Summary

I/O Multiplexing and Considerations

PORT - I/O Pin Controller

#### 52.5.3 DMA

The DMAC can be configured to use the RX channel of the PCC as trigger source.

If configured, a trigger signal is send to the DMAC when data is received by the PCC, such that the DMAC will automatically read the received data buffer. The buffer ready signal will be automatically clear upon the read done by the DMAC.

#### **Related Links**

52.6.3 Programming Sequence 52.6.3.1 Without DMAC 52.6.3.2 With DMAC

#### 52.5.4 Interrupts

The PCC has these interrupts:

- OVRE Overrun Error interrupt

- DRDY Data Ready interrupt

# SAMD5x/E5x Family Data Sheet

## **Packaging Information**

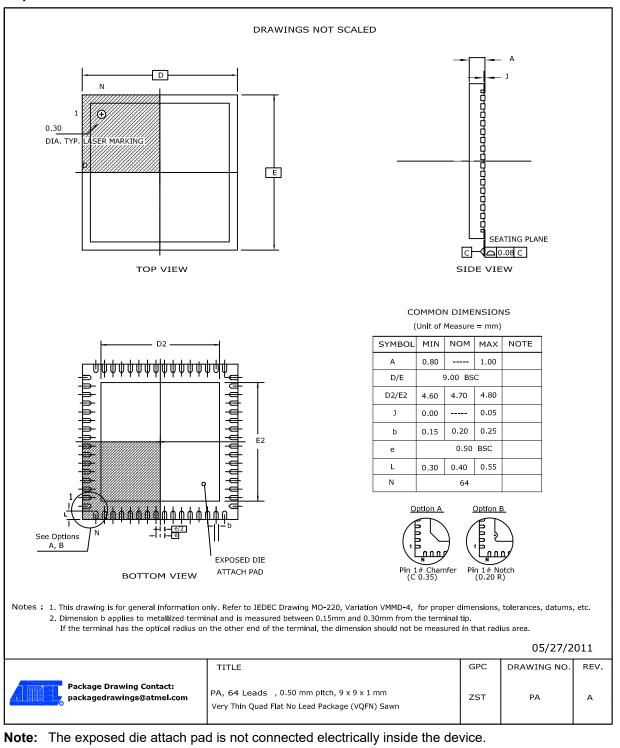

#### 55.3.3 64 pin QFN

#### Table 55-8. Device and Package Maximum Weight

200

mg