Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Dectano                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | ARM® Cortex®-M4F                                                            |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                     |

| Number of I/O              | 51                                                                          |

| Program Memory Size        | 512KB (512K x 8)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 192К х 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                               |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-VQFN (9x9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd51j19a-mu   |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# DSU - Device Service Unit

|        | Name:<br>Offset:<br>Reset:<br>Property: | CID2<br>0x1FF8<br>0x00000005<br>- |    |        |           |    |          |          |

|--------|-----------------------------------------|-----------------------------------|----|--------|-----------|----|----------|----------|

| Bit    | 31                                      | 30                                | 29 | 28     | 27        | 26 | 25       | 24       |

|        |                                         |                                   |    |        |           |    |          |          |

| Access |                                         |                                   |    |        |           |    |          |          |

| Reset  |                                         |                                   |    |        |           |    |          |          |

|        |                                         |                                   |    |        |           |    |          |          |

| Bit    | 23                                      | 22                                | 21 | 20     | 19        | 18 | 17       | 16       |

|        |                                         |                                   |    |        |           |    |          |          |

| Access |                                         |                                   |    |        |           |    |          |          |

| Reset  |                                         |                                   |    |        |           |    |          |          |

| Bit    | 15                                      | 14                                | 13 | 12     | 11        | 10 | 9        | 8        |

| Dit    |                                         |                                   | 10 | 12     |           |    | <u> </u> | <u> </u> |

| Access |                                         |                                   |    |        |           |    |          |          |

| Reset  |                                         |                                   |    |        |           |    |          |          |

|        |                                         |                                   |    |        |           |    |          |          |

| Bit    | 7                                       | 6                                 | 5  | 4      | 3         | 2  | 1        | 0        |

|        |                                         |                                   |    | PREAMB | LEB2[7:0] |    |          |          |

| Access | R                                       | R                                 | R  | R      | R         | R  | R        | R        |

| Reset  | 0                                       | 0                                 | 0  | 0      | 0         | 1  | 0        | 1        |

|        |                                         |                                   |    |        |           |    |          |          |

12.13.24 Component Identification 2

**Bits 7:0 – PREAMBLEB2[7:0]** Preamble Byte 2 These bits will always return 0x00000005 when read.

**GCLK - Generic Clock Controller**

| Value     | Name      | Description                      |

|-----------|-----------|----------------------------------|

| 0x00      | XOSC0     | XOSC 0 oscillator output         |

| 0x01      | XOSC1     | XOSC 1 oscillator output         |

| 0x02      | GCLK_IN   | Generator input pad (GCLK_IO)    |

| 0x03      | GCLK_GEN1 | Generic clock generator 1 output |

| 0x04      | OSCULP32K | OSCULP32K oscillator output      |

| 0x05      | XOSC32K   | XOSC32K oscillator output        |

| 0x06      | DFLL      | DFLL oscillator output           |

| 0x07      | DPLL0     | DPLL0 output                     |

| 0x08      | DPLL1     | DPLL1 output                     |

| 0x09-0x1F | Reserved  | Reserved for future use          |

#### Table 14-4. Generator Clock Source Selection

A Power Reset will reset all GENCTRLn registers. the Reset values of the GENCTRLn registers are shown in table below.

#### Table 14-5. GENCTRLn Reset Value after a Power Reset

| GCLK Generator | Reset Value after a Power Reset |

|----------------|---------------------------------|

| 0              | 0x0000106                       |

| others         | 0x0000000                       |

A User Reset will reset the associated GENCTRL register unless the Generator is the source of a locked Peripheral Channel (PCHCTRLm.WRTLOCK=1). The reset values of the GENCTRL register are as shown in the table below.

#### Table 14-6. GENCTRLn Reset Value after a User Reset

| GCLK Generator | Reset Value after a User Reset                                                                       |

|----------------|------------------------------------------------------------------------------------------------------|

| 0              | 0x0000106                                                                                            |

| others         | No change if the generator is used by a Peripheral Channel m with PCHCTRLm.WRTLOCK=1 else 0x00000000 |

## **Related Links**

14.8.4 PCHCTRLm

#### **Related Links**

6. I/O Multiplexing and Considerations

## 16.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 16.5.1 I/O Lines

Not applicable.

#### 16.5.2 Power Management

The Reset Controller module is always on.

#### 16.5.3 Clocks

The RSTC bus clock (CLK\_RSTC\_APB) can be enabled and disabled in the Main Clock Controller.

#### **Related Links**

MCLK – Main Clock

Main Clock Masking

#### 16.5.4 DMA

Not applicable.

#### 16.5.5 Interrupts

Not applicable.

#### 16.5.6 Events

Not applicable.

#### 16.5.7 Debug Operation

When the CPU is halted in debug mode, the RSTC continues normal operation.

#### 16.5.8 Register Access Protection

All registers with write-access can be optionally write-protected by the Peripheral Access Controller (PAC).

**Note:** Optional write-protection is indicated by the "PAC Write-Protection" property in the register description.

Write-protection does not apply for accesses through an external debugger.

#### 16.5.9 Analog Connections

Not applicable.

## 16.6 Functional Description

### 16.6.1 Principle of Operation

The Reset Controller collects the various Reset sources and generates Reset for the device.

# 21.7 Register Summary - Mode 0 - 32-Bit Counter

| Offset | Name     | Bit Pos. |           |          |           |              |            |          |           |          |

|--------|----------|----------|-----------|----------|-----------|--------------|------------|----------|-----------|----------|

| 000    | CTRLA    | 7:0      | MATCHCLR  |          |           |              | MOE        | DE[1:0]  | ENABLE    | SWRST    |

| 0x00   | CIRLA    | 15:8     | COUNTSYNC | GPTRST   |           |              |            | PRESCA   | LER[3:0]  |          |

| 0.00   |          | 7:0      | DMAEN     | RTCOUT   | DEBASYNC  | DEBMAJ       |            |          | GP2EN     | GP0EN    |

| 0x02   | CTRLB    | 15:8     |           |          | ACTF[2:0] |              |            |          | DEBF[2:0] |          |

|        |          | 7:0      |           |          |           | PERE         | On[7:0]    |          |           |          |

| 0.04   | EVCTRL   | 15:8     | OVFEO     | TAMPEREO |           |              |            |          | CMPE      | On[1:0]  |

| 0x04   | EVCIRL   | 23:16    |           |          |           |              |            |          |           | TAMPEVEI |

|        |          | 31:24    |           |          |           |              |            |          |           |          |

| 0.00   |          | 7:0      |           |          |           | PER          | n[7:0]     |          |           |          |

| 0x08   | INTENCLR | 15:8     | OVF       | TAMPER   |           |              |            |          | CMP       | n[1:0]   |

| 004    |          | 7:0      |           |          |           | PER          | n[7:0]     |          |           |          |

| 0x0A   | INTENSET | 15:8     | OVF       | TAMPER   |           |              |            |          | CMP       | n[1:0]   |

| 0.00   |          | 7:0      |           |          |           | PER          | n[7:0]     |          |           |          |

| 0x0C   | INTFLAG  | 15:8     | OVF       | TAMPER   |           |              |            |          | CMP       | n[1:0]   |

| 0x0E   | DBGCTRL  | 7:0      |           |          |           |              |            |          |           | DBGRUN   |

| 0x0F   | Reserved |          |           |          |           |              |            |          |           |          |

|        |          | 7:0      |           | COM      | Pn[1:0]   |              | COUNT      | FREQCORR | ENABLE    | SWRST    |

| 0.40   |          | 15:8     | COUNTSYNC |          |           |              |            |          |           |          |

| 0x10   | SYNCBUSY | 23:16    |           |          |           |              |            | GPn      | [3:0]     |          |

|        |          | 31:24    |           |          |           |              |            |          |           |          |

| 0x14   | FREQCORR | 7:0      | SIGN      |          |           |              | VALUE[6:0] |          |           |          |

| 0x15   |          |          |           |          |           |              |            |          |           |          |

|        | Reserved |          |           |          |           |              |            |          |           |          |

| 0x17   |          |          |           |          |           |              |            |          |           |          |

|        |          | 7:0      |           |          |           | COUN         | NT[7:0]    |          |           |          |

| 0x18   | COUNT    | 15:8     |           |          |           | COUN         | T[15:8]    |          |           |          |

| 0,10   | 000111   | 23:16    |           |          |           | COUNT[23:16] |            |          |           |          |

|        |          | 31:24    |           |          |           | COUN         | Г[31:24]   |          |           |          |

| 0x1C   |          |          |           |          |           |              |            |          |           |          |

|        | Reserved |          |           |          |           |              |            |          |           |          |

| 0x1F   |          |          |           |          |           |              |            |          |           |          |

|        |          | 7:0      |           |          |           |              | P[7:0]     |          |           |          |

| 0x20   | COMP0    | 15:8     |           |          |           |              | P[15:8]    |          |           |          |

|        |          | 23:16    |           |          |           |              | [23:16]    |          |           |          |

|        |          | 31:24    |           |          |           | COMP         | [31:24]    |          |           |          |

|        |          | 7:0      |           |          |           |              | P[7:0]     |          |           |          |

| 0x24   | COMP1    | 15:8     |           |          |           |              | P[15:8]    |          |           |          |

|        |          | 23:16    |           |          |           |              | [23:16]    |          |           |          |

|        |          | 31:24    |           |          |           | COMP         | [31:24]    |          |           |          |

| 0x28   |          |          |           |          |           |              |            |          |           |          |

|        | Reserved |          |           |          |           |              |            |          |           |          |

| 0x3F   |          |          |           |          |           |              |            |          |           |          |

| 0x40   | GP0      | 7:0      |           |          |           | GP           | [7:0]      |          |           |          |

# **DMAC – Direct Memory Access Controller**

| Offset | Name         | Bit Pos. |  |  |        |      |       |      |

|--------|--------------|----------|--|--|--------|------|-------|------|

| 0x023B |              |          |  |  |        |      |       |      |

| 0x023C | CHINTENCLR31 | 7:0      |  |  |        | SUSP | TCMPL | TERR |

| 0x023D | CHINTENSET31 | 7:0      |  |  |        | SUSP | TCMPL | TERR |

| 0x023E | CHINTFLAG31  | 7:0      |  |  |        | SUSP | TCMPL | TERR |

| 0x023F | CHSTATUS31   | 7:0      |  |  | CRCERR | FERR | BUSY  | PEND |

## 22.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 22.5.8 Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

#### 22.8.14 Descriptor Memory Section Base Address

| Name:     | BASEADDR                               |

|-----------|----------------------------------------|

| Offset:   | 0x34                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31  | 30  | 29  | 28     | 27        | 26  | 25  | 24  |

|--------|-----|-----|-----|--------|-----------|-----|-----|-----|

|        |     |     |     | BASEAD | DR[31:24] |     |     |     |

| Access | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

|        |     |     |     |        |           |     |     |     |

| Bit    | 23  | 22  | 21  | 20     | 19        | 18  | 17  | 16  |

|        |     |     |     | BASEAD | DR[23:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

|        |     |     |     |        |           |     |     |     |

| Bit    | 15  | 14  | 13  | 12     | 11        | 10  | 9   | 8   |

|        |     |     |     | BASEAD | DR[15:8]  |     |     |     |

| Access | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

|        |     |     |     |        |           |     |     |     |

| Bit    | 7   | 6   | 5   | 4      | 3         | 2   | 1   | 0   |

|        |     |     |     | BASEAD | DDR[7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W    | R/W       | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0      | 0         | 0   | 0   | 0   |

|        |     |     |     |        |           |     |     |     |

Bits 31:0 - BASEADDR[31:0] Descriptor Memory Base Address

These bits store the Descriptor memory section base address. The value must be 128-bit aligned.

# **DMAC – Direct Memory Access Controller**

|        | Offset:<br>Property: | 0x08<br>-      |                  |            |            |              |            |        |

|--------|----------------------|----------------|------------------|------------|------------|--------------|------------|--------|

|        | The DSTAD            | DR register of | fset is relative | to (BASEAD | DR or WRBA | .DDR) + Char | nel Number | * 0x10 |

| Bit    | 31                   | 30             | 29               | 28         | 27         | 26           | 25         | 24     |

|        |                      |                |                  | DSTADE     | DR[31:24]  |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

| Bit    | 23                   | 22             | 21               | 20         | 19         | 18           | 17         | 16     |

|        |                      |                |                  | DSTADE     | DR[23:16]  |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

|        |                      |                |                  |            |            |              |            |        |

| Bit    | 15                   | 14             | 13               | 12         | 11         | 10           | 9          | 8      |

|        |                      |                |                  | DSTADI     | DR[15:8]   |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

|        | _                    |                | _                |            |            |              |            |        |

| Bit    | 7                    | 6              | 5                | 4          | 3          | 2            | 1          | 0      |

|        |                      |                |                  | DSTAD      | DR[7:0]    |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

#### 22.10.4 Block Transfer Destination Address

DSTADDR

Name:

#### Bits 31:0 – DSTADDR[31:0] Transfer Destination Address

This bit group holds the destination address corresponding to the last beat transfer address in the block transfer.

A multicast match will be signaled if the multicast hash enable bit is set, da[0] is logic 1 and the hash index points to a bit set in the Hash register.

A unicast match will be signaled if the unicast hash enable bit is set, da[0] is logic 0 and the hash index points to a bit set in the Hash register.

To receive all multicast frames, the Hash register should be set with all ones and the multicast hash enable bit should be set in the Network Configuration register.

#### 24.6.10 Copy all Frames (Promiscuous Mode)

If the Copy All Frames bit is set in the Network Configuration register then all frames (except those that are too long, too short, have FCS errors or have GRXER asserted during reception) will be copied to memory. Frames with FCS errors will be copied if bit 26 is set in the Network Configuration register.

#### 24.6.11 Disable Copy of Pause Frames

Pause frames can be prevented from being written to memory by setting the disable copying of pause frames control bit 23 in the Network Configuration register. When set, pause frames are not copied to memory regardless of the Copy All Frames bit, whether a hash match is found, a type ID match is identified or if a destination address match is found.

#### 24.6.12 VLAN Support

The following table describes an Ethernet encoded 802.1Q VLAN tag.

#### Table 24-4. 802.1Q VLAN Tag

| TPID (Tag Protocol Identifier) 16 bits | TCI (Tag Control Information) 16 bits                 |

|----------------------------------------|-------------------------------------------------------|

| 0x8100                                 | First 3 bits priority, then CFI bit, last 12 bits VID |

The VLAN tag is inserted at the 13th byte of the frame adding an extra four bytes to the frame. To support these extra four bytes, the GMAC can accept frame lengths up to 1536 bytes by setting bit 8 in the Network Configuration register.

If the VID (VLAN identifier) is null (0x000) this indicates a priority-tagged frame.

The following bits in the receive buffer descriptor status word give information about VLAN tagged frames:-

- Bit 21 set if receive frame is VLAN tagged (i.e., type ID of 0x8100).

- Bit 20 set if receive frame is priority tagged (i.e., type ID of 0x8100 and null VID). (If bit 20 is set, bit 21 will be set also.)

- Bit 19, 18 and 17 set to priority if bit 21 is set.

- Bit 16 set to CFI if bit 21 is set.

The GMAC can be configured to reject all frames except VLAN tagged frames by setting the discard non-VLAN frames bit in the Network Configuration register.

#### 24.6.13 Wake on LAN Support

The receive block supports Wake on LAN by detecting the following events on incoming receive frames:

- Magic packet

- Address Resolution Protocol (ARP) request to the device IP address

- Specific address 1 filter match

- Multicast hash filter match

#### 24.9.9 GMAC Receive Status Register

| Name:     | RSR        |

|-----------|------------|

| Offset:   | 0x020      |

| Reset:    | 0x00000000 |

| Property: | -          |

This register, when read, provides receive status details. Once read, individual bits may be cleared by writing a '1' to them. It is not possible to set a bit to '1' by writing to this register.

| Bit    | 31 | 30 | 29 | 28 | 27  | 26    | 25  | 24  |

|--------|----|----|----|----|-----|-------|-----|-----|

|        |    |    |    |    |     |       |     |     |

| Access |    |    |    |    |     |       |     |     |

| Reset  |    |    |    |    |     |       |     |     |

|        |    |    |    |    |     |       |     |     |

| Bit    | 23 | 22 | 21 | 20 | 19  | 18    | 17  | 16  |

|        |    |    |    |    |     |       |     |     |

| Access |    |    |    |    |     |       |     |     |

| Reset  |    |    |    |    |     |       |     |     |

|        |    |    |    |    |     |       |     |     |

| Bit    | 15 | 14 | 13 | 12 | 11  | 10    | 9   | 8   |

|        |    |    |    |    |     |       |     |     |

| Access |    |    |    |    |     |       |     |     |

| Reset  |    |    |    |    |     |       |     |     |

|        |    |    |    |    |     |       |     |     |

| Bit    | 7  | 6  | 5  | 4  | 3   | 2     | 1   | 0   |

|        |    |    |    |    | HNO | RXOVR | REC | BNA |

| Access |    |    |    |    | R/W | R/W   | R/W | R/W |

| Reset  |    |    |    |    | 0   | 0     | 0   | 0   |

#### Bit 3 – HNO HRESP Not OK

This bit is set when the DMA block sees HRESP not OK.

This bit is cleared by writing a '1' to it.

#### Bit 2 - RXOVR Receive Overrun

This bit is set if the receive status was not taken at the end of the frame. The buffer will be recovered if an overrun occurs.

This bit is cleared by writing a '1' to it.

#### Bit 1 – REC Frame Received

This bit is set to when one or more frames have been received and placed in memory.

This bit is cleared by writing a '1' to it.

#### Bit 0 – BNA Buffer Not Available

When this bit is set, an attempt was made to get a new buffer and the pointer indicated that it was owned by the processor. The DMA will re-read the pointer each time an end of frame is received until a valid pointer is found. This bit is set following each descriptor read attempt that fails, even if consecutive pointers are unsuccessful and software has in the mean time cleared the status flag.

© 2018 Microchip Technology Inc.

**OSCCTRL – Oscillators Controller**

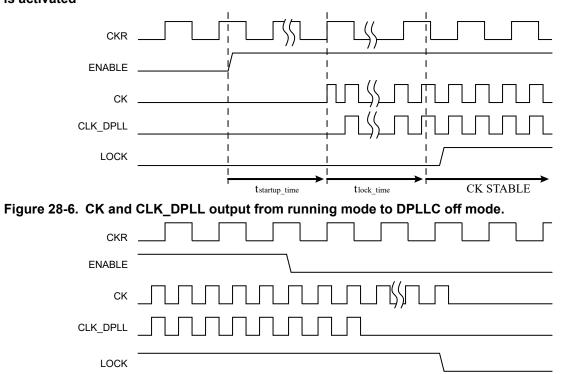

# Figure 28-5. CK and CLK\_DPLL output from DPLL off mode to running mode when wake up fast is activated

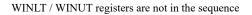

### **Operating modes**

The DPLLn will behave differently in different sleep modes based on the settings of DPLLnCTRLA.RUNSTDBY, DPLLnCTRLA.ONDEMAND and DPLLnCTRLA.ENABLE.

| DPLLCTRLA.RUNSTD<br>BY | DPLLCTRLA.ONDEMA<br>ND | DPLLCTRLA.ENABLE | Sleep Behavior                                                                                   |

|------------------------|------------------------|------------------|--------------------------------------------------------------------------------------------------|

| -                      | -                      | 0                | Disabled                                                                                         |

| 0                      | 0                      | 1                | Always run in Idle Sleep<br>modes. Run in Standby<br>Sleep mode if requested<br>by a peripheral. |

| 0                      | 1                      | 1                | Only run in Idle or<br>Standby Sleep modes if<br>requested by a<br>peripheral.                   |

| 1                      | 0                      | 1                | Always run in Idle and Standby Sleep modes.                                                      |

| 1                      | 1                      | 1                | Only run in Idle or<br>Standby Sleep modes if<br>requested by a<br>peripheral.                   |

PORT - I/O Pin Controller

| Offset | Name     | Bit Pos. |        |  |        |      |        |

|--------|----------|----------|--------|--|--------|------|--------|

| 0x59   | PINCFG25 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5A   | PINCFG26 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5B   | PINCFG27 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5C   | PINCFG28 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5D   | PINCFG29 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5E   | PINCFG30 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

| 0x5F   | PINCFG31 | 7:0      | DRVSTR |  | PULLEN | INEN | PMUXEN |

## 32.8 PORT Pin Groups and Register Repetition

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

## 32.9 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 32.5.8 Register Access Protection.

## Bit 0 – PMUXEN Peripheral Multiplexer Enable

This bit enables or disables the peripheral multiplexer selection set in the Peripheral Multiplexing register (PMUXn) to enable or disable alternative peripheral control over an I/O pin direction and output drive value.

Writing a zero to this bit allows the PORT to control the pad direction via the Data Direction register (DIR) and output drive value via the Data Output Value register (OUT). The peripheral multiplexer value in PMUXn is ignored. Writing '1' to this bit enables the peripheral selection in PMUXn to control the pad. In this configuration, the physical pin state may still be read from the Data Input Value register (IN) if PINCFGn.INEN is set.

| Value | Description                                                                                                                          |

|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The peripheral multiplexer selection is disabled, and the PORT registers control the direction and output drive value.               |

| 1     | The peripheral multiplexer selection is enabled, and the selected peripheral function controls the direction and output drive value. |

# **QSPI - Quad Serial Peripheral Interface**

| Value | Description                                                                           |

|-------|---------------------------------------------------------------------------------------|

| 0     | Data is captured on the leading edge of SCK and changed on the following edge of SCK. |

| 1     | Data is changed on the leading edge of SCK and captured on the following edge of SCK. |

### Bit 0 – CPOL Clock Polarity

CPOL is used to determine the inactive state value of the serial clock (SCK). It is used with CPHA to produce the required clock/data relationship between master and slave devices.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The inactive state value of SCK is logic level zero.  |

| 0     | The inactive state value of SCK is logic level 'one'. |

# AES – Advanced Encryption Standard

### 42.8.1 Control A

Name:CTRLAOffset:0x00Reset:0x0000000Property:PAC Write-Protection, Enable-protected

| Bit    | 31  | 30        | 29     | 28  | 27           | 26     | 25     | 24      |

|--------|-----|-----------|--------|-----|--------------|--------|--------|---------|

|        |     |           |        |     |              |        |        |         |

| Access |     |           |        |     |              |        |        |         |

| Reset  |     |           |        |     |              |        |        |         |

|        |     |           |        |     |              |        |        |         |

| Bit    | 23  | 22        | 21     | 20  | 19           | 18     | 17     | 16      |

|        |     |           |        |     |              | CTYP   | E[3:0] |         |

| Access |     |           |        |     | R/W          | R/W    | R/W    | R/W     |

| Reset  |     |           |        |     | 0            | 0      | 0      | 0       |

|        |     |           |        |     |              |        |        |         |

| Bit    | 15  | 14        | 13     | 12  | 11           | 10     | 9      | 8       |

|        |     | XORKEY    | KEYGEN | LOD | STARTMODE    | CIPHER | KEYSI  | ZE[1:0] |

| Access |     | R/W       | R/W    | R/W | R/W          | R/W    | R/W    | R/W     |

| Reset  |     | 0         | 0      | 0   | 0            | 0      | 0      | 0       |

|        |     |           |        |     |              |        |        |         |

| Bit    | 7   | 6         | 5      | 4   | 3            | 2      | 1      | 0       |

|        |     | CFBS[2:0] |        |     | AESMODE[2:0] |        | ENABLE | SWRST   |

| Access | R/W | R/W       | R/W    | R/W | R/W          | R/W    | R/W    | R/W     |

| Reset  | 0   | 0         | 0      | 0   | 0            | 0      | 0      | 0       |

### Bits 19:16 - CTYPE[3:0] Counter Measure Type

| Value | Name            | Description              |

|-------|-----------------|--------------------------|

| XXX0  | CTYPE1 disabled | Countermeasure1 disabled |

| XXX1  | CTYPE1 enabled  | Countermeasure1 enabled  |

| XXOX  | CTYPE2 disabled | Countermeasure2 disabled |

| XX1X  | CTYPE2 enabled  | Countermeasure2 enabled  |

| XOXX  | CTYPE3 disabled | Countermeasure3 disabled |

| X1XX  | CTYPE3 enabled  | Countermeasure3 enabled  |

| 0XXX  | CTYPE4 disabled | Countermeasure4 disabled |

| 1XXX  | CTYPE4 enabled  | Countermeasure4 enabled  |

#### Bit 14 – XORKEY XOR Key Operation

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 0     | No effect                                                               |

| 1     | The user keyword gets XORed with the previous keyword register content. |

Bit 13 – KEYGEN Last Key Generation

# Public Key Cryptography Controller (PUKCC)

#### 43.3.7.3.5 Code Example

#### 43.3.7.3.6 Constraints

No overlapping between either input and output are allowed. The following conditions must be avoided to ensure the service works correctly:

- nu1ModBase, nu1CnsBase, nu1PointABase, nu1ABBase, nu1Workspace are not aligned on 32-bit boundaries

- {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1PointABase, 3\*u2ModLength+ 12}, {nu1ABBase, 2\*u2ModLength + 8}, {nu1Workspace, <WorkspaceLength>} are not in Crypto RAM

- u2ModLength is either: < 12, > 0xffc or not a 32-bit length

- All overlapping between {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1PointABase, 3\*u2ModLength + 12}, {nu1ABase, u2ModLength + 4} and {nu1Workspace, 4\*u2ModLength + 28}

#### 43.3.7.3.7 Status Returned Values

#### Table 43-97. GF2NEccDblFast Service Return Codes

| Returned Status | Importance | Meaning                                 |

|-----------------|------------|-----------------------------------------|

| PUKCL_OK        | _          | The computation passed without problem. |

#### 43.3.7.4 Scalar Point Multiply

#### 43.3.7.4.1 Purpose

This service is used to multiply a point by an integral constant K on a given elliptic curve over GF(2<sup>n</sup>).

#### 43.3.7.4.2 How to Use the Service

#### 43.3.7.4.3 Description

The operation performed is:

$Pt_C = K \times Pt_A$

In this computation, the following parameters need to be provided:

- A the input point is filled in projective coordinates (X,Y,Z) (pointed by {nu1PointABase, 3\*u2ModLength + 12}). This point can be the Infinite Point.

- Cns the Fast Modular Constant filled (pointed by {nu1CnsBase,u2ModLength + 8})

# ADC – Analog-to-Digital Converter

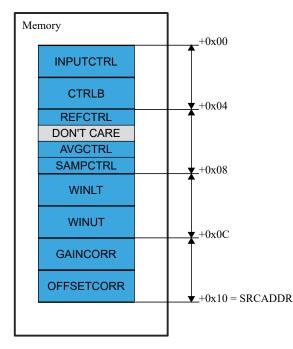

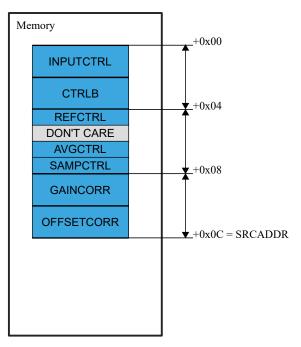

- Enable the source address increment options (DMAC.BTCTRL.SRCINC = 1, DMAC.BTCTRL.STEPSEL = SRC, DMAC.BTCTRL.STEPSIZE = X1).

- Disable the destination address increment (DMAC.BTCTRL.DSTINC=0).

- Set the block transfer count value (DMAC.BTCNT).

- Set the block transfer source address (DMAC.SRCADDR), as described in the DMAC Addressing section. The address corresponds to the memory section from where the DMA reads the data.

- Select the ADC.DSEQDATA address as value for the block transfer destination address (DMAC.DSTADDR = ADC.DSEQDATA address).

- Select the channel single transfer type (DMAC.CHCTRLA.BURSTLEN=SINGLE)

- Select the channel burst trigger action (DMAC.CHCTRLA.TRIGACT=BURST)

- Select the ADC DMA Sequencing trigger as channel trigger source (DMAC.CHCTRLA.TRIGSRC=DSEQ)

- Enable optional channel interrupts (DMAC.CHINTENSET)

- Enable the corresponding DMA channel (DMAC.CHCTRLA.ENABLE)

When an ADC condition is enabled to trigger a DMA transfer, one word (32-bit) will be read by the DMA from the memory source location. Since the source address is incrementing by 0x1, the data memory must be organized in a contiguous memory area. As consequence, if an ADC group of registers does not generate any DMA trigger, no data must be reserved in the memory area for this register group. The next figure shows an example of memory organization when all ADC registers are part of the sequence, and a second example where WINLT and WINUT registers are not part of the sequence.

All registers are in the sequence

#### **Automatic Start Conversion**

By default, a new conversion starts when a new start software or event trigger is received. It is also possible to automatically enable an ADC conversion by writing '1' to the AUTOSTART bit in DSEQCTRL register (DSEQCTRL.AUTOSTART). When set, the ADC automatically starts a new conversion when a DMA sequence is complete.

register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register.

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the DAC Controller is reset. See 47.8.6 INTFLAG for details on how to clear interrupt flags.

All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the INTFLAG register to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated.

### 47.6.6 Events

The DAC Controller can generate the following output events:

- Data Buffer 0 Empty (EMPTY0): Generated when the internal data buffer of DAC0 is empty. Refer to 47.6.4 DMA Operation for details.

- Data Buffer 1 Empty (EMPTY1): Generated when the internal data buffer of DAC1 is empty. Refer to 47.6.4 DMA Operation for details.

- Filter 0 Result Ready (RESRDY0): Generated when standalone filter 0 result is ready.

- Filter 1 Result Ready (RESRDY1): Generated when standalone filter 1 result is ready.

Writing a '1' to an Event Output bit in the Event Control Register (EVCTRL.EMPTYEOx) enables the corresponding output event. Writing a '0' to this bit disables the corresponding output event. Refer to the Event System chapter for details on configuring the event system.

The DAC Controller can take the following actions on an input event:

- DAC0 Start Conversion (START0): DATABUF0 value is transferred into DATA0 as soon as DAC0 is ready for the next conversion, and then conversion is started. START0 is considered as asynchronous to GCLK\_DAC, thus it is resynchronized in the DAC Controller. Refer to 47.6.2.4 Digital to Analog Conversion for details.

- DAC1 Start Conversion (START1): DATABUF1 value is transferred into DATA1 as soon as DAC1 is ready for the next conversion, and then conversion is started. START1 is considered as asynchronous to GCLK\_DAC, thus it is resynchronized in the DAC Controller. Refer to 47.6.2.4 Digital to Analog Conversion for details.

Writing a '1' to an Event Input bit in the Event Control register (EVCTRL.STARTEIx) enables the corresponding action on input event. Writing a '0' to this bit will disable the corresponding action on input event.

**Note:** When several events are connected to the DAC Controller, the enabled action will be taken on any of the incoming events.

By default, DAC Controller detects rising edge events. Falling edge detection can be enabled by writing '1' to EVCTRL.INVEIx.

Note that if an event occurs before startup time is completed, DATAx is loaded but start of conversion is ignored.

#### 47.6.7 Sleep Mode Operation

If the Run In Standby bit in the DAC Control x register DACCCTRLx.RUNSTDBY=1, the DACx will continue the conversions in standby sleep mode.

If DACCCTRLx.RUNSTDBY=0, the DACx will stop conversions in standby sleep mode.

#### 48.7.3.5 Interrupt Enable Clear

Name:INTENCLROffset:0x08Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7 | 6 | 5   | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|-----|-----|---|---|-----|-----|

|        |   |   | MC1 | MC0 |   |   | ERR | OVF |

| Access |   |   | R/W | R/W |   |   | R/W | R/W |

| Reset  |   |   | 0   | 0   |   |   | 0   | 0   |

**Bit 5 – MC1** Match or Capture Channel x Interrupt Enable Writing a '0' to these bits has no effect.

Writing a '1' to MCx will clear the corresponding Match or Capture Channel x Interrupt Enable bit, which disables the Match or Capture Channel x interrupt.

| V | /alue | Description                                           |

|---|-------|-------------------------------------------------------|

| 0 |       | The Match or Capture Channel x interrupt is disabled. |

| 1 |       | The Match or Capture Channel x interrupt is enabled.  |

Bit 4 – MC0 Match or Capture Channel x Interrupt Enable

Writing a '0' to these bits has no effect.

Writing a '1' to MCx will clear the corresponding Match or Capture Channel x Interrupt Enable bit, which disables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

#### **Bit 1 – ERR** Error Interrupt Disable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Error Interrupt Enable bit, which disables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

Bit 0 – OVF Overflow Interrupt Disable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt request.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### 49.8.9 Event Control

| Name:     | EVCTRL                                 |

|-----------|----------------------------------------|

| Offset:   | 0x20                                   |

| Reset:    | 0x0000000                              |

| Property: | PAC Write-Protection, Enable-Protected |

| Bit    | 31    | 30      | 29     | 28          | 27    | 26    | 25    | 24    |

|--------|-------|---------|--------|-------------|-------|-------|-------|-------|

|        |       |         | MCEOx  | MCEOx       | MCEOx | MCEOx | MCEOx | MCEOx |

| Access |       |         | R/W    | R/W         | R/W   | R/W   | R/W   | R/W   |

| Reset  |       |         | 0      | 0           | 0     | 0     | 0     | 0     |

|        |       |         |        |             |       |       |       |       |

| Bit    | 23    | 22      | 21     | 20          | 19    | 18    | 17    | 16    |

|        |       |         | MCEIx  | MCEIx       | MCEIx | MCEIx | MCEIx | MCEIx |

| Access |       |         | R/W    | R/W         | R/W   | R/W   | R/W   | R/W   |

| Reset  |       |         | 0      | 0           | 0     | 0     | 0     | 0     |

|        |       |         |        |             |       |       |       |       |

| Bit    | 15    | 14      | 13     | 12          | 11    | 10    | 9     | 8     |

|        | TCEIx | TCEIx   | TCINVx | TCINVx      |       | CNTEO | TRGEO | OVFEO |

| Access | R/W   | R/W     | R/W    | R/W         |       | R/W   | R/W   | R/W   |

| Reset  | 0     | 0       | 0      | 0           |       | 0     |       | 0     |

|        |       |         |        |             |       |       |       |       |

| Bit    | 7     | 6       | 5      | 4           | 3     | 2     | 1     | 0     |

|        | CNTS  | EL[1:0] |        | EVACT1[2:0] |       |       |       |       |

| Access | R/W   | R/W     | R/W    | R/W         | R/W   | R/W   | R/W   | R/W   |

| Reset  | 0     | 0       | 0      | 0           | 0     | 0     | 0     | 0     |

**Bits 29,28,27,26,25,24 – MCEOx** Match or Capture Channel x Event Output Enable These bits control if the Match/capture event on channel x is enabled and will be generated for every match or capture.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | Match/capture x event is disabled and will not be generated.                                   |

| 1     | Match/capture x event is enabled and will be generated for every compare/capture on channel x. |

**Bits 21,20,19,18,17,16 – MCEIx** Match or Capture Channel x Event Input Enable These bits indicate if the Match/capture x incoming event is enabled

These bits are used to enable match or capture input events to the CCx channel of TCC.

| Value | Description                   |

|-------|-------------------------------|

| 0     | Incoming events are disabled. |

| 1     | Incoming events are enabled.  |

**Bits 15,14 – TCEIx** Timer/Counter Event Input x Enable This bit is used to enable input event x to the TCC.

Electrical Characteristics at 85°C

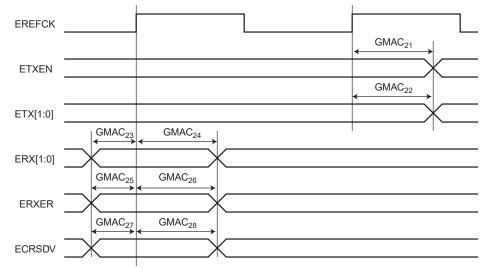

| Symbol             | Parameter                                 | Min. | Max. | Units |

|--------------------|-------------------------------------------|------|------|-------|

| GMAC <sub>25</sub> | Setup for ERXER<br>from EREFCK<br>rising  | 4    | -    |       |

| GMAC <sub>26</sub> | Hold for ERXER<br>from EREFCK<br>rising   | 2    | -    |       |

| GMAC <sub>27</sub> | Setup for ECRSDV<br>from EREFCK<br>rising | 4    | -    |       |

| GMAC <sub>28</sub> | Hold for ECRSDV<br>from EREFCK<br>rising  | 2    | -    |       |

### Figure 54-19. GMAC RMII Mode Signals

### 54.13.5 I<sup>2</sup>S Characteristics

## Table 54-59. I<sup>2</sup>S Timing Characteristics and Requirements (see Note 1)

| Name                 | Description                      | Mode                                           | VDD = 1.8V |      |      | VDD = 3.3V |      |      | Units |

|----------------------|----------------------------------|------------------------------------------------|------------|------|------|------------|------|------|-------|

|                      |                                  |                                                | Min.       | Тур. | Max. | Min.       | Тур. | Max. |       |

| t <sub>M_MCKOR</sub> | I2S MCK rise time <sup>(2)</sup> | Master mode /<br>Capacitive load CL = 20<br>pF | -          | -    | 5.41 | -          | -    | 2.68 | ns    |

| t <sub>M_MCKOF</sub> | I2S MCK fall time <sup>(2)</sup> | Master mode /<br>Capacitive load CL = 20<br>pF | -          | -    | 5.84 | -          | -    | 2.81 | ns    |

| d <sub>M_MCKO</sub>  | I2S MCK duty cycle               | Master mode                                    | -          | 50.0 | -    | -          | 50.0 | -    | %     |

© 2018 Microchip Technology Inc.