#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                            |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                     |

| Number of I/O              | 81                                                                          |

| Program Memory Size        | 1MB (1M x 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | •                                                                           |

| RAM Size                   | 256K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                               |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 100-TQFP                                                                    |

| Supplier Device Package    | 100-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd51n20a-au   |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

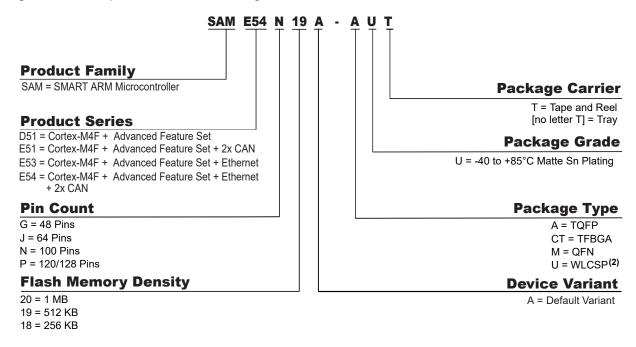

## 2. Ordering Information

Figure 2-1. Composition of the Ordering Numbers<sup>(1)</sup>

#### Note:

- 1. Not all combinations are valid. The available device part numbers are listed in Configuration Summary.

- 2. Devices in the WLCSP package include a factory programmed Bootloader. Please contact your local Microchip sales office for more information.

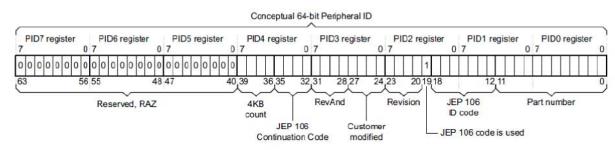

### 12.10 Device Identification

Device identification relies on the ARM CoreSight component identification scheme, which allows the chip to be identified as a SAM device implementing a DSU. The DSU contains identification registers to differentiate the device.

#### 12.10.1 CoreSight Identification

A system-level ARM<sup>®</sup> CoreSight<sup>™</sup> ROM table is present in the device to identify the vendor and the chip identification method. Its address is provided in the MEM-AP BASE register inside the ARM Debug Access Port. The CoreSight ROM implements a 64-bit conceptual ID composed as follows from the PID0 to PID7 CoreSight ROM Table registers:

#### Figure 12-5. Conceptual 64-bit Peripheral ID

| Field           | Size | Description                                                                                                                                                                                                                                                        | Location  |

|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| JEP-106 CC code | 4    | Continuation code: 0x0                                                                                                                                                                                                                                             | PID4      |

| JEP-106 ID code | 7    | Device ID: 0x1F                                                                                                                                                                                                                                                    | PID1+PID2 |

| 4KB count       | 4    | Indicates that the CoreSight component is a ROM: 0x0                                                                                                                                                                                                               | PID4      |

| RevAnd          | 4    | Not used; read as 0                                                                                                                                                                                                                                                | PID3      |

| CUSMOD          | 4    | Not used; read as 0                                                                                                                                                                                                                                                | PID3      |

| PARTNUM         | 12   | Contains 0xCD0 to indicate that DSU is present                                                                                                                                                                                                                     | PID0+PID1 |

| REVISION        | 4    | DSU revision (starts at 0x0 and increments by 1 at both major<br>and minor revisions). Identifies DSU identification method<br>variants. If 0x0, this indicates that device identification can be<br>completed by reading the Device Identification register (DID) | PID2      |

#### Table 12-2. Conceptual 64-Bit Peripheral ID Bit Descriptions

For more information, refer to the ARM Debug Interface Version 5 Architecture Specification.

#### 12.10.2 Chip Identification Method

The DSU DID register identifies the device by implementing the following information:

- Processor identification

- Product family identification

- Product series identification

- Device select

#### 19.6.6 Interrupts

The SUPC has the following interrupt sources, which are either synchronous or asynchronous wake-up sources:

- VDDCORE Voltage Ready (VCORERDY), asynchronous

- Voltage Regulator Ready (VREGRDY) asynchronous

- BOD33 Ready (BOD33RDY), synchronous

- BOD33 Detection (BOD33DET), asynchronous

- BOD33 Synchronization Ready (B33SRDY), synchronous

- BOD12 Ready (BOD12RDY), synchronous

- BOD12 Detection (BOD12DET), asynchronous

- BOD12 Synchronization Ready (BOD12SRDY), synchronous

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when the interrupt condition occurs.

Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set register (INTENSET), and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear register (INTENCLR).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled, or the SUPC is reset. See the INTFLAG register for details on how to clear interrupt flags. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated.

#### 19.6.7 Synchronization

The prescaler counters that are used to trigger brown-out detections operate asynchronously from the peripheral bus. As a consequence, the BOD33 Enable bit (BOD33.ENABLE) need synchronization when written.

The Write-Synchronization of the Enable bit is triggered by writing a '1' to the Enable bit of the BOD33 Control register. The Synchronization Ready bit (STATUS.B33SRDY) in the STATUS register will be cleared when the Write-Synchronization starts, and set again when the Write-Synchronization is complete. Writing to the same register while the Write-Synchronization is ongoing (STATUS.B33SRDY is '0') will generate a PAC error without stalling the APB bus.

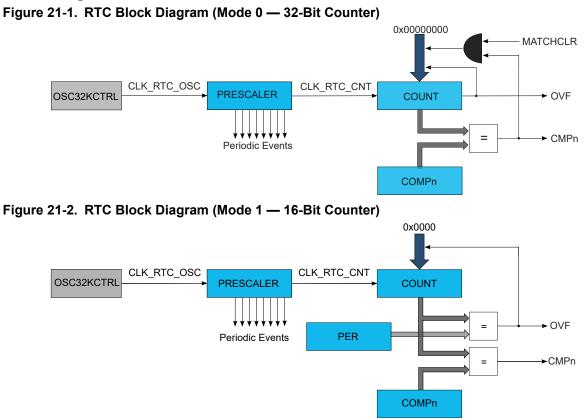

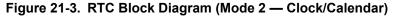

## **RTC – Real-Time Counter**

## 21.3 Block Diagram

#### 21.8.4 Interrupt Enable Clear in COUNT32 mode (CTRLA.MODE=0)

Name:INTENCLROffset:0x08Reset:0x0000Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 15  | 14     | 13  | 12  | 11     | 10  | 9   | 8      |

|--------|-----|--------|-----|-----|--------|-----|-----|--------|

|        | OVF | TAMPER |     |     |        |     | CMP | n[1:0] |

| Access | R/W | R/W    |     |     |        |     | R/W | R/W    |

| Reset  | 0   | 0      |     |     |        |     | 0   | 0      |

| Bit    | 7   | 6      | 5   | 4   | 3      | 2   | 1   | 0      |

|        |     |        |     | PER | n[7:0] |     |     |        |

| Access | R/W | R/W    | R/W | R/W | R/W    | R/W | R/W | R/W    |

| Reset  | 0   | 0      | 0   | 0   | 0      | 0   | 0   | 0      |

## Bit 15 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overflow Interrupt Enable bit, which disables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### Bit 14 – TAMPER Tamper Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this but will clear the Tamper Interrupt Enable bit, which disables the Tamper interrupt.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The Tamper interrupt is disabled. |

| 1     | The Tamper interrupt is enabled.  |

**Bits 9:8 – CMPn[1:0]** Compare n Interrupt Enable [n = 1..0] Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Compare n Interrupt Enable bit, which disables the Compare n interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Compare n interrupt is disabled |

| 1     | The Compare n interrupt is enabled. |

**Bits 7:0 – PERn[7:0]** Periodic Interval n Interrupt Enable [n = 7..0] Writing a '0' to this bit has no effect.

#### 21.10.6 Interrupt Flag Status and Clear in COUNT16 mode (CTRLA.MODE=1)

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x0C<br>0x0000<br>- |     |     |        |     |        |     |

|--------|-----------------------------------------|--------------------------------|-----|-----|--------|-----|--------|-----|

| Bit    | 15                                      | 14                             | 13  | 12  | 11     | 10  | 9      | 8   |

|        | OVF                                     | TAMPER                         |     |     |        | CMP | า[3:0] |     |

| Access | R/W                                     | R/W                            |     |     | R/W    | R/W | R/W    | R/W |

| Reset  | 0                                       | 0                              |     |     | 0      | 0   | 0      | 0   |

|        |                                         |                                |     |     |        |     |        |     |

| Bit    | 7                                       | 6                              | 5   | 4   | 3      | 2   | 1      | 0   |

|        |                                         |                                |     | PER | n[7:0] |     |        |     |

| Access | R/W                                     | R/W                            | R/W | R/W | R/W    | R/W | R/W    | R/W |

| Reset  | 0                                       | 0                              | 0   | 0   | 0      | 0   | 0      | 0   |

#### Bit 15 – OVF Overflow

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after an overflow condition occurs, and an interrupt request will be generated if INTENCLR/SET.OVF is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Overflow interrupt flag.

#### Bit 14 – TAMPER Tamper

This flag is set after a tamper condition occurs, and an interrupt request will be generated if INTENCLR.TAMPER/ INTENSET.TAMPER is one.

Writing a '0' to this bit has no effect.

Writing a one to this bit clears the Tamper interrupt flag.

#### Bits 11:8 - CMPn[3:0] Compare n [n = 3..0]

This flag is cleared by writing a '1' to the flag.

This flag is set on the next CLK\_RTC\_CNT cycle after a match with the compare condition, and an interrupt request will be generated if INTENCLR/SET.COMPn is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Compare n interrupt flag.

#### Bits 7:0 – PERn[7:0] Periodic Interval n [n = 7..0]

This flag is cleared by writing a '1' to the flag.

This flag is set on the 0-to-1 transition of prescaler bit [n+2], and an interrupt request will be generated if INTENCLR/SET.PERx is one.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Periodic Interval n interrupt flag.

# SAMD5x/E5x Family Data Sheet

## **DMAC – Direct Memory Access Controller**

| Offset | Name         | Bit Pos. |  |  |        |      |       |      |

|--------|--------------|----------|--|--|--------|------|-------|------|

| 0x023B |              |          |  |  |        |      |       |      |

| 0x023C | CHINTENCLR31 | 7:0      |  |  |        | SUSP | TCMPL | TERR |

| 0x023D | CHINTENSET31 | 7:0      |  |  |        | SUSP | TCMPL | TERR |

| 0x023E | CHINTFLAG31  | 7:0      |  |  |        | SUSP | TCMPL | TERR |

| 0x023F | CHSTATUS31   | 7:0      |  |  | CRCERR | FERR | BUSY  | PEND |

## 22.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 22.5.8 Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

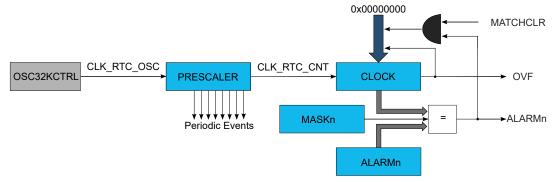

### 24.3 Block Diagram

Figure 24-1. Block Diagram

## 24.4 Signal Description

The GMAC includes the following signal interfaces:

- MII, RMII to an external PHY

- MDIO interface for external PHY management

- Slave APB interface for accessing GMAC registers

- Master AHB interface for memory access

- GTSUCOMP signal for TSU timer count value comparison

#### Table 24-1. GMAC Connections in Different Modes

| Signal Name | Function                          | MII      | RMII     |

|-------------|-----------------------------------|----------|----------|

| GTXCK       | Transmit Clock or Reference Clock | ТХСК     | REFCK    |

| GTXEN       | Transmit Enable                   | TXEN     | TXEN     |

| GTX[30]     | Transmit Data                     | TXD[3:0] | TXD[1:0] |

| GTXER       | Transmit Coding Error             | TXER     | Not Used |

| GRXCK       | Receive Clock                     | RXCK     | Not Used |

| GRXDV       | Receive Data Valid                | RXDV     | CRSDV    |

| GRX[30]     | Receive Data                      | RXD[3:0] | RXD[1:0] |

| GRXER       | Receive Error                     | RXER     | RXER     |

| GCRS        | Carrier Sense and Data Valid      | CRS      | Not Used |

| GCOL        | Collision Detect                  | COL      | Not Used |

|                        | Name:<br>Offset:<br>Reset:<br>Property: | SAMT1<br>0x0CC<br>0x00000000<br>- |     |      |         |     |     |     |

|------------------------|-----------------------------------------|-----------------------------------|-----|------|---------|-----|-----|-----|

| Bit                    | 31                                      | 30                                | 29  | 28   | 27      | 26  | 25  | 24  |

|                        |                                         |                                   |     |      |         |     |     |     |

| Access                 |                                         |                                   |     |      |         |     |     |     |

| Reset                  |                                         |                                   |     |      |         |     |     |     |

| Bit                    | 23                                      | 22                                | 21  | 20   | 19      | 18  | 17  | 16  |

|                        |                                         |                                   |     |      |         |     |     |     |

| Access                 |                                         | -                                 |     |      |         |     | •   |     |

| Reset                  |                                         |                                   |     |      |         |     |     |     |

| Bit                    | 15                                      | 14                                | 13  | 12   | 11      | 10  | 9   | 8   |

|                        |                                         |                                   |     | ADDF | R[15:8] |     |     |     |

| Access                 | R/W                                     | R/W                               | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset                  | 0                                       | 0                                 | 0   | 0    | 0       | 0   | 0   | 0   |

| <b>D</b> <sup>14</sup> | 7                                       | 6                                 | F   | 4    | 2       | 0   | 4   | 0   |

| Bit                    | 7                                       | 6                                 | 5   | 4    | 3       | 2   | 1   | 0   |

|                        |                                         |                                   |     |      | R[7:0]  |     |     |     |

| Access                 |                                         | R/W                               | R/W | R/W  | R/W     | R/W | R/W | R/W |

| Reset                  | 0                                       | 0                                 | 0   | 0    | 0       | 0   | 0   | 0   |

## 24.9.30 GMAC Specific Address Mask 1 Top

Bits 15:0 – ADDR[15:0] Specific Address 1 Mask

Setting a bit to '1' masks the corresponding bit in the Specific Address 1 register SAT1.

|                 | Name:<br>Offset:<br>Reset:<br>Property: | OFR<br>0x188<br>0x00000000<br>Read-Only |    |     |        |    |    |        |

|-----------------|-----------------------------------------|-----------------------------------------|----|-----|--------|----|----|--------|

| Bit             | 31                                      | 30                                      | 29 | 28  | 27     | 26 | 25 | 24     |

| Access<br>Reset |                                         |                                         |    |     |        |    |    |        |

| Bit             | 23                                      | 22                                      | 21 | 20  | 19     | 18 | 17 | 16     |

| Access<br>Reset |                                         |                                         |    |     |        |    |    |        |

| Bit             | 15                                      | 14                                      | 13 | 12  | 11     | 10 | 9  | 8      |

|                 |                                         |                                         |    |     |        |    |    | X[9:8] |

| Access          |                                         |                                         |    |     |        |    | R  | R      |

| Reset           |                                         |                                         |    |     |        |    | 0  | 0      |

| Bit             | 7                                       | 6                                       | 5  | 4   | 3      | 2  | 1  | 0      |

|                 |                                         |                                         |    | OFR | X[7:0] |    |    |        |

| Access          |                                         | R                                       | R  | R   | R      | R  | R  | R      |

| Reset           | 0                                       | 0                                       | 0  | 0   | 0      | 0  | 0  | 0      |

#### 24.9.72 GMAC Oversized Frames Received Register

#### Bits 9:0 - OFRX[9:0] Oversized Frames Received

This pit field counts the number of frames received exceeding 1518 Bytes in length (1536 Bytes if NCFGR.MAXFS is written to '1') but do not have either a CRC error, an alignment error, nor a receive symbol error.

## SAMD5x/E5x Family Data Sheet

## PAC - Peripheral Access Controller

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAGAHB and INTFLAGn) registers is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the PAC is reset. All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. The user must read the INTFLAGAHB and INTFLAGn registers to determine which interrupt condition is present.

Note that interrupts must be globally enabled for interrupt requests to be generated.

#### **Related Links**

10.2 Nested Vector Interrupt Controller

#### 27.5.5 Events

The PAC can generate the following output event:

• Error (ERR): Generated when one of the interrupt flag registers bits is set

Writing a '1' to an Event Output bit in the Event Control Register (EVCTRL.ERREO) enables the corresponding output event. Writing a '0' to this bit disables the corresponding output event.

#### 27.5.6 Sleep Mode Operation

In Sleep mode, the PAC is kept enabled if an available bus master (CPU, DMA) is running. The PAC will continue to catch access errors from the module and generate interrupts or events.

#### 27.5.7 Synchronization

Not applicable.

## SAMD5x/E5x Family Data Sheet SERCOM USART - SERCOM Synchronous and Asyn...

#### 34.8.5 Receive Pulse Length Register

| Name:     | RXPL                                   |

|-----------|----------------------------------------|

| Offset:   | 0x0E                                   |

| Reset:    | 0x00                                   |

| Property: | Enable-Protected, PAC Write-Protection |

| Bit    | 7   | 6   | 5   | 4    | 3      | 2   | 1   | 0   |

|--------|-----|-----|-----|------|--------|-----|-----|-----|

|        |     |     |     | RXPI | _[7:0] |     |     |     |

| Access | R/W | R/W | R/W | R/W  | R/W    | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0    | 0      | 0   | 0   | 0   |

#### Bits 7:0 – RXPL[7:0] Receive Pulse Length

When the encoding format is set to IrDA (CTRLB.ENC=1), these bits control the minimum pulse length that is required for a pulse to be accepted by the IrDA receiver with regards to the serial engine clock period  $SE_{per}$ .

$PULSE \geq (RXPL + 2) \cdot SE_{per}$

## SERCOM I2C – Inter-Integrated Circuit

#### 36.8.5 Interrupt Enable Set

Name:INTENSETOffset:0x16Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7     | 6 | 5 | 4 | 3 | 2    | 1      | 0    |

|--------|-------|---|---|---|---|------|--------|------|

|        | ERROR |   |   |   |   | DRDY | AMATCH | PREC |

| Access | R/W   |   |   |   |   | R/W  | R/W    | R/W  |

| Reset  | 0     |   |   |   |   | 0    | 0      | 0    |

#### Bit 7 – ERROR Error Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                  |

|-------|------------------------------|

| 0     | Error interrupt is disabled. |

| 1     | Error interrupt is enabled.  |

#### **Bit 2 – DRDY** Data Ready Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Data Ready bit, which enables the Data Ready interrupt.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | The Data Ready interrupt is disabled. |

| 1     | The Data Ready interrupt is enabled.  |

#### Bit 1 – AMATCH Address Match Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Address Match Interrupt Enable bit, which enables the Address Match interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Address Match interrupt is disabled. |

| 1     | The Address Match interrupt is enabled.  |

#### Bit 0 – PREC Stop Received Interrupt Enable

Writing '0' to this bit has no effect.

Writing '1' to this bit will set the Stop Received Interrupt Enable bit, which enables the Stop Received interrupt.

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The Stop Received interrupt is disabled. |

| 1     | The Stop Received interrupt is enabled.  |

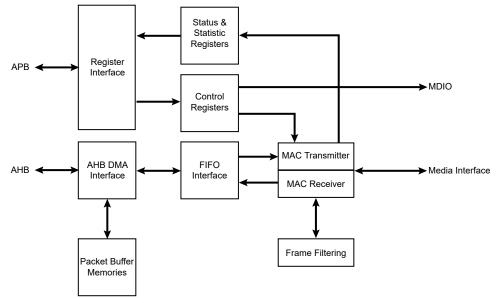

## **QSPI - Quad Serial Peripheral Interface**

## 37.3 Block Diagram

Figure 37-1. QSPI Block Diagram

## 37.4 Signal Description Table 37-1. Quad-SPI Signals

| Signal      | Description                       | Туре                  |

|-------------|-----------------------------------|-----------------------|

| SCK         | Serial Clock                      | Output                |

| CS          | Chip Select                       | Output                |

| MOSI(DATA0) | Data Output (Data Input Output 0) | Output (Input/Output) |

| MISO(DATA1) | Data Input (Data Input Output 1)  | Input (Input/Output)  |

| DATA2       | Data Input Output 2               | Input/Output          |

| DATA3       | Data Input Output 3               | Input/Output          |

**Note:** MOSI and MISO are used for single-bit SPI operation

**Note:** DATA0-DATA1 are used for Dual SPI operation

**Note:** DATA0-DATA3 are used for Quad SPI operation

Refer to the pinout table for details on the pin mapping for this peripheral. One signal can be mapped to one of several pins.

## 37.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 37.5.1 I/O Lines

Using the QSPI I/O lines requires the I/O pins to be configured.

#### 39.8.41 Tx Buffer Transmission Occurred

| Name:     | ТХВТО      |

|-----------|------------|

| Offset:   | 0xD8       |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

| Bit    | 31 | 30 | 29 | 28    | 27     | 26 | 25 | 24 |

|--------|----|----|----|-------|--------|----|----|----|

|        |    |    |    | TOn[  | 31:24] |    |    |    |

| Access | R  | R  | R  | R     | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

|        |    |    |    |       |        |    |    |    |

| Bit    | 23 | 22 | 21 | 20    | 19     | 18 | 17 | 16 |

|        |    |    |    | TOn[2 | 23:16] |    |    |    |

| Access | R  | R  | R  | R     | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

|        |    |    |    |       |        |    |    |    |

| Bit    | 15 | 14 | 13 | 12    | 11     | 10 | 9  | 8  |

|        |    |    |    | TOn   | 15:8]  |    |    |    |

| Access | R  | R  | R  | R     | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

|        |    |    |    |       |        |    |    |    |

| Bit    | 7  | 6  | 5  | 4     | 3      | 2  | 1  | 0  |

|        |    |    |    | TOn   | [7:0]  |    |    |    |

| Access | R  | R  | R  | R     | R      | R  | R  | R  |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

#### Bits 31:0 - TOn[31:0] Transmission Occurred

Each Tx Buffer has its own Transmission Occurred bit.

The bits are set when the corresponding TXBRP bit is cleared after a successful transmission.

The bits are reset when a new transmission is requested by writing '1' to the corresponding bit of register TXBAR.

## ADC – Analog-to-Digital Converter

#### 45.5.6 Events

The events are connected to the Event System.

#### **Related Links**

31. EVSYS – Event System

#### 45.5.7 Debug Operation

When the CPU is halted in debug mode the ADC will halt normal operation. The ADC can be forced to continue operation during debugging. Refer to DBGCTRL register for details.

#### **Related Links**

45.8.3 DBGCTRL

#### 45.5.8 Register Access Protection

All registers with write-access are optionally write-protected by the peripheral access controller (PAC), except the following register:

• Interrupt Flag Status and Clear (INTFLAG) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

#### **Related Links**

27. PAC - Peripheral Access Controller

#### 45.5.9 Analog Connections

I/O-pins (AINx), as well as the VREFA/VREFB/VREFC reference voltage pins are analog inputs to the ADC. Any internal reference source, such as a bandgap voltage reference, or DAC must be configured and enabled prior to its use with the ADC.

#### 45.5.10 Calibration

The BIASREFBUF, BIASR2R and BIASCOMP calibration values from the production test must be loaded from the NVM Software Calibration Area into the ADC Calibration register (CALIB) by software to achieve specified accuracy.

#### 45.6 Functional Description

#### 45.6.1 Principle of Operation

By default, the ADC provides results with 12-bit resolution. 8-bit or 10-bit results can be selected in order to reduce the conversion time, see 45.6.2.8 Conversion Timing and Sampling Rate.

The ADC has an oversampling with decimation option that can extend the resolution to 16 bits. The input values can be either internal (e.g., an internal temperature sensor) or external (connected I/O pins). The user can also configure whether the conversion should be single-ended or differential.

#### 45.6.2 Basic Operation

#### 45.6.2.1 Initialization

The following registers are enable-protected, meaning that they can only be written when the ADC is disabled (CTRLA.ENABLE=0):

## DAC – Digital-to-Analog Converter

#### 47.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x04Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7        | 6        | 5       | 4       | 3      | 2      | 1         | 0         |

|--------|----------|----------|---------|---------|--------|--------|-----------|-----------|

|        | OVERRUN1 | OVERRUN0 | RESRDY1 | RESRDY0 | EMPTY1 | EMPTY0 | UNDERRUN1 | UNDERRUN0 |

| Access | R/W      | R/W      | R/W     | R/W     | R/W    | R/W    | R/W       | R/W       |

| Reset  | 0        | 0        | 0       | 0       | 0      | 0      | 0         | 0         |

#### Bit 7 – OVERRUN1 Overrun Interrupt Enable for Filter Channel 1

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overrun Interrupt Enable for Filter Channel 1 bit, which disables the Filter 1 Overrun interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | Filter 1 Result Ready interrupt is disabled. |

| 1     | Filter 1 Result Ready interrupt is enabled.  |

#### **Bit 6 – OVERRUN0** Overrun Interrupt Enable for Filter Channel 0

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overrun Interrupt Enable for Filter Channel 0 bit, which disables the Filter 0 Overrun interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | Filter 0 Result Ready interrupt is disabled. |

| 1     | Filter 0 Result Ready interrupt is enabled.  |

#### **Bit 5 – RESRDY1** Filter Channel 1 Result Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Filter Channel 1 Result Ready Interrupt Enable bit, which disables the Filter Channel 1 Result Ready interrupt.

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | Filter 1 Result Ready interrupt is disabled. |

| 1     | Filter 1 Result Ready interrupt is enabled.  |

#### **Bit 4 – RESRDY0** Filter Channel 0 Result Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Filter Channel 0 Result Ready Interrupt Enable bit, which disables the Filter Channel 0 Result Ready interrupt.

## TCC – Timer/Counter for Control Applications

#### Bit 14 – ALOCK Auto Lock

This bit is not synchronized.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The Lock Update bit in the Control B register (CTRLB.LUPD) is not affected by overflow/ |

|       | underflow, and re-trigger events                                                        |

| 1     | CTRLB.LUPD is set to '1' on each overflow/underflow or re-trigger event.                |

#### Bits 13:12 – PRESCYNC[1:0] Prescaler and Counter Synchronization

These bits select if on re-trigger event, the Counter is cleared or reloaded on either the next GCLK\_TCCx clock, or on the next prescaled GCLK\_TCCx clock. It is also possible to reset the prescaler on re-trigger event.

These bits are not synchronized.

| Value | Name     | Description                                     |                         |

|-------|----------|-------------------------------------------------|-------------------------|

|       |          | Counter Reloaded                                | Prescaler               |

| 0x0   | GCLK     | Reload or reset Counter on next<br>GCLK         | -                       |

| 0x1   | PRESC    | Reload or reset Counter on next prescaler clock | -                       |

| 0x2   | RESYNC   | Reload or reset Counter on next<br>GCLK         | Reset prescaler counter |

| 0x3   | Reserved |                                                 |                         |

#### Bit 11 – RUNSTDBY Run in Standby

This bit is used to keep the TCC running in standby mode.

This bit is not synchronized.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The TCC is halted in standby.        |

| 1     | The TCC continues to run in standby. |

#### Bits 10:8 - PRESCALER[2:0] Prescaler

These bits select the Counter prescaler factor.

These bits are not synchronized.

| Value | Name    | Description              |

|-------|---------|--------------------------|

| 0x0   | DIV1    | Prescaler: GCLK_TCC      |

| 0x1   | DIV2    | Prescaler: GCLK_TCC/2    |

| 0x2   | DIV4    | Prescaler: GCLK_TCC/4    |

| 0x3   | DIV8    | Prescaler: GCLK_TCC/8    |

| 0x4   | DIV16   | Prescaler: GCLK_TCC/16   |

| 0x5   | DIV64   | Prescaler: GCLK_TCC/64   |

| 0x6   | DIV256  | Prescaler: GCLK_TCC/256  |

| 0x7   | DIV1024 | Prescaler: GCLK_TCC/1024 |

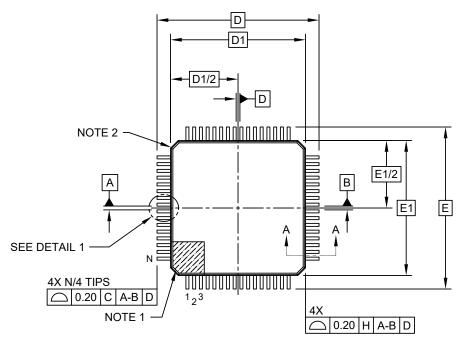

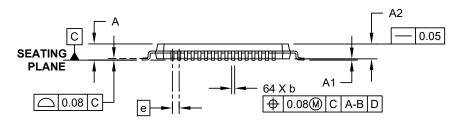

#### 55.3.4 64-pin TQFP

#### 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

TOP VIEW

SIDE VIEW

Microchip Technology Drawing C04-085C Sheet 1 of 2

# SAMD5x/E5x Family Data Sheet

## **Schematic Checklist**

| Signal Name        | Recommended Pin Connection           | Description                        |

|--------------------|--------------------------------------|------------------------------------|

|                    | Linear regulator mode: Not connected |                                    |

| GND                | -                                    | Ground                             |

| GND <sub>ANA</sub> | -                                    | Ground for the analog power domain |

#### Note:

- 1. These values are only given as a typical example.

- 2. Decoupling capacitors should be placed close to the device for each supply pin pair in the signal group, low ESR capacitors should be used for better decoupling.

- 3. An inductor should be added between the external power and the V<sub>DD</sub> for power filtering.

- 4. A ferrite bead has better filtering performance compared to standard inductor at high frequencies. A ferrite bead can be added between the main power supply (V<sub>DD</sub>) and V<sub>DDANA</sub> to prevent digital noise from entering the analog power domain. The bead should provide enough impedance (e.g., 50Ω at 20 MHz and 220Ω at 100 MHz) to separate the digital and analog power domains. Make sure to select a ferrite bead designed for filtering applications with a low DC resistance to avoid a large voltage drop across the ferrite bead.

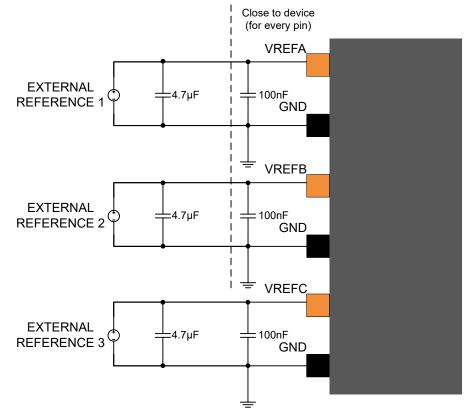

## 56.3 External Analog Reference Connections

The following schematic checklist is only necessary if the application is using one or more of the external analog references. If the internal references are used instead, the following circuits are not necessary.

#### Figure 56-4. External Analog Reference Schematic With Three References