Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                            |

| Core Size                  | 32-Bit Single-Core                                                          |

| Speed                      | 120MHz                                                                      |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                     |

| Number of I/O              | 99                                                                          |

| Program Memory Size        | 1MB (1M × 8)                                                                |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                               |

| Data Converters            | A/D 32x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 120-TFBGA                                                                   |

| Supplier Device Package    | 120-TFBGA (8x8)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsamd51p20a-ctut |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 21.12.5 Interrupt Enable Set in Clock/Calendar mode (CTRLA.MODE=2)

Name:INTENSETOffset:0x0AReset:0x0000Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

| R/W |

|-----|

| 0   |

|     |

| 0   |

|     |

| R/W |

| 0   |

|     |

### Bit 15 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

### Bit 14 – TAMPER Tamper Interrupt Enable

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Tamper Interrupt Enable bit, which enables the Tamper interrupt.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | The Tamper interrupt it disabled. |

| 1     | The Tamper interrupt is enabled.  |

### Bits 9:8 – ALARMn[1:0] Alarm n Interrupt Enable [n = 1..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Alarm n Interrupt Enable bit, which and enables the Alarm n interrupt.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The Alarm n interrupt is disabled. |

| 1     | The Alarm n interrupt is enabled.  |

### Bits 7:0 – PERn[7:0] Periodic Interval n Interrupt Enable [n = 7..0]

Writing a '0' to this bit has no effect. Writing a '1' to this bit will set the Periodic Interval n Interrupt Enable bit, which enables the Periodic Interval n interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Periodic Interval n interrupt is disabled. |

| 1     | Periodic Interval n interrupt is enabled.  |

### 24.9.22 GMAC Specific Address n Bottom Register

Name:

SAB

Offset:

0x88 + n\*0x08 [n=0..3]

Reset:

0x0000000

Property:

The addresses stored in the Specific Address Registers are deactivated at reset or when their corresponding Specific Address Register Bottom is written. They are activated when Specific Address Register Top is written.

| R/W<br>0 |

|----------|

|          |

| 0        |

| 0        |

|          |

| 16       |

|          |

| R/W      |

| 0        |

|          |

| 8        |

|          |

| R/W      |

| 0        |

|          |

| 0        |

|          |

| R/W      |

| 0        |

| -        |

### Bits 31:0 - ADDR[31:0] Specific Address n

Least significant 32 bits of the destination address, that is, bits 31:0. Bit zero indicates whether the address is multicast or unicast and corresponds to the least significant bit of the first byte received.

|                 | Name:<br>Offset:<br>Reset:<br>Property: | IPGS<br>0x0BC<br>0x00000000<br>- |     |          |       |     |     |     |

|-----------------|-----------------------------------------|----------------------------------|-----|----------|-------|-----|-----|-----|

| Bit             | 31                                      | 30                               | 29  | 28       | 27    | 26  | 25  | 24  |

| Access<br>Reset |                                         |                                  |     |          |       |     |     |     |

| Bit             | 23                                      | 22                               | 21  | 20       | 19    | 18  | 17  | 16  |

| Access<br>Reset |                                         |                                  |     |          |       |     |     |     |

| Bit             | 15                                      | 14                               | 13  | 12       | 11    | 10  | 9   | 8   |

|                 |                                         |                                  |     | FL[1     | 15:8] |     |     |     |

| Access          | R/W                                     | R/W                              | R/W | R/W      | R/W   | R/W | R/W | R/W |

| Reset           | 0                                       | 0                                | 0   | 0        | 0     | 0   | 0   | 0   |

| Bit             | 7                                       | 6                                | 5   | 4<br>FL[ | 3     | 2   | 1   | 0   |

| Access          | R/W                                     | R/W                              | R/W | R/W      | R/W   | R/W | R/W | R/W |

| Reset           |                                         | 0                                | 0   | 0        | 0     | 0   | 0   | 0   |

### 24.9.26 GMAC IPG Stretch Register

### Bits 15:0 - FL[15:0] Frame Length

Bits FL[7:0] are multiplied with the previously transmitted frame length (including preamble), and divided by FL[15:8]+1 (adding 1 to prevent division by zero). RESULT =  $\frac{FL[7:0]}{F[15+8]+1}$

If RESULT > 96 and the IP Stretch Enable bit in the Network Configuration Register (NCFGR.IPGSEN) is written to '1', RESULT is used for the transmit inter-packet-gap.

|        | Name:<br>Offset:<br>Reset:<br>Property: | PEFTSH<br>0x0F0<br>0x00000000<br>Read-Only |    |     |        |    |    |    |

|--------|-----------------------------------------|--------------------------------------------|----|-----|--------|----|----|----|

| Bit    | 31                                      | 30                                         | 29 | 28  | 27     | 26 | 25 | 24 |

|        |                                         |                                            |    |     |        |    |    |    |

| Access |                                         |                                            |    |     |        |    |    |    |

| Reset  |                                         |                                            |    |     |        |    |    |    |

| Dit    | 00                                      | 22                                         | 24 | 20  | 10     | 10 | 47 | 40 |

| Bit    | 23                                      | 22                                         | 21 | 20  | 19     | 18 | 17 | 16 |

| Access |                                         |                                            |    |     |        |    |    |    |

| Reset  |                                         |                                            |    |     |        |    |    |    |

| Reset  |                                         |                                            |    |     |        |    |    |    |

| Bit    | 15                                      | 14                                         | 13 | 12  | 11     | 10 | 9  | 8  |

|        |                                         |                                            |    |     | [15:8] |    |    |    |

| Access | R                                       | R                                          | R  | R   | R      | R  | R  | R  |

| Reset  |                                         | 0                                          | 0  | 0   | 0      | 0  | 0  | 0  |

|        |                                         |                                            |    |     |        |    |    |    |

| Bit    | 7                                       | 6                                          | 5  | 4   | 3      | 2  | 1  | 0  |

|        |                                         |                                            |    | RUD | [7:0]  |    |    |    |

| Access | R                                       | R                                          | R  | R   | R      | R  | R  | R  |

| Reset  | 0                                       | 0                                          | 0  | 0   | 0      | 0  | 0  | 0  |

|        |                                         |                                            |    |     |        |    |    |    |

### 24.9.36 GMAC PTP Peer Event Frame Transmitted Seconds High Register

### Bits 15:0 - RUD[15:0] Register Update

The register is updated with the value that the IEEE 1588 timer seconds register held when the SFD of a PTP transmit peer event crosses the MII interface. An interrupt is issued when the register is updated.

|        | Name:<br>Offset:<br>Reset:<br>Property: | AE<br>0x19C<br>0x00000000<br>Read-only |    |    |       |    |     |       |

|--------|-----------------------------------------|----------------------------------------|----|----|-------|----|-----|-------|

| Bit    | 31                                      | 30                                     | 29 | 28 | 27    | 26 | 25  | 24    |

|        |                                         |                                        |    |    |       |    |     |       |

| Access |                                         |                                        |    |    |       |    |     |       |

| Reset  |                                         |                                        |    |    |       |    |     |       |

| Bit    | 23                                      | 22                                     | 21 | 20 | 19    | 18 | 17  | 16    |

|        |                                         |                                        |    |    |       |    |     |       |

| Access |                                         |                                        |    |    |       |    |     |       |

| Reset  |                                         |                                        |    |    |       |    |     |       |

|        |                                         |                                        |    |    |       |    |     |       |

| Bit    | 15                                      | 14                                     | 13 | 12 | 11    | 10 | 9   | 8     |

|        |                                         |                                        |    |    |       |    | AER | [9:8] |

| Access |                                         |                                        |    |    |       |    | R   | R     |

| Reset  |                                         |                                        |    |    |       |    | 0   | 0     |

|        |                                         |                                        |    |    |       |    |     |       |

| Bit    | 7                                       | 6                                      | 5  | 4  | 3     | 2  | 1   | 0     |

|        |                                         |                                        |    |    | [7:0] |    |     |       |

| Access |                                         | R                                      | R  | R  | R     | R  | R   | R     |

| Reset  | 0                                       | 0                                      | 0  | 0  | 0     | 0  | 0   | 0     |

### 24.9.77 GMAC Alignment Errors Register

### Bits 9:0 – AER[9:0] Alignment Errors

This bit field counts the frames that are not an integral number of bytes long and have bad CRC when their length is truncated to an integral number of Bytes and are between 64 and 1518 Bytes in length (1536 if NCFGR.MAXFS=1). This register is also incremented if a symbol error is detected and the frame is of valid length and does not have an integral number of bytes.

## ICM - Integrity Check Monitor

### Bits 7:4 – RDM[3:0] Region Digest Mismatch

RDM[i] is set when there is a digest comparison mismatch between the hash value of region i and the reference value located in the Hash Area.

### Bits 3:0 - RHC[3:0] Region Hash Completed

RHC[i] is set when the ICM has completed the region with identifier i.

# FREQM – Frequency Meter

### 30.8.2 Control B

| Name:     | CTRLB |

|-----------|-------|

| Offset:   | 0x01  |

| Reset:    | 0x00  |

| Property: | _     |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0     |

|--------|---|---|---|---|---|---|---|-------|

|        |   |   |   |   |   |   |   | START |

| Access |   |   |   |   |   |   |   | W     |

| Reset  |   |   |   |   |   |   |   | 0     |

#### Bit 0 – START Start Measurement

| Va | alue | Description                         |

|----|------|-------------------------------------|

| 0  |      | Writing a '0' has no effect.        |

| 1  |      | Writing a '1' starts a measurement. |

## **FREQM – Frequency Meter**

### 30.8.4 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x08                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0    |

|--------|---|---|---|---|---|---|---|------|

|        |   |   |   |   |   |   |   | DONE |

| Access |   |   |   |   |   |   |   | R/W  |

| Reset  |   |   |   |   |   |   |   | 0    |

Bit 0 – DONE Measurement Done Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Measurement Done Interrupt Enable bit, which disables the Measurement Done interrupt.

| I | Value | Description                                 |

|---|-------|---------------------------------------------|

|   | 0     | The Measurement Done interrupt is disabled. |

|   | 1     | The Measurement Done interrupt is enabled.  |

### 32.9.14 Pin Configuration

| Name:     | PINCFG                |

|-----------|-----------------------|

| Offset:   | 0x40 + n*0x01 [n=031] |

| Reset:    | 0x00                  |

| Property: | PAC Write-Protection  |

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

There are up to 32 Pin Configuration registers in each PORT group, one for each I/O line.

| Bit    | 7 | 6      | 5 | 4 | 3 | 2      | 1    | 0      |

|--------|---|--------|---|---|---|--------|------|--------|

|        |   | DRVSTR |   |   |   | PULLEN | INEN | PMUXEN |

| Access |   | RW     |   |   |   | RW     | RW   | RW     |

| Reset  |   | 0      |   |   |   | 0      | 0    | 0      |

### **Bit 6 – DRVSTR** Output Driver Strength Selection

This bit controls the output driver strength of an I/O pin configured as an output.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Pin drive strength is set to normal drive strength.   |

| 1     | Pin drive strength is set to stronger drive strength. |

#### Bit 2 – PULLEN Pull Enable

This bit enables the internal pull-up or pull-down resistor of an I/O pin configured as an input.

| Value | Description                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------|

| 0     | Internal pull resistor is disabled, and the input is in a high-impedance configuration.                               |

| 1     | Internal pull resistor is enabled, and the input is driven to a defined logic level in the absence of external input. |

#### Bit 1 - INEN Input Enable

This bit controls the input buffer of an I/O pin configured as either an input or output.

Writing a zero to this bit disables the input buffer completely, preventing read-back of the physical pin state when the pin is configured as either an input or output.

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | Input buffer for the I/O pin is disabled, and the input value will not be sampled.          |

| 1     | Input buffer for the I/O pin is enabled, and the input value will be sampled when required. |

- Data register (DATA)

- Address register (ADDR)

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

PAC write-protection does not apply to accesses through an external debugger.

### Related Links

27. PAC - Peripheral Access Controller

### 33.5.9 Analog Connections

Not applicable.

### 33.6 Functional Description

### 33.6.1 Principle of Operation

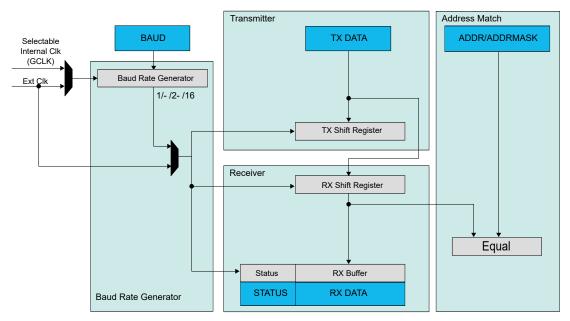

The basic structure of the SERCOM serial engine is shown in Figure 33-2. Labels in capital letters are synchronous to the system clock and accessible by the CPU; labels in lowercase letters can be configured to run on the GCLK\_SERCOMx\_CORE clock or an external clock.

### Figure 33-2. SERCOM Serial Engine

The transmitter consists of a single write buffer and a shift register.

The receiver consists of a one-level (I<sup>2</sup>C), two-level (USART, SPI) receive buffer and a shift register.

The baud-rate generator is capable of running on the GCLK\_SERCOMx\_CORE clock or an external clock.

Address matching logic is included for SPI and I<sup>2</sup>C operation.

# **Bit 0 – DRE** Data Register Empty Interrupt Enable Writing '0' to this bit has no effect.

Writing '1' to this bit will clear the Data Register Empty Interrupt Enable bit, which disables the Data Register Empty interrupt.

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | Data Register Empty interrupt is disabled. |

| 1     | Data Register Empty interrupt is enabled.  |

# SAMD5x/E5x Family Data Sheet

## **QSPI - Quad Serial Peripheral Interface**

### 37.8.14 Scrambling Key

| Name:     | SCRAMBKEY            |

|-----------|----------------------|

| Offset:   | 0x44                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

| Bit    | 31         | 30 | 29 | 28    | 27     | 26 | 25 | 24 |  |

|--------|------------|----|----|-------|--------|----|----|----|--|

|        | KEY[31:24] |    |    |       |        |    |    |    |  |

| Access | W          | W  | W  | W     | W      | W  | W  | W  |  |

| Reset  | 0          | 0  | 0  | 0     | 0      | 0  | 0  | 0  |  |

|        |            |    |    |       |        |    |    |    |  |

| Bit    | 23         | 22 | 21 | 20    | 19     | 18 | 17 | 16 |  |

|        |            |    |    | KEY[2 | 23:16] |    |    |    |  |

| Access | W          | W  | W  | W     | W      | W  | W  | W  |  |

| Reset  | 0          | 0  | 0  | 0     | 0      | 0  | 0  | 0  |  |

|        |            |    |    |       |        |    |    |    |  |

| Bit    | 15         | 14 | 13 | 12    | 11     | 10 | 9  | 8  |  |

|        |            |    |    | KEY   | [15:8] |    |    |    |  |

| Access | W          | W  | W  | W     | W      | W  | W  | W  |  |

| Reset  | 0          | 0  | 0  | 0     | 0      | 0  | 0  | 0  |  |

|        |            |    |    |       |        |    |    |    |  |

| Bit    | 7          | 6  | 5  | 4     | 3      | 2  | 1  | 0  |  |

|        | KEY[7:0]   |    |    |       |        |    |    |    |  |

| Access | W          | W  | W  | W     | W      | W  | W  | W  |  |

| Reset  | 0          | 0  | 0  | 0     | 0      | 0  | 0  | 0  |  |

|        |            |    |    |       |        |    |    |    |  |

**Bits 31:0 – KEY[31:0]** Scrambling User Key This field defines the user key value.

### **CAN - Control Area Network**

### 39.8.47 Tx Event FIFO Acknowledge

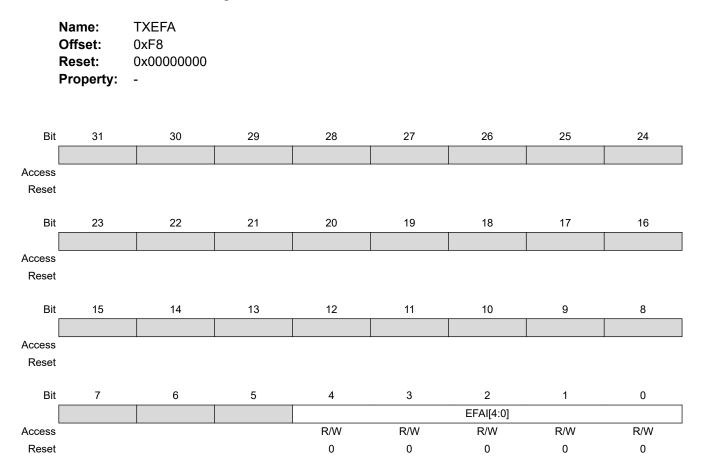

### Bits 4:0 - EFAI[4:0] Event FIFO Acknowledge Index

After the Host has read an element or a sequence of elements from the Tx Event FIFO it has to write the index of the last element read from Tx Event FIFO to EFAI. This will set the Tx Event FIFO Get Index TXEFS.EFGI to EFAI + 1 and update the FIFO 0 Fill Level TXEFS.EFFL.

### 39.9 Message RAM

For storage of Rx/Tx messages and for storage of the filter configuration a single- or dual-ported Message RAM has to be connected to the CAN module.

### 39.9.1 Message RAM Configuration

The Message RAM has a width of 32 bits. In case parity checking or ECC is used a respective number of bits has to be added to each word. The CAN module can be configured to allocate up to 4352 words in the Message RAM. It is not necessary to configure each of the sections listed in the figure below, nor is there any restriction with respect to the sequence of the sections.

When operated in CAN FD mode the required Message RAM size strongly depends on the element size configured for Rx FIFO 0, Rx FIFO 1, Rx Buffers, and Tx Buffers via RXESC.F0DS, RXESC.F1DS, RXESC.RBDS, and TXESC.TBDS.

### 40.8.5 Transfer Mode Register

| Name:     | TMR    |

|-----------|--------|

| Offset:   | 0x0C   |

| Reset:    | 0x0000 |

| Property: | -      |

This register is used to control data transfers. The user shall set this register before issuing a command which transfers data (refer to bit DPSEL in CR), or before issuing a Resume command. The user must save the value of this register when the data transfer is suspended (as a result of a Suspend command) and restore it before issuing a Resume command. To prevent data loss, this register cannot be written while data transactions are in progress. Writes to this register are ignored when bit PSR.CMDINHD is '1'.

|        | MSBSEL | В  | BCEN       |        | BCR.BLKCNT |      | Function               |      |       |

|--------|--------|----|------------|--------|------------|------|------------------------|------|-------|

|        | 0      | D  | Don't care |        | Don't care |      | Single Transfer        |      |       |

|        | 1      | 0  | 0          |        | Don't care |      | Infinite Transfer      |      |       |

|        | 1      | 1  | 1          |        | Not Zero   |      | Multiple Transfer      |      |       |

|        | 1      | 1  | 1          |        | Zero       |      | Stop Multiple Transfer |      |       |

| Bit    | 15     | 14 | 1          | 13     | 12         | 11   | 10                     | 9    | 8     |

| Access |        |    |            |        |            |      |                        |      |       |

| Reset  |        |    |            |        |            |      |                        |      |       |

| Bit    | 7      | 6  |            | 5      | 4          | 3    | 2                      | 1    | 0     |

|        |        |    |            | MSBSEL | DTDSEL     | ACMD | EN[1:0]                | BCEN | DMAEN |

| Access |        |    |            | R/W    | R/W        | R/W  | R/W                    | R/W  | R/W   |

| Reset  |        |    |            | 0      | 0          | 0    | 0                      | 0    | 0     |

#### Table 40-1. Determining the Transfer Type

### Bit 5 – MSBSEL Multi/Single Block Selection

Write this bit to '1' when issuing multiple-block transfer commands using DAT line(s). For any other commands, write this bit to 0. If this bit is 0, it is not necessary to write BCR to '1' (refer to Table 1-4).

### Bit 4 – DTDSEL Data Transfer Direction Selection

This bit defines the direction of the DAT lines data transfers. Write this bit to '1' to transfer data from the device (SD Card/SDIO/e.MMC) to the peripheral. Write this bit to '0' for all other commands.

| Value | Name  | Description                                    |

|-------|-------|------------------------------------------------|

| 0     | WRITE | Writes data from the peripheral to the device. |

| 1     | READ  | Reads data from the device to the peripheral.  |

### Bits 3:2 - ACMDEN[1:0] Auto Command Enable

Two methods can be used to stop Multiple-block read and write operation:

1. Auto CMD12: when the ACMDEN field is set to 1, the peripheral issues CMD12 automatically when the last block transfer is completed. An Auto CMD12 error is indicated to ACESR. Auto CMD12 is not enabled if the command does not require CMD12.

# SAMD5x/E5x Family Data Sheet

### AES – Advanced Encryption Standard

| Offset           | Name     | Bit Pos. |                 |  |  |  |  |  |  |

|------------------|----------|----------|-----------------|--|--|--|--|--|--|

|                  |          | 23:16    | GHASH[23:16]    |  |  |  |  |  |  |

|                  |          | 31:24    | GHASH[31:24]    |  |  |  |  |  |  |

|                  |          | 7:0      | GHASH[7:0]      |  |  |  |  |  |  |

| 0x70             | GHASH1   | 15:8     | GHASH[15:8]     |  |  |  |  |  |  |

|                  | GRASHI   | 23:16    | GHASH[23:16]    |  |  |  |  |  |  |

|                  |          | 31:24    | GHASH[31:24]    |  |  |  |  |  |  |

|                  |          | 7:0      | GHASH[7:0]      |  |  |  |  |  |  |

| 0x74             | GHASH2   | 15:8     | GHASH[15:8]     |  |  |  |  |  |  |

| UX74             | GHASH2   | 23:16    | GHASH[23:16]    |  |  |  |  |  |  |

|                  |          | 31:24    | GHASH[31:24]    |  |  |  |  |  |  |

|                  |          | 7:0      | GHASH[7:0]      |  |  |  |  |  |  |

| 0x78             | GHASH3   | 15:8     | GHASH[15:8]     |  |  |  |  |  |  |

|                  | GRASHS   | 23:16    | GHASH[23:16]    |  |  |  |  |  |  |

|                  |          |          | GHASH[31:24]    |  |  |  |  |  |  |

| 0x7C<br><br>0x7F | Reserved |          |                 |  |  |  |  |  |  |

|                  |          | 7:0      | CIPLEN[7:0]     |  |  |  |  |  |  |

| 80               | CIPLEN   | 15:8     | CIPLEN[15:8]    |  |  |  |  |  |  |

| 80               |          | 23:16    | CIPLEN[23:16]   |  |  |  |  |  |  |

|                  |          | 31:24    | CIPLEN[31:24]   |  |  |  |  |  |  |

|                  |          | 7:0      | RANDSEED[7:0]   |  |  |  |  |  |  |

| 0x84             | RANDSEED | 15:8     | RANDSEED[15:8]  |  |  |  |  |  |  |

| 0X04             |          | 23:16    | RANDSEED[23:16] |  |  |  |  |  |  |

|                  |          | 31:24    | RANDSEED[31:24] |  |  |  |  |  |  |

### 42.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 42.5.8 Register Access Protection.

Some registers are enable-protected, meaning they can only be written when the peripheral is disabled. Enable-protection is denoted by the "Enable-Protected" property in each individual register description.

# SAMD5x/E5x Family Data Sheet

## Public Key Cryptography Controller (PUKCC)

### 43.3.5.1.7 Modular Reductions Service Parameters Definition Table 43-44. RedMod Service Parameters

| Parameter                               | Туре | Direction | Location      | Data Length                         | Before<br>Executing the<br>Service | After Executing the Service                                                      |

|-----------------------------------------|------|-----------|---------------|-------------------------------------|------------------------------------|----------------------------------------------------------------------------------|

| u2Options                               | u2   | 1         | -             | _                                   | Options (see<br>below)             | Options (see<br>below)                                                           |

| Specific/CarryIn                        | Bits | 1         | -             | _                                   | Must be set to zero.               | -                                                                                |

| Specific/Gf2n                           | Bit  | I         | _             | -                                   | GF(2 <sup>n</sup> ) Bit            | -                                                                                |

| Specific/<br>CarryOut Zero<br>Violation | Bits | l         | -             | -                                   | -                                  | Carry Out, Zero<br>Bit and Violation<br>Bit filled<br>according to the<br>result |

| nu1ModBase<br>( see <b>Note 1</b> )     | nu1  | 1         | Crypto<br>RAM | u2ModLength + 4                     | Base of N                          | Base of N<br>untouched                                                           |

| nu1CnsBase                              | nu1  | I         | Crypto<br>RAM | u2ModLength + 12                    | Base of Cns                        | Base of Cns<br>filled with the<br>Setup Constant                                 |

| u2ModLength                             | u2   | I         | _             | -                                   | Length of N                        | Length of N                                                                      |

| nu1RBase                                | nu1  | I         | Crypto<br>RAM | GF(p): 64 bytes<br>GF(2n): 68 bytes | Base of R<br>as a workspace        | Base of R<br>workspace<br>corrupted                                              |

| nu1XBase (see<br><b>Note 2</b> )        | nu1  | I         | Crypto<br>RAM | 2*u2ModLength<br>+ 8                | Base of X as a workspace           | Base of X<br>workspace<br>corrupted                                              |

### Note:

1. The Modulus is to be given as a u2ModLength Aligned Significant Length Bytes however, it has to be provided as a u2ModLength + 4 bytes long number, having the four high-order bytes set to zero.

Before the X (pointed by {nu1XBase,2 \* u2ModLength + 8}) LSB bytes, four supplementary bytes will be saved/restored. Other four supplementary bytes will also be saved/restored after the X MSB bytes. All these supplementary bytes may be entirely in the Crypto RAM (therefore, do not place the X area too near the end of the Crypto RAM) and shall not overlap with other area used by the service.

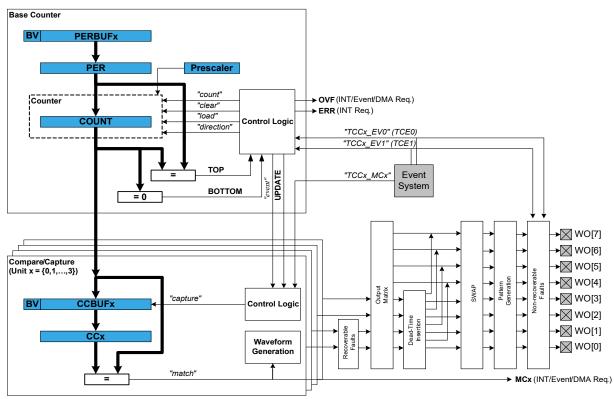

### TCC – Timer/Counter for Control Applications

- Two non-recoverable fault sources

- Debugger can be a source of non-recoverable fault

- Input events:

- Two input events (EVx) for counter

- One input event (MCx) for each channel

- Output events:

- Three output events (Count, Re-Trigger and Overflow) are available for counter

- One Compare Match/Input Capture event output for each channel

- Interrupts:

- Overflow and Re-Trigger interrupt

- Compare Match/Input Capture interrupt

- Interrupt on fault detection

### 49.3 Block Diagram

### Figure 49-1. Timer/Counter for Control Applications - Block Diagram

### 49.4 Signal Description

| Pin Name  | Туре           | Description                       |

|-----------|----------------|-----------------------------------|

| TCC/WO[0] | Digital output | Compare channel 0 waveform output |

| TCC/WO[1] | Digital output | Compare channel 1 waveform output |

# SAMD5x/E5x Family Data Sheet

# Packaging Information

| Table 55-5. Device and Package Maximum Weight |      |  |  |  |

|-----------------------------------------------|------|--|--|--|

| 14                                            | mg   |  |  |  |

| Table 55-6. Package Characteristics           |      |  |  |  |

| Moisture Sensitivity Level                    | MSL1 |  |  |  |

| Table 55-7. Package Reference                 |      |  |  |  |

| JEDEC Drawing Reference                       | N/A  |  |  |  |

| JESD97 Classification                         | e1   |  |  |  |

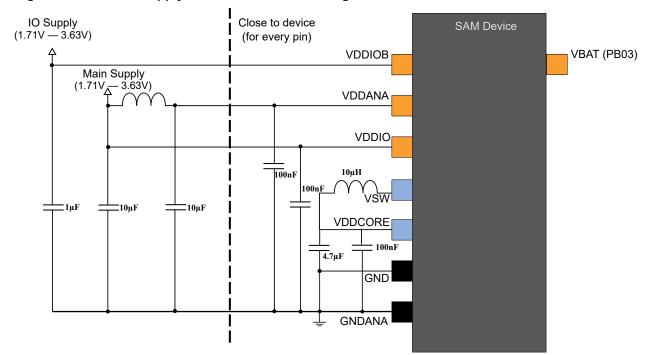

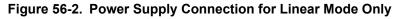

### **Schematic Checklist**

Figure 56-1. Power Supply Connection for Switching/Linear Mode

## The Microchip Web Site

Microchip provides online support via our web site at http://www.microchip.com/. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- **General Technical Support** Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# **Customer Change Notification Service**

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at <a href="http://www.microchip.com/">http://www.microchip.com/</a>. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **Customer Support**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://www.microchip.com/support