Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 120MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                             |

| Number of I/O              | 51                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-TQFP                                                                             |

| Supplier Device Package    | 64-TQFP (10x10)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame51j20a-au           |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 38.7.    | Register Summary                        | 1167 |

|----------|-----------------------------------------|------|

| 38.8.    | Register Description                    | 1171 |

| 20 044   | L. Construct Annual Materia             | 1011 |

|          | I - Control Area Network                |      |

|          | Overview                                |      |

|          | Features                                |      |

|          | Block Diagram                           |      |

|          | Signal Description                      |      |

|          | Product Dependencies                    |      |

|          | Functional Description                  |      |

|          | Register Summary                        |      |

|          | Register Description                    |      |

| 39.9.    | Message RAM                             | 1343 |

| 40. SD/I | MMC Host Controller (SDHC)              | 1353 |

|          | Overview                                |      |

|          | Features                                |      |

|          | Block Diagrams                          |      |

|          | Signal Description                      |      |

|          | Product Dependencies                    |      |

|          | Functional Description                  |      |

|          | Register Summary                        |      |

|          | Register Description                    |      |

| 10.01    |                                         |      |

| 41. CCL  | . – Configurable Custom Logic           |      |

| 41.1.    | Overview                                | 1432 |

| 41.2.    | Features                                | 1432 |

| 41.3.    | Block Diagram                           | 1433 |

| 41.4.    | Signal Description                      | 1433 |

| 41.5.    | Product Dependencies                    | 1433 |

| 41.6.    | Functional Description                  | 1435 |

| 41.7.    | Register Summary                        | 1446 |

| 41.8.    | Register Description                    | 1446 |

| 10 AES   | Advanced Eneruntian Standard            | 1151 |

|          | Advanced Encryption Standard            |      |

|          | Overview                                |      |

|          | Features                                |      |

|          | Block Diagram                           |      |

|          | Signal Description                      |      |

|          | Product Dependencies                    |      |

|          | Functional Description                  |      |

|          | Register Summary                        |      |

| 42.8.    | Register Description                    | 1465 |

|          | lic Key Cryptography Controller (PUKCC) |      |

| 43.1.    | Overview                                | 1482 |

| 43.2.    | Product Dependencies                    |      |

| 43.3.    | Functional Description                  | 1483 |

|          |                                         |      |

This bit is never cleared.

One-hot priority encoding enforced automatically on register writes as follows. 'x' represents don't care.

| Value | Name   | Description                                      |

|-------|--------|--------------------------------------------------|

| 0     | -      | Reserved                                         |

| 1     | SINGLE | 00001: Always use SINGLE AHB bursts              |

| 2     | -      | Reserved                                         |

| 4     | INCR4  | 001xx: Attempt to use INCR4 AHB bursts (Default) |

| 8     | INCR8  | 01xxx: Attempt to use INCR8 AHB bursts           |

| 16    | INCR16 | 1xxxx: Attempt to use INCR16 AHB bursts          |

### NVMCTRL – Nonvolatile Memory Controller

#### 25.8.14 SmartEEPROM Status

|        | Name:<br>Offset:<br>Reset:<br>Property: | SEESTAT<br>0x2C<br>0x00000000<br>Read-Only |    |       |      |           |          |       |

|--------|-----------------------------------------|--------------------------------------------|----|-------|------|-----------|----------|-------|

| Bit    | 31                                      | 30                                         | 29 | 28    | 27   | 26        | 25       | 24    |

|        |                                         |                                            |    |       |      |           |          |       |

| Access |                                         |                                            |    |       |      |           |          |       |

| Reset  |                                         |                                            |    |       |      |           |          |       |

| Bit    | 23                                      | 22                                         | 21 | 20    | 19   | 18        | 17       | 16    |

|        |                                         |                                            |    |       |      |           | PSZ[2:0] |       |

| Access |                                         |                                            |    |       |      | R         | R        | R     |

| Reset  |                                         |                                            |    |       |      | 0         | 0        | x     |

|        |                                         |                                            |    |       |      |           |          |       |

| Bit    | 15                                      | 14                                         | 13 | 12    | 11   | 10        | 9        | 8     |

|        |                                         |                                            |    |       |      | SBLK[3:0] |          |       |

| Access |                                         |                                            |    |       | R    | R         | R        | R     |

| Reset  |                                         |                                            |    |       | 0    | 0         | 0        | x     |

|        |                                         |                                            |    |       |      |           |          |       |

| Bit    | 7                                       | 6                                          | 5  | 4     | 3    | 2         | 1        | 0     |

|        |                                         |                                            |    | RLOCK | LOCK | BUSY      | LOAD     | ASEES |

| Access |                                         |                                            |    | R     | R    | R         | R        | R     |

| Reset  |                                         |                                            |    | 0     | x    | 0         | 0        | x     |

#### Bits 18:16 - PSZ[2:0] SmartEEPROM Page Size

This bit field is automatically loaded from the user page during startup.

Indicates the page size. Not all device families will provide all the page sizes indicated in the table.

#### Bits 11:8 - SBLK[3:0] Blocks Number In a Sector

This bit field is automatically loaded from the user page during startup.

Indicates the number of blocks allocated to a SEES.

#### Bit 4 – RLOCK RLOCK

SmartEEPROM Write Access To Register Address Space Is Locked

#### Bit 3 – LOCK SmartEEPROM Section Locked

This bit field is automatically loaded from the user page during startup.

Access to the SmartEEPROM data is locked. Writes to AHB2 throws hardfault exceptions.

- 0: SmartEEPROM access is not locked

- 1: SmartEEPROM access is locked

#### Bit 2 – BUSY Busy

0: SmartEEPROM is ready.

© 2018 Microchip Technology Inc.

**OSCCTRL – Oscillators Controller**

This flag is set on a zero-to-one transition of the XOSC0 Ready bit in the Status register (STATUS.XOSCRDYn) and will generate an interrupt request if INTENSET.XOSCRDYn is '1'.

Writing a zero to this bit has no effect.

Writing a '1' to this bit clears the XOSCn Ready interrupt flag.

#### 31.7.8 Channel n Control

| Name:     | CHANNEL               |

|-----------|-----------------------|

| Offset:   | 0x20 + n*0x08 [n=031] |

| Reset:    | 0x00008000            |

| Property: | PAC Write-Protection  |

This register allows the user to configure channel n. To write to this register, do a single, 32-bit write of all the configuration data.

| Bit    | 31       | 30       | 29      | 28 | 27          | 26      | 25   | 24     |

|--------|----------|----------|---------|----|-------------|---------|------|--------|

|        |          |          |         |    |             |         |      |        |

| Access |          |          |         |    |             |         |      |        |

| Reset  |          |          |         |    |             |         |      |        |

|        |          |          |         |    |             |         |      |        |

| Bit    | 23       | 22       | 21      | 20 | 19          | 18      | 17   | 16     |

|        |          |          |         |    |             |         |      |        |

| Access |          |          |         |    |             |         |      |        |

| Reset  |          |          |         |    |             |         |      |        |

|        |          |          |         |    |             |         |      |        |

| Bit    | 15       | 14       | 13      | 12 | 11          | 10      | 9    | 8      |

|        | ONDEMAND | RUNSTDBY |         |    | EDGS        | EL[1:0] | PATH | I[1:0] |

| Access | RW       | RW       |         |    | RW          | RW      | RW   | RW     |

| Reset  | 1        | 0        |         |    | 0           | 0       | 0    | 0      |

|        |          |          |         |    |             |         |      |        |

| Bit    | _        | _        |         |    | •           | •       | 4    | 0      |

|        | 7        | 6        | 5       | 4  | 3           | 2       | 1    | 0      |

|        | 7        | 6        | 5       |    | 3<br>N[7:0] | 2       | 1    | 0      |

| Access | 7<br>RW  | 6<br>RW  | 5<br>RW |    |             | RW      | RW   | RW     |

#### Bit 15 - ONDEMAND Generic Clock On Demand

| Value | Description                                                                              |

|-------|------------------------------------------------------------------------------------------|

| 0     | Generic clock for a channel is always on, if the channel is configured and generic clock |

|       | source is enabled.                                                                       |

| 1     | Generic clock is requested on demand while an event is handled                           |

#### Bit 14 - RUNSTDBY Run in Standby

This bit is used to define the behavior during standby sleep mode.

| Value | Description                                                         |

|-------|---------------------------------------------------------------------|

| 0     | The channel is disabled in standby sleep mode.                      |

| 1     | The channel is not stopped in standby sleep mode and depends on the |

|       | CHANNEL.ONDEMAND bit.                                               |

#### Bits 11:10 – EDGSEL[1:0] Edge Detection Selection

These bits set the type of edge detection to be used on the channel.

These bits must be written to zero when using the asynchronous path.

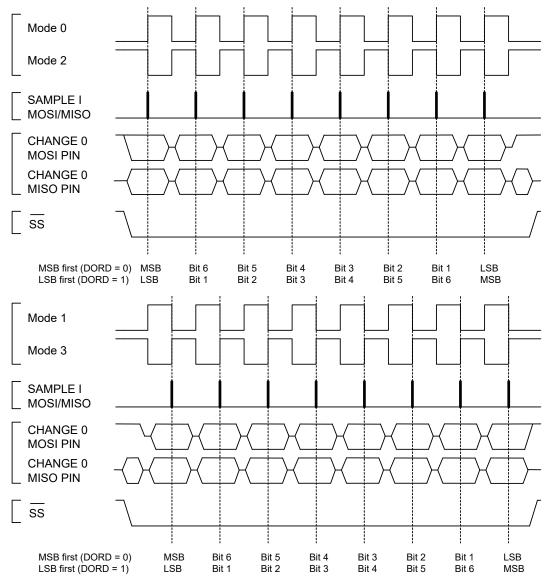

## SAMD5x/E5x Family Data Sheet SERCOM SPI – SERCOM Serial Peripheral Interface

#### Figure 35-3. SPI Transfer Modes

#### 35.6.2.6 Transferring Data

#### 35.6.2.6.1 Master

In master mode (CTRLA.MODE=0x3), when Master Slave Enable Select (CTRLB.MSSEN) is '1', hardware will control the  $\overline{SS}$  line.

When Master Slave Select Enable (CTRLB.MSSEN) is '0', the  $\overline{SS}$  line must be configured as an output.  $\overline{SS}$  can be assigned to any general purpose I/O pin. When the SPI is ready for a data transaction, software must pull the  $\overline{SS}$  line low.

When writing a character to the Data register (DATA), the character will be transferred to the shift register. Once the content of TxDATA has been transferred to the shift register, the Data Register Empty flag in the Interrupt Flag Status and Clear register (INTFLAG.DRE) will be set. And a new character can be written to DATA.

Each time one character is shifted out from the master, another character will be shifted in from the slave simultaneously. If the receiver is enabled (CTRLA.RXEN=1), the contents of the shift register will be

© 2018 Microchip Technology Inc.

Enable-protection is denoted by the "Enable-Protection" property in the register description.

Before the I<sup>2</sup>C is enabled it must be configured as outlined by the following steps:

- 1. Select I<sup>2</sup>C Master or Slave mode by writing 0x4 (Slave mode) or 0x5 (Master mode) to the Operating Mode bits in the CTRLA register (CTRLA.MODE).

- 2. If desired, select the SDA Hold Time value in the CTRLA register (CTRLA.SDAHOLD).

- 3. In Slave mode, the minimum slave setup time for the SDA can be selected in the SDA Setup Time bit group in the Control C register (CTRLC.SDASETUP).

- 4. If desired, enable smart operation by setting the Smart Mode Enable bit in the CTRLB register (CTRLB.SMEN).

- 5. If desired, enable SCL low time-out by setting the SCL Low Time-Out bit in the Control A register (CTRLA.LOWTOUT).

- 6. In Master mode:

- 6.1. Select the inactive bus time-out in the Inactive Time-Out bit group in the CTRLA register (CTRLA.INACTOUT).

- 6.2. Write the Baud Rate register (BAUD) to generate the desired baud rate.

In Slave mode:

- 6.1. Configure the address match configuration by writing the Address Mode value in the CTRLB register (CTRLB.AMODE).

- 6.2. Set the Address and Address Mask value in the Address register (ADDR.ADDR and ADDR.ADDRMASK) according to the address configuration.

#### 36.6.2.2 Enabling, Disabling, and Resetting

This peripheral is enabled by writing '1' to the Enable bit in the Control A register (CTRLA.ENABLE), and disabled by writing '0' to it.

Writing '1' to the Software Reset bit in the Control A register (CTRLA.SWRST) will reset all registers of this peripheral to their initial states, except the DBGCTRL register, and the peripheral is disabled.

#### 36.6.2.3 I<sup>2</sup>C Bus State Logic

The bus state logic includes several logic blocks that continuously monitor the activity on the I<sup>2</sup>C bus lines in all sleep modes with running GCLK\_SERCOM\_x clocks. The start and stop detectors and the bit counter are all essential in the process of determining the current bus state. The bus state is determined according to Bus State Diagram. Software can get the current bus state by reading the Master Bus State bits in the Status register (STATUS.BUSSTATE). The value of STATUS.BUSSTATE in the figure is shown in binary.

USB – Universal Serial Bus

Writing a zero to this bit has no effect.

Writing a one to this bit clears the TRCPT Interrupt Flag.

**USB – Universal Serial Bus**

| SIZE[2:0] | Description                                                                |

|-----------|----------------------------------------------------------------------------|

| 0x4       | 128 Byte <sup>(1)</sup>                                                    |

| 0x5       | 256 Byte <sup>(1)</sup>                                                    |

| 0x6       | 512 Byte <sup>(1)</sup>                                                    |

| 0x7       | 1024 Byte in HS mode <sup>(1)</sup><br>1023 Byte in FS mode <sup>(1)</sup> |

1. For Isochronous pipe only.

### Bits 27:14 – MULTI\_PACKET\_SIZE[13:0] Multi Packet IN or OUT size

These bits define the 14-bit value that is used for multi-packet transfers.

For IN pipes, MULTI\_PACKET\_SIZE holds the total number of bytes sent. MULTI\_PACKET\_SIZE should be written to zero when setting up a new transfer.

For OUT pipes, MULTI\_PACKET\_SIZE holds the total data size for the complete transfer. This value must be a multiple of the maximum packet size.

#### Bits 13:8 - BYTE\_COUNT[5:0] Byte Count

These bits define the 14-bit value that contains number of bytes sent in the last OUT or SETUP transaction for an OUT pipe, or of the number of bytes to be received in the next IN transaction for an input pipe.

#### 38.8.7.5 Host Status Bank

| Name:     | STATUS_BK   |

|-----------|-------------|

| Offset:   | 0x0A & 0x1A |

| Reset:    | 0xxxxxxx    |

| Property: | NA          |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1         | 0      |

|--------|---|---|---|---|---|---|-----------|--------|

|        |   |   |   |   |   |   | ERRORFLOW | CRCERR |

| Access |   |   |   |   |   |   | R/W       | R/W    |

| Reset  |   |   |   |   |   |   | x         | х      |

Bit 1 – ERRORFLOW Error Flow Status

This bit defines the Error Flow Status.

This bit is set when a Error Flow has been detected during transfer from/towards this bank.

For IN transfer, a NAK handshake has been received. For OUT transfer, a NAK handshake has been received. For Isochronous IN transfer, an overrun condition has occurred. For Isochronous OUT transfer, an underflow condition has occurred.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No Error Flow detected.         |

| 1     | A Error Flow has been detected. |

#### Bit 0 - CRCERR CRC Error

This bit defines the CRC Error Status.

This bit is set when a CRC error has been detected in an isochronous IN endpoint bank.

| Value | Description         |

|-------|---------------------|

| 0     | No CRC Error.       |

| 1     | CRC Error detected. |

### Public Key Cryptography Controller (PUKCC)

#### Table 43-28. Fmult Service Carry Settings

| Option AND CARRYOPTIONS            | CarryOperand | Resulting Operation   |

|------------------------------------|--------------|-----------------------|

| SET_CARRYOPTION(ADD_CARRY)         | CarryIn      | R = X*Y + CarryIn     |

| SET_CARRYOPTION(SUB_CARRY)         | - CarryIn    | R = X*Y - CarryIn     |

| SET_CARRYOPTION(ADD_1_PLUS_CARRY)  | 1 + CarryIn  | R = X*Y + 1 + CarryIn |

| SET_CARRYOPTION(ADD_1_MINUS_CARRY) | 1 - CarryIn  | R = X*Y + 1 - CarryIn |

| SET_CARRYOPTION(CARRY_NONE)        | 0            | R = X*Y               |

| SET_CARRYOPTION(ADD_1)             | 1            | R = X*Y + 1           |

| SET_CARRYOPTION(SUB_1)             | - 1          | R = X*Y - 1           |

| SET_CARRYOPTION(ADD_2)             | 2            | R = X*Y + 2           |

#### 43.3.4.9.9 Status Returned Values

#### Table 43-29. Fmult Service Return Codes

| Returned Status | Importance | Meaning                      |

|-----------------|------------|------------------------------|

| PUKCL_OK        | -          | Service functioned correctly |

#### 43.3.4.10 Square

#### 43.3.4.10.1 Purpose

The purpose of this service is to compute the square of a big number and optionally accumulate/subtract from a second big number.

Please note that this service uses an optimized implementation of the squaring. It also means that when the GF(2<sup>n</sup>) flag is set, the execution time will be smaller than when not set (in that case, the squaring execution time will still be smaller than for a standard multiplication).

The available options are as follows:

- Work in the GF(2<sup>n</sup>) or in the standard integer arithmetic field

- Add of a supplemental CarryOperand

- Overlapping of the operands is possible, taking into account some constraints

- Modular Reduction of the computation result

#### 43.3.4.10.2 How to Use the Service

#### 43.3.4.10.3 Description

This service provides the following (if not computing a modular reduction of the result):

#### $R = [Z] \pm (X^2 + CarryOperand)$

Or (if computing a modular reduction of the result):

#### $R = ([Z] \pm (X^2 + CarryOperand))mod N$

The service name for this operation is Square.

In these computations, the following data has to be provided:

• R the result (pointed by {nu1RBase,2 \*u2Xlength})

- P the modulus filled (pointed by {nu1ModBase,u2ModLength + 4})

- The workspace not initialized (pointed by {nu1WorkSpace, 8\*u2ModLength + 44}

- The a and b parameters relative to the elliptic curve (pointed by {nu1ABBase,2\*u2ModLength + 8})

- K the scalar number (pointed by {nu1ScalarNumber,u2ScalarLength + 4})

The resulting C point is represented in projective coordinates (X,Y,Z) and is stored at the very same place than the input point A. This point can be the Infinite Point.

The service name for this operation is GF2NEccMulFast. This service uses Fast mode and Fast Modular Reduction for computation.

**Important:** Before using this service, ensure that the constant Cns has been calculated with the setup of the Fast Modular Reductions service.

#### 43.3.7.4.4 Parameters Definition

### Table 43-98. GF2NEccMulFast Service Parameters

| Parameter    | Туре | Direction | Location      | Data Length           | Before<br>Executing the<br>Service               | After<br>Executing the<br>Service                |

|--------------|------|-----------|---------------|-----------------------|--------------------------------------------------|--------------------------------------------------|

| nu1ModBase   | nu1  | I         | Crypto<br>RAM | u2ModLength + 4       | Base of modulus<br>P                             | Base of<br>modulus P                             |

| nu1CnsBase   | nu1  | I         | Crypto<br>RAM | u2ModLength + 12      | Base of Cns                                      | Base of Cns                                      |

| u2ModLength  | u2   | I         | -             | -                     | Length of<br>modulus P                           | Length of<br>modulus P                           |

| nu1KBase     | nu1  | 1         | Crypto<br>RAM | u2KLength             | Scalar number<br>used to multiply<br>the point A | Unchanged                                        |

| u2KLength    | u2   | I         | -             | -                     | Length of scalar<br>K                            | Length of scalar<br>K                            |

| nu1PointBase | nu1  | I/O       | Crypto<br>RAM | 3*u2ModLength<br>+ 12 | Input point A<br>(projective<br>coordinates)     | Resulting point<br>C (projective<br>coordinates) |

| nu1ABase     | nu1  | 1         | Crypto<br>RAM | 2*u2ModLength<br>+ 8  | Parameters a and<br>b of the elliptic<br>curve   | Unchanged                                        |

| nu1Workspace | nu1  | 1         | Crypto<br>RAM | 8*u2ModLength<br>+ 44 | _                                                | Corrupted<br>workspace                           |

#### 43.3.7.4.5 Code Example

```

PUKCL_PARAM PUKCLParam;

PPUKCL_PARAM pvPUKCLParam = &PUKCLParam;

```

```

PUKCL (u2Option) = 0;

```

#### 46.8.5 Interrupt Enable Set

Name:INTENSETOffset:0x05Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1     | 0     |

|--------|---|---|---|------|---|---|-------|-------|

|        |   |   |   | WIN0 |   |   | COMPx | COMPx |

| Access |   |   |   | R/W  |   |   | R/W   | R/W   |

| Reset  |   |   |   | 0    |   |   | 0     | 0     |

#### Bit 4 – WIN0 Window 0 Interrupt Enable

Reading this bit returns the state of the Window 0 interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit enables the Window 0 interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Window 0 interrupt is disabled. |

| 1     | The Window 0 interrupt is enabled.  |

#### **Bits 1,0 – COMPx** Comparator x Interrupt Enable

Reading this bit returns the state of the Comparator x interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Ready interrupt bit and enable the Ready interrupt.

|   | Value | Description                             |

|---|-------|-----------------------------------------|

| [ | 0     | The Comparator x interrupt is disabled. |

|   | 1     | The Comparator x interrupt is enabled.  |

### DAC – Digital-to-Analog Converter

| 47.8.8          | Synchroni                               | zation Busy                         |          |          |       |       |        |       |

|-----------------|-----------------------------------------|-------------------------------------|----------|----------|-------|-------|--------|-------|

|                 | Name:<br>Offset:<br>Reset:<br>Property: | SYNCBUSY<br>0x08<br>0x00000000<br>- |          |          |       |       |        |       |

| Bit             | t 31                                    | 30                                  | 29       | 28       | 27    | 26    | 25     | 24    |

|                 |                                         |                                     |          |          |       |       |        |       |

| Access          |                                         |                                     |          |          |       |       |        |       |

| Reset           | t                                       |                                     |          |          |       |       |        |       |

| Bit             | t23                                     | 22                                  | 21       | 20       | 19    | 18    | 17     | 16    |

|                 |                                         |                                     |          |          |       |       |        |       |

| Access<br>Reset |                                         |                                     |          |          |       |       |        |       |

| Bi              | t 15                                    | 14                                  | 13       | 12       | 11    | 10    | 9      | 8     |

| Access<br>Rese  |                                         |                                     |          |          |       |       |        |       |

| Bit             | t 7                                     | 6                                   | 5        | 4        | 3     | 2     | 1      | 0     |

|                 |                                         |                                     | DATABUF1 | DATABUF0 | DATA1 | DATA0 | ENABLE | SWRST |

| Access          | ;                                       |                                     | R        | R        | R     | R     | R      | R     |

| Reset           | t                                       |                                     | 0        | 0        | 0     | 0     | 0      | 0     |

#### Bit 5 - DATABUF1 Data Buffer DAC1

This bit is set when DATABUF1 register is written.

This bit is cleared when DATABUF1 synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

#### Bit 4 – DATABUF0 Data Buffer DAC0

This bit is set when DATABUF0 register is written.

This bit is cleared when DATABUF0 synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

#### Bit 3 – DATA1 Data DAC1

This bit is set when DATA1 register is written.

This bit is cleared when DATA1 synchronization is completed.

#### 48.7.1.3 Control B Set

Name:CTRLBSETOffset:0x05Reset:0x00Property:PAC Write-Protection, Read-synchronized, Write-Synchronized

This register allows the user to set bits in the CTRLB register without doing a read-modify-write operation. Changes in this register will also be reflected in the Control B Clear register (CTRLBCLR).

| Bit    | 7   | 6        | 5   | 4 | 3 | 2       | 1    | 0   |

|--------|-----|----------|-----|---|---|---------|------|-----|

|        |     | CMD[2:0] |     |   |   | ONESHOT | LUPD | DIR |

| Access | R/W | R/W      | R/W |   |   | R/W     | R/W  | R/W |

| Reset  | 0   | 0        | 0   |   |   | 0       | 0    | 0   |

#### Bits 7:5 – CMD[2:0] Command

These bits are used for software control of the TC. The commands are executed on the next prescaled GCLK\_TC clock cycle. When a command has been executed, the CMD bit group will be read back as zero.

Writing 0x0 to these bits has no effect.

Writing a value different from 0x0 to these bits will issue a command for execution.

| Value | Name      | Description                               |

|-------|-----------|-------------------------------------------|

| 0x0   | NONE      | No action                                 |

| 0x1   | RETRIGGER | Force a start, restart or retrigger       |

| 0x2   | STOP      | Force a stop                              |

| 0x3   | UPDATE    | Force update of double buffered registers |

| 0x4   | READSYNC  | Force a read synchronization of COUNT     |

#### Bit 2 - ONESHOT One-Shot on Counter

This bit controls one-shot operation of the TC.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will enable one-shot operation.

| Value | Description                                                                       |

|-------|-----------------------------------------------------------------------------------|

| 0     | The TC will wrap around and continue counting on an overflow/underflow condition. |

| 1     | The TC will wrap around and stop on the next underflow/overflow condition.        |

#### Bit 1 – LUPD Lock Update

This bit controls the update operation of the TC buffered registers.

When CTRLB.LUPD is set, no any update of the registers with value of its buffered register is performed on hardware UPDATE condition. Locking the update ensures that all buffer registers are valid before an hardware update is performed. After all the buffer registers are loaded correctly, the buffered registers can be unlocked.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the LUPD bit.

#### 48.7.3.8 Status

| Name:     | STATUS            |

|-----------|-------------------|

| Offset:   | 0x0B              |

| Reset:    | 0x01              |

| Property: | Read-Synchronized |

| Bit    | 7 | 6 | 5 | 4       | 3       | 2 | 1     | 0    |

|--------|---|---|---|---------|---------|---|-------|------|

|        |   |   |   | CCBUFVx | PERBUFV |   | SLAVE | STOP |

| Access |   |   |   | R/W     | R/W     |   | R     | R    |

| Reset  |   |   |   | 0       | 0       |   | 0     | 1    |

#### Bit 4 – CCBUFVx Channel x Compare or Capture Buffer Valid

For a compare channel x, the bit x is set when a new value is written to the corresponding CCBUFx register.

The bit x is cleared by writing a '1' to it when CTRLB.LUPD is set, or it is cleared automatically by hardware on UPDATE condition.

For a capture channel x, the bit x is set when a valid capture value is stored in the CCBUFx register. The bit x is cleared automatically when the CCx register is read.

#### Bit 3 – PERBUFV Period Buffer Valid

This bit is set when a new value is written to the PERBUF register. The bit is cleared by writing '1' to the corresponding location when CTRLB.LUPD is set, or automatically cleared by hardware on UPDATE condition. This bit is available only in 8-bit mode and will always read zero in 16- and 32-bit modes.

#### Bit 1 – SLAVE Slave Status Flag

This bit is only available in 32-bit mode on the slave TC (i.e., TC1 and/or TC3). The bit is set when the associated master TC (TC0 and TC2, respectively) is set to run in 32-bit mode.

#### Bit 0 – STOP Stop Status Flag

This bit is set when the TC is disabled, on a Stop command, or on an overflow/underflow condition when the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT) is '1'.

| Value | Description         |

|-------|---------------------|

| 0     | Counter is running. |

| 1     | Counter is stopped. |

PCC - Parallel Capture Controller

| Value | Description                                                 |

|-------|-------------------------------------------------------------|

| 0     | No new data is ready to be read since the last read of RHR. |

| 1     | New data is ready to be read since the last read of RHR.    |

**Electrical Characteristics at 85°C**

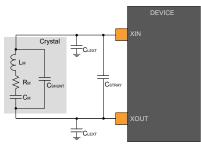

#### Figure 54-6. Oscillator Connection

The user must choose a crystal oscillator where the crystal load capacitance  $C_L$  is within the range given in the Table. The exact value of  $C_L$  can be found in the crystal datasheet. The capacitance of the external capacitors ( $C_{LEXT}$ ) can then be computed as follows:

$C_{\text{LEXT}} = 2(C_{\text{L}} - C_{\text{STRAY}} - _{\text{SHUNT}})$ ,

where C<sub>SHUNT</sub> is the shunt capacity of the crystal, and C<sub>STRAY</sub> is the capacitance of the pins and the PCB:

$C_{\text{STRAY}} = C_{\text{StrayDevice}} + C_{\text{StrayPCB}}$ , and  $1/C_{\text{StrayDevice}} = 1/C_{\text{XIN}} + 1/C_{\text{XOUT}}$ .

Table 54-40. Multi-Crystal Oscillator Electrical Characteristics

| Symbol           | Parameter                              | Conditions                                                        | Min. | Тур.  | Max.  | Units  |

|------------------|----------------------------------------|-------------------------------------------------------------------|------|-------|-------|--------|

| FOUT             | Crystal oscillator frequency           |                                                                   | 8    | -     | 48    | MHz    |

| CL               | Crystal Load                           | F = 8 MHz                                                         | -    | -     | 20    | pF     |

|                  |                                        | F = 16 MHz                                                        | -    | -     | 20    |        |

|                  |                                        | F = 32 MHz                                                        | -    | -     | 13    |        |

|                  |                                        | F = 48 MHz                                                        | -    | -     | 13    |        |

| ESR              | Crystal Equivalent Series Resistance - | F = 8 MHz, CL=20 pF - IMULT = 0x3                                 | -    | -     | 181   | Ω      |

| SF=3             | SF=3                                   | F = 16 MHz, CL = 20 pF - IMULT = 0x4                              | -    | -     | 180   | _      |

|                  |                                        | F= 24 MHz, C <sub>L</sub> = 20 pF - IMULT = 0x5                   | -    | -     | 70    |        |

|                  | F = 48 MHz, CL = 13 pF - IMULT = 0x6   | -                                                                 | -    | 70    |       |        |

| C <sub>XIN</sub> | Parasitic load capacitor               | -                                                                 | -    | 6.3   | -     | pF     |

| CXOUT            |                                        | -                                                                 | -    | 5.9   | -     |        |

| DL               | Drive Level (see Note 1)               | ENALC = ON                                                        | -    | -     | 100   | μW     |

| TSTART           | Startup time                           | F = 8 MHz, $C_L$ = 20 pF, $C_{SHUNT}$ = 2 pF - IMULT = 0x3        | -    | 39700 | 72200 | Cycles |

|                  |                                        | $F$ = 16 MHz, $C_{L}$ = 20 pF, $C_{SHUNT}$ = 1.5 pF - IMULT = 0x4 | -    | 37550 | 62000 |        |

|                  |                                        | $F$ = 24 MHz, $C_L$ = 20 pF, $C_SHUNT$ = 2.5 pF - IMULT = 0x5     | -    | 32700 | 68500 |        |

|                  |                                        | F = 48 MHz, CL = 13 pF, CSHUNT = 5 pF - IMULT = 0x6               | -    | 18400 | 38500 |        |

**Note:** To ensure that the crystal is not overdriven, the automatic loop control is recommended to be turned ON (ENALC = 1).

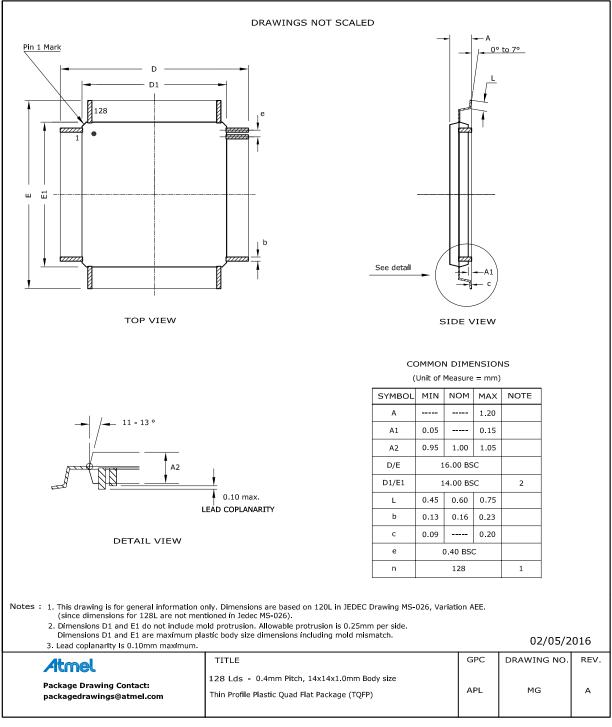

### **Packaging Information**

#### 55.3.7 128 pin TQFP

| 520 | mg |

|-----|----|

|-----|----|

#### Table 55-15. Package Characteristics

| Moisture Sensitivity Level | MSL3 |

|----------------------------|------|

|----------------------------|------|