Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 120MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                             |

| Number of I/O              | 51                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-TQFP                                                                             |

| Supplier Device Package    | 64-TQFP (10x10)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame51j20a-aut          |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 29.2.   | Features                                                     | 832   |

|---------|--------------------------------------------------------------|-------|

| 29.3.   | Block Diagram                                                | 833   |

| 29.4.   | Signal Description                                           | 833   |

| 29.5.   | Product Dependencies                                         | 833   |

| 29.6.   | Functional Description                                       | 835   |

| 29.7.   | Register Summary                                             | 840   |

| 29.8.   | Register Description                                         | 840   |

| 30. FRE | QM – Frequency Meter                                         | . 852 |

|         | Overview                                                     |       |

|         | Features                                                     |       |

|         | Block Diagram                                                |       |

|         | Signal Description                                           |       |

|         | Product Dependencies                                         |       |

|         | Functional Description                                       |       |

|         | Register Summary                                             |       |

|         | Register Description                                         |       |

| 00.0.   |                                                              |       |

|         | YS – Event System                                            |       |

|         | Overview                                                     |       |

|         | Features                                                     |       |

|         | Block Diagram                                                |       |

|         | Product Dependencies                                         |       |

|         | Functional Description                                       |       |

| 31.6.   | Register Summary                                             | 876   |

| 31.7.   | Register Description                                         | 883   |

| 32. POF | RT - I/O Pin Controller                                      | 904   |

| 32.1.   | Overview                                                     | 904   |

| 32.2.   | Features                                                     | 904   |

| 32.3.   | Block Diagram                                                | 905   |

| 32.4.   | Signal Description                                           | 905   |

| 32.5.   | Product Dependencies                                         | 905   |

|         | Functional Description                                       |       |

|         | Register Summary                                             |       |

|         | PORT Pin Groups and Register Repetition                      |       |

|         | Register Description                                         |       |

| 33 SER  | COM – Serial Communication Interface                         | 939   |

|         |                                                              |       |

|         | Overview                                                     |       |

|         | Features                                                     |       |

|         | Block Diagram                                                |       |

|         | Signal Description                                           |       |

|         | Product Dependencies                                         |       |

| 33.6.   | Functional Description                                       | 942   |

| 34. SER | COM USART - SERCOM Synchronous and Asynchronous Receiver and |       |

| Tran    | smitter                                                      | 948   |

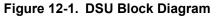

# 12.3 Block Diagram

# 12.4 Signal Description

The DSU uses three signals to function.

| Signal Name | Туре          | Description               |

|-------------|---------------|---------------------------|

| RESET       | Digital Input | External reset            |

| SWCLK       | Digital Input | SW clock                  |

| SWDIO       | Digital I/O   | SW bidirectional data pin |

# **Related Links**

6. I/O Multiplexing and Considerations

# 12.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 12.5.1 I/O Lines

The SWCLK pin is by default assigned to the DSU module to allow debugger probe detection and to stretch the CPU reset phase. For more information, refer to 12.6.3 Debugger Probe Detection. The Hot-Plugging feature depends on the PORT configuration. If the SWCLK pin function is changed in the PORT or if the PORT\_MUX is disabled, the Hot-Plugging feature is disabled until a power-reset or an external reset is performed.

# 12.5.2 Power Management

The DSU will continue to operate in Idle mode.

# DSU - Device Service Unit

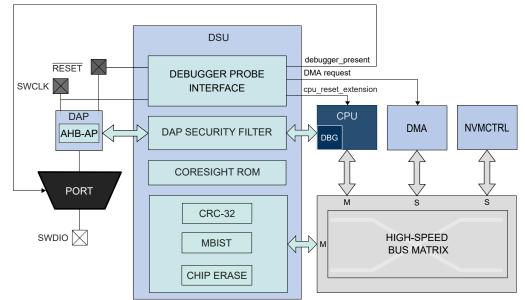

### 12.13.23 Component Identification 1

# Bits 7:4 - CCLASS[3:0] Component Class

These bits will always return 0x1 when read indicating that this ARM CoreSight component is ROM table (refer to the ARM Debug Interface v5 Architecture Specification at http://www.arm.com).

# Bits 3:0 - PREAMBLE[3:0] Preamble

These bits will always return 0x00 when read.

# DSU - Device Service Unit

|        | Name:<br>Offset:<br>Reset:<br>Property: | CID2<br>0x1FF8<br>0x00000005<br>- |    |        |           |    |          |          |

|--------|-----------------------------------------|-----------------------------------|----|--------|-----------|----|----------|----------|

| Bit    | 31                                      | 30                                | 29 | 28     | 27        | 26 | 25       | 24       |

|        |                                         |                                   |    |        |           |    |          |          |

| Access |                                         |                                   |    |        |           |    |          |          |

| Reset  |                                         |                                   |    |        |           |    |          |          |

|        |                                         |                                   |    |        |           |    |          |          |

| Bit    | 23                                      | 22                                | 21 | 20     | 19        | 18 | 17       | 16       |

|        |                                         |                                   |    |        |           |    |          |          |

| Access |                                         |                                   |    |        |           |    |          |          |

| Reset  |                                         |                                   |    |        |           |    |          |          |

| Bit    | 15                                      | 14                                | 13 | 12     | 11        | 10 | 9        | 8        |

| Dit    |                                         | 17                                | 10 | 12     |           |    | <u> </u> | <u> </u> |

| Access |                                         |                                   |    |        |           |    |          |          |

| Reset  |                                         |                                   |    |        |           |    |          |          |

|        |                                         |                                   |    |        |           |    |          |          |

| Bit    | 7                                       | 6                                 | 5  | 4      | 3         | 2  | 1        | 0        |

|        |                                         |                                   |    | PREAMB | LEB2[7:0] |    |          |          |

| Access | R                                       | R                                 | R  | R      | R         | R  | R        | R        |

| Reset  | 0                                       | 0                                 | 0  | 0      | 0         | 1  | 0        | 1        |

|        |                                         |                                   |    |        |           |    |          |          |

12.13.24 Component Identification 2

**Bits 7:0 – PREAMBLEB2[7:0]** Preamble Byte 2 These bits will always return 0x00000005 when read.

MCLK – Main Clock

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBB clock for the SERCOMn is stopped. |

| 1     | The APBB clock for the SERCOMn is enabled. |

### Bit 7 – EVSYS EVSYS APBB Clock Enable

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The APBB clock for the EVSYS is stopped. |

| 1     | The APBB clock for the EVSYS is enabled. |

### Bit 4 – PORT PORT APBB Clock Enable

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The APBB clock for the PORT is stopped. |

| 1     | The APBB clock for the PORT is enabled. |

### Bit 2 – NVMCTRL NVMCTRL APBB Clock Enable

| Value | Description                                |

|-------|--------------------------------------------|

| 0     | The APBB clock for the NVMCTRL is stopped. |

| 1     | The APBB clock for the NVMCTRL is enabled. |

### Bit 1 – DSU DSU APBB Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBB clock for the DSU is stopped. |

| 1     | The APBB clock for the DSU is enabled. |

# Bit 0 – USB USB APBB Clock Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | The APBB clock for the USB is stopped. |

| 1     | The APBB clock for the USB is enabled. |

and Clear register (CHINTFLAG.SUSP) is set, and the Channel Fetch Error bit in the Channel Status register (CHSTATUS.FERR) is set. If enabled, the optional suspend interrupt is generated.

# 22.6.3 Additional Features

### 22.6.3.1 Linked Descriptors

A transaction can consist of either a single block transfer or of several block transfers. When a transaction consists of several block transfers it is done with the help of linked descriptors.

Figure 22-3 illustrates how linked descriptors work. When the first block transfer is completed on DMA channel 0, the DMAC fetches the next transfer descriptor, which is pointed to by the value stored in the Next Descriptor Address (DESCADDR) register of the first transfer descriptor. Fetching the next transfer descriptor (DESCADDR) is continued until the last transfer descriptor. When the block transfer for the last transfer descriptor is executed and DESCADDR=0x00000000, the transaction is terminated. For further details on how the next descriptor is fetched from SRAM, refer to section 22.6.2.5 Data Transmission.

### 22.6.3.1.1 Adding Descriptor to the End of a List

To add a new descriptor at the end of the descriptor list, create the descriptor in SRAM, with DESCADDR=0x00000000 indicating that it is the new last descriptor in the list, and modify the DESCADDR value of the current last descriptor to the address of the newly created descriptor.

### 22.6.3.1.2 Modifying a Descriptor in a List

In order to add descriptors to a linked list, the following actions must be performed:

- 1. Enable the Suspend interrupt for the DMA channel.

- 2. Enable the DMA channel.

- 3. Reserve memory space in SRAM to configure a new descriptor.

- 4. Configure the new descriptor:

- Set the next descriptor address (DESCADDR)

- Set the destination address (DSTADDR)

- Set the source address (SRCADDR)

- Configure the block transfer control (BTCTRL) including

- Optionally enable the Suspend block action

- Set the descriptor VALID bit

- 5. Clear the VALID bit for the existing list and for the descriptor which has to be updated.

- 6. Read DESCADDR from the Write-Back memory.

- If the DMA has not already fetched the descriptor which requires changes (i.e., DESCADDR is wrong):

- Update the DESCADDR location of the descriptor from the List

- Optionally clear the Suspend block action

- Set the descriptor VALID bit to '1'

- Optionally enable the Resume software command

- If the DMA is executing the same descriptor as the one which requires changes:

- Set the Channel Suspend software command and wait for the Suspend interrupt

- Update the next descriptor address (DESCRADDR) in the write-back memory

- · Clear the interrupt sources and set the Resume software command

- Update the DESCADDR location of the descriptor from the List

- Optionally clear the Suspend block action

- Set the descriptor VALID bit to '1'

# 22.8.22 Channel Interrupt Flag Status and Clear

Name:

CHINTFLAG

Offset:

0x4E + n\*0x10 [n=0..31]

Reset:

0x00

Property:

This register affects the DMA channel that is selected in the Channel ID register (CHID.ID).

| Bit    | 7 | 6 | 5 | 4 | 3 | 2    | 1     | 0    |

|--------|---|---|---|---|---|------|-------|------|

|        |   |   |   |   |   | SUSP | TCMPL | TERR |

| Access |   |   |   |   |   | R/W  | R/W   | R/W  |

| Reset  |   |   |   |   |   | 0    | 0     | 0    |

### Bit 2 – SUSP Channel Suspend

This flag is cleared by writing a '1' to it.

This flag is set when a block transfer with suspend block action is completed, when a software suspend command is executed, when a suspend event is received or when an invalid descriptor is fetched by the DMA.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Channel Suspend interrupt flag for the corresponding channel.

For details on available software commands, refer to CHCTRLB.CMD.

For details on available event input actions, refer to CHCTRLB.EVACT.

For details on available block actions, refer to **BTCTRL**.BLOCKACT.

# Bit 1 – TCMPL Channel Transfer Complete

This flag is cleared by writing a '1' to it.

This flag is set when a block transfer is completed and the corresponding interrupt block action is enabled.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transfer Complete interrupt flag for the corresponding channel.

### Bit 0 – TERR Channel Transfer Error

This flag is cleared by writing a '1' to it.

This flag is set when a bus error is detected during a beat transfer or when the DMAC fetches an invalid descriptor.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transfer Error interrupt flag for the corresponding channel.

# **EIC – External Interrupt Controller**

# 23.4 Signal Description

| Signal Name | Туре          | Description                |

|-------------|---------------|----------------------------|

| EXTINT[150] | Digital Input | External interrupt pin     |

| NMI         | Digital Input | Non-maskable interrupt pin |

One signal may be available on several pins.

# 23.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

# 23.5.1 I/O Lines

Using the EIC's I/O lines requires the I/O pins to be configured.

# **Related Links**

32. PORT - I/O Pin Controller

### 23.5.2 Power Management

All interrupts are available down to STANDBY sleep mode, but the EIC can be configured to automatically mask some interrupts in order to prevent device wake-up.

The EIC will continue to operate in any sleep mode where the selected source clock is running. The EIC's interrupts can be used to wake up the device from sleep modes. Events connected to the Event System can trigger other operations in the system without exiting sleep modes.

# **Related Links**

18. PM – Power Manager

# 23.5.3 Clocks

The EIC bus clock (CLK\_EIC\_APB) can be enabled and disabled by the Main Clock Controller, the default state of CLK\_EIC\_APB can be found in the Peripheral Clock Masking section.

Some optional functions need a peripheral clock, which can either be a generic clock (GCLK\_EIC, for wider frequency selection) or a Ultra Low Power 32KHz clock (CLK\_ULP32K, for highest power efficiency). One of the clock sources must be configured and enabled before using the peripheral:

GCLK\_EIC is configured and enabled in the Generic Clock Controller.

CLK\_ULP32K is provided by the internal ultra-low-power (OSCULP32K) oscillator in the OSC32KCTRL module.

Both GCLK\_EIC and CLK\_ULP32K are asynchronous to the user interface clock (CLK\_EIC\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

# **Related Links**

15. MCLK – Main Clock

15.6.2.6 Peripheral Clock Masking

- 14. GCLK Generic Clock Controller

- 29. OSC32KCTRL 32KHz Oscillators Controller

# 24.9.95 GMAC PTP Peer Event Frame Transmitted Seconds Low Register

| Name:     | PEFTSL     |

|-----------|------------|

| Offset:   | 0x1F0      |

| Reset:    | 0x00000000 |

| Property: | Read-Only  |

| R<br>0   |  |  |  |  |

|----------|--|--|--|--|

|          |  |  |  |  |

| 0        |  |  |  |  |

|          |  |  |  |  |

|          |  |  |  |  |

| 16       |  |  |  |  |

|          |  |  |  |  |

| R        |  |  |  |  |

| 0        |  |  |  |  |

|          |  |  |  |  |

| 8        |  |  |  |  |

|          |  |  |  |  |

| R        |  |  |  |  |

| 0        |  |  |  |  |

|          |  |  |  |  |

| 0        |  |  |  |  |

| RUD[7:0] |  |  |  |  |

| R        |  |  |  |  |

| 0        |  |  |  |  |

|          |  |  |  |  |

### Bits 31:0 - RUD[31:0] Register Update

The register is updated with the value that the IEEE 1588 Timer Seconds Register holds when the SFD of a PTP transmit peer event crosses the MII interface. An interrupt is issued when the register is updated.

SERCOM I2C – Inter-Integrated Circuit

# 36.6.2.4.1 Master Clock Generation

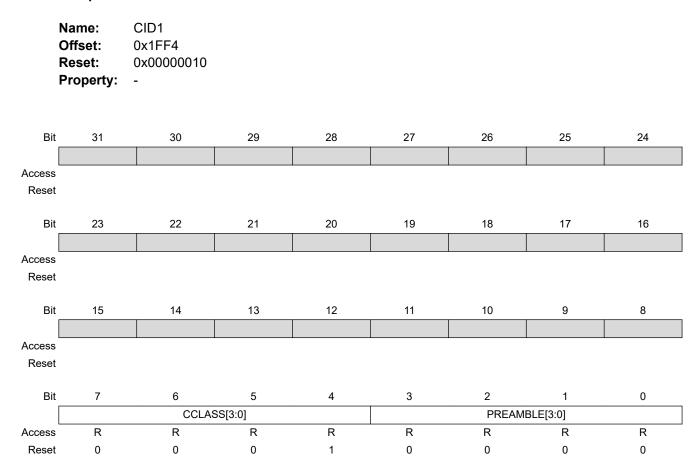

The SERCOM peripheral supports several I<sup>2</sup>C bidirectional modes:

- Standard mode (Sm) up to 100kHz

- Fast mode (*Fm*) up to 400kHz

- Fast mode Plus (*Fm*+) up to 1MHz

- High-speed mode (Hs) up to 3.4MHz

The Master clock configuration for *Sm*, *Fm*, and *Fm*+ are described in Clock Generation (Standard-Mode, Fast-Mode, and Fast-Mode Plus). For *Hs*, refer to Master Clock Generation (High-Speed Mode).

# Clock Generation (Standard-Mode, Fast-Mode, and Fast-Mode Plus)

In I<sup>2</sup>C *Sm, Fm*, and *Fm*+ mode, the Master clock (SCL) frequency is determined as described in this section:

The low (T<sub>LOW</sub>) and high (T<sub>HIGH</sub>) times are determined by the Baud Rate register (BAUD), while the rise (T<sub>RISE</sub>) and fall (T<sub>FALL</sub>) times are determined by the bus topology. Because of the wired-AND logic of the bus, T<sub>FALL</sub> will be considered as part of T<sub>LOW</sub>. Likewise, T<sub>RISE</sub> will be in a state between T<sub>LOW</sub> and T<sub>HIGH</sub> until a high state has been detected.

# SERCOM I2C – Inter-Integrated Circuit

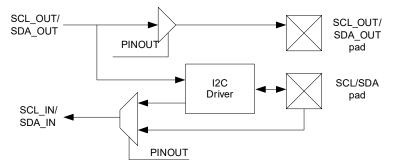

### Figure 36-14. I<sup>2</sup>C Pad Interface

### 36.6.3.4 Quick Command

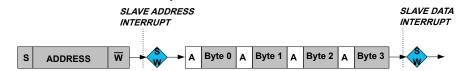

Setting the Quick Command Enable bit in the Control B register (CTRLB.QCEN) enables quick command. When quick command is enabled, the corresponding interrupt flag (INTFLAG.SB or INTFLAG.MB) is set immediately after the slave acknowledges the address. At this point, the software can either issue a stop command or a repeated start by writing CTRLB.CMD or ADDR.ADDR.

#### 36.6.3.5 32-bit Extension

For better system bus utilization, 32-bit data receive and transmit can be enabled by writing to the Data 32-bit bit field in the Control C register (CTRLC.DATA32B=1). When enabled, write and read transaction to/from the DATA register are 32 bit in size.

If frames are not multiples of 4 Bytes, the Length Counter (LENGTH.LEN) and Length Enable (LENGTH.LENEN) must be configured before data transfer begins. LENGTH.LEN must be enabled only when CTRLC.DATA32B is enabled.

The figure below shows the order of transmit and receive when using 32-bit mode. Bytes are transmitted or received and stored in order from 0 to 3.

### Figure 36-15. 32-bit Extension Byte Ordering

| APB Write/Read | BYTE3 | BYTE2 | BYTE1 | BYTE0 |   |

|----------------|-------|-------|-------|-------|---|

| Bit Position 3 | 1     |       |       | C     | , |

### 32-bit Extension Slave Operation

The figure below shows a transaction with 32-bit Extension enabled (CTRLC.DATA32B=1). In slave operation, the Address Match interrupt in the Interrupt Flag Status and Clear register (INTFLAG.AMATCH) is set after the address is received and available in the DATA register. The Data Ready interrupt (INTFLAG.DRDY) will then be raised for every 4 Bytes transferred.

### Figure 36-16. 32-bit Extension Slave Operation

The LENGTH register can be written before the frame begins, or when the AMATCH interrupt is set. If the frame size is not LENGTH.LEN Bytes, the Length Error status bit (STATUS.LENERR) is raised. If LENGTH.LEN is not a multiple of 4 Bytes, the final INTFLAG.DRDY interrupt is raised when the last Byte is received for master reads. For master writes, the last data byte will be automatically NACKed. On address recognition, the internal length counter is reset in preparation for the incoming frame.

High Speed transactions start with a Full Speed Master Code. When a Master Code is detected, no data is received and the next expected operation is a repeated start. For this reason, the length is not counted

© 2018 Microchip Technology Inc.

#### 38.8.2.5 Device Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x0000               |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 15      | 14    | 13    | 12     | 11    | 10  | 9       | 8       |

|--------|---------|-------|-------|--------|-------|-----|---------|---------|

|        |         |       |       |        |       |     | LPMSUSP | LPMNYET |

| Access |         |       |       |        |       |     | R/W     | R/W     |

| Reset  |         |       |       |        |       |     | 0       | 0       |

|        |         |       |       |        |       |     |         |         |

| Bit    | 7       | 6     | 5     | 4      | 3     | 2   | 1       | 0       |

|        | RAMACER | UPRSM | EORSM | WAKEUP | EORST | SOF |         | SUSPEND |

| Access | R/W     | R/W   | R/W   | R/W    | R/W   | R/W |         | R/W     |

| Reset  | 0       | 0     | 0     | 0      | 0     | 0   |         | 0       |

**Bit 9 – LPMSUSP** Link Power Management Suspend Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Link Power Management Suspend Interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The Link Power Management Suspend interrupt is disabled.                                |

| 1     | The Link Power Management Suspend interrupt is enabled and an interrupt request will be |

|       | generated when the Link Power Management Suspend interrupt Flag is set.                 |

**Bit 8 – LPMNYET** Link Power Management Not Yet Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Link Power Management Not Yet interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The Link Power Management Not Yet interrupt is disabled.                                |

| 1     | The Link Power Management Not Yet interrupt is enabled and an interrupt request will be |

|       | generated when the Link Power Management Not Yet interrupt Flag is set.                 |

### Bit 7 – RAMACER RAM Access Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the RAM Access interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                             |

|-------|-----------------------------------------------------------------------------------------|

| 0     | The RAM Access interrupt is disabled.                                                   |

| 1     | The RAM Access interrupt is enabled and an interrupt request will be generated when the |

|       | RAM Access interrupt Flag is set.                                                       |

# Bits 6:4 - F1DS[2:0] Rx FIFO 1 Data Field Size

In case the data field size of an accepted CAN frame exceeds the data field size configured for the matching Rx FIFO 1, only the number of bytes as configured by RXESC are stored to the Rx FIFO 1 element. The rest of the frame's data field is ignored.

| Value | Name   | Description         |

|-------|--------|---------------------|

| 0x0   | DATA8  | 8 byte data field.  |

| 0x1   | DATA12 | 12 byte data field. |

| 0x2   | DATA16 | 16 byte data field. |

| 0x3   | DATA20 | 20 byte data field. |

| 0x4   | DATA24 | 24 byte data field. |

| 0x5   | DATA32 | 32 byte data field. |

| 0x6   | DATA48 | 48 byte data field. |

| 0x7   | DATA64 | 64 byte data field. |

# Bits 2:0 - F0DS[2:0] Rx FIFO 0 Data Field Size

In case the data field size of an accepted CAN frame exceeds the data field size configured for the matching Rx FIFO 0, only the number of bytes as configured by RXESC are stored to the Rx FIFO 0 element. The rest of the frame's data field is ignored.

| Value | Name   | Description         |

|-------|--------|---------------------|

| 0x0   | DATA8  | 8 byte data field.  |

| 0x1   | DATA12 | 12 byte data field. |

| 0x2   | DATA16 | 16 byte data field. |

| 0x3   | DATA20 | 20 byte data field. |

| 0x4   | DATA24 | 24 byte data field. |

| 0x5   | DATA32 | 32 byte data field. |

| 0x6   | DATA48 | 48 byte data field. |

| 0x7   | DATA64 | 64 byte data field. |

SD/MMC Host Controller ...

| Value | Description |

|-------|-------------|

| 0     | Work        |

| 1     | Reset       |

ADC – Analog-to-Digital Converter

The ADC can take the following actions on an input event:

- Start conversion (START): Start a conversion. Refer to SWTRIG register for details.

- Conversion flush (FLUSH): Flush the conversion. Refer to SWTRIG register for details.

Setting an Event Input bit in the Event Control register (EVCTRL.xxEI=1) enables the corresponding action on input event. Clearing this bit disables the corresponding action on input event.

The ADC uses only asynchronous events, so the asynchronous Event System channel path must be configured. By default, the ADC will detect a rising edge on the incoming event. If the ADC action must be performed on the falling edge of the incoming event, the event line must be inverted first. This is done by setting the corresponding Event Invert Enable bit in Event Control register (EVCTRL.xINV=1).

**Note:** If several events are connected to the ADC, the enabled action will be taken on any of the incoming events. If FLUSH and START events are available at the same time, the FLUSH event has priority.

### **Related Links**

45.8.2 EVCTRL45.8.5 CTRLB45.8.13 SWTRIG31. EVSYS – Event System

### 45.6.7 Sleep Mode Operation

The ONDEMAND and RUNSTDBY bits in the Control A register (CTRLA) control the behavior of the ADC during standby sleep mode, in cases where the ADC is enabled (CTRLA.ENABLE = 1). For further details on available options, refer to Table 45-6.

**Note:** When CTRLA.ONDEMAND=1, the analog block is powered-off when the conversion is complete. When a start request is detected, the system returns from sleep and starts a new conversion after the start-up time delay.

| CTRLA.RUNSTDBY | CTRLA.ONDEMAND | CTRLA.ENABLE | Description                                        |

|----------------|----------------|--------------|----------------------------------------------------|

| x              | x              | 0            | Disabled                                           |

| 0              | 0              | 1            | Run in all sleep modes except<br>STANDBY.          |

| 0              | 1              | 1            | Run in all sleep modes on request, except STANDBY. |

| 1              | 0              | 1            | Run in all sleep modes.                            |

| 1              | 1              | 1            | Run in all sleep modes on request.                 |

### Table 45-6. ADC Sleep Behavior

### 45.6.8 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in Control A register (CTRLA.SWRST)

- Enable bit in Control A register (CTRLA.ENABLE)

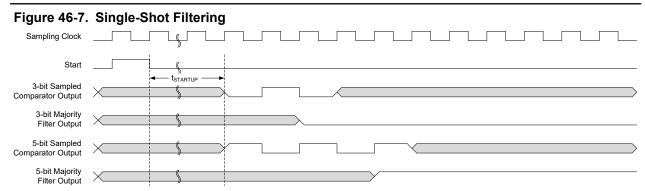

During sleep modes, filtering is supported only for single-shot measurements. Filtering must be disabled if continuous measurements will be done during sleep modes, or the resulting interrupt/event may be generated incorrectly.

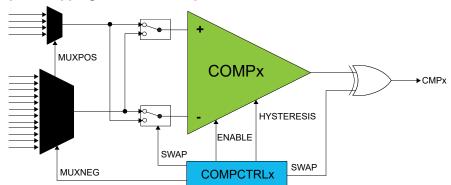

### 46.6.8 Comparator Output

The output of each comparator can be routed to an I/O pin by setting the Output bit group in the Comparator Control x register (COMPCTRLx.OUT). This allows the comparator to be used by external circuitry. Either the raw, non-synchronized output of the comparator or the CLK\_AC-synchronized version, including filtering, can be used as the I/O signal source. The output appears on the corresponding CMP[x] pin.

#### 46.6.9 Offset Compensation

The Swap bit in the Comparator Control registers (COMPCTRLx.SWAP) controls switching of the input signals to a comparator's positive and negative terminals. When the comparator terminals are swapped, the output signal from the comparator is also inverted, as shown in Figure 46-8. This allows the user to measure or compensate for the comparator input offset voltage. As part of the input selection, COMPCTRLx.SWAP can be changed only while the comparator is disabled.

#### Figure 46-8. Input Swapping for Offset Compensation

### 46.6.10 DMA Operation

Not applicable.

### 46.6.11 Interrupts

The AC has the following interrupt sources:

- Comparator (COMP0, COMP1): Indicates a change in comparator status.

- Window (WIN0): Indicates a change in the window status.

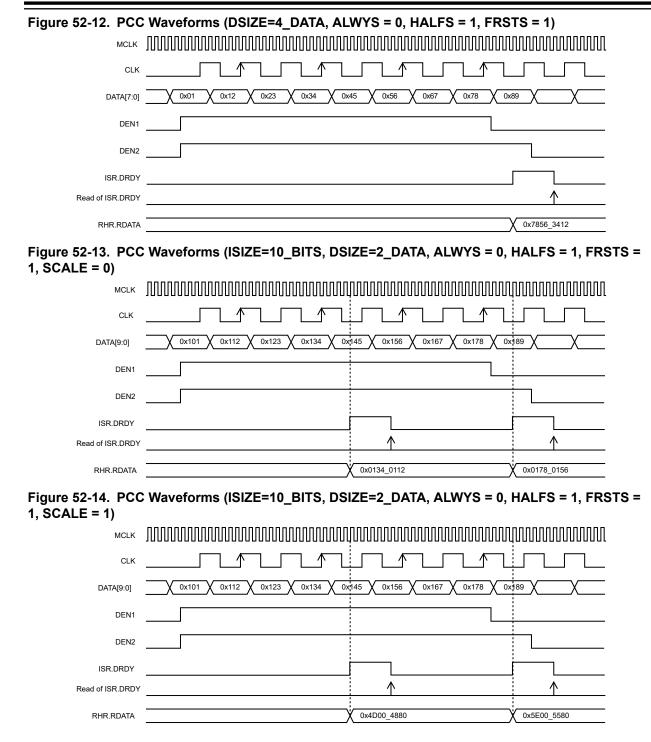

**PCC - Parallel Capture Controller**

# 52.6.2 Register Access Protection

The configuration bit fields ISIZE, SCALE, DSIZE, ALWYS, HALFS and FRSTS in the Mode Register (MR) can be changed ONLY if the PCC is disabled at this time (MR.PCEN=0).

### 53.6.2.6.4 Missing Pulse Detection and Auto-Correction

The PDEC embeds circuitry to detect and correct errors that may result from contamination on optical disks or other sources producing quadrature phase signals.

The auto-correction works in QDEC X4 mode only. A missing pulse on a phase signal is automatically detected, and the pulse count reported in the Angular part of COUNT is automatically corrected.

There is no autocorrection if both phase signals are affected at the same location on the input signals, because the autocorrection requires a valid phase signal to detect contamination on the other phase signal.

If the quadrature source is undamaged, the number of pulses counted for a predefined period of time must be the same with or without detection and auto-correction. Therefore, if the measurement results differ, a contamination exists on the source producing the quadrature signals. This does not substitute the measurements of the number of pulses between two index pulses (if available) but provides an additional method to detect damaged quadrature sources.

When the source providing quadrature signals is strongly damaged, potentially leading to a number of consecutive missing pulses greater than 1, the quadrature decoder processing may be affected.

The Maximum Consecutive Missing Pulses bits in Control A register (CTRLA.MAXCMP) define the maximum acceptable number of consecutive missing pulses. If the limit is reached, the Missing Pulse Error flag in Status register (STATUS.MPERR) is set. The Error Interrupt flag is set (INTFLAG.ERR) and an optional interrupt can be generated.

Note: When the MAXCMP value is zero, the MPERR error flag is never set.

### 53.6.3 Additional Features

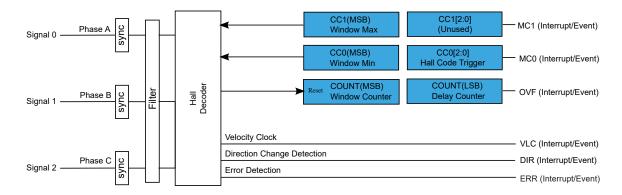

### 53.6.3.1 HALL Operation Mode

In HALL operation mode, control logic signal 0, 1 and 2 inputs represent the phase A, B and C of a Hall sensor, respectively.

A programmable delayed event can be generated to update a TCC pattern generator.

### Figure 53-8. HALL Block Diagram

### **Related Links**

53.3 Block Diagram

### 53.6.3.1.1 Hall Sensor Control

On any update of the filter output:

### 53.6.3.3 Register Lock Update

Prescaler (PRESC), FILTER, and CCx registers are buffered (PRESCBUF, FILTERBUF, CCBUFx registers, respectively). When a new value is written in a buffer register, the corresponding Buffer Valid bit is set in the Buffer Status register (STATUS.FILTERBUFV, STATUS.PRESCBUFV, STATUS.CCBUFVx).

By default, a register is updated with the its buffer register's value on UPDATE condition, which represents:

- The next filter transition in QDEC and HALL mode of operation

- The overflow/underflow or re-trigger event detection in COUNT mode of operation

The buffer valid flags in the STATUS register are automatically cleared by hardware when the data is copied from the buffer to the corresponding register.

It is possible to lock the updates by writing a '1' to the Lock Update bit in Control B Set register (CTRLBSET.LUPD).

The lock feature is disabled by writing a '1' to the Lock Update bit in Control B Clear register (CTRLBCLR.LUPD). When a buffer valid status flag is '1' and updating is not locked, the data from the buffer register will be copied into the corresponding register on UPDATE condition.

It is also possible to modify the LUPD bit behavior by hardware, by writing a '1' to the Auto-lock bit in Control A register (CTRLA.ALOCK). When the bit is '1', the Lock Update bit in Control B register (CTRLBSET.LUPD) is set when the UPDATE condition is detected.

### 53.6.3.4 Software Command and Event Actions

The PDEC peripheral supports software commands and event actions. The software commands are applied by the Software Command bit field in the Control B register (CTRLBSET.CMD, CTRLBCLR.CMD). The event actions are available in the Event Action bit-field in Event Control register (EVCTRL.EVACT).

### 53.6.3.4.1 Re-trigger Software Command or Event Action

A re-trigger command can be issued from software by using PDEC Command bits in Control B Set register (CTRLBSET.CMD = RETRIGGER) or when the re-trigger event action is configured in the Input Event Action bits in Event Control register (EVCTRL.EVACT = RETRIGGER) and an event is detected by hardware.

When the re-trigger command is detected during counting operation, the counter will be reloaded or cleared, depending on the counting direction (DIR). If the re-trigger command is detected when the counter is stopped, the counter will resume counting operation from the value in the COUNT register.

**Note:** When re-trigger event action is enabled, enabling the counter will not start the counter. The counter will start on the next incoming event and restart on any following event.

### 53.6.3.4.2 Count Event Action

The count action can be selected in the Event Control register (EVCTRL.EVACT) and can be used to count external events. When an event is received, the counter increments the value.

### 53.6.3.4.3 Force Update Software Command

A Force Update command can be issued by writing the PDEC Command bits in Control B Set register (CTRLBSET.CMD = UPDATE). When the command is issued, the buffered registers will be updated.

### 53.6.3.4.4 Force Read Synchronization Software Command

A Force Read Synchronization command can be issued writing the PDEC Command bits in Control B Set register (CTRLBSET.CMD = READSYNC). When the command is issued, a COUNT register read synchronization is forced.

**Note:** This command should be used to read the most updated COUNT internal value.

Electrical Characteristics at 85°C

| Symbol | Parameter                     | Conditions                                                 |                                                                     | Min. | Тур.     | Max.     | Unit |

|--------|-------------------------------|------------------------------------------------------------|---------------------------------------------------------------------|------|----------|----------|------|

|        |                               | fADC = 1 Msps - R2R<br>enabled (see <b>Note 1</b> )        | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> | 11.1 | 11.4     | 11.6     |      |

| TUE    | Total<br>Unadjusted<br>Error  | fADC = 500 ksps -<br>R2R disabled                          | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> | -    | ±2.2     | ±5.2     | LSB  |

|        |                               |                                                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= 2.0V               | -    | ±3.4     | ±9.4     |      |

|        |                               | fADC = 1 Msps - R2R<br>disabled                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> | -    | ±2.3     | ±5.2     |      |

| INL    | Integral Non<br>Linearity     | fADC = 500 ksps -<br>R2R disabled                          | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> | -    | ±1.1     | ±1.7     | LSB  |

|        |                               |                                                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= 2.0V               | -    | ±1.3     | ±2.2     |      |

|        |                               | fADC = 1 Msps - R2R<br>disabled                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> | -    | ±1.2     | ±1.5     |      |

| DNL    | Differential<br>Non Linearity | fADC = 500 ksps -<br>R2R disabled                          | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> | -    | ±1       | ±1       | LSB  |

|        |                               |                                                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= 2.0V               | -    | -1/+0.98 | -1/+1.02 |      |

|        |                               | fADC = 1 Msps - R2R<br>disabled                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> | -    | ±1       | ±1       |      |

| Gain   | Gain Error                    | fADC = 1 Msps - R2R<br>disabled w/o gain<br>compensation   | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= V <sub>DDANA</sub> |      | ±0.001   | ±0.2     | %    |

|        |                               |                                                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= 2.0V               |      | ±0.07    | ±0.9     |      |

|        |                               |                                                            | V <sub>DDANA</sub> = 3.0V, 1V<br>Internal Ref                       |      | ±1       | ±4.9     |      |

|        |                               |                                                            | $V_{DDANA} = 3.0V, V_{REF}$<br>= $V_{DDANA}/2$                      |      | ±0.11    | ±1       |      |

|        |                               | fADC = 1 Msps - R2R<br>disabled with gain<br>compensation  | V <sub>DDANA</sub> = 3.0V V <sub>REF</sub><br>= 2.0V                |      | ±0.12    | ±0.4     |      |

|        |                               |                                                            | $V_{DDANA} = 3.0V, V_{REF}$<br>= $V_{DDANA}/2$                      |      | ±0.2     | ±0.65    |      |

| Offset | Offset Error                  | fADC = 1 Msps - R2R<br>disabled w/o offset<br>compensation | V <sub>DDANA</sub> = 3.0V V <sub>REF</sub><br>= V <sub>DDANA</sub>  |      | ±0.03    | ±9.9     | mV   |

|        |                               |                                                            | V <sub>DDANA</sub> = 3.0V, V <sub>REF</sub><br>= 2.0V               |      | ±0.03    | ±9.9     |      |

|        |                               |                                                            | V <sub>DDANA</sub> = 3.0V, 1V<br>Internal Ref                       |      | ±0.5     | ±5       |      |