Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 120MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                             |

| Number of I/O              | 51                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                        |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 256K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                       |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 64-VFQFN Exposed Pad                                                                |

| Supplier Device Package    | 64-VQFN (9x9)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame51j20a-mut          |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

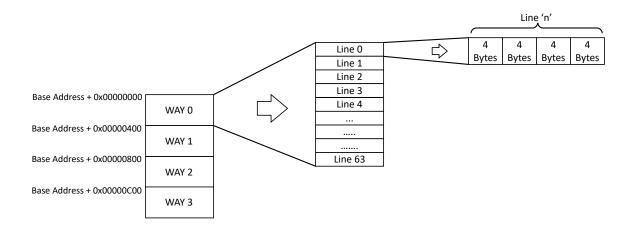

# **CMCC - Cortex M Cache Controller**

# 11.3 Block Diagram

Figure 11-1. CMCC Block Diagram

Figure 11-2. CMCC Organization

# 12.13.7 Debug Communication Channel x

| Name:     | DCC                  |

|-----------|----------------------|

| Offset:   | 0x10 + n*0x04 [n=01] |

| Reset:    | 0x0000000            |

| Property: | -                    |

| Bit    | 31          | 30  | 29  | 28    | 27             | 26  | 25  | 24  |

|--------|-------------|-----|-----|-------|----------------|-----|-----|-----|

|        | DATA[31:24] |     |     |       |                |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |

|        |             |     |     |       |                |     |     |     |

| Bit    | 23          | 22  | 21  | 20    | 19             | 18  | 17  | 16  |

|        |             |     |     | DATA[ | 23:16]         |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |

|        |             |     |     |       |                |     |     |     |

| Bit    | 15          | 14  | 13  | 12    | 11             | 10  | 9   | 8   |

|        |             |     |     | DATA  | [15:8]         |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |

|        |             |     |     |       |                |     |     |     |

| Bit    | 7           | 6   | 5   | 4     | 3              | 2   | 1   | 0   |

|        |             |     |     | DATA  | <b>\</b> [7:0] |     |     |     |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |

Bits 31:0 – DATA[31:0] Data Data register.

# **GCLK - Generic Clock Controller**

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | The Generator is stopped in Standby and the GCLK_IO pin state (one or zero) will be  |

|       | dependent on the setting in GENCTRL.OOV.                                             |

| 1     | The Generator is kept running and output to its dedicated GCLK_IO pin during Standby |

|       | mode.                                                                                |

# Bit 12 – DIVSEL Divide Selection

This bit determines how the division factor of the clock source of the Generator will be calculated from DIV. If the clock source should not be divided, DIVSEL must be 0 and the GENCTRLn.DIV value must be either 0 or 1.

| Value | Description                                                                                            |

|-------|--------------------------------------------------------------------------------------------------------|

| 0     | The Generator clock frequency equals the clock source frequency divided by                             |

|       | GENCTRLn.DIV.                                                                                          |

| 1     | The Generator clock frequency equals the clock source frequency divided by 2 <sup>^</sup> (N+1), where |

|       | N is the Division Factor Bits for the selected generator (refer to GENCTRLn.DIV).                      |

# Bit 11 – OE Output Enable

This bit is used to output the Generator clock output to the corresponding pin (GCLK\_IO), as long as GCLK\_IO is not defined as the Generator source in the GENCTRLn.SRC bit field.

| Value | Description                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | No Generator clock signal on pin GCLK_IO.                                                                                                          |

| 1     | The Generator clock signal is output on the corresponding GCLK_IO, unless GCLK_IO is selected as a generator source in the GENCTRLn.SRC bit field. |

# Bit 10 - OOV Output Off Value

This bit is used to control the clock output value on pin (GCLK\_IO) when the Generator is turned off or the OE bit is zero, as long as GCLK\_IO is not defined as the Generator source in the GENCTRLn.SRC bit field.

| V | /alue | Description                                                                       |

|---|-------|-----------------------------------------------------------------------------------|

| 0 | )     | The GCLK_IO will be LOW when generator is turned off or when the OE bit is zero.  |

| 1 |       | The GCLK_IO will be HIGH when generator is turned off or when the OE bit is zero. |

# Bit 9 – IDC Improve Duty Cycle

This bit is used to improve the duty cycle of the Generator output to 50/50 for odd division factors.

| Value | Description                                                                          |

|-------|--------------------------------------------------------------------------------------|

| 0     | Generator output clock duty cycle is not balanced to 50/50 for odd division factors. |

| 1     | Generator output clock duty cycle is 50/50.                                          |

# Bit 8 – GENEN Generator Enable

This bit is used to enable and disable the Generator.

| Value | Description            |

|-------|------------------------|

| 0     | Generator is disabled. |

| 1     | Generator is enabled.  |

## Bits 4:0 – SRC[4:0] Generator Clock Source Selection

These bits select the Generator clock source, as shown in this table.

# **RTC – Real-Time Counter**

| Value | Description                                                                 |  |

|-------|-----------------------------------------------------------------------------|--|

| 0     | Tamper DMA request is disabled. Reading TIMESTAMP has no effect on          |  |

|       | INTFLAG.TAMPER.                                                             |  |

| 1     | Tamper DMA request is enabled. Reading TIMESTAMP will clear INTFLAG.TAMPER. |  |

# Bit 6 – RTCOUT RTC Out Enable

| Value | Description                              |

|-------|------------------------------------------|

| 0     | The RTC active layer output is disabled. |

| 1     | The RTC active layer output is enabled.  |

# Bit 5 – DEBASYNC Debouncer Asynchronous Enable

| Value | Description                                         |

|-------|-----------------------------------------------------|

| 0     | The tamper input debouncers operate synchronously.  |

| 1     | The tamper input debouncers operate asynchronously. |

# Bit 4 – DEBMAJ Debouncer Majority Enable

| Value | Description                                                     |

|-------|-----------------------------------------------------------------|

| 0     | The tamper input debouncers match three equal values.           |

| 1     | The tamper input debouncers match majority two of three values. |

# Bit 1 – GP2EN General Purpose 2 Enable

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | COMP1 compare function enabled. GP2/GP3 disabled. |

| 1     | COMP1 compare function disabled. GP2/GP3 enabled. |

# **Bit 0 – GP0EN** General Purpose 0 Enable

| Value | Description                                   |

|-------|-----------------------------------------------|

| 0     | COMP0 compare function enabled. GP0 disabled. |

| 1     | COMP0 compare function disabled. GP0 enabled. |

|        | Name:<br>Offset:<br>Reset:<br>Property: | TIDM<br>0xA8 + n*0x0<br>0x00000000<br>- | 4 [n=03] |      |       |     |     |     |

|--------|-----------------------------------------|-----------------------------------------|----------|------|-------|-----|-----|-----|

| Bit    | 31                                      | 30                                      | 29       | 28   | 27    | 26  | 25  | 24  |

|        | ENIDn                                   |                                         |          |      |       |     |     |     |

| Access | R/W                                     |                                         |          |      |       |     |     |     |

| Reset  | 0                                       |                                         |          |      |       |     |     |     |

| Bit    | 23                                      | 22                                      | 21       | 20   | 19    | 18  | 17  | 16  |

|        |                                         |                                         |          |      |       |     |     |     |

| Access |                                         |                                         |          |      |       |     |     |     |

| Reset  |                                         |                                         |          |      |       |     |     |     |

| Bit    | 15                                      | 14                                      | 13       | 12   | 11    | 10  | 9   | 8   |

|        |                                         |                                         |          | TID[ | 15:8] |     |     |     |

| Access | R/W                                     | R/W                                     | R/W      | R/W  | R/W   | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                       | 0        | 0    | 0     | 0   | 0   | 0   |

| Bit    | 7                                       | 6                                       | 5        | 4    | 3     | 2   | 1   | 0   |

|        |                                         |                                         |          | TID  | [7:0] |     |     |     |

| Access | R/W                                     | R/W                                     | R/W      | R/W  | R/W   | R/W | R/W | R/W |

| Reset  | 0                                       | 0                                       | 0        | 0    | 0     | 0   | 0   | 0   |

# 24.9.24 GMAC Type ID Match n Register

# Bit 31 – ENIDn Enable Copying of TID Matched Frames

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | TID n is not part of the comparison match.   |

| 1     | TID n is processed for the comparison match. |

# Bits 15:0 - TID[15:0] Type ID Match n

For use in comparisons with received frames type ID/length frames.

| Name:<br>Offset:<br>Reset:<br>Property: |     | WOL<br>0x0B8<br>0x00000000<br>- |     |      |      |     |     |     |

|-----------------------------------------|-----|---------------------------------|-----|------|------|-----|-----|-----|

| Bit                                     | 31  | 30                              | 29  | 28   | 27   | 26  | 25  | 24  |

|                                         |     |                                 |     |      |      |     |     |     |

| Access                                  |     |                                 |     |      |      |     |     |     |

| Reset                                   |     |                                 |     |      |      |     |     |     |

| Bit                                     | 23  | 22                              | 21  | 20   | 19   | 18  | 17  | 16  |

|                                         |     |                                 |     |      | MTI  | SA1 | ARP | MAG |

| Access                                  |     | -                               |     |      | R/W  | R/W | R/W | R/W |

| Reset                                   |     |                                 |     |      | 0    | 0   | 0   | 0   |

| Bit                                     | 15  | 14                              | 13  | 12   | 11   | 10  | 9   | 8   |

|                                         |     |                                 |     | IP[1 | 5:8] |     |     |     |

| Access                                  | R/W | R/W                             | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Reset                                   | 0   | 0                               | 0   | 0    | 0    | 0   | 0   | 0   |

|                                         |     |                                 |     |      |      |     |     |     |

| Bit                                     | 7   | 6                               | 5   | 4    | 3    | 2   | 1   | 0   |

|                                         |     |                                 |     |      | 7:0] |     |     |     |

| Access                                  |     | R/W                             | R/W | R/W  | R/W  | R/W | R/W | R/W |

| Reset                                   | 0   | 0                               | 0   | 0    | 0    | 0   | 0   | 0   |

# 24.9.25 GMAC Wake on LAN Register

# Bit 19 - MTI Multicast Hash Event Enable

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | Wake on LAN multicast hash Event disabled |

| 1     | Wake on LAN multicast hash Event enabled  |

# Bit 18 – SA1 Specific Address Register 1 Event Enable

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | Wake on Specific Address Register 1 Event disabled |

| 1     | Wake on Specific Address Register 1 Event enabled  |

# Bit 17 - ARP ARP Request Event Enable

| Value | Description                            |

|-------|----------------------------------------|

| 0     | Wake on LAN ARP request Event disabled |

| 1     | Wake on LAN ARP request Event enabled  |

Bit 16 – MAG Magic Packet Event Enable

# **PAC - Peripheral Access Controller**

# 27.7.10 Peripheral Write Protection Status A

| Name:     | STATUSA              |

|-----------|----------------------|

| Offset:   | 0x34                 |

| Reset:    | 0x00010000           |

| Property: | PAC Write-Protection |

Writing to this register has no effect.

Reading STATUS register returns peripheral write protection status:

|        | Value | Descr  | iption                             |              |       |      |    |     |  |  |

|--------|-------|--------|------------------------------------|--------------|-------|------|----|-----|--|--|

|        | 0     | Periph | Peripheral is not write protected. |              |       |      |    |     |  |  |

|        | 1     | Periph | Peripheral is write protected.     |              |       |      |    |     |  |  |

| Bit    | 31    | 30     | 29                                 | 28           | 27    | 26   | 25 | 24  |  |  |

| DIL    | 51    | 50     | 29                                 | 20           | 21    | 20   | 23 | 24  |  |  |

| Access |       |        |                                    |              |       |      |    |     |  |  |

| Reset  |       |        |                                    |              |       |      |    |     |  |  |

| Bit    | 23    | 22     | 21                                 | 20           | 19    | 18   | 17 | 16  |  |  |

|        |       |        |                                    |              |       |      |    |     |  |  |

| Access |       |        |                                    |              |       |      |    |     |  |  |

| Reset  |       |        |                                    |              |       |      |    |     |  |  |

| Bit    | 15    | 14     | 13                                 | 12           | 11    | 10   | 9  | 8   |  |  |

|        | TC1   | TC0    | SERCOM1                            | SERCOM0      | FREQM | EIC  |    | WDT |  |  |

| Access | R     | R      | R                                  | R            | R     | R    |    | R   |  |  |

| Reset  | 0     | 0      | 0                                  | 0            | 0     | 0    |    | 0   |  |  |

| Bit    | 7     | 6      | 5                                  | 4            | 3     | 2    | 1  | 0   |  |  |

| ы      | GCLK  | SUPC   | osc32kctrl                         | 4<br>OSCCTRL | RSTC  | MCLK | PM | PAC |  |  |

| •      |       |        |                                    |              |       |      |    |     |  |  |

| Access | R     | R      | R                                  | R            | R     | R    | R  | R   |  |  |

| Reset  | 0     | 0      | 0                                  | 0            | 0     | 0    | 0  | 0   |  |  |

| Value | Description                |

|-------|----------------------------|

| 0     | TC1 is not write protected |

| 1     | TC1 is write protected     |

# Bit 14 – TC0 TC0 APB Protect Enable

| Value | Description                |

|-------|----------------------------|

| 0     | TC0 is not write protected |

| 1     | TC0 is write protected     |

# Bit 13 – SERCOM1 SERCOM1 APB Protect Enable

© 2018 Microchip Technology Inc.

# SERCOM I2C – Inter-Integrated Circuit

# 36.8.10 Address

Name:ADDROffset:0x24Reset:0x0000000Property:PAC Write-Protection, Enable-Protected

| Bit    | 31       | 30  | 29  | 28            | 27  | 26  | 25           | 24     |

|--------|----------|-----|-----|---------------|-----|-----|--------------|--------|

|        |          |     |     |               |     |     | ADDRMASK[9:7 | ]      |

| Access |          |     |     |               |     | R/W | R/W          | R/W    |

| Reset  |          |     |     |               |     | 0   | 0            | 0      |

|        |          |     |     |               |     |     |              |        |

| Bit    | 23       | 22  | 21  | 20            | 19  | 18  | 17           | 16     |

|        |          |     |     | ADDRMASK[6:0] | ]   |     |              |        |

| Access | R/W      | R/W | R/W | R/W           | R/W | R/W | R/W          |        |

| Reset  | 0        | 0   | 0   | 0             | 0   | 0   | 0            |        |

|        |          |     |     |               |     |     |              |        |

| Bit    | 15       | 14  | 13  | 12            | 11  | 10  | 9            | 8      |

|        | TENBITEN |     |     |               |     |     | ADDR[9:7]    |        |

| Access | R/W      |     |     |               |     | R/W | R/W          | R/W    |

| Reset  | 0        |     |     |               |     | 0   | 0            | 0      |

|        |          |     |     |               |     |     |              |        |

| Bit    | 7        | 6   | 5   | 4             | 3   | 2   | 1            | 0      |

|        |          |     |     | ADDR[6:0]     |     |     |              | GENCEN |

| Access | R/W      | R/W | R/W | R/W           | R/W | R/W | R/W          | R/W    |

| Reset  | 0        | 0   | 0   | 0             | 0   | 0   | 0            | 0      |

# Bits 26:17 – ADDRMASK[9:0] Address Mask

These bits act as a second address match register, an address mask register or the lower limit of an address range, depending on the CTRLB.AMODE setting.

# Bit 15 – TENBITEN Ten Bit Addressing Enable

| Value | Description                          |

|-------|--------------------------------------|

| 0     | 10-bit address recognition disabled. |

| 1     | 10-bit address recognition enabled.  |

## Bits 10:1 - ADDR[9:0] Address

These bits contain the I<sup>2</sup>C slave address used by the slave address match logic to determine if a master has addressed the slave.

When using 7-bit addressing, the slave address is represented by ADDR[6:0].

When using 10-bit addressing (ADDR.TENBITEN=1), the slave address is represented by ADDR[9:0]

When the address match logic detects a match, INTFLAG.AMATCH is set and STATUS.DIR is updated to indicate whether it is a read or a write transaction.

## Bit 0 – GENCEN General Call Address Enable

A general call address is an address consisting of all-zeroes, including the direction bit (master write).

© 2018 Microchip Technology Inc.

**QSPI - Quad Serial Peripheral Interface**

| Value | Description                      |

|-------|----------------------------------|

| 0     | The ERROR interrupt is disabled. |

| 1     | The ERROR interrupt is enabled.  |

**Bit 2 – TXC** Transmission Complete Interrupt Disable Writing a '0' to this bit has no effect.

Writing a '1' will clear the corresponding interrupt request.

| Value | Description                    |

|-------|--------------------------------|

| 0     | The TXC interrupt is disabled. |

| 1     | The TXC interrupt is enabled.  |

**Bit 1 – DRE** Transmit Data Register Empty Interrupt Disable Writing a '0' to this bit has no effect.

Writing a '1' will clear the corresponding interrupt request.

| Value | Description                    |

|-------|--------------------------------|

| 0     | The DRE interrupt is disabled. |

| 1     | The DRE interrupt is enabled.  |

**Bit 0 – RXC** Receive Data Register Full Interrupt Disable Writing a '0' to this bit has no effect.

Writing a '1' will clear the corresponding interrupt request.

| Value | Description                    |

|-------|--------------------------------|

| 0     | The RXC interrupt is disabled. |

| 1     | The RXC interrupt is enabled.  |

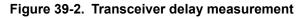

- The sum of the measured delay from CAN\_TX to CAN\_RX and the configured transceiver delay compensation offset FBTP.TDCO has to be less than 6 bit times in the data phase.

- The sum of the measured delay from CAN\_TX to CAN\_RX and the configured transceiver delay compensation offset FBTP.TDCO has to be less or equal to 127 mtq. In case this sum exceeds 127 mtq, the maximum value of 127 mtq is used for transceiver delay compensation.

- The data phase ends at the sample point of the CRC delimiter, that stops checking of receive bits at the SSPs.

Transmitter Delay Compensation Measurement

If transmitter delay compensation is enabled by programming DBTP.TDC = '1', the measurement is started within each transmitted CAN FD frame at the falling edge of bit FDF to bit res. The measurement is stopped when this edge is seen at the receive input CAN\_TX of the transmitter. The resolution of this measurement is one mtq.

To avoid that a dominant glitch inside the received FDF bit ends the delay compensation measurement before the falling edge of the received res bit, resulting in a too early SSP position, the use of a transmitter delay compensation filter window can be enabled by programming TDCR.TDCF. This defines a minimum value for the SSP position. Dominant edges of CAN\_RX, that would result in an earlier SSP position are ignored for transmitter delay measurement. The measurement is stopped when the SSP position is at least TDCR.TDCF AND CAN\_RX is low.

## 39.6.2.5 Restricted Operation Mode

In Restricted Operation Mode the node is able to receive data and remote frames and to give acknowledge to valid frames, but it does not send data frames, remote frames, active error frames, or overload frames. In case of an error condition or overload condition, it does not send dominant bits, instead it waits for the occurrence of bus idle condition to resynchronize itself to the CAN communication. The error counters (ECR.REC, ECR.TEC) are frozen while Error Logging (ECR.CEL) is still incremented. The CPU can set the CAN into Restricted Operation mode by setting bit CCCR.ASM. The bit can only be set by the CPU when both CCCR.CCE and CCCR.INIT are set to '1'. The bit can be reset by the CPU at any time.

Restricted Operation Mode is automatically entered when the Tx Handler was not able to read data from the Message RAM in time. To leave Restricted Operation Mode, the CPU has to reset CCCR.ASM.

The Restricted Operation Mode can be used in applications that adapt themselves to different CAN bit rates. In this case the application tests different bit rates and leaves the Restricted Operation Mode after it has received a valid frame.

© 2018 Microchip Technology Inc.

**CAN - Control Area Network**

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | No Message RAM Watchdog event occurred.          |

| 1     | Message RAM Watchdog event due to missing READY. |

# Bit 25 – BO Bus\_Off Status

| Value | Description               |

|-------|---------------------------|

| 0     | Bus_Off status unchanged. |

| 1     | Bus_Off status changed.   |

# Bit 24 – EW Error Warning Status

| Value | Description                     |

|-------|---------------------------------|

| 0     | Error_Warning status unchanged. |

| 1     | Error_Warning status changed.   |

# Bit 23 – EP Error Passive

| Value | Description                     |  |  |

|-------|---------------------------------|--|--|

| 0     | Error_Passive status unchanged. |  |  |

| 1     | Error_Passive status changed.   |  |  |

# Bit 22 – ELO Error Logging Overflow

| Value | Description                                     |

|-------|-------------------------------------------------|

| 0     | CAN Error Logging Counter did not overflow.     |

| 1     | Overflow of CAN Error Logging Counter occurred. |

# Bit 21 – BEU Bit Error Uncorrected

Message RAM bit error detected, uncorrected. Generated by an optional external parity / ECC logic attached to the Message RAM. An uncorrected Message RAM bit sets CCCR.INIT to 1. This is done to avoid transmission of corrupted data.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | Not bit error detected when reading from Message RAM. |

| 1     | Bit error detected, uncorrected (e.g. parity logic).  |

# Bit 20 - BEC Bit Error Corrected

Message RAM bit error detected and corrected. Generated by an optional external parity / ECC logic attached to the Message RAM.

| Value | e Description                                         |

|-------|-------------------------------------------------------|

| 0     | Not bit error detected when reading from Message RAM. |

| 1     | Bit error detected and corrected (e.g. ECC).          |

# Bit 19 – DRX Message stored to Dedicated Rx Buffer

The flag is set whenever a received message has been stored into a dedicated Rx Buffer.

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | No Rx Buffer updated.                                  |

| 1     | At least one received message stored into a Rx Buffer. |

SD/MMC Host Controller ...

| Value | Description |

|-------|-------------|

| 0     | Work        |

| 1     | Reset       |

## 43.3.4.5.6 Constraints

The parameter placements that are not allowed are are as follows.

If nu1XBase equals zero, no checks are made on nu1XBase (fixed) and u2XLength (unused).

The following conditions must be avoided to ensure that the service works correctly:

- nu1XBase or nu1RBase are not aligned on 32-bit boundaries

- u2XLength or u2RLength is either: <4, >0xffc or not a 32-bit length or u2XLength >u2RLength

- {nu1XBase, u2XLength} or {nu1RBase, u2RLength} do not entirely lie in Crypto RAM

- {nu1XBase, u2XLength} overlaps {nu1RBase,u2RLength}

## 43.3.4.5.7 Status Returned Values

#### Table 43-14. FastCopy Service Return Codes

| Returned status | Importance | Meaning                      |  |  |

|-----------------|------------|------------------------------|--|--|

| PUKCL_OK        | _          | Service functioned correctly |  |  |

#### 43.3.4.6 Conditional Copy/Clear

#### 43.3.4.6.1 Purpose

This service conditionally performs a copy from a memory area to another or a memory area clear.

#### 43.3.4.6.2 How to Use the Service

## 43.3.4.6.3 Description

This service copies a number X into another number R, padding with zero on the MSB side up to the length specified for R. This copy operation is performed under the conditions specified in the options.

If the condition is verified, R = X.

The copy or clear action is made under condition.

The four possible options for the condition are described in the following table. Two of the conditions check the Specific.CarryIn bit (see 43.3.3.2 Accessing Different Library Services).

The processing is done as follows:

- If the condition is not verified, nothing is processed.

- If the condition is verified the copy or clear follows the rules:

- If the lengths of R and X are equal, a complete fast copy is processed

- If the length of R is strictly greater than the length of X, X is first copied in the Low Significant Bytes side of R, and R is padded with zeros on the Most Significant Bytes side.

- If the pointer on the X area equals zero, R is filled with zeros.

The service name for this operation is CondCopy.

#### 43.3.6.8.6 Constraints

. . .

No overlapping between either input and output are allowed. The following conditions must be avoided to ensure that the service works correctly:

- nu1ModBase, nu1CnsBase, nu1PointABase, nu1Workspace are not aligned on 32-bit boundaries

- {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1PointABase, 3\*u2ModLength+ 12}, {nu1Workspace, <WorkspaceLength>} are not in Crypto RAM

- u2ModLength is either: < 12, > 0xffc or not a 32-bit length

- All overlapping between {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength +8}, {nu1PointABase, 3\*u2ModLength + 12}, and {nu1Workspace, 2\*u2ModLength + 16}

## 43.3.6.8.7 Status Returned Values

## Table 43-80. ZpEccConvAffineToProjective Service Return Codes

| Returned Status | Importance | Meaning                                 |

|-----------------|------------|-----------------------------------------|

| PUKCL_OK        | -          | The computation passed without problem. |

#### 43.3.6.9 Randomize a Coordinate

#### 43.3.6.9.1 Purpose

This service is used to convert the projective representation of a point to another projective representation.

#### 43.3.6.9.2 How to Use the Service

## 43.3.6.9.3 Description

The operation performed is:

$Projective(X_1, Y_1, Z_1) \rightarrow Projective(X_2, Y_2, Z_2)$

In this computation, the following parameters need to be provided:

- The input point is filled in projective coordinates (X,Y,Z) (pointed by {nu1PointBase,3\*u2ModLength + 12}). This Point must not be the point at infinity.

- Cns the Fast Modular Constant filled (pointed by {nu1CnsBase,u2ModLength +8})

- P the modulus filled (pointed by {nu1ModBase,u2ModLength +4})

- The workspace not initialized (pointed by {nu1WorkSpace, 3\*u2ModLength +28}

- The random number (pointed by {nu1RandomBase, u2ModLength +4}).

The result is the point nu1PointBase with its (X,Y,Z) coordinates randomized.

The service for this operation is ZpEcRandomiseCoordinate.

# Public Key Cryptography Controller (PUKCC)

else // Manage the error

#### 43.3.7.5.6 Constraints

No overlapping between either input and output are allowed. The following conditions must be avoided to ensure the service works correctly:

- nu1ModBase, nu1CnsBase, nu1PointABase, nu1Workspace are not aligned on 32-bit boundaries

- {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8},{nu1PointABase, 3\*u2ModLength + 12}, {nu1Workspace, <WorkspaceLength>} are not in Crypto RAM

- u2ModLength is either: < 12, > 0xffc or not a 32-bit length

- All overlapping between {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1PointABase, 3\*u2ModLength + 12} and {nu1Workspace, 4\*u2ModLength + 48}

## 43.3.7.5.7 Status Returned Values

# Table 43-101. GF2NEcConvProjToAffine Service Return Codes

| Returned Status         | Importance | Meaning                                                                                   |

|-------------------------|------------|-------------------------------------------------------------------------------------------|

| PUKCL_OK                | -          | The computation passed without problem.                                                   |

| PUKCL_POINT_AT_INFINITY | Warning    | The input point has its Z equal to zero, so it is a representation of the infinite point. |

#### 43.3.7.6 Affine to Projective Coordinates Conversion

#### 43.3.7.6.1 Purpose

This service is used to perform a point coordinates conversion from an affine point representation to projective.

#### 43.3.7.6.2 How to Use the Service

## 43.3.7.6.3 Description

The operation performed is:

```

affine(Xa, Ya) \rightarrow projective(Xp, Yp, Zp)

```

In this computation, the following parameters need to be provided:

- A the input point is filled in affine coordinates for X and Y, and setting Z to 1 (pointed by {nu1PointABase,3\*u2ModLength + 4}).

- Cns the Fast Modular Constant filled (pointed by {nu1CnsBase,u2ModLength + 8})

- P the modulus filled (pointed by {nu1ModBase,u2ModLength + 4})

- The workspace not initialized (pointed by {nu1WorkSpace, 2\*u2ModLength +16} The result is the point A with its (X,Y,Z) projective coordinates.

The service name for this operation is GF2NEcConvAffineToProjective.

**Important:** Before using this service, ensure that the constant Cns has been calculated with the setup of the Fast Modular Reductions service.

# ADC – Analog-to-Digital Converter

# 45.8.19 DSEQDATA

| Name:     | DSEQDATA             |  |  |  |  |

|-----------|----------------------|--|--|--|--|

| Offset:   | 0x34                 |  |  |  |  |

| Reset:    | 0x0000000            |  |  |  |  |

| Property: | PAC Write-Protection |  |  |  |  |

| Bit    | 31 | 30          | 29 | 28   | 27      | 26 | 25 | 24 |  |

|--------|----|-------------|----|------|---------|----|----|----|--|

|        |    | DATA[31:24] |    |      |         |    |    |    |  |

| Access | W  | W           | W  | W    | W       | W  | W  | W  |  |

| Reset  | 0  | 0           | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |    |             |    |      |         |    |    |    |  |

| Bit    | 23 | 22          | 21 | 20   | 19      | 18 | 17 | 16 |  |

|        |    |             |    | DATA | [23:16] |    |    |    |  |

| Access | W  | W           | W  | W    | W       | W  | W  | W  |  |

| Reset  | 0  | 0           | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |    |             |    |      |         |    |    |    |  |

| Bit    | 15 | 14          | 13 | 12   | 11      | 10 | 9  | 8  |  |

|        |    | DATA[15:8]  |    |      |         |    |    |    |  |

| Access | W  | W           | W  | W    | W       | W  | W  | W  |  |

| Reset  | 0  | 0           | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |    |             |    |      |         |    |    |    |  |

| Bit    | 7  | 6           | 5  | 4    | 3       | 2  | 1  | 0  |  |

|        |    |             |    | DATA | 4[7:0]  |    |    |    |  |

| Access | W  | W           | W  | W    | W       | W  | W  | W  |  |

| Reset  | 0  | 0           | 0  | 0    | 0       | 0  | 0  | 0  |  |

|        |    |             |    |      |         |    |    |    |  |

# Bits 31:0 - DATA[31:0] DMA Sequential Data

This register stores data written by the DMA and re-directed to the first enabled ADC registers in the DSEQSTAT register.

# 46.5.1 I/O Lines

Using the AC's I/O lines requires the I/O pins to be configured. Refer to *PORT - I/O Pin Controller* for details.

# Table 46-1. I/O Lines

| Instance | Signal | I/O Line | Peripheral Function |

|----------|--------|----------|---------------------|

| AC0      | AIN0   | PAxx     | A                   |

| AC0      | AIN1   | PAxx     | A                   |

| AC0      | AIN2   | PAxx     | A                   |

| AC0      | AIN3   | PAxx     | A                   |

| AC0      | CMP0   | PAxx     | A                   |

| AC0      | CMP1   | PAxx     | A                   |

# **Related Links**

32. PORT - I/O Pin Controller

# 46.5.2 Power Management

The AC will continue to operate in any sleep mode where the selected source clock is running. The AC's interrupts can be used to wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

## 46.5.3 Clocks

The AC bus clock (CLK\_AC\_APB) can be enabled and disabled in the Main Clock module, MCLK (see *MCLK - Main Clock*, and the default state of CLK\_AC\_APB can be found in *Peripheral Clock Masking*.

A generic clock (GCLK\_AC) is required to clock the AC. This clock must be configured and enabled in the generic clock controller before using the AC. Refer to the Generic Clock Controller chapter for details.

This generic clock is asynchronous to the bus clock (CLK\_AC\_APB). Due to this asynchronicity, writes to certain registers will require synchronization between the clock domains. Refer to Synchronization for further details.

## **Related Links**

15.6.2.6 Peripheral Clock Masking15. MCLK – Main Clock

## 46.5.4 DMA

Not applicable.

# 46.5.5 Interrupts

The interrupt request lines are connected to the interrupt controller. Using the AC interrupts requires the interrupt controller to be configured first. Refer to *Nested Vector Interrupt Controller* for details.

## **Related Links**

10.2 Nested Vector Interrupt Controller

# 46.5.6 Events

The events are connected to the Event System. Refer to *EVSYS – Event System* for details on how to configure the Event System.

# DAC – Digital-to-Analog Converter

| 47.8.8          | Synchronization Busy                    |                                     |          |          |       |       |        |       |

|-----------------|-----------------------------------------|-------------------------------------|----------|----------|-------|-------|--------|-------|

|                 | Name:<br>Offset:<br>Reset:<br>Property: | SYNCBUSY<br>0x08<br>0x00000000<br>- |          |          |       |       |        |       |

| Bit             | t 31                                    | 30                                  | 29       | 28       | 27    | 26    | 25     | 24    |

|                 |                                         |                                     |          |          |       |       |        |       |

| Access          |                                         |                                     |          |          |       |       |        |       |

| Reset           | t                                       |                                     |          |          |       |       |        |       |

| Bit             | t23                                     | 22                                  | 21       | 20       | 19    | 18    | 17     | 16    |

|                 |                                         |                                     |          |          |       |       |        |       |

| Access<br>Reset |                                         |                                     |          |          |       |       |        |       |

| Bi              | t 15                                    | 14                                  | 13       | 12       | 11    | 10    | 9      | 8     |

| Access<br>Reset |                                         |                                     |          |          |       |       |        |       |

| Bit             | t 7                                     | 6                                   | 5        | 4        | 3     | 2     | 1      | 0     |

|                 |                                         |                                     | DATABUF1 | DATABUF0 | DATA1 | DATA0 | ENABLE | SWRST |

| Access          | ;                                       |                                     | R        | R        | R     | R     | R      | R     |

| Reset           | t                                       |                                     | 0        | 0        | 0     | 0     | 0      | 0     |

# Bit 5 - DATABUF1 Data Buffer DAC1

This bit is set when DATABUF1 register is written.

This bit is cleared when DATABUF1 synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

# Bit 4 – DATABUF0 Data Buffer DAC0

This bit is set when DATABUF0 register is written.

This bit is cleared when DATABUF0 synchronization is completed.

| Value | Description                     |

|-------|---------------------------------|

| 0     | No ongoing synchronized access. |

| 1     | Synchronized access is ongoing. |

# Bit 3 – DATA1 Data DAC1

This bit is set when DATA1 register is written.

This bit is cleared when DATA1 synchronization is completed.

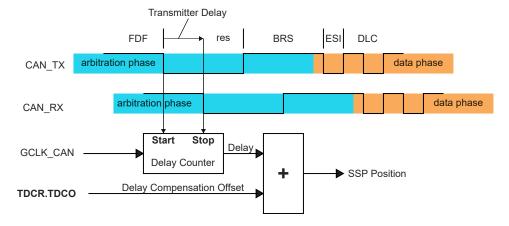

# TCC – Timer/Counter for Control Applications

# Figure 49-39. DMA Triggers in DSBOTH Operation Mode and Circular Buffer Enabled

# 49.6.5.2 Interrupts

The TCC has the following interrupt sources:

- Overflow/Underflow (OVF)

- Retrigger (TRG)

- Count (CNT) refer also to description of EVCTRL.CNTSEL.

- Capture Overflow Error (ERR)

- Debug Fault State (DFS)

- Recoverable Faults (FAULTn)

- Non-recoverable Faults (FAULTx)

- Compare Match or Capture Channels (MCx)

These interrupts are asynchronous wake-up sources. See Sleep Mode Entry and Exit Table in PM/Sleep Mode Controller section for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by writing a '1' to the corresponding bit in the Interrupt Enable Set (INTENSET) register, and disabled by writing a '1' to the corresponding bit in the Interrupt Enable Clear (INTENCLR) register. An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the TCC is reset. See 49.8.12 INTFLAG for details on how to clear interrupt flags. The TCC has one common interrupt request line for all the interrupt sources. The user must read the INTFLAG register to determine which interrupt condition is present.

Note: Interrupts must be globally enabled for interrupt requests to be generated. Refer to *Nested Vector Interrupt Controller* for details.

# **Related Links**

10.2 Nested Vector Interrupt Controller

# 49.6.5.3 Events

The TCC can generate the following output events:

• Overflow/Underflow (OVF)

Electrical Characteristics at 85°C

# 54.13.2 SERCOM in SPI Mode Timing

Table 54-52. SPI Timing Characteristics and Requirements<sup>(1)</sup>

| Symbol                | Parameter                    | Conditions        |                               | Min.                                                             | Тур.                   | Max. | Units |

|-----------------------|------------------------------|-------------------|-------------------------------|------------------------------------------------------------------|------------------------|------|-------|

| t <sub>SCK</sub> (10) | SCK period                   | Master            | Reception                     | 2*(t <sub>MIS</sub><br>+t <sub>SLAVE_OUT</sub> ) <sup>(3)</sup>  | -                      | -    | ns    |

|                       |                              | Master            | Transmission                  | $2^{*}(t_{MOV}+t_{SLAVE_IN})$                                    | -                      | -    |       |

| t <sub>SCKW</sub>     | SCK high/low width           | Master            | Master - 0.5*t <sub>SCF</sub> |                                                                  | 0.5*t <sub>SCK</sub>   | -    |       |

| t <sub>SCKR</sub>     | SCK rise time <sup>(2)</sup> | Master            |                               | -                                                                | 0.25*t <sub>SCK</sub>  | -    |       |

| t <sub>SCKF</sub>     | SCK fall time <sup>(2)</sup> | Master            |                               | -                                                                | 0.25*t <sub>SCK</sub>  | -    |       |

| t <sub>MIS</sub>      | MISO setup to SCK            | Master, VDD>2.70V |                               | 18                                                               | -                      | -    |       |

|                       |                              | Master,           | VDD>1.71V                     | 19                                                               | -                      | -    |       |

| t <sub>MIH</sub>      | MISO hold after<br>SCK       | Master,           | VDD>2.70V                     | 0                                                                | -                      | -    |       |

|                       |                              | Master,           | VDD>1.71V                     | 0                                                                | -                      | -    |       |

| t <sub>MOV</sub>      | MOSI output valid<br>SCK     | Master,           | VDD>2.70V                     | -                                                                | -                      | 9    |       |

|                       |                              | Master,           | VDD>1.71V                     | -                                                                | -                      | 14   |       |

| t <sub>MOH</sub>      | MOSI hold after<br>SCK       | Master, VDD>2.70V |                               | -                                                                | -                      | -3   |       |

|                       |                              | Master,           | VDD>1.71V                     | -                                                                | -                      | -3   |       |

| t <sub>SSCK</sub>     | Slave SCK Period             | Slave             | Reception                     | 2*(t <sub>SIS</sub><br>+t <sub>MASTER_OUT</sub> ) <sup>(5)</sup> | -                      | -    | ns    |

|                       |                              | Slave             | Transmission                  | 2*(t <sub>SOV</sub><br>+t <sub>MASTER_IN</sub> ) <sup>(6)</sup>  | -                      | -    |       |

| t <sub>ssckw</sub>    | SCK high/low width           | Slave             |                               | -                                                                | 0.5*t <sub>SSCK</sub>  | -    |       |

| t <sub>SSCKR</sub>    | SCK rise time <sup>(2)</sup> | Slave             |                               | -                                                                | 0.25*t <sub>SSCK</sub> | -    |       |

| t <sub>SSCKF</sub>    | SCK fall time <sup>(2)</sup> | Slave             |                               | -                                                                | 0.25*t <sub>SSCK</sub> | -    |       |

| t <sub>SIS</sub>      | MOSI setup to SCK            | Slave, VDD>2.70V  |                               | 7.5                                                              | -                      | -    |       |

|                       |                              | Slave, VDD>1.71V  |                               | 8.5                                                              | -                      | -    |       |

| t <sub>SIH</sub>      | MOSI hold after<br>SCK       | Slave, VDD>2.70V  |                               | 4                                                                | -                      | -    |       |

|                       |                              | Slave, VDD>1.71V  |                               | 4                                                                | -                      | -    |       |

| t <sub>SSS</sub>      | SS setup to SCK              | Slave             | PRELOADEN=1                   | $t_{SOSS}$ + $t_{EXT_MIS}$ +2* $t_{APBC}$ <sup>(8)(9)</sup>      | -                      | -    |       |

|                       |                              |                   | PRELOADEN=0                   | $t_{\text{SOSS}}$ + $t_{\text{EXT}_{MIS}}^{(8)}$                 | -                      | -    |       |

| t <sub>SSH</sub>      | SS hold after SCK            | Slave             |                               | 0.5*t <sub>SSCK</sub>                                            | -                      | -    |       |

| t <sub>SOV</sub>      | MISO output valid<br>SCK     | Slave, VDD>2.70V  |                               | 15                                                               | -                      | -    |       |

|                       |                              | Slave, VDD>1.71V  |                               | 24                                                               | -                      | -    |       |

© 2018 Microchip Technology Inc.