#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                              |

|----------------------------|-------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                    |

| Core Size                  | 32-Bit Single-Core                                                                  |

| Speed                      | 120MHz                                                                              |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM                             |

| Number of I/O              | 81                                                                                  |

| Program Memory Size        | 512KB (512K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                               |

| EEPROM Size                | -                                                                                   |

| RAM Size                   | 192К х 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                       |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                               |

| Oscillator Type            | Internal                                                                            |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                       |

| Package / Case             | 100-TQFP                                                                            |

| Supplier Device Package    | 100-TQFP (14x14)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame51n19a-au           |

|                            |                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|             | 53.7.  | Register Summary                      | 2006 |

|-------------|--------|---------------------------------------|------|

|             | 53.8.  | Register Description                  |      |

| 54          | Elect  | rical Characteristics at 85°C         |      |

|             | 54 1   | Disclaimer                            | 2034 |

|             |        | Absolute Maximum Ratings              |      |

|             |        | General Operating Ratings             |      |

|             |        | Injection Current                     |      |

|             | 54.5.  | Supply Characteristics                | 2036 |

|             | 54.6.  | Maximum Clock Frequencies             |      |

|             | 54.7.  | Power Consumption                     |      |

|             | 54.8.  | Wake-Up Time                          | 2042 |

|             | 54.9.  | I/O Pin Characteristics               | 2043 |

|             | 54.10  | Analog Characteristics                |      |

|             | 54.11. | NVM Characteristics                   | 2058 |

|             | 54.12  | Oscillators Characteristics           | 2059 |

|             | 54.13  | . Timing Characteristics              | 2065 |

|             | 54.14  | USB Characteristics                   |      |

| 55          | Pack   | aging Information                     |      |

|             | 55.1.  | Package Marking Information           |      |

|             |        | Thermal Considerations                |      |

|             |        | Package Drawings                      |      |

|             |        | Soldering Profile                     |      |

| 56          | Sche   | matic Checklist                       |      |

|             | 56 1   | Introduction                          | 2100 |

|             |        | Power Supply                          |      |

|             |        | External Analog Reference Connections |      |

|             |        | External Reset Circuit                |      |

|             |        | Unused or Unconnected Pins            |      |

|             | 56.6.  | Clocks and Crystal Oscillators        | 2106 |

|             | 56.7.  | Programming and Debug Ports           | 2109 |

|             | 56.8.  | QSPI Interface                        |      |

|             | 56.9.  | USB Interface                         |      |

|             | 56.10  | SDHC Interface                        |      |

| 57          | Con    | ventions                              | 2116 |

|             | 57.1.  | Numerical Notation                    |      |

|             |        | Memory Size and Type                  |      |

|             |        | Frequency and Time                    |      |

|             |        | Registers and Bits                    |      |

|             |        | -                                     |      |

| 58          | Acro   | nyms and Abbreviations                | 2118 |

| 59          | Revi   | sion History                          | 2121 |

| <b>T</b> 1- |        | ochip Web Site                        | 2122 |

**GCLK - Generic Clock Controller**

| Offset | Name      | Bit Pos. |         |      |  |     |                |  |

|--------|-----------|----------|---------|------|--|-----|----------------|--|

|        |           | 15:8     |         |      |  |     |                |  |

|        |           | 23:16    |         |      |  |     |                |  |

|        |           | 31:24    |         |      |  |     |                |  |

|        |           | 7:0      | WRTLOCK | CHEN |  | GEN | <b>I</b> [3:0] |  |

| 0.0100 |           | 15:8     |         |      |  |     |                |  |

| 0x0128 | PCHCTRL42 | 23:16    |         |      |  |     |                |  |

|        |           | 31:24    |         |      |  |     |                |  |

|        |           | 7:0      | WRTLOCK | CHEN |  | GEN | <b>I</b> [3:0] |  |

| 0.0400 |           | 15:8     |         |      |  |     |                |  |

| 0x012C | PCHCTRL43 | 23:16    |         |      |  |     |                |  |

|        |           | 31:24    |         |      |  |     |                |  |

|        | PCHCTRL44 | 7:0      | WRTLOCK | CHEN |  | GEN | <b>I</b> [3:0] |  |

| 0.0100 |           | 15:8     |         |      |  |     |                |  |

| 0x0130 |           | 23:16    |         |      |  |     |                |  |

|        |           | 31:24    |         |      |  |     |                |  |

|        |           | 7:0      | WRTLOCK | CHEN |  | GEN | <b>I</b> [3:0] |  |

| 0x0134 | PCHCTRL45 | 15:8     |         |      |  |     |                |  |

| 0x0134 | PCHCTRL45 | 23:16    |         |      |  |     |                |  |

|        |           | 31:24    |         |      |  |     |                |  |

|        |           | 7:0      | WRTLOCK | CHEN |  | GEN | <b>I</b> [3:0] |  |

| 0.0120 |           | 15:8     |         |      |  |     |                |  |

| 0x0138 | PCHCTRL46 | 23:16    |         |      |  |     |                |  |

|        |           | 31:24    |         |      |  |     |                |  |

|        |           | 7:0      | WRTLOCK | CHEN |  | GEN | <b>I</b> [3:0] |  |

| 0.0120 |           | 15:8     |         |      |  |     |                |  |

| 0x013C | PCHCTRL47 | 23:16    |         |      |  |     |                |  |

|        |           | 31:24    |         |      |  |     |                |  |

### 14.8 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to 14.5.8 Register Access Protection.

Some registers are synchronized when read and/or written. Synchronization is denoted by the "Write-Synchronized" or the "Read-Synchronized" property in each individual register description. For details, refer to 14.6.6 Synchronization.

|                 | Name:<br>Offset:<br>Reset:<br>Property: | OFR<br>0x188<br>0x00000000<br>Read-Only |    |     |        |    |    |        |

|-----------------|-----------------------------------------|-----------------------------------------|----|-----|--------|----|----|--------|

| Bit             | 31                                      | 30                                      | 29 | 28  | 27     | 26 | 25 | 24     |

| Access<br>Reset |                                         |                                         |    |     |        |    |    |        |

| Bit             | 23                                      | 22                                      | 21 | 20  | 19     | 18 | 17 | 16     |

| Access<br>Reset |                                         |                                         |    |     |        |    |    |        |

| Bit             | 15                                      | 14                                      | 13 | 12  | 11     | 10 | 9  | 8      |

|                 |                                         |                                         |    |     |        |    |    | X[9:8] |

| Access          |                                         |                                         |    |     |        |    | R  | R      |

| Reset           |                                         |                                         |    |     |        |    | 0  | 0      |

| Bit             | 7                                       | 6                                       | 5  | 4   | 3      | 2  | 1  | 0      |

|                 |                                         |                                         |    | OFR | X[7:0] |    |    |        |

| Access          |                                         | R                                       | R  | R   | R      | R  | R  | R      |

| Reset           | 0                                       | 0                                       | 0  | 0   | 0      | 0  | 0  | 0      |

### 24.9.72 GMAC Oversized Frames Received Register

### Bits 9:0 - OFRX[9:0] Oversized Frames Received

This pit field counts the number of frames received exceeding 1518 Bytes in length (1536 Bytes if NCFGR.MAXFS is written to '1') but do not have either a CRC error, an alignment error, nor a receive symbol error.

|                 | Name:<br>Offset:<br>Reset:<br>Property: | RLPITR<br>0x270<br>0x00000000<br>Read-Only |        |            |         |        |    |    |

|-----------------|-----------------------------------------|--------------------------------------------|--------|------------|---------|--------|----|----|

| Bit             | 31                                      | 30                                         | 29     | 28         | 27      | 26     | 25 | 24 |

| Access          |                                         |                                            |        |            |         |        |    |    |

| Reset           |                                         |                                            |        |            |         |        |    |    |

| Bit             | 23                                      | 22                                         | 21     | 20         | 19      | 18     | 17 | 16 |

|                 |                                         |                                            |        |            |         |        |    |    |

| Access<br>Reset |                                         |                                            |        |            |         |        |    |    |

| Bit             | 15                                      | 14                                         | 13     | 12         | 11      | 10     | 9  | 8  |

|                 |                                         |                                            |        | RLPITI     | R[15:8] |        |    |    |

| Access          | R                                       | R                                          | R      | R          | R       | R      | R  | R  |

| Reset           | 0                                       | 0                                          | 0      | 0          | 0       | 0      | 0  | 0  |

| Dit             | 7                                       | C                                          | F      | 4          | 2       | 0      | 4  | 0  |

| Bit             | 7                                       | 6                                          | 5      | 4<br>RLPIT | 3       | 2      | 1  | 0  |

| Access          | R                                       | R                                          | R      | R          | R       | R      | R  | R  |

| Reset           |                                         | 0                                          | R<br>0 | К<br>0     | R<br>0  | к<br>0 | 0  | 0  |

| 10301           | 0                                       | Ū                                          | 0      | 0          | 0       | 0      | 0  | v  |

### 24.9.99 Received LPI Transitions

### Bits 15:0 - RLPITR[15:0] Received LPI Transitions

The value of this bit field is a counter of transitions from receiving normal idle to receiving low power idle.

Cleared on read.

### 25.8.5 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x0E                 |

| Reset:    | 0x0000               |

| Property: | PAC Write-Protection |

| Bit    | 15   | 14   | 13    | 12    | 11    | 10     | 9       | 8        |

|--------|------|------|-------|-------|-------|--------|---------|----------|

|        |      |      |       |       |       | SEEWRC | SEESOVF | SEESFULL |

| Access |      |      |       |       |       | R/W    | R/W     | R/W      |

| Reset  |      |      |       |       |       | 0      | 0       | 0        |

|        |      |      |       |       |       |        |         |          |

| Bit    | 7    | 6    | 5     | 4     | 3     | 2      | 1       | 0        |

|        | SUSP | NVME | ECCDE | ECCSE | LOCKE | PROGE  | ADDRE   | DONE     |

| Access | R/W  | R/W  | R/W   | R/W   | R/W   | R/W    | R/W     | R/W      |

| Reset  | 0    | 0    | 0     | 0     | 0     | 0      | 0       | 0        |

**Bit 10 – SEEWRC** SEE Write Completed Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit sets the SEEWRC interrupt enable.

This bit will read as the current value of the SEEWRC interrupt enable.

**Bit 9 – SEESOVF** Active SEES Overflow Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit sets the SEESOVF interrupt enable.

This bit will read as the current value of the SEESOVF interrupt enable.

**Bit 8 – SEESFULL** Active SEES Full Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit sets the SEESFULL interrupt enable.

This bit will read as the current value of the SEESFULL interrupt enable.

**Bit 7 – SUSP** Suspended Write Or Erase Interrupt Enable Writing a zero to this bit has no effect.

Writing a one to this bit sets the SUSP interrupt enable.

This bit will read as the current value of the SUSP interrupt enable.

### Bit 6 – NVME NVM Error Interrupt Enable

Writing a zero to this bit has no effect.

Writing a one to this bit sets the NVME interrupt enable.

This bit will read as the current value of the NVME interrupt enable.

**Bit 5 – ECCDE** ECC Dual Error Interrupt Enable Writing a zero to this bit has no effect.

© 2018 Microchip Technology Inc.

## ICM - Integrity Check Monitor

|        | Name:<br>Offset:<br>Reset:<br>Property: | RCFG<br>0x04 + n*0x00<br>0x00000000<br>Read/Write | C [n=03]  |       |    |         |       |       |

|--------|-----------------------------------------|---------------------------------------------------|-----------|-------|----|---------|-------|-------|

| Bit    | 31                                      | 30                                                | 29        | 28    | 27 | 26      | 25    | 24    |

|        |                                         |                                                   |           |       |    |         |       |       |

| Access |                                         |                                                   |           |       |    |         |       |       |

| Reset  |                                         |                                                   |           |       |    |         |       |       |

| Bit    | 23                                      | 22                                                | 21        | 20    | 19 | 18      | 17    | 16    |

|        |                                         |                                                   |           |       |    |         |       |       |

| Access |                                         |                                                   |           |       |    |         |       |       |

| Reset  |                                         |                                                   |           |       |    |         |       |       |

| Bit    | 15                                      | 14                                                | 13        | 12    | 11 | 10      | 9     | 8     |

|        |                                         |                                                   | ALGO[2:0] |       |    | PROCDLY | SUIEN | ECIEN |

| Access |                                         |                                                   |           |       |    | R/W     | R/W   | R/W   |

| Reset  |                                         | 0                                                 | 0         | 0     |    | 0       | 1     | 1     |

|        |                                         |                                                   |           |       |    |         |       |       |

| Bit    |                                         | 6                                                 | 5         | 4     | 3  | 2       | 1     | 0     |

|        | WCIEN                                   | BEIEN                                             | DMIEN     | RHIEN |    | EOM     | WRAP  | CDWBN |

| Access | R/W                                     | R/W                                               | R/W       | R/W   |    | R/W     | R/W   | R/W   |

| Reset  | 1                                       | 1                                                 | 1         | 1     |    | 0       | 0     | 0     |

### 26.6.3.1.2 Region Configuration Structure Member

### Bits 14:12 - ALGO[2:0] User SHA Algorithm

| Value | Name   | Description                |  |  |  |

|-------|--------|----------------------------|--|--|--|

| 0     | SHA1   | SHA1 algorithm processed   |  |  |  |

| 1     | SHA256 | HA256 algorithm processed  |  |  |  |

| 4     | SHA224 | SHA224 algorithm processed |  |  |  |

| Other | -      | Reserved                   |  |  |  |

### Bit 10 – PROCDLY Processing Delay

For a given SHA algorithm, the runtime period has two possible lengths:

### Table 26-2. SHA Processing Runtime Periods

| Algorithm | SHORTEST [number of cycles] | LONGEST [number of cycles] |  |  |

|-----------|-----------------------------|----------------------------|--|--|

| SHA1      | 85                          | 209                        |  |  |

| SHA224    | 72                          | 194                        |  |  |

| SHA256    | 72                          | 194                        |  |  |

| Value | Name     | Description                                |

|-------|----------|--------------------------------------------|

| 0     | SHORTEST | SHA processing runtime is the shortest one |

| 1     | LONGEST  | SHA processing runtime is the longest one  |

#### 30.8.9 Value

|        | Name:<br>Offset:<br>Reset:<br>Property: | VALUE<br>0x10<br>0x00000000<br>- |    |       |         |    |    |    |

|--------|-----------------------------------------|----------------------------------|----|-------|---------|----|----|----|

| Bit    | 31                                      | 30                               | 29 | 28    | 27      | 26 | 25 | 24 |

|        |                                         |                                  |    |       |         |    |    |    |

| Access |                                         |                                  |    |       |         |    |    |    |

| Reset  |                                         |                                  |    |       |         |    |    |    |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 23                                      | 22                               | 21 | 20    | 19      | 18 | 17 | 16 |

|        |                                         |                                  |    |       | [23:16] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 15                                      | 14                               | 13 | 12    | 11      | 10 | 9  | 8  |

|        |                                         |                                  |    | VALUE | E[15:8] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 7                                       | 6                                | 5  | 4     | 3       | 2  | 1  | 0  |

|        |                                         |                                  |    | VALU  | E[7:0]  |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

Bits 23:0 - VALUE[23:0] Measurement Value Result from measurement.

# SAMD5x/E5x Family Data Sheet SERCOM SPI – SERCOM Serial Peripheral Interface

### 35.8.8 Status

|        | Name:<br>Offset:<br>Reset:<br>Property: | STATUS<br>0x1A<br>0x0000<br>- |    |    |        |        |   |   |

|--------|-----------------------------------------|-------------------------------|----|----|--------|--------|---|---|

| Bit    | 15                                      | 14                            | 13 | 12 | 11     | 10     | 9 | 8 |

|        |                                         |                               |    |    | LENERR |        |   |   |

| Access |                                         |                               |    |    | R/W    |        |   |   |

| Reset  |                                         |                               |    |    | 0      |        |   |   |

| Bit    | 7                                       | 6                             | 5  | 4  | 3      | 2      | 1 | 0 |

|        |                                         |                               |    |    |        | BUFOVF |   |   |

| Access |                                         |                               |    |    |        | R/W    |   |   |

| Reset  |                                         |                               |    |    |        | 0      |   |   |

### Bit 11 – LENERR Transaction Length Error

This bit is set in slave mode when the length counter is enabled (LENGTH.LENEN=1) and the transfer length while  $\overline{SS}$  is low is not a multiple of LENGTH.LEN.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

| Value | Description                   |

|-------|-------------------------------|

| 0     | No Length Error has occurred. |

| 1     | A Length Error has occurred.  |

### Bit 2 – BUFOVF Buffer Overflow

Reading this bit before reading DATA will indicate the error status of the next character to be read.

This bit is cleared by writing '1' to the bit or by disabling the receiver.

This bit is set when a buffer overflow condition is detected. See also CTRLA.IBON for overflow handling.

When set, the corresponding RxDATA will be zero.

Writing '0' to this bit has no effect.

Writing '1' to this bit will clear it.

| Value | Description                      |

|-------|----------------------------------|

| 0     | No Buffer Overflow has occurred. |

| 1     | A Buffer Overflow has occurred.  |

## SAMD5x/E5x Family Data Sheet USB – Universal Serial Bus

After resuming from the L1 SLEEP state, the bit CTRLB.SOFE is set, allowing Start-of-Frame generation.

### 38.8.6.6 Host Pipe Interrupt Flag Register

| Name:     | PINTFLAG           |

|-----------|--------------------|

| Offset:   | 0x107 + (n x 0x20) |

| Reset:    | 0x00               |

| Property: | -                  |

| Bit    | 7 | 6 | 5     | 4     | 3    | 2      | 1 | 0     |

|--------|---|---|-------|-------|------|--------|---|-------|

| ĺ      |   |   | STALL | TXSTP | PERR | TRFAIL |   | TRCPT |

| Access |   |   | R/W   | R/W   | R/W  | R/W    |   | R/W   |

| Reset  |   |   | 0     | 0     | 0    | 0      |   | 2     |

**Bit 5 – STALL** STALL Received Interrupt Flag This flag is cleared by writing a one to the flag.

This flag is set when a stall occurs and will generate an interrupt if PINTENCLR/SET.STALL is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the STALL Interrupt Flag.

Bit 4 – TXSTP Transmitted Setup Interrupt Flag

This flag is cleared by writing a one to the flag.

This flag is set when a Transfer Complete occurs and will generate an interrupt if PINTENCLR/ SET.TXSTP is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the TXSTP Interrupt Flag.

### **Bit 3 – PERR** Pipe Error Interrupt Flag

This flag is cleared by writing a one to the flag.

This flag is set when a pipe error occurs and will generate an interrupt if PINTENCLR/SET.PERR is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the PERR Interrupt Flag.

### Bit 2 – TRFAIL Transfer Fail Interrupt Flag

This flag is cleared by writing a one to the flag.

This flag is set when a Transfer Fail occurs and will generate an interrupt if PINTENCLR/SET.TRFAIL is one.

Writing a zero to this bit has no effect.

Writing a one to this bit clears the TRFAIL Interrupt Flag.

**Bit 0 – TRCPT** Transfer Complete x interrupt Flag This flag is cleared by writing a one to the flag.

This flag is set when a Transfer complete occurs and will generate an interrupt if PINTENCLR/ SET.TRCPT is one. PINTFLAG.TRCPT is set for a single bank IN/OUT pipe or a double bank IN/OUT pipe when current bank is 0.

### 39.8.1 Core Release

| Name:     | CREL       |

|-----------|------------|

| Offset:   | 0x00       |

| Reset:    | 0x32100000 |

| Property: | Read-only  |

| Bit    | 31       | 30    | 29      | 28 | 27        | 26 | 25 | 24 |  |

|--------|----------|-------|---------|----|-----------|----|----|----|--|

|        | REL[3:0] |       |         |    | STEP[3:0] |    |    |    |  |

| Access | R        | R     | R       | R  | R         | R  | R  | R  |  |

| Reset  | 0        | 0     | 1       | 1  | 0         | 0  | 1  | 0  |  |

|        |          |       |         |    |           |    |    |    |  |

| Bit    | 23       | 22    | 21      | 20 | 19        | 18 | 17 | 16 |  |

|        |          | SUBST | EP[3:0] |    |           |    |    |    |  |

| Access | R        | R     | R       | R  |           |    |    |    |  |

| Reset  | 0        | 0     | 0       | 1  |           |    |    |    |  |

|        |          |       |         |    |           |    |    |    |  |

| Bit    | 15       | 14    | 13      | 12 | 11        | 10 | 9  | 8  |  |

|        |          |       |         |    |           |    |    |    |  |

| Access |          |       |         |    | -         |    |    |    |  |

| Reset  |          |       |         |    |           |    |    |    |  |

|        |          |       |         |    |           |    |    |    |  |

| Bit    | 7        | 6     | 5       | 4  | 3         | 2  | 1  | 0  |  |

|        |          |       |         |    |           |    |    |    |  |

| Access |          |       |         |    |           |    |    |    |  |

Reset

**Bits 31:28 – REL[3:0]** Core Release One digit, BCD-coded.

**Bits 27:24 – STEP[3:0]** Step of Core Release One digit, BCD-coded.

**Bits 23:20 – SUBSTEP[3:0]** Sub-step of Core Release One digit, BCD-coded.

SD/MMC Host Controller ...

| Offset | Name     | Bit Pos. |                      |           |          |         |           |          |           |          |

|--------|----------|----------|----------------------|-----------|----------|---------|-----------|----------|-----------|----------|

| 0x2B   | WCR      | 7:0      |                      |           |          |         |           | WKENCREM | WKENCINS  | WKENCINT |

| 0.20   | 000      | 7:0      | USDCLK               | FSEL[1:0] | CLKGSEL  |         |           | SDCLKEN  | INTCLKS   | INTCLKEN |

| 0x2C   | CCR      | 15:8     |                      |           |          | SDCLKF  | SEL[7:0]  |          |           |          |

| 0x2E   | TCR      | 7:0      |                      |           |          |         |           | DTCV     | AL[3:0]   |          |

| 0x2F   | SRR      | 7:0      |                      |           |          |         |           | SWRSTDAT | SWRSTCMD  | SWRSTALL |

| 0x30   | NISTR    | 7:0      | CREM                 | CINS      | BRDRDY   | BWRRDY  | DMAINT    | BLKGE    | TRFC      | CMDC     |

| 0,00   | Norre    | 15:8     | ERRINT               | BOOTAR    |          |         |           |          |           | CINT     |

| 0x32   | EISTR    | 7:0      | CURLIM               | DATEND    | DATCRC   | DATTEO  | CMDIDX    | CMDEND   | CMDCRC    | CMDTEO   |

| 0.02   | LIGHT    | 15:8     |                      |           |          | BOOTAE  |           |          | ADMA      | ACMD     |

| 0x34   | NISTER   | 7:0      | CREM                 | CINS      | BRDRDY   | BWRRDY  | DMAINT    | BLKGE    | TRFC      | CMDC     |

| 0,04   | NOTER    | 15:8     |                      | BOOTAR    |          |         |           |          |           |          |

| 0x36   | EISTER   | 7:0      | CURLIM               | DATEND    | DATCRC   | DATTEO  | CMDIDX    | CMDEND   | CMDCRC    | CMDTEO   |

| 0,00   | LIGTER   | 15:8     |                      |           |          | BOOTAE  |           |          | ADMA      | ACMD     |

| 0x38   | NISIER   | 7:0      | CREM                 | CINS      | BRDRDY   | BWRRDY  | DMAINT    | BLKGE    | TRFC      | CMDC     |

| 0,00   | MOLEN    | 15:8     |                      | BOOTAR    |          |         |           |          |           | CINT     |

| 0x3A   | EISIER   | 7:0      | CURLIM               | DATEND    | DATCRC   | DATTEO  | CMDIDX    | CMDEND   | CMDCRC    | CMDTEO   |

|        | LIGIER   | 15:8     |                      |           |          | BOOTAE  |           |          | ADMA      | ACMD     |

| 0x3C   | ACESR    | 7:0      | CMDNI                |           |          | ACMDIDX | ACMDEND   | ACMDCRC  | ACMDTEO   | ACMD12NE |

|        | ACCON    | 15:8     |                      |           |          |         |           |          |           |          |

| 0x3E   | HC2R     | 7:0      |                      |           |          |         |           |          |           |          |

|        |          | 15:8     | PVALEN               |           |          |         |           |          |           |          |

| 0x3E   | HC2R     | 7:0      |                      |           |          |         |           |          |           |          |

|        |          | 15:8     | PVALEN               | ASINTEN   |          |         |           |          |           |          |

|        |          | 7:0      | TEOCLKU TEOCLKF[5:0] |           |          |         |           |          |           |          |

| 0x40   | CA0R     | 15:8     |                      |           |          | BASEC   | LKF[7:0]  |          |           |          |

| 0X10   | CAUR     | 23:16    | SRSUP                | SDMASUP   | HSSUP    |         | ADMA2SUP  | ED8SUP   |           | MAXBLKL  |

|        |          | 31:24    | SLTY                 | PE[1:0]   | ASINTSUP | SB64SUP |           |          | V30VSUP   | V33VSUP  |

|        |          | 7:0      |                      | DRVDSUP   | DRVCSUP  | DRVASUP |           | DDR50SUP | SDR104SUP | SDR50SUP |

| 0x44   | CA1R     | 15:8     |                      |           |          |         |           |          |           |          |

| UX II  | o, the   | 23:16    |                      |           | 1        | CLKMU   | JLT[7:0]  | 1        |           |          |

|        |          | 31:24    |                      |           |          |         |           |          |           |          |

|        |          | 7:0      |                      |           |          | MAXCU   | R33V[7:0] |          |           |          |

| 0x48   | MCCAR    | 15:8     |                      |           |          | MAXCU   | R30V[7:0] |          |           |          |

| UX IO  |          | 23:16    |                      |           |          |         |           |          |           |          |

|        |          | 31:24    |                      |           |          |         |           |          |           |          |

| 0x4C   |          |          |                      |           |          |         |           |          |           |          |

|        | Reserved |          |                      |           |          |         |           |          |           |          |

| 0x4F   |          |          |                      |           |          |         |           |          |           |          |

| 0x50   | FERACES  | 7:0      | CMDNI                |           |          | ACMDIDX | ACMDEND   | ACMDCRC  | ACMDTEO   | ACMD12NE |

|        |          | 15:8     |                      |           |          |         |           |          |           |          |

| 0x52   | FEREIS   | 7:0      | CURLIM               | DATEND    | DATCRC   | DATTEO  | CMDIDX    | CMDEND   | CMDCRC    | CMDTEO   |

|        |          | 15:8     |                      |           |          | BOOTAE  |           |          | ADMA      | ACMD     |

| 0x54   | AESR     | 7:0      |                      |           |          |         |           | LMIS     | ERRS      | T[1:0]   |

| 0x55   |          |          |                      |           |          |         |           |          |           |          |

|        | Reserved |          |                      |           |          |         |           |          |           |          |

| 0x57   |          |          |                      |           |          |         |           |          |           |          |

### SD/MMC Host Controller ...

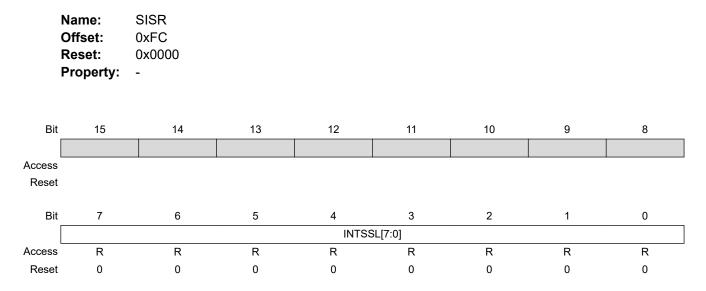

### 40.8.34 Slot Interrupt Status Register

Bits 7:0 - INTSSL[7:0] Interrupt Signal for Each Slot

These status bits indicate the logical OR of Interrupt Signals and WakeUp Signal for each peripheral instance in the device. INTSSL[x] corresponds to instance SDHCx. There are 2 instances in this device.

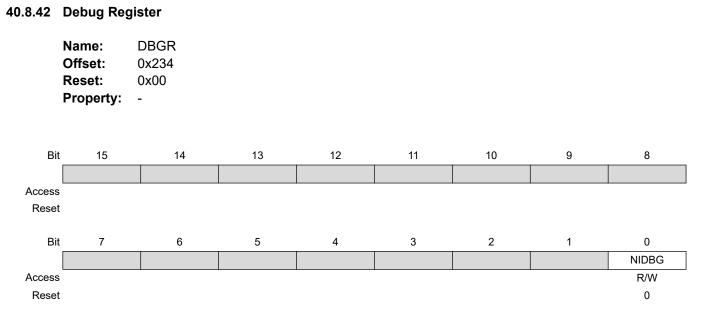

## SD/MMC Host Controller ...

### Bit 0 - NIDBG Non-Intrusive Debug

| Value | Name     | Description                                                                      |

|-------|----------|----------------------------------------------------------------------------------|

| 0     | DISABLED | Reading the BDPR via debugger increments the dual port RAM read pointer.         |

| 1     | ENABLED  | Reading the BDPR via debugger does not increment the dual port RAM read pointer. |

TC – Timer/Counter

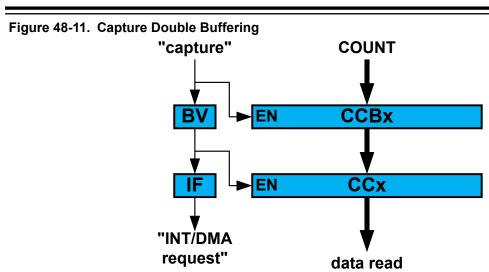

For input capture, the buffer register and the corresponding CCx act like a FIFO. When CCx is empty or read, any content in CCBUFx is transferred to CCx. The buffer valid flag is passed to set the CCx interrupt flag (IF) and generate the optional interrupt, event or DMA request. The CCBUFx register value can't be read, all captured data must be read from CCx register.

### Note:

When up-counting (CTRLBSET.DIR=0), counter values lower than 1 cannot be captured. To capture the full range including value 0, the TC must be in down-counting mode (CTRLBSET.DIR=0).

### 48.6.2.8.1 Event Capture Action

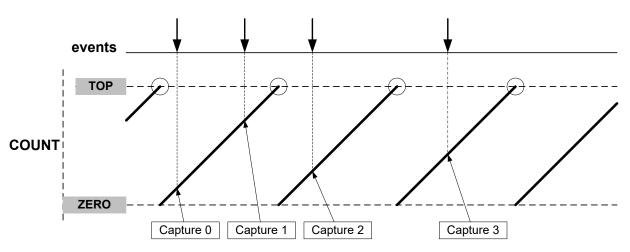

The compare/capture channels can be used as input capture channels to capture events from the Event System and give them a timestamp. The following figure shows four capture events for one capture channel.

### Figure 48-12. Input Capture Timing

The TC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Interrupt flag (INTFLAG.MCx) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

### 48.6.2.8.2 Period and Pulse-Width (PPW) Capture Action

The TC can perform two input captures and restart the counter on one of the edges. This enables the TC to measure the pulse width and period and to characterize the frequency f and duty cycle of an input signal:

### TC – Timer/Counter

#### 48.7.1.12 Synchronization Busy

|         | Name:<br>Offset:<br>Reset:<br>Property: | SYNCBUSY<br>0x10<br>0x00000000<br>- |    |       |        |       |        |       |

|---------|-----------------------------------------|-------------------------------------|----|-------|--------|-------|--------|-------|

| Bit     | 31                                      | 30                                  | 29 | 28    | 27     | 26    | 25     | 24    |

|         |                                         |                                     |    |       |        |       |        |       |

| Access  |                                         |                                     |    |       |        |       |        |       |

| Reset   |                                         |                                     |    |       |        |       |        |       |

|         |                                         |                                     |    |       |        |       |        |       |

| Bit     | 23                                      | 22                                  | 21 | 20    | 19     | 18    | 17     | 16    |

|         |                                         |                                     |    |       |        |       |        |       |

| Access  |                                         |                                     |    |       |        |       |        |       |

| Reset   |                                         |                                     |    |       |        |       |        |       |

| Bit     | 15                                      | 14                                  | 13 | 10    | 11     | 10    | 9      | 8     |

| DIL     | 15                                      | 14                                  | 13 | 12    | 11     | 10    | 9      | 0     |

| Access  |                                         |                                     |    |       |        |       |        |       |

| Reset   |                                         |                                     |    |       |        |       |        |       |

| i veset |                                         |                                     |    |       |        |       |        |       |

| Bit     | 7                                       | 6                                   | 5  | 4     | 3      | 2     | 1      | 0     |

|         |                                         | CCx                                 |    | COUNT | STATUS | CTRLB | ENABLE | SWRST |

| Access  |                                         | R                                   |    | R     | R      | R     | R      | R     |

| Reset   |                                         | 0                                   |    | 0     | 0      | 0     | 0      | 0     |

**Bit 6 – CCx** Compare/Capture Channel x Synchronization Busy For details on CC channels number, refer to each TC feature list.

This bit is set when the synchronization of CCx between clock domains is started.

This bit is also set when the CCBUFx is written, and cleared on update condition. The bit is automatically cleared when the STATUS.CCBUFx bit is cleared.

### **Bit 4 – COUNT** COUNT Synchronization Busy

This bit is cleared when the synchronization of COUNT between the clock domains is complete.

This bit is set when the synchronization of COUNT between clock domains is started.

### Bit 3 – STATUS STATUS Synchronization Busy

This bit is cleared when the synchronization of STATUS between the clock domains is complete.

This bit is set when a '1' is written to the Capture Channel Buffer Valid status flags (STATUS.CCBUFVx) and the synchronization of STATUS between clock domains is started.

### Bit 2 - CTRLB CTRLB Synchronization Busy

This bit is cleared when the synchronization of CTRLB between the clock domains is complete.

This bit is set when the synchronization of CTRLB between clock domains is started.

### Bit 4 – TCINV TC Inverted Event Input Polarity

This bit inverts the asynchronous input event source.

| V | alue | Description                         |

|---|------|-------------------------------------|

| 0 |      | Input event source is not inverted. |

| 1 |      | Input event source is inverted.     |

### Bits 2:0 - EVACT[2:0] Event Action

These bits define the event action the TC will perform on an event.

| Value | Name      | Description                                       |  |  |  |  |

|-------|-----------|---------------------------------------------------|--|--|--|--|

| 0x0   | OFF       | Event action disabled                             |  |  |  |  |

| 0x1   | RETRIGGER | RETRIGGER Start, restart or retrigger TC on event |  |  |  |  |

| 0x2   | COUNT     | Count on event                                    |  |  |  |  |

| 0x3   | START     | Start TC on event                                 |  |  |  |  |

| 0x4   | STAMP     | Time stamp capture                                |  |  |  |  |

| 0x5   | PPW       | Period captured in CC0, pulse width in CC1        |  |  |  |  |

| 0x6   | PWP       | Period captured in CC1, pulse width in CC0        |  |  |  |  |

| 0x7   | PW        | Pulse width capture                               |  |  |  |  |

# 49. TCC – Timer/Counter for Control Applications

### 49.1 Overview

The device provides five instances of the Timer/Counter for Control applications (TCC) peripheral, TCC[4:0].

Each TCC instance consists of a counter, a prescaler, compare/capture channels and control logic. The counter can be set to count events or clock pulses. The counter together with the compare/capture channels can be configured to time stamp input events, allowing capture of frequency and pulse-width. It can also perform waveform generation, such as frequency generation and pulse-width modulation.

Waveform extensions are featured for motor control, ballast, LED, H-bridge, power converters, and other types of power control applications. They allow for low-side and high-side output with optional dead-time insertion. Waveform extensions can also generate a synchronized bit pattern across the waveform output pins. The fault options enable fault protection for safe and deterministic handling, disabling and/or shut down of external drivers.

**Note:** The TCC configurations, such as channel numbers and features, may be reduced for some of the TCC instances.

### **Related Links**

6.2.7 TCC Configurations

### 49.2 Features

- Up to six compare/capture channels (CC) with:

- Double buffered period setting

- Double buffered compare or capture channel

- Circular buffer on period and compare channel registers

- Waveform generation:

- Frequency generation

- Single-slope pulse-width modulation (PWM)

- Dual-slope PWM with half-cycle reload capability

- Input capture:

- Event capture

- Frequency capture

- Pulse-width capture

- Waveform extensions:

- Configurable distribution of compare channels outputs across port pins

- Low-side and high-side output with programmable dead-time insertion

- Waveform swap option with double buffer support

- Pattern generation with double buffer support

- Dithering support

- Fault protection for safe disabling of drivers:

- Two recoverable fault sources

**PTC - Peripheral Touch Controller**

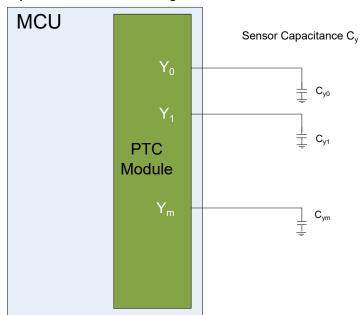

### Figure 50-4. Self-Capacitance Sensor Arrangement

For more information about designing the touch sensor, refer to Buttons, Sliders and Wheels Touch Sensor Design Guide.

### 50.5.2 Analog-Digital Converter (ADC)

The PTC is using the ADC for signal conversion and acquisition. The ADC must be enabled and configured appropriately to allow correct behavior of the PTC.

### **Related Links**

45. ADC - Analog-to-Digital Converter

### 50.6 Functional Description

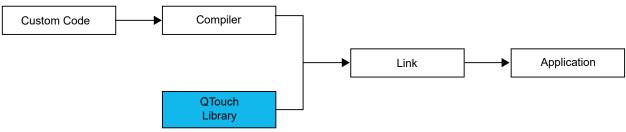

In order to access the PTC, the user must use the Atmel Start QTouch<sup>®</sup> Configurator to configure and link the QTouch Library firmware with the application software. QTouch Library can be used to implement buttons, sliders, and wheels in a variety of combinations on a single interface.

### Figure 50-5. QTouch Library Usage

For more information about QTouch Library, refer to the QTouch Library Peripheral Touch Controller User Guide.

## PCC - Parallel Capture Controller

### 52.8.6 Reception Holding Register

| Name:     | RHR        |

|-----------|------------|

| Offset:   | 0x14       |

| Reset:    | 0x00000000 |

| Property: | -          |

| Bit    | 31           | 30 | 29 | 28 | 27 | 26 | 25 | 24 |

|--------|--------------|----|----|----|----|----|----|----|

|        | RDATA[31:24] |    |    |    |    |    |    |    |

| Access | R            | R  | R  | R  | R  | R  | R  | R  |

| Reset  | 0            | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|        |              |    |    |    |    |    |    |    |

| Bit    | 23           | 22 | 21 | 20 | 19 | 18 | 17 | 16 |

|        | RDATA[23:16] |    |    |    |    |    |    |    |

| Access | R            | R  | R  | R  | R  | R  | R  | R  |

| Reset  | 0            | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|        |              |    |    |    |    |    |    |    |

| Bit    | 15           | 14 | 13 | 12 | 11 | 10 | 9  | 8  |

|        | RDATA[15:8]  |    |    |    |    |    |    |    |

| Access | R            | R  | R  | R  | R  | R  | R  | R  |

| Reset  | 0            | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

|        |              |    |    |    |    |    |    |    |

| Bit    | 7            | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|        | RDATA[7:0]   |    |    |    |    |    |    |    |

| Access | R            | R  | R  | R  | R  | R  | R  | R  |

| Reset  | 0            | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

### Bits 31:0 - RDATA[31:0] Reception Data

| ISIZE   | SCALE   | DSIZE  | Description                                |  |

|---------|---------|--------|--------------------------------------------|--|

| 8_BITS  | -       | 1_DATA | RDATA[7:0] is useful                       |  |

|         |         | 2_DATA | RDATA[15:0] is useful                      |  |

|         |         | 4_DATA | RDATA[31:0] is useful                      |  |

| 10_BITS | 0 (OFF) | 1_DATA | RDATA[9:0] is useful                       |  |

|         |         | 2_DATA | RDATA[9:0] and<br>RDATA[25:16] are useful  |  |

|         | 1 (ON)  | 1_DATA | RDATA[15:0] is useful                      |  |

|         |         | 2_DATA | RDATA[31:0] is useful                      |  |

| 12_BITS | 0 (OFF) | 1_DATA | RDATA[11:0] is useful                      |  |

|         |         | 2_DATA | RDATA[11:0] and<br>RDATA[27:16] are useful |  |

|         | 1 (ON)  | 1_DATA | RDATA[15:0] is useful                      |  |

|         |         | 2_DATA | RDATA[31:0] is useful                      |  |