Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 120MHz                                                                                |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 51                                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 128K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-TQFP                                                                               |

| Supplier Device Package    | 64-TQFP (10x10)                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame53j18a-au             |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### CMCC - Cortex M Cache Controller

#### 11.10.11 Cache Monitor Status

| Name:     | MSR        |

|-----------|------------|

| Offset:   | 0x34       |

| Reset:    | 0x00000000 |

| Property: | -          |

| Bit    | 31               | 30 | 29 | 28      | 27        | 26 | 25 | 24 |  |  |  |

|--------|------------------|----|----|---------|-----------|----|----|----|--|--|--|

|        | EVENT_CNT[31:24] |    |    |         |           |    |    |    |  |  |  |

| Access | R                | R  | R  | R       | R         | R  | R  | R  |  |  |  |

| Reset  | 0                | 0  | 0  | 0       | 0         | 0  | 0  | 0  |  |  |  |

|        |                  |    |    |         |           |    |    |    |  |  |  |

| Bit    | 23               | 22 | 21 | 20      | 19        | 18 | 17 | 16 |  |  |  |

|        |                  |    |    | EVENT_C | NT[23:16] |    |    |    |  |  |  |

| Access | R                | R  | R  | R       | R         | R  | R  | R  |  |  |  |

| Reset  | 0                | 0  | 0  | 0       | 0         | 0  | 0  | 0  |  |  |  |

|        |                  |    |    |         |           |    |    |    |  |  |  |

| Bit    | 15               | 14 | 13 | 12      | 11        | 10 | 9  | 8  |  |  |  |

|        |                  |    |    | EVENT_  | CNT[15:8] |    |    |    |  |  |  |

| Access | R                | R  | R  | R       | R         | R  | R  | R  |  |  |  |

| Reset  | 0                | 0  | 0  | 0       | 0         | 0  | 0  | 0  |  |  |  |

|        |                  |    |    |         |           |    |    |    |  |  |  |

| Bit    | 7                | 6  | 5  | 4       | 3         | 2  | 1  | 0  |  |  |  |

|        |                  |    |    | EVENT_  | CNT[7:0]  |    |    |    |  |  |  |

| Access | R                | R  | R  | R       | R         | R  | R  | R  |  |  |  |

| Reset  | 0                | 0  | 0  | 0       | 0         | 0  | 0  | 0  |  |  |  |

|        |                  |    |    |         |           |    |    |    |  |  |  |

**Bits 31:0 – EVENT\_CNT[31:0]** Monitor Event Counter This field indicates the Monitor Event Counter value.

### **DSU - Device Service Unit**

#### 12.13.15 Peripheral Identification 7

|        | Name:<br>Offset:<br>Reset:<br>Property: | PID7<br>0x1FDC<br>0x00000000<br>Read-Only |    |    |    |    |    |    |

|--------|-----------------------------------------|-------------------------------------------|----|----|----|----|----|----|

| Bit    | 31                                      | 30                                        | 29 | 28 | 27 | 26 | 25 | 24 |

|        |                                         |                                           |    |    |    |    |    |    |

| Access |                                         |                                           |    |    |    |    |    |    |

| Reset  |                                         |                                           |    |    |    |    |    |    |

| Bit    | 23                                      | 22                                        | 21 | 20 | 19 | 18 | 17 | 16 |

|        |                                         |                                           |    |    |    |    |    |    |

| Access |                                         |                                           |    |    |    |    |    |    |

| Reset  |                                         |                                           |    |    |    |    |    |    |

| Bit    | 15                                      | 14                                        | 13 | 12 | 11 | 10 | 9  | 8  |

|        |                                         |                                           |    |    |    |    |    |    |

| Access |                                         |                                           |    |    |    |    |    |    |

| Reset  |                                         |                                           |    |    |    |    |    |    |

| Bit    | 7                                       | 6                                         | 5  | 4  | 3  | 2  | 1  | 0  |

|        |                                         |                                           |    |    |    |    |    |    |

| Access |                                         |                                           |    |    |    |    |    |    |

| Reset  |                                         |                                           |    |    |    |    |    |    |

**RTC – Real-Time Counter**

#### Bit 2 – FREQCORR Frequency Correction Synchronization Busy Status

| Value | Description                                              |

|-------|----------------------------------------------------------|

| 0     | Write synchronization for FREQCORR register is complete. |

| 1     | Write synchronization for FREQCORR register is ongoing.  |

#### **Bit 1 – ENABLE** Enable Synchronization Busy Status

| Value | Description                                             |

|-------|---------------------------------------------------------|

| 0     | Write synchronization for CTRLA.ENABLE bit is complete. |

| 1     | Write synchronization for CTRLA.ENABLE bit is ongoing.  |

#### Bit 0 – SWRST Software Reset Synchronization Busy Status

| Value | Description                                            |

|-------|--------------------------------------------------------|

| 0     | Write synchronization for CTRLA.SWRST bit is complete. |

| 1     | Write synchronization for CTRLA.SWRST bit is ongoing.  |

- 1. Write to Network Control register to disable transmit and receive circuits.

- 2. Write to Network Control register to change loop back mode.

- 3. Write to Network Control register to re-enable transmit or receive circuits. Note: These writes to the Network Control register cannot be combined in any way.

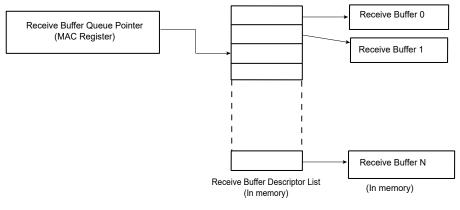

#### 24.7.1.2 Receive Buffer List

Receive data is written to areas of data (i.e., buffers) in system memory. These buffers are listed in another data structure that also resides in main memory. This data structure (receive buffer queue) is a sequence of descriptor entries as defined in Table 1-6 "Receive Buffer Descriptor Entry".

The Receive Buffer Queue Pointer register points to this data structure.

#### Figure 24-3. Receive Buffer List

To create the list of buffers:

- 1. Allocate a number (N) of buffers of X bytes in system memory, where X is the DMA buffer length programmed in the DMA Configuration register.

- 2. Allocate an area 8N bytes for the receive buffer descriptor list in system memory and create N entries in this list. Mark all entries in this list as owned by GMAC, i.e., bit 0 of word 0 set to 0.

- 3. Mark the last descriptor in the queue with the wrap bit (bit 1 in word 0 set to 1).

- 4. Write address of receive buffer descriptor list and control information to GMAC register receive buffer queue pointer

- 5. The receive circuits can then be enabled by writing to the address recognition registers and the Network Control register.

#### 24.7.1.3 Transmit Buffer List

Transmit data is read from areas of data (the buffers) in system memory. These buffers are listed in another data structure that also resides in main memory. This data structure (Transmit Buffer Queue) is a sequence of descriptor entries as defined in Table 1-7 "Transmit Buffer Descriptor Entry".

The Transmit Buffer Queue Pointer register points to this data structure.

To create this list of buffers:

- 1. Allocate a number (N) of buffers of between 1 and 2047 bytes of data to be transmitted in system memory. Up to 128 buffers per frame are allowed.

- 2. Allocate an area 8N bytes for the transmit buffer descriptor list in system memory and create N entries in this list. Mark all entries in this list as owned by GMAC, i.e., bit 31 of word 1 set to 0.

- 3. Mark the last descriptor in the queue with the wrap bit (bit 30 in word 1 set to 1).

#### 24.9.2 **GMAC Network Configuration Register**

| C<br>F | Name:<br>Dffset:<br>Reset:<br>Property: | NCFGR<br>0x004<br>0x00080000<br>R/W |      |        |          |        |       |        |

|--------|-----------------------------------------|-------------------------------------|------|--------|----------|--------|-------|--------|

| Bit    | 31                                      | 30                                  | 29   | 28     | 27       | 26     | 25    | 24     |

|        |                                         | IRXER                               | RXBP | IPGSEN |          | IRXFCS | EFRHD | RXCOEN |

| Access |                                         | R/W                                 | R/W  | R/W    |          | R/W    | R/W   | R/W    |

| Reset  |                                         | 0                                   | 0    | 0      |          | 0      | 0     | 0      |

| Bit    | 23                                      | 22                                  | 21   | 20     | 19       | 18     | 17    | 16     |

| Γ      | DCPF                                    |                                     |      |        | CLK[2:0] |        | RFCS  | LFERD  |

| Access | R/W                                     |                                     |      | R/W    | R/W      | R/W    | R/W   | R/W    |

| Reset  | 0                                       |                                     |      | 0      | 1        | 0      | 0     | 0      |

| Bit    | 15                                      | 14                                  | 13   | 12     | 11       | 10     | 9     | 8      |

| Γ      | RXB                                     | UFO[1:0]                            | PEN  | RTY    |          |        |       | MAXFS  |

| Access | R/W                                     | R/W                                 | R/W  | R/W    |          | •      |       | R/W    |

| Reset  | 0                                       | 0                                   | 0    | 0      |          |        |       | 0      |

| Bit    | 7                                       | 6                                   | 5    | 4      | 3        | 2      | 1     | 0      |

| Γ      | UNIHEN                                  | MTIHEN                              | NBC  | CAF    | JFRAME   | DNVLAN | FD    | SPD    |

| Access | R/W                                     | R/W                                 | R/W  | R/W    | R/W      | R/W    | R/W   | R/W    |

| Reset  | 0                                       | 0                                   | 0    | 0      | 0        | 0      | 0     | 0      |

#### Bit 30 – IRXER Ignore IPG GRXER

When this bit is written to '1', the Receive Error signal (GRXER) has no effect on the GMAC operation when Receive Data Valid signal (GRXDV) is low.

#### Bit 29 - RXBP Receive Bad Preamble

When written to '1', frames with non-standard preamble are not rejected.

#### Bit 28 - IPGSEN IP Stretch Enable

Writing a '1' to this bit allows the transmit IPG to increase above 96 bit times, depending on the previous frame length using the IPG Stretch Register.

#### Bit 26 – IRXFCS Ignore RX FCS

For normal operation this bit must be written to zero.

When this bit is written to '1', frames with FCS/CRC errors will not be rejected. FCS error statistics will still be collected for frames with bad FCS, and FCS status will be recorded in the DMA descriptor of the frame.

#### Bit 25 – EFRHD Enable Frames Received in half-duplex

Writing a '1' to this bit enables frames to be received in half-duplex mode while transmitting.

#### Cleared on read.

#### Bit 6 – TFC Transmit Frame Corruption Due to AHB Error

Transmit frame corruption due to AHB error. Set if an error occurs during reading a transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame.

#### Bit 5 – RLEX Retry Limit Exceeded

Retry Limit Exceeded Transmit error.

Cleared on read.

#### Bit 4 – TUR Transmit Underrun

This interrupt is set if the transmitter was forced to terminate an ongoing frame transmission due to further data being unavailable.

This interrupt is also set if a transmitter status write back has not completed when another status write back is attempted.

This interrupt is also set when the transmit DMA has written the SOP data into the FIFO and either the AHB bus was not granted in time for further data, or because an AHB not OK response was returned, or because the used bit was read.

#### **Bit 3 – TXUBR** TX Used Bit Read Set when a transmit buffer descriptor is read with its used bit set.

Cleared on read.

#### Bit 2 – RXUBR RX Used Bit Read

Set when a receive buffer descriptor is read with its used bit set.

Cleared on read.

#### Bit 1 – RCOMP Receive Complete

A frame has been stored in memory.

Cleared on read.

#### Bit 0 - MFS Management Frame Sent

The PHY Maintenance Register has completed its operation.

Cleared on read.

#### 24.9.61 GMAC Broadcast Frames Received Register

| Name:     | BCFR       |

|-----------|------------|

| Offset:   | 0x15C      |

| Reset:    | 0x00000000 |

| Property: | Read-only  |

| Bit    | 31          | 30 | 29 | 28   | 27      | 26 | 25 | 24 |  |  |

|--------|-------------|----|----|------|---------|----|----|----|--|--|

|        | BFRX[31:24] |    |    |      |         |    |    |    |  |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |  |

|        |             |    |    |      |         |    |    |    |  |  |

| Bit    | 23          | 22 | 21 | 20   | 19      | 18 | 17 | 16 |  |  |

|        |             |    |    | BFRX | [23:16] |    |    |    |  |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |  |

|        |             |    |    |      |         |    |    |    |  |  |

| Bit    | 15          | 14 | 13 | 12   | 11      | 10 | 9  | 8  |  |  |

|        |             |    |    | BFRX | ([15:8] |    |    |    |  |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |  |

|        |             |    |    |      |         |    |    |    |  |  |

| Bit    | 7           | 6  | 5  | 4    | 3       | 2  | 1  | 0  |  |  |

|        |             |    |    | BFR  | X[7:0]  |    |    |    |  |  |

| Access | R           | R  | R  | R    | R       | R  | R  | R  |  |  |

| Reset  | 0           | 0  | 0  | 0    | 0       | 0  | 0  | 0  |  |  |

#### Bits 31:0 - BFRX[31:0] Broadcast Frames Received without Error

Broadcast frames received without error. This bit field counts the number of broadcast frames successfully received. This excludes pause frames, and is only incremented if the frame is successfully filtered and copied to memory.

#### 24.9.100 Received LPI Time

|        | Name:<br>Offset:<br>Reset:<br>Property: | RLPITI<br>0x274<br>0x00000000<br>Read-Only |    |       |          |    |    |    |

|--------|-----------------------------------------|--------------------------------------------|----|-------|----------|----|----|----|

| Bit    | 31                                      | 30                                         | 29 | 28    | 27       | 26 | 25 | 24 |

|        |                                         |                                            |    |       |          |    |    |    |

| Access |                                         |                                            |    |       |          |    |    |    |

| Reset  |                                         |                                            |    |       |          |    |    |    |

| Bit    | 23                                      | 22                                         | 21 | 20    | 19       | 18 | 17 | 16 |

|        |                                         |                                            |    | RLPIT | I[23:16] |    |    |    |

| Access | R                                       | R                                          | R  | R     | R        | R  | R  | R  |

| Reset  | 0                                       | 0                                          | 0  | 0     | 0        | 0  | 0  | 0  |

|        |                                         |                                            |    |       |          |    |    |    |

| Bit    | 15                                      | 14                                         | 13 | 12    | 11       | 10 | 9  | 8  |

|        |                                         |                                            |    | RLPIT | TI[15:8] |    |    |    |

| Access | R                                       | R                                          | R  | R     | R        | R  | R  | R  |

| Reset  | 0                                       | 0                                          | 0  | 0     | 0        | 0  | 0  | 0  |

|        |                                         |                                            |    |       |          |    |    |    |

| Bit    | 7                                       | 6                                          | 5  | 4     | 3        | 2  | 1  | 0  |

|        |                                         |                                            |    | RLPI  | TI[7:0]  |    |    |    |

| Access | R                                       | R                                          | R  | R     | R        | R  | R  | R  |

| Reset  | 0                                       | 0                                          | 0  | 0     | 0        | 0  | 0  | 0  |

|        |                                         |                                            |    |       |          |    |    |    |

#### Bits 23:0 - RLPITI[23:0] Received LPI Time

The value of this bit field increments once every 16 AHB clock cycles when the Low Power Idle Enable bit in the Network Configuration Register (NCR.LPI) is written to '1'.

Cleared on read.

### ICM - Integrity Check Monitor

#### Bits 7:4 – RDM[3:0] Region Digest Mismatch

RDM[i] is set when there is a digest comparison mismatch between the hash value of region i and the reference value located in the Hash Area.

#### Bits 3:0 - RHC[3:0] Region Hash Completed

RHC[i] is set when the ICM has completed the region with identifier i.

#### **Clock Failure Detection**

The CFD is reset only at power-on (POR). The CFD does not monitor the XOSC32K clock when the oscillator is disabled (XOSC32K.ENABLE=0).

Before starting CFD operation, the user must start and enable the safe clock source (OSCULP32K oscillator).

CFD operation is started by writing a '1' to the CFD Enable bit in the External Oscillator Control register (CFDCTRL.CFDEN). After starting or restarting the XOSC32K, the CFD does not detect failure until the start-up time has elapsed. The start-up time is configured by the Oscillator Start-Up Time in the External Multipurpose Crystal Oscillator Control register (XOSC32K.STARTUP). Once the XOSC32K Start-Up Time is elapsed, the XOSC32K clock is constantly monitored.

During a period of 4 safe clocks (monitor period), the CFD watches for a clock activity from the XOSC32K. There must be at least one rising and one falling XOSC32K clock edge during 4 safe clock periods to meet non-failure conditions. If no or insufficient activity is detected, the failure status is asserted: The Clock Failure Detector status bit in the Status register (STATUS.XOSC32KFAIL) and the Clock Failure Detector interrupt flag bit in the Interrupt Flag register (INTFLAG.XOSC32KFAIL) are set. If the XOSC32KFAIL bit in the Interrupt Enable Set register (INTENSET.XOSC32KFAIL) is set, an interrupt is generated as well. If the Event Output enable bit in the Event Control register (EVCTRL.CFDEO) is set, an output event is generated, too.

After a clock failure was issued the monitoring of the XOSC32K clock is continued, and the Clock Failure Detector status bit in the Status register (STATUS.XOSC32KFAIL) reflects the current XOSC32K activity.

#### **Clock Switch**

When a clock failure is detected, the XOSC32K clock is replaced by the safe clock in order to maintain an active clock during the XOSC32K clock failure. The safe clock source is the OSCULP32K oscillator clock. Both 32KHz and 1KHz outputs of the XOSC32K are replaced by the respective OSCULP32K 32KHz and 1KHz outputs. The safe clock source can be scaled down by a configurable prescaler to ensure that the safe clock frequency does not exceed the operating conditions selected by the application. When the XOSC32K clock is switched to the safe clock, the Clock Switch bit in the Status register (STATUS.XOSC32KSW) is set.

When the CFD has switched to the safe clock, the XOSC32K is not disabled. If desired, the application must take the necessary actions to disable the oscillator. The application must also take the necessary actions to configure the system clocks to continue normal operations. In the case the application can recover the XOSC32K, the application can switch back to the XOSC32K clock by writing a '1' to Switch Back Enable bit in the Clock Failure Control register (CFDCTRL.SWBACK). Once the XOSC32K clock is switched back, the Switch Back bit (CFDCTRL.SWBACK) is cleared by hardware.

#### Prescaler

The CFD has an internal configurable prescaler to generate the safe clock from the OSCULP32K oscillator. The prescaler size allows to scale down the OSCULP32K oscillator so the safe clock frequency is not higher than the XOSC32K clock frequency monitored by the CFD. The maximum division factor is 2.

The prescaler is applied on both outputs (32KHz and 1KHz) of the safe clock.

#### Example 29-1. Example

For an external crystal oscillator at 32KHz and the OSCULP32K frequency is 32KHz, the XOSC32K.CFDPRESC should be set to 0 for a safe clock of equal frequency.

#### 30.8.9 Value

|        | Name:<br>Offset:<br>Reset:<br>Property: | VALUE<br>0x10<br>0x00000000<br>- |    |       |         |    |    |    |

|--------|-----------------------------------------|----------------------------------|----|-------|---------|----|----|----|

| Bit    | 31                                      | 30                               | 29 | 28    | 27      | 26 | 25 | 24 |

|        |                                         |                                  |    |       |         |    |    |    |

| Access |                                         |                                  |    |       |         |    |    |    |

| Reset  |                                         |                                  |    |       |         |    |    |    |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 23                                      | 22                               | 21 | 20    | 19      | 18 | 17 | 16 |

|        |                                         |                                  |    |       | [23:16] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 15                                      | 14                               | 13 | 12    | 11      | 10 | 9  | 8  |

|        |                                         |                                  |    | VALUE | E[15:8] |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

|        |                                         |                                  |    |       |         |    |    |    |

| Bit    | 7                                       | 6                                | 5  | 4     | 3       | 2  | 1  | 0  |

|        |                                         |                                  |    | VALU  | E[7:0]  |    |    |    |

| Access | R                                       | R                                | R  | R     | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                | 0  | 0     | 0       | 0  | 0  | 0  |

Bits 23:0 - VALUE[23:0] Measurement Value Result from measurement.

#### 10.2 Nested Vector Interrupt Controller

#### 34.5.6 Events

Not applicable.

#### 34.5.7 Debug Operation

When the CPU is halted in debug mode, this peripheral will continue normal operation. If the peripheral is configured to require periodical service by the CPU through interrupts or similar, improper operation or data loss may result during debugging. This peripheral can be forced to halt operation during debugging - refer to the Debug Control (DBGCTRL) register for details.

#### **Related Links**

34.8.14 DBGCTRL

#### 34.5.8 Register Access Protection

Registers with write-access can be write-protected optionally by the peripheral access controller (PAC).

PAC Write-Protection is not available for the following registers:

- Interrupt Flag Clear and Status register (INTFLAG)

- Status register (STATUS)

- Data register (DATA)

Optional PAC Write-Protection is denoted by the "PAC Write-Protection" property in each individual register description.

Write-protection does not apply to accesses through an external debugger.

#### Related Links

27. PAC - Peripheral Access Controller

#### 34.5.9 Analog Connections

Not applicable.

#### 34.6 Functional Description

#### 34.6.1 Principle of Operation

The USART uses the following lines for data transfer:

- RxD for receiving

- TxD for transmitting

- XCK for the transmission clock in synchronous operation

USART data transfer is frame based. A serial frame consists of:

- 1 start bit

- From 5 to 9 data bits (MSB or LSB first)

- No, even or odd parity bit

- 1 or 2 stop bits

A frame starts with the start bit followed by one character of data bits. If enabled, the parity bit is inserted after the data bits and before the first stop bit. After the stop bit(s) of a frame, either the next frame can

© 2018 Microchip Technology Inc.

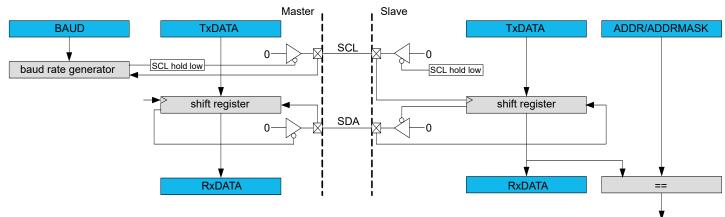

SERCOM I2C – Inter-Integrated Circuit

#### 36.3 Block Diagram

Figure 36-1. I<sup>2</sup>C Single-Master Single-Slave Interconnection

#### 36.4 Signal Description

| Signal Name | Туре        | Description                |

|-------------|-------------|----------------------------|

| PAD[0]      | Digital I/O | SDA                        |

| PAD[1]      | Digital I/O | SCL                        |

| PAD[2]      | Digital I/O | SDA_OUT (4-wire operation) |

| PAD[3]      | Digital I/O | SCL_OUT (4-wire operation) |

One signal can be mapped on several pins.

Not all the pins are  $I^2C$  pins.

#### **Related Links**

6. I/O Multiplexing and Considerations6.2.6 SERCOM I2C Configurations36.6.3.3 4-Wire Mode

#### 36.5 Product Dependencies

In order to use this peripheral, other parts of the system must be configured correctly, as described below.

#### 36.5.1 I/O Lines

In order to use the I/O lines of this peripheral, the I/O pins must be configured using the I/O Pin Controller (PORT).

When the SERCOM is used in  $I^2C$  mode, the SERCOM controls the direction and value of the I/O pins. If the receiver or transmitter is disabled, these pins can be used for other purposes.

#### **Related Links**

32. PORT - I/O Pin Controller

© 2018 Microchip Technology Inc.

### SERCOM I2C – Inter-Integrated Circuit

#### 36.10.10 Address

| ADDR               |

|--------------------|

| 0x24               |

| 0x0000             |

| Write-Synchronized |

|                    |

| Bit             | 31       | 30  | 29    | 28   | 27     | 26  | 25         | 24  |

|-----------------|----------|-----|-------|------|--------|-----|------------|-----|

| Access<br>Reset |          |     |       |      |        |     |            |     |

| Bit             | 23       | 22  | 21    | 20   | 19     | 18  | 17         | 16  |

|                 |          |     |       | LEN  | [7:0]  |     |            |     |

| Access          | R/W      | R/W | R/W   | R/W  | R/W    | R/W | R/W        | R/W |

| Reset           | 0        | 0   | 0     | 0    | 0      | 0   | 0          | 0   |

|                 |          |     |       |      |        |     |            |     |

| Bit             | 15       | 14  | 13    | 12   | 11     | 10  | 9          | 8   |

|                 | TENBITEN | HS  | LENEN |      |        |     | ADDR[10:8] |     |

| Access          | R/W      | R/W | R/W   |      |        | R/W | R/W        | R/W |

| Reset           | 0        | 0   | 0     |      |        | 0   | 0          | 0   |

|                 |          |     |       |      |        |     |            |     |

| Bit             | 7        | 6   | 5     | 4    | 3      | 2   | 1          | 0   |

|                 |          |     |       | ADDI | R[7:0] |     |            |     |

| Access          | R/W      | R/W | R/W   | R/W  | R/W    | R/W | R/W        | R/W |

| Reset           | 0        | 0   | 0     | 0    | 0      | 0   | 0          | 0   |

|                 |          |     |       |      |        |     |            |     |

#### Bits 23:16 – LEN[7:0] Transaction Length

These bits define the transaction length of a DMA and/or 32-bit transaction from 0 to 255 bytes. The Transfer Length Enable (LENEN) bit must be written to '1' in order to use DMA.

#### Bit 15 – TENBITEN Ten Bit Addressing Enable

This bit enables 10-bit addressing. This bit can be written simultaneously with ADDR to indicate a 10-bit or 7-bit address transmission.

| Value | Description                 |

|-------|-----------------------------|

| 0     | 10-bit addressing disabled. |

| 1     | 10-bit addressing enabled.  |

#### Bit 14 – HS High Speed

This bit enables High-speed mode for the current transfer from repeated START to STOP. This bit can be written simultaneously with ADDR for a high speed transfer.

| Value | Description                   |

|-------|-------------------------------|

| 0     | High-speed transfer disabled. |

| 1     | High-speed transfer enabled.  |

Bit 13 – LENEN Transfer Length Enable

### **CAN - Control Area Network**

#### Bit 2 – ASM Restricted Operation Mode

This bit field is write-restricted.

Writing a 0 to this field is always allowed.

Writing a 1 to this field is only allowed if bit fields CCE = 1 and INIT = 1.

| Value | Description                       |

|-------|-----------------------------------|

| 0     | Normal CAN operation.             |

| 1     | Restricted Operation Mode active. |

#### Bit 1 – CCE Configuration Change Enable

This bit field is write-restricted and only writable if bit field INIT = 1.

| V | alue | Description                                                                              |

|---|------|------------------------------------------------------------------------------------------|

| 0 |      | The CPU has no write access to the protected configuration registers.                    |

| 1 |      | The CPU has write access to the protected configuration registers (while CCCR.INIT = 1). |

#### Bit 0 - INIT Initialization

Due to the synchronization mechanism between the two clock domains, there may be a delay until the value written to INIT can be read back. The programmer has to assure that the previous value written to INIT has been accepted by reading INIT before setting INIT to a new value.

| Value | Description                |

|-------|----------------------------|

| 0     | Normal Operation.          |

| 1     | Initialization is started. |

SD/MMC Host Controller ...

| Offset     | Name     | Bit Pos. |     |          |         |           |          |         |           |

|------------|----------|----------|-----|----------|---------|-----------|----------|---------|-----------|

|            |          | 7:0      |     |          | ADMA    | SA[7:0]   |          |         |           |

|            |          | 15:8     |     |          | ADMAS   | SA[15:8]  |          |         |           |

| 0x58       | ASARx    | 23:16    |     |          |         | A[23:16]  |          |         |           |

|            |          | 31:24    |     |          |         | A[31:24]  |          |         |           |

| 0x5C       |          | 01121    |     |          |         | , (01.21) |          |         |           |

|            | Reserved |          |     |          |         |           |          |         |           |

| <br>0x5F   | Reserved |          |     |          |         |           |          |         |           |

| 0,01       |          | 7:0      |     |          | SDCI KE | SEL[7:0]  |          |         |           |

| 0x60       | PVRx0    |          |     |          | SDCLKF  |           |          |         |           |

|            |          | 15:8     |     |          | 000110  |           | CLKGSEL  | SDCLKF  | SEL[9:8]  |

| 0x62       | PVRx1    | 7:0      |     |          | SDCLKF  | SEL[7:0]  |          |         |           |

|            |          | 15:8     |     |          |         |           | CLKGSEL  | SDCLKF  | SEL[9:8]  |

| 0x64       | PVRx2    | 7:0      |     |          | SDCLKF  | SEL[7:0]  |          |         |           |

|            |          | 15:8     |     |          |         |           | CLKGSEL  | SDCLKF  | SEL[9:8]  |

| 0x66       | PVRx3    | 7:0      |     |          | SDCLKF  | SEL[7:0]  |          |         |           |

| 0,00       | L ALY 2  | 15:8     |     |          |         |           | CLKGSEL  | SDCLKF  | SEL[9:8]  |

|            |          | 7:0      |     |          | SDCLKF  | SEL[7:0]  |          |         |           |

| 0x68       | PVRx4    | 15:8     |     |          |         |           | CLKGSEL  | SDCLKF  | SEL[9:8]  |

|            |          | 7:0      |     |          | SDCLKF  | SEL[7:0]  |          |         |           |

| 0x6A       | PVRx5    | 15:8     |     |          |         |           | CLKGSEL  | SDCLKF  | SEL[9:8]  |

|            |          | 7:0      |     |          | SDCI KE | SEL[7:0]  |          |         |           |

| 0x6C       | PVRx6    | 15:8     |     |          | OBOLIN  |           | CLKGSEL  | SDCLKF  | SEI 10-81 |

|            |          | 7:0      |     |          | SDCI KE |           | OLINOOLL | ODOLIN  | 0000      |

| 0x6E       | PVRx7    |          |     |          | SDCLKF  | SEL[7:0]  |          |         |           |

|            |          | 15:8     |     |          |         |           | CLKGSEL  | SDCLKF  | SEL[9:8]  |

| 0x70       |          |          |     |          |         |           |          |         |           |

|            | Reserved |          |     |          |         |           |          |         |           |

| 0xFB       |          |          |     |          |         |           |          |         |           |

| 0xFC       | SISR     | 7:0      |     |          | INTSS   | SL[7:0]   |          |         |           |

|            |          | 15:8     |     |          |         |           |          |         |           |

| 0xFE       | HCVR     | 7:0      |     |          | SVE     | R[7:0]    |          |         |           |

| UNIL       | novix    | 15:8     |     |          | VVE     | R[7:0]    |          |         |           |

| 0x0100     |          |          |     |          |         |           |          |         |           |

|            | Reserved |          |     |          |         |           |          |         |           |

| 0x01FF     |          |          |     |          |         |           |          |         |           |

|            |          | 7:0      |     |          |         |           | HDATL    | .L[3:0] |           |

|            |          | 15:8     |     |          |         |           |          |         |           |

| 0x0200     | APSR     | 23:16    |     |          |         |           |          |         |           |

|            |          | 31:24    |     |          |         |           |          |         |           |

| 0x0204     | MC1R     | 7:0      | FCD | BOOTA    |         |           |          | CMDT    | YP[1:0]   |

| 0x0204     | MC2R     | 7:0      |     |          |         |           |          | ABOOT   | SRESP     |

| 0x0205     | WOZIX    | 1.0      |     |          |         |           |          | 10001   | UNLOF     |

|            |          |          |     |          |         |           |          |         |           |

| <br>0x0207 | Reserved |          |     |          |         |           |          |         |           |

| 0x0207     |          | 7.0      |     | DAVERSIS |         |           |          |         | x[4.0]    |

|            |          | 7:0      |     | B1KBDIS  | HNBRDIS |           |          | BMA     | <[1:0]    |

| 0x0208     | ACR      | 15:8     |     |          |         |           |          |         |           |

|            |          | 23:16    |     |          |         |           |          |         |           |

|            |          | 31:24    |     |          |         |           |          |         |           |

#### AES – Advanced Encryption Standard

#### 42.8.2 Control B

| Name:     | CTRLB                |

|-----------|----------------------|

| Offset:   | 0x04                 |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7 | 6 | 5 | 4 | 3     | 2   | 1      | 0     |

|--------|---|---|---|---|-------|-----|--------|-------|

|        |   |   |   |   | GFMUL | EOM | NEWMSG | START |

| Access |   |   |   |   | R/W   | R/W | R/W    | R/W   |

| Reset  |   |   |   |   | 0     | 0   | 0      | 0     |

Bit 3 – GFMUL GF Multiplication

This bit is applicable only to GCM mode.

| Value | Description                                                                                          |

|-------|------------------------------------------------------------------------------------------------------|

| 0     | No action                                                                                            |

| 1     | Setting this bit calculates GF multiplication with data buffer content and hashkey register content. |

#### Bit 2 – EOM End of Message

This bit is applicable only to GCM mode.

| Value | Description                                                   |  |

|-------|---------------------------------------------------------------|--|

| 0     | No action                                                     |  |

| 1     | Setting this bit generates final GHASH value for the message. |  |

#### Bit 1 - NEWMSG New Message

This bit is used in cipher block chaining (CBC), cipher feedback (CFB) and output feedback (OFB), counter (CTR) modes to indicate the hardware to use Initialization vector for encrypting the first block of message.

| Value | Description                                                    |  |

|-------|----------------------------------------------------------------|--|

| 0     | No action                                                      |  |

| 1     | Setting this bit indicates start of new message to the module. |  |

#### Bit 0 – START Start Encryption/Decryption

| Value | Description                                   |  |

|-------|-----------------------------------------------|--|

| 0     | No action                                     |  |

| 1     | Start encryption / decryption in manual mode. |  |

### Public Key Cryptography Controller (PUKCC)

| Modular Input Dynamic<br>Reduction<br>Form                     |                                        | Result Dynamic                                        | Comments                                                                                          |

|----------------------------------------------------------------|----------------------------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| GF(2n): Input < ((P[x]) <sup>2</sup> ) *<br>(X <sup>32</sup> ) |                                        |                                                       |                                                                                                   |

| Normalized                                                     | InputLength < NLength<br>+ 4 bytes     | GF(p): 0 ≤ Res < N<br>GF(2 <sup>n</sup> ): Res < P[X] | The correction step does not<br>runs in constant time. Needs a<br>precomputed constant.           |

|                                                                |                                        |                                                       | The Normalize function cannot<br>be applied to the product of two<br>numbers of length u2NLength. |

| Using<br>Euclidean<br>division                                 | InputLength < 2 *<br>NLength + 4 bytes | GF(p): 0 ≤ Res < N<br>GF(2 <sup>n</sup> ): Res < P[X] | Does not need any precomputed constant.                                                           |

To be able to use these modular reduction services (except the Euclidean division), first the implementer shall call the setup service, providing the modulus as well as one free memory space for the constant (this constant is used to speed up the modular reduction). In most commands (except the modular exponentiation), the quotient is stored in the high order bytes of the number to be reduced, using only eight bytes more than the maximum size of the number to be reduced.

The following rules must be respected to ensure the modular reduction services function correctly:

- The numbers to be reduced can have any significant length, given the fact it CANNOT BE GREATER than 2\*u2ModLength + 4 bytes.

- The modulus SHALL ALWAYS HAVE a significant length of <u2ModLength> bytes. The modulus must be provided as a <u2ModLength + 4> bytes long number, padded on the most significant side with a 32-bit word cleared to zero. Not respecting this rule leads to unexpected and wrong results from the modular reduction.

- The normalization operation ALWAYS performs a modular reduction step, and will therefore have the same memory usage as this one.

- The very first operation before any modular operation SHALL BE a modular setup.

#### 43.3.5.1 Modular Reduction

#### 43.3.5.1.1 Purpose

This service is used to perform the various steps necessary to perform a modular reduction and accepts as input numbers in GF(p) or polynomials in  $GF(2^n)$ .

The available options for this service are:

- Work in the GF(2<sup>n</sup>) or in the standard integer arithmetic field GF(p)

- Operation is the generation of the reduction constant.

- Operation is a Modular Reduction.

- Operation is a Normalization.

#### 43.3.5.1.2 How to Use the Service

#### 43.3.5.1.3 Description

This service performs one of the following operations:

#### DAC – Digital-to-Analog Converter

#### 47.8.1 Control A

| Name:     | CTRLA                                    |

|-----------|------------------------------------------|

| Offset:   | 0x00                                     |

| Reset:    | 0x00                                     |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1      | 0     |

|--------|---|---|---|---|---|---|--------|-------|

|        |   |   |   |   |   |   | ENABLE | SWRST |

| Access |   |   |   |   |   |   | R/W    | R/W   |

| Reset  |   |   |   |   |   |   | 0      | 0     |

#### Bit 1 – ENABLE Enable DAC Controller

Due to synchronization there is delay from writing CTRLA.ENABLE until the peripheral is enabled/ disabled. The value written to CTRLA.ENABLE will read back immediately and the corresponding bit in the Synchronization Busy register (SYNCBUSY.ENABLE) will be set. SYNCBUSY.ENABLE will be cleared when the operation is complete.

| Value | Description                 |  |

|-------|-----------------------------|--|

| 0     | The peripheral is disabled. |  |

| 1     | The peripheral is enabled.  |  |

#### Bit 0 – SWRST Software Reset

Writing '0' to this bit has no effect.

Writing '1' to this bit resets all registers in the DAC to their initial state, and the DAC will be disabled.

Writing a '1' to CTRLA.SWRST will always take precedence, meaning that all other writes in the same write-operation will be discarded.

Due to synchronization there is a delay from writing CTRLA.SWRST until the reset is complete. CTRLA.SWRST and SYNCBUSY.SWRST will both be cleared when the reset is complete.

| Value | Description                          |  |

|-------|--------------------------------------|--|

| 0     | There is no reset operation ongoing. |  |

| 1     | The reset operation is ongoing.      |  |

**PDEC – Position Decoder**

| Value                              | Description                     |  |

|------------------------------------|---------------------------------|--|

| 0 The Error interrupt is disabled. |                                 |  |

| 1                                  | The Error interrupt is enabled. |  |

Bit 0 – OVF Overflow/Underflow Interrupt Disable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Overflow Interrupt Disable/Enable bit, which disables the Overflow interrupt.

|                                       | Value | Description                         |  |

|---------------------------------------|-------|-------------------------------------|--|

| 0 The Overflow interrupt is disabled. |       | The Overflow interrupt is disabled. |  |

|                                       | 1     | The Overflow interrupt is enabled.  |  |