#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 120MHz                                                                                |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 51                                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 128K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-VFQFN Exposed Pad                                                                  |

| Supplier Device Package    | 64-QFN (9x9)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame53j18a-mu             |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 44. TRN  | IG – True Random Number Generator | 1613 |

|----------|-----------------------------------|------|

| 44.1.    | Overview                          | 1613 |

| 44.2.    | Features                          | 1613 |

| 44.3.    | Block Diagram                     |      |

| 44.4.    | Signal Description                |      |

| 44.5.    | Product Dependencies              |      |

| 44.6.    | Functional Description            | 1615 |

| 44.7.    | Register Summary                  | 1617 |

| 44.8.    | Register Description              |      |

|          | C – Analog-to-Digital Converter   |      |

| 45.1.    | Overview                          |      |

| 45.2.    | Features                          |      |

| 45.3.    | Block Diagram                     |      |

| 45.4.    | Signal Description                |      |

| 45.5.    | Product Dependencies              |      |

|          | Functional Description            |      |

|          | Register Summary                  |      |

| 45.8.    | Register Description              |      |

| 46. AC - | - Analog Comparators              | 1679 |

| 46.1.    | Overview                          | 1679 |

| 46.2.    | Features                          | 1679 |

| 46.3.    | Block Diagram                     |      |

| 46.4.    | Signal Description                | 1680 |

| 46.5.    | Product Dependencies              |      |

| 46.6.    | Functional Description            | 1682 |

| 46.7.    | Register Summary                  | 1692 |

| 46.8.    | Register Description              |      |

| 47. DAC  | C – Digital-to-Analog Converter   |      |

| 47.1.    | Overview                          |      |

|          | Features                          |      |

| 47.3.    | Block Diagram                     |      |

| 47.4.    | Signal Description                | 1712 |

| 47.5.    | Product Dependencies              |      |

| 47.6.    | Functional Description            | 1714 |

| 47.7.    | Register Summary                  | 1724 |

| 47.8.    | Register Description              | 1724 |

| 48. TC - | - Timer/Counter                   |      |

| 48.1.    | Overview                          | 1750 |

| 48.2.    | Features                          |      |

| 48.3.    | Block Diagram                     |      |

|          | Signal Description                |      |

| 48.5.    | Product Dependencies              |      |

| 48.6.    | Functional Description            | 1753 |

## 18.8.3 Interrupt Enable Clear

Name:INTENCLROffset:0x04Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0        |

|--------|---|---|---|---|---|---|---|----------|

|        |   |   |   |   |   |   |   | SLEEPRDY |

| Access |   |   |   |   |   |   |   | W        |

| Reset  |   |   |   |   |   |   |   | 0        |

# **Bit 0 – SLEEPRDY** Sleep Mode Entry Ready Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Sleep Mode Entry Ready Interrupt Enable bit and the corresponding interrupt request.

| Value | Description                                                                            |

|-------|----------------------------------------------------------------------------------------|

| 0     | The Sleep Mode Entry Ready interrupt is disabled.                                      |

| 1     | The Sleep Mode Entry Ready interrupt is enabled and will generate an interrupt request |

|       | when the Sleep Mode Entry Ready Interrupt Flag is set.                                 |

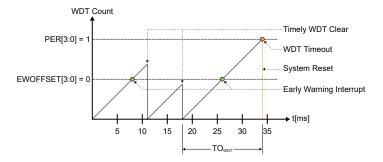

WDT will issue a system reset if a time-out occurs. This can be prevented by clearing the WDT at any time during the time-out period.

The WDT is cleared and a new WDT time-out period is started by writing 0xA5 to the Clear register (CLEAR). Writing any other value than 0xA5 to CLEAR will issue an immediate system reset.

There are 12 possible WDT time-out (TO<sub>WDT</sub>) periods, selectable from 8ms to 16s.

By default, the early warning interrupt is disabled. If it is desired, the Early Warning Interrupt Enable bit in the Interrupt Enable register (INTENSET.EW) must be written to '1'. The Early Warning Interrupt is disabled again by writing a '1' to the Early Warning Interrupt bit in the Interrupt Enable Clear register (INTENCLR.EW).

If the Early Warning Interrupt is enabled, an interrupt is generated prior to a WDT time-out condition. In Normal mode, the Early Warning Offset bits in the Early Warning Interrupt Control register, EWCTRL.EWOFFSET, define the time when the early warning interrupt occurs. The Normal mode operation is illustrated in the figure Normal-Mode Operation.

# Figure 20-2. Normal-Mode Operation

# 20.6.2.5 Window Mode

In Window mode operation, the WDT uses two different time specifications: the WDT can only be cleared by writing 0xA5 to the CLEAR register *after* the closed window time-out period ( $TO_{WDTW}$ ), during the subsequent Normal time-out period ( $TO_{WDT}$ ). If the WDT is cleared before the time window opens (before  $TO_{WDTW}$  is over), the WDT will issue a system reset.

Both parameters  $TO_{WDTW}$  and  $TO_{WDT}$  are periods in a range from 8ms to 16s, so the total duration of the WDT time-out period is the sum of the two parameters.

The closed window period is defined by the Window Period bits in the Configuration register (CONFIG.WINDOW), and the open window period is defined by the Period bits in the Configuration register (CONFIG.PER).

By default, the Early Warning interrupt is disabled. If it is desired, the Early Warning Interrupt Enable bit in the Interrupt Enable register (INTENSET.EW) must be written to '1'. The Early Warning Interrupt is disabled again by writing a '1' to the Early Warning Interrupt bit in the Interrupt Enable Clear (INTENCLR.EW) register.

If the Early Warning interrupt is enabled in Window mode, the interrupt is generated at the start of the open window period, i.e. after TO<sub>WDTW</sub>. The Window mode operation is illustrated in figure Window-Mode Operation.

# 21.10.15 Timestamp

|        | Name:<br>Offset:<br>Reset:<br>Property: | TIMESTAMP<br>0x64<br>0x0000<br>Read-Only |    |      |         |    |    |    |

|--------|-----------------------------------------|------------------------------------------|----|------|---------|----|----|----|

| Bit    | 31                                      | 30                                       | 29 | 28   | 27      | 26 | 25 | 24 |

|        |                                         |                                          |    |      |         |    |    |    |

| Access |                                         |                                          |    |      |         |    |    |    |

| Reset  |                                         |                                          |    |      |         |    |    |    |

| Bit    | 23                                      | 22                                       | 21 | 20   | 19      | 18 | 17 | 16 |

| Dit    | 23                                      |                                          | 21 | 20   | 19      | 10 | 17 | 10 |

| Access |                                         |                                          |    |      |         |    |    |    |

| Reset  |                                         |                                          |    |      |         |    |    |    |

|        |                                         |                                          |    |      |         |    |    |    |

| Bit    | 15                                      | 14                                       | 13 | 12   | 11      | 10 | 9  | 8  |

|        |                                         |                                          |    | COUN | T[15:8] |    |    |    |

| Access | R                                       | R                                        | R  | R    | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                        | 0  | 0    | 0       | 0  | 0  | 0  |

|        |                                         |                                          |    |      |         |    |    |    |

| Bit    | 7                                       | 6                                        | 5  | 4    | 3       | 2  | 1  | 0  |

|        |                                         |                                          |    |      | IT[7:0] |    |    |    |

| Access | R                                       | R                                        | R  | R    | R       | R  | R  | R  |

| Reset  | 0                                       | 0                                        | 0  | 0    | 0       | 0  | 0  | 0  |

Bits 15:0 – COUNT[15:0] Count Timestamp Value

The 16-bit value of COUNT is captured by the TIMESTAMP when a tamper condition occurs.

# **DMAC – Direct Memory Access Controller**

|        | Offset:<br>Property: | 0x08<br>-      |                  |            |            |              |            |        |

|--------|----------------------|----------------|------------------|------------|------------|--------------|------------|--------|

|        | The DSTAD            | DR register of | fset is relative | to (BASEAD | DR or WRBA | .DDR) + Char | nel Number | * 0x10 |

| Bit    | 31                   | 30             | 29               | 28         | 27         | 26           | 25         | 24     |

|        |                      |                |                  | DSTADE     | DR[31:24]  |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

| Bit    | 23                   | 22             | 21               | 20         | 19         | 18           | 17         | 16     |

|        |                      |                |                  | DSTADE     | DR[23:16]  |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

|        |                      |                |                  |            |            |              |            |        |

| Bit    | 15                   | 14             | 13               | 12         | 11         | 10           | 9          | 8      |

|        |                      |                |                  | DSTADI     | DR[15:8]   |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

|        | _                    |                | _                |            |            |              |            |        |

| Bit    | 7                    | 6              | 5                | 4          | 3          | 2            | 1          | 0      |

|        |                      |                |                  | DSTAD      | DR[7:0]    |              |            |        |

| Access |                      |                |                  |            |            |              |            |        |

| Reset  |                      |                |                  |            |            |              |            |        |

## 22.10.4 Block Transfer Destination Address

DSTADDR

Name:

# Bits 31:0 – DSTADDR[31:0] Transfer Destination Address

This bit group holds the destination address corresponding to the last beat transfer address in the block transfer.

|        | Name:<br>Offset:<br>Reset:<br>Property: | NSC<br>0x0DC<br>0x00000000<br>- |     |       |          |          |          |     |

|--------|-----------------------------------------|---------------------------------|-----|-------|----------|----------|----------|-----|

| Bit    | 31                                      | 30                              | 29  | 28    | 27       | 26       | 25       | 24  |

|        |                                         |                                 |     |       |          |          |          |     |

| Access |                                         |                                 |     |       |          |          |          |     |

| Reset  |                                         |                                 |     |       |          |          |          |     |

|        |                                         |                                 |     |       |          |          |          |     |

| Bit    | 23                                      | 22                              | 21  | 20    | 19       | 18       | 17       | 16  |

|        |                                         |                                 |     |       | NANOSE   | C[21:16] |          |     |

| Access |                                         |                                 | R/W | R/W   | R/W      | R/W      | R/W      | R/W |

| Reset  |                                         |                                 | 0   | 0     | 0        | 0        | 0        | 0   |

|        |                                         |                                 |     |       |          |          |          |     |

| Bit    | 15                                      | 14                              | 13  | 12    | 11       | 10       | 9        | 8   |

|        |                                         |                                 |     | NANOS | EC[15:8] |          |          |     |

| Access | R/W                                     | R/W                             | R/W | R/W   | R/W      | R/W      | R/W      | R/W |

| Reset  | 0                                       | 0                               | 0   | 0     | 0        | 0        | 0        | 0   |

|        |                                         |                                 |     |       |          |          |          |     |

| Bit    | 7                                       | 6                               | 5   | 4     | 3        | 2        | 1        | 0   |

|        |                                         |                                 |     | NANOS | EC[7:0]  |          | <u>.</u> |     |

| Access | R/W                                     | R/W                             | R/W | R/W   | R/W      | R/W      | R/W      | R/W |

| Reset  | 0                                       | 0                               | 0   | 0     | 0        | 0        | 0        | 0   |

|        |                                         |                                 |     |       |          |          |          |     |

# 24.9.31 GMAC 1588 Timer Nanosecond Comparison Register

Bits 21:0 – NANOSEC[21:0] 1588 Timer Nanosecond Comparison Value

Value is compared to the bits [45:24] of the TSU timer count value (upper 22 bits of nanosecond value).

## 25.8.4 Interrupt Enable Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x0C                 |

| Reset:    | 0x0000               |

| Property: | PAC Write-Protection |

| Bit    | 15   | 14   | 13    | 12    | 11    | 10     | 9       | 8        |

|--------|------|------|-------|-------|-------|--------|---------|----------|

|        |      |      |       |       |       | SEEWRC | SEESOVF | SEESFULL |

| Access |      |      |       |       |       | R/W    | R/W     | R/W      |

| Reset  |      |      |       |       |       | 0      | 0       | 0        |

|        |      |      |       |       |       |        |         |          |

| Bit    | 7    | 6    | 5     | 4     | 3     | 2      | 1       | 0        |

|        | SUSP | NVME | ECCDE | ECCSE | LOCKE | PROGE  | ADDRE   | DONE     |

| Access | R/W  | R/W  | R/W   | R/W   | R/W   | R/W    | R/W     | R/W      |

| Reset  | 0    | 0    | 0     | 0     | 0     | 0      | 0       | 0        |

**Bit 10 – SEEWRC** SEE Write Completed Interrupt Clear Writing a zero to this bit has no effect.

Writing a '1' to this bit clears the SEEWRC interrupt enable.

This bit will read as the current value of the SEEWRC interrupt enable.

**Bit 9 – SEESOVF** Active SEES Overflow Interrupt Clear Writing a zero to this bit has no effect.

Writing a '1' to this bit clears the SEESOVF interrupt enable.

This bit will read as the current value of the SEESOVF interrupt enable.

**Bit 8 – SEESFULL** Active SEES Full Interrupt Clear Writing a zero to this bit has no effect.

Writing a '1' to this bit clears the SEESFULL interrupt enable.

This bit will read as the current value of the SEESFULL interrupt enable.

**Bit 7 – SUSP** Suspended Write Or Erase Interrupt Clear Writing a zero to this bit has no effect.

Writing a '1' to this bit clears the SUSP interrupt enable.

This bit will read as the current value of the SUSP interrupt enable.

# Bit 6 – NVME NVM Error Interrupt Clear

Writing a zero to this bit has no effect.

Writing a '1' to this bit clears the NVME interrupt enable.

This bit will read as the current value of the NVME interrupt enable.

**Bit 5 – ECCDE** ECC Dual Error Interrupt Clear Writing a zero to this bit has no effect.

© 2018 Microchip Technology Inc.

# OSC32KCTRL – 32KHz Oscillators Controller

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x08<br>0x00000000<br>- |    |    |    |             |    |            |

|--------|-----------------------------------------|------------------------------------|----|----|----|-------------|----|------------|

| Bit    | 31                                      | 30                                 | 29 | 28 | 27 | 26          | 25 | 24         |

|        |                                         |                                    |    |    |    |             |    |            |

| Access |                                         | -                                  |    |    |    |             |    |            |

| Reset  |                                         |                                    |    |    |    |             |    |            |

|        |                                         |                                    |    |    |    |             |    |            |

| Bit    | 23                                      | 22                                 | 21 | 20 | 19 | 18          | 17 | 16         |

|        |                                         |                                    |    |    |    |             |    |            |

| Access |                                         |                                    |    |    |    |             |    |            |

| Reset  |                                         |                                    |    |    |    |             |    |            |

|        |                                         |                                    | 10 | 10 |    | 10          |    |            |

| Bit    | 15                                      | 14                                 | 13 | 12 | 11 | 10          | 9  | 8          |

|        |                                         |                                    |    |    |    |             |    |            |

| Access |                                         |                                    |    |    |    |             |    |            |

| Reset  |                                         |                                    |    |    |    |             |    |            |

| Bit    | 7                                       | 6                                  | 5  | 4  | 3  | 2           | 1  | 0          |

| Dit    | •                                       | -                                  | -  |    | -  | XOSC32KFAIL | •  | XOSC32KRDY |

| Access |                                         |                                    |    |    |    | R/W         |    | R/W        |

| Reset  |                                         |                                    |    |    |    | 0           |    | 0          |

### 29.8.3 Interrupt Flag Status and Clear

Bit 2 – XOSC32KFAIL XOSC32K Clock Failure Detector

This flag is cleared by writing a '1' to it.

This flag is set on a zero-to-one transition of the XOSC32K Clock Failure Detection bit in the Status register (STATUS.XOSC32KFAIL) and will generate an interrupt request if INTENSET.XOSC32KFAIL is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the XOSC32K Clock Failure Detection flag.

# Bit 0 – XOSC32KRDY XOSC32K Ready

This flag is cleared by writing a '1' to it.

This flag is set by a zero-to-one transition of the XOSC32K Ready bit in the Status register (STATUS.XOSC32KRDY), and will generate an interrupt request if INTENSET.XOSC32KRDY=1.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the XOSC32K Ready interrupt flag.

# EVSYS – Event System

| Value       | Name         | Description         |  |  |

|-------------|--------------|---------------------|--|--|

| 0x62        | PDEC_ERR     | PDEC Error          |  |  |

| 0x63        | PDEC_DIR     | PDEC Direction      |  |  |

| 0x64        | PDEC_VLC     | PDEC VLC            |  |  |

| 0x65 - 0x66 | PDEC_MCx     | PDEC MCx x=01       |  |  |

| 0x67        | ADC0_RESRDY  | ADC0 RESRDY         |  |  |

| 0x68        | ADC0_WINMON  | ADC0 Window Monitor |  |  |

| 0x69        | ADC1_RESRDY  | ADC1 RESRDY         |  |  |

| 0x6A        | ADC1_WINMON  | ADC1 Window Monitor |  |  |

| 0x6B - 0x6C | AC_COMPx     | AC Comparator, x=01 |  |  |

| 0x6D        | AC_WIN       | AC0 Window          |  |  |

| 0x6E - 0x6F | DAC_EMPTYx   | DAC empty, x=01     |  |  |

| 0x70 - 0x71 | DAC_RESRDYx  | DAC RSRDY, x=01     |  |  |

| 0x72        | GMAC_TSU_CMP | GMAC Timestamp CMP  |  |  |

| 0x73        | TRNG_READY   | TRNG ready          |  |  |

| 0x74 - 0x77 | CCL_LUTOUT   | CCL LUTOUT          |  |  |

- External clocking, CTRLA.RUNSTDBY=1: The Receive Complete interrupt(s) can wake up the device.

- Internal clocking, CTRLA.RUNSTDBY=0: Internal clock will be disabled, after any ongoing transfer was completed. The Receive Complete interrupt(s) can wake up the device.

- External clocking, CTRLA.RUNSTDBY=0: External clock will be disconnected, after any ongoing transfer was completed. All reception will be dropped.

# 34.6.6 Synchronization

Due to asynchronicity between the main clock domain and the peripheral clock domains, some registers need to be synchronized when written or read.

The following bits are synchronized when written:

- Software Reset bit in the CTRLA register (CTRLA.SWRST)

- Enable bit in the CTRLA register (CTRLA.ENABLE)

- Receiver Enable bit in the CTRLB register (CTRLB.RXEN)

- Transmitter Enable bit in the Control B register (CTRLB.TXEN)

**Note:** CTRLB.RXEN is write-synchronized somewhat differently. See also 34.8.2 CTRLB for details.

Required write-synchronization is denoted by the "Write-Synchronized" property in the register description.

# SAMD5x/E5x Family Data Sheet SERCOM SPI – SERCOM Serial Peripheral Interface

### This bit is not synchronized.

| Mode | CPOL | СРНА | Leading Edge    | Trailing Edge   |

|------|------|------|-----------------|-----------------|

| 0x0  | 0    | 0    | Rising, sample  | Falling, change |

| 0x1  | 0    | 1    | Rising, change  | Falling, sample |

| 0x2  | 1    | 0    | Falling, sample | Rising, change  |

| 0x3  | 1    | 1    | Falling, change | Rising, sample  |

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | The data is sampled on a leading SCK edge and changed on a trailing SCK edge. |

| 1     | The data is sampled on a trailing SCK edge and changed on a leading SCK edge. |

# Bits 27:24 - FORM[3:0] Frame Format

This bit field selects the various frame formats supported by the SPI in slave mode. When the 'SPI frame with address' format is selected, the first byte received is checked against the ADDR register.

| FORM[3:0] | Name     | Description            |

|-----------|----------|------------------------|

| 0x0       | SPI      | SPI frame              |

| 0x1       | -        | Reserved               |

| 0x2       | SPI_ADDR | SPI frame with address |

| 0x3-0xF   | -        | Reserved               |

# Bits 21:20 - DIPO[1:0] Data In Pinout

These bits define the data in (DI) pad configurations.

In master operation, DI is MISO.

In slave operation, DI is MOSI.

These bits are not synchronized.

| DIPO[1:0] | Name   | Description                         |

|-----------|--------|-------------------------------------|

| 0x0       | PAD[0] | SERCOM PAD[0] is used as data input |

| 0x1       | PAD[1] | SERCOM PAD[1] is used as data input |

| 0x2       | PAD[2] | SERCOM PAD[2] is used as data input |

| 0x3       | PAD[3] | SERCOM PAD[3] is used as data input |

# Bits 17:16 - DOPO[1:0] Data Out Pinout

This bit defines the available pad configurations for data out (DO) and the serial clock (SCK). In slave operation, the slave select line  $(\overline{SS})$  is controlled by DOPO, while in master operation the  $\overline{SS}$  line is controlled by the port configuration.

In master operation, DO is MOSI.

In slave operation, DO is MISO.

These bits are not synchronized.

# 37. QSPI - Quad Serial Peripheral Interface

# 37.1 Overview

The Quad SPI Interface (QSPI) circuit is a synchronous serial data link that provides communication with external devices in Master mode.

The QSPI can be used in "SPI mode" to interface serial peripherals, such as ADCs, DACs, LCD controllers and sensors, or in "Serial Memory Mode" to interface serial Flash memories.

The QSPI allows the system to execute code directly from a serial Flash memory (XIP) without code shadowing to SRAM. The serial Flash memory mapping is seen in the system as other memories (ROM, SRAM, DRAM, embedded Flash memories, etc.,).

With the support of the quad-SPI protocol, the QSPI allows the system to use high performance serial Flash memories which are small and inexpensive, in place of larger and more expensive parallel Flash memories.

# 37.2 Features

- Master SPI Interface:

- Programmable Clock Phase and Clock Polarity

- Programmable transfer delays between consecutive transfers, between clock and data, between deactivation and activation of chip select (CS)

- SPI Mode:

- To use serial peripherals, such as ADCs, DACs, LCD controllers, CAN controllers, and sensors

- 8-bit, 16-bit, or 32-bit programmable data length

- Serial Memory Mode:

- To use serial Flash memories operating in single-bit SPI, Dual SPI and Quad SPI

- Supports "execute in place" (XIP). The system can execute code directly from a Serial Flash memory.

- Flexible Instruction register, to be compatible with all Serial Flash memories

- 32-bit Address mode (default is 24-bit address) to support Serial Flash memories larger than 128 Mbit

- Continuous Read mode

- Scrambling/Unscrambling "On-the-Fly"

- Double data rate support

- Connection to DMA Channel Capabilities Optimizes Data Transfers

- One channel for the receiver and one channel for the transmitter

- Register Write Protection

# 38.7 Register Summary

The register mapping depends on the Operating Mode field in the Control A register (CTRLA.MODE). The register summary is detailed below.

# 38.7.1 Common Device Summary

| Offset | Name      | Bit Pos. |                         |                |  |       |              |         |        |        |

|--------|-----------|----------|-------------------------|----------------|--|-------|--------------|---------|--------|--------|

| 0x00   | CTRLA     | 7:0      | MODE                    |                |  |       |              | RUNSTBY | ENABLE | SWRST  |

| 0x01   | Reserved  |          |                         |                |  |       |              |         |        |        |

| 0x02   | SYNCBUSY  | 7:0      |                         |                |  |       |              |         | ENABLE | SWRST  |

| 0x03   | QOSCTRL   | 7:0      |                         |                |  |       | DQO          | S[1:0]  | CQO    | S[1:0] |

| 0x0D   | FSMSTATUS | 7:0      |                         |                |  |       | FSMSTATE[6:0 | )]      |        |        |

| 0x24   |           | 7:0      |                         |                |  | DESCA | ADD[7:0]     |         |        |        |

| 0x25   | DESCADD   | 15:8     |                         | DESCADD[15:8]  |  |       |              |         |        |        |

| 0x26   | DESCADD   | 23:16    |                         | DESCADD[23:16] |  |       |              |         |        |        |

| 0x27   |           | 31:24    | DESCADD[31:24]          |                |  |       |              |         |        |        |

| 0x28   | PADCAL    | 7:0      | TRANSN[1:0] TRANSP[4:0] |                |  |       |              |         |        |        |

| 0x29   | FADCAL    | 15:8     | TRIM[2:0] TRANSN[4:2]   |                |  |       |              |         |        |        |

# 38.7.2 Device Summary

# Table 38-1. General Device Registers

| Offset | Name     | Bit Pos. |         |           |       |        |           |          |         |         |

|--------|----------|----------|---------|-----------|-------|--------|-----------|----------|---------|---------|

| 0x04   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x05   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x06   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x07   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x08   | CTRLB    | 7:0      |         |           |       | NREPLY | SPDCC     | DNF[1:0] | UPRSM   | DETACH  |

| 0x09   | CIREB    | 15:8     |         |           |       |        | LPMHD     | SK[1:0]  | GNAK    |         |

| 0x0A   | DADD     |          | ADDEN   |           |       |        | DADD[6:0] |          |         |         |

| 0x0B   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x0C   | STATUS   | 7:0      | LINESTA | ATE[1:0]  |       |        | SPEE      | D[1:0]   |         |         |

| 0x0E   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x0F   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x10   | FNUM     | 7:0      |         | FNUM[4:0] |       |        |           |          |         |         |

| 0x11   | FNUM     | 15:8     | FNCERR  |           |       |        | FNUM      | JM[10:5] |         |         |

| 0x12   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x14   | INTENCLR | 7:0      | RAMACER | UPRSM     | EORSM | WAKEUP | EORST     | SOF      |         | SUSPEND |

| 0x15   | INTENCLR | 15:8     |         |           |       |        |           |          | LPMSUSP | LPMNYET |

| 0x16   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x17   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x18   |          | 7:0      | RAMACER | UPRSM     | EORSM | WAKEUP | EORST     | SOF      |         | SUSPEND |

| 0x19   | x19      | 15:8     |         |           |       |        |           |          | LPMSUSP | LPMNYET |

| 0x1A   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x1B   | Reserved |          |         |           |       |        |           |          |         |         |

| 0x1C   | INTFLAG  | 7:0      | RAMACER | UPRSM     | EORSM | WAKEUP | EORST     | SOF      |         | SUSPEND |

## 38.8.3.4 EndPoint Status n

| Name:     | EPSTATUSn            |

|-----------|----------------------|

| Offset:   | 0x106 + (n x 0x20)   |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7      | 6      | 5 | 4       | 3 | 2     | 1      | 0       |

|--------|--------|--------|---|---------|---|-------|--------|---------|

| Γ      | BK1RDY | BK0RDY |   | STALLRQ |   | CURBK | DTGLIN | DTGLOUT |

| Access | R      | R      |   | R       |   | R     | R      | R       |

| Reset  | 0      | 0      |   | 2       |   | 0     | 0      | 0       |

### Bit 7 – BK1RDY Bank 1 is ready

For Control/OUT direction Endpoints, the bank is empty.

Writing a one to the bit EPSTATUSCLR.BK1RDY will clear this bit.

Writing a one to the bit EPSTATUSSET.BK1RDY will set this bit.

| Value | Description                                                                                 |

|-------|---------------------------------------------------------------------------------------------|

| 0     | The bank number 1 is not ready : For IN direction Endpoints, the bank is not yet filled in. |

| 1     | The bank number 1 is ready: For IN direction Endpoints, the bank is filled in. For          |

|       | Control/OUT direction Endpoints, the bank is full.                                          |

#### Bit 6 – BK0RDY Bank 0 is ready

Writing a one to the bit EPSTATUSCLR.BK0RDY will clear this bit.

Writing a one to the bit EPSTATUSSET.BK0RDY will set this bit.

| Value | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| 0     | The bank number 0 is not ready : For IN direction Endpoints, the bank is not yet filled in. For |

|       | Control/OUT direction Endpoints, the bank is empty.                                             |

| 1     | The bank number 0 is ready: For IN direction Endpoints, the bank is filled in. For              |

|       | Control/OUT direction Endpoints, the bank is full.                                              |

#### Bit 4 – STALLRQ STALL bank x request

Writing a zero to the bit EPSTATUSCLR.STALLRQ will clear this bit.

Writing a one to the bit EPSTATUSSET.STALLRQ will set this bit.

This bit is cleared by hardware when receiving a SETUP packet.

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Disable STALLRQx feature.                                                                 |

| 1     | Enable STALLRQx feature: a STALL handshake will be sent to the host in regards to bank x. |

### Bit 2 – CURBK Current Bank

Writing a zero to the bit EPSTATUSCLR.CURBK will clear this bit.

Writing a one to the bit EPSTATUSSET.CURBK will set this bit.

# **CAN - Control Area Network**

| Vá | alue | Description                                                                                 |

|----|------|---------------------------------------------------------------------------------------------|

|    |      | 0 to 31. The actual interpretation by the hardware of this value is such that one more than |

|    |      | the value programmed here is used.                                                          |

## Bits 12:8 – DTSEG1[4:0] Fast time segment before sample point

| Value  | Description                                                                                    |

|--------|------------------------------------------------------------------------------------------------|

| 0x00 - | Valid values are 0 to 31. The actual interpretation by the hardware of this value is such that |

| 0x1F   | one more than the programmed value is used. DTSEG1 is the sum of Prop_Seg and                  |

|        | Phase_Seg1.                                                                                    |

# Bits 7:4 – DTSEG2[3:0] Data time segment after sample point

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0x0 - | Valid values are 0 to 15. The actual interpretation by the hardware of this value is such that |

| 0xF   | one more than the programmed value is used. DTSEG2 is Phase_Seg2.                              |

# Bits 3:0 – DSJW[3:0] Data (Re)Syncronization Jump Width

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0x0 - | Valid values are 0 to 15. The actual interpretation by the hardware of this value is such that |

| 0xF   | one more than the programmed value is used.                                                    |

# **CAN - Control Area Network**

### 39.8.22 Extended ID Filter Configuration

| Name:     | XIDFC            |

|-----------|------------------|

| Offset:   | 0x88             |

| Reset:    | 0x00000000       |

| Property: | Write-restricted |

| Bit             | 31       | 30  | 29  | 28   | 27       | 26  | 25  | 24  |

|-----------------|----------|-----|-----|------|----------|-----|-----|-----|

| Access<br>Reset |          |     |     |      |          |     |     |     |

| Bit             | 23       | 22  | 21  | 20   | 19       | 18  | 17  | 16  |

|                 |          |     |     |      | LSE[6:0] |     |     |     |

| Access          | <b>L</b> | R/W | R/W | R/W  | R/W      | R/W | R/W | R/W |

| Reset           |          | 0   | 0   | 0    | 0        | 0   | 0   | 0   |

| Bit             | 15       | 14  | 13  | 12   | 11       | 10  | 9   | 8   |

|                 |          |     |     | FLES | A[15:8]  |     |     |     |

| Access          | R/W      | R/W | R/W | R/W  | R/W      | R/W | R/W | R/W |

| Reset           | 0        | 0   | 0   | 0    | 0        | 0   | 0   | 0   |

| Bit             | 7        | 6   | 5   | 4    | 3        | 2   | 1   | 0   |

|                 |          |     |     |      | A[7:0]   |     |     |     |

| Access          | R/W      | R/W | R/W | R/W  | R/W      | R/W | R/W | R/W |

| Reset           | 0        | 0   | 0   | 0    | 0        | 0   | 0   | 0   |

## Bits 22:16 - LSE[6:0] List Size Extended

| Value  | Description                                    |  |  |  |  |

|--------|------------------------------------------------|--|--|--|--|

| 0      | No extended Message ID filter.                 |  |  |  |  |

| 1 - 64 | Number of Extended Message ID filter elements. |  |  |  |  |

| > 64   | Values greater than 64 are interpreted as 64.  |  |  |  |  |

#### Bits 15:0 - FLESA[15:0] Filter List Extended Start Address

Start address of extended Message ID filter list. When the CAN module addresses the Message RAM it addresses 32-bit words, not single bytes. The configurable start addresses are 32-bit word addresses, i.e. only bits 15 to 2 are evaluated, the two least significant bits are ignored. Bits 1 to 0 will always be read back as "00".

### 43.3.7.2.2 How to Use the Service

### 43.3.7.2.3 Description

The operation performed is:

$Pt_C = Pt_A + Pt_B$

In this computation, the following parameters need to be provided:

- Point A the input point is filled in projective coordinates (X,Y,Z) (pointed by {nu1PointABase, 3\*u2ModLength + 12}). This point can be the Infinite Point.

- Point B the input point is filled in projective coordinates (X,Y,Z) (pointed by {nu1PointBBase, 3\*u2ModLength + 12}). This point can be the Infinite Point.

- Cns the Fast Modular Constant filled (pointed by {nu1CnsBase,u2ModLength + 12})

- P the modulus filled (pointed by {nu1ModBase,u2ModLength + 4})

- The a parameter relative to the elliptic curve equation (pointed by {nu1ABase,u2ModLength + 4})

- The workspace not initialized (pointed by {nu1WorkSpace, 7\*u2ModLength + 40}

The resulting C point is represented in projective coordinates (X,Y,Z) and is stored at the same place than the input point A. This Point can be the Infinite Point.

The services for this operation are:

• Service GF2NEccAddFast: The fast mode is used, the fast modular reduction is used in the computations.

**Important:** Before using this service, ensure that the constant Cns has been calculated with the setup of the Modular Reductions service.

# 43.3.7.2.4 Parameters Definition

#### Table 43-94. GF2NEccAddFast Service Parameters

| Parameter     | Туре | Direction | Location      | Data Length           | Before<br>Executing the<br>Service           | After<br>Executing the<br>Service                |

|---------------|------|-----------|---------------|-----------------------|----------------------------------------------|--------------------------------------------------|

| nu1ModBase    | nu1  | I         | Crypto<br>RAM | u2ModLength + 4       | Base of Modulus<br>P                         | Base of<br>Modulus P                             |

| nu1CnsBase    | nu1  | I         | Crypto<br>RAM | u2ModLength + 12      | Base of Cns                                  | Base of Cns                                      |

| u2ModLength   | u2   | I         | -             | _                     | Length of modulo                             | Length of<br>modulo                              |

| nu1PointABase | nu1  | I/O       | Crypto<br>RAM | 3*u2ModLength<br>+ 12 | Input point A<br>(projective<br>coordinates) | Resulting point<br>C (projective<br>coordinates) |

| nu1PointBBase | nu1  | I         | Crypto<br>RAM | 3*u2ModLength<br>+ 12 | Input point B<br>(projective<br>coordinates) | Input point B                                    |

# Public Key Cryptography Controller (PUKCC)

| Parameter     | Туре | Direction | Location   | Data Length           | Before<br>Executing the<br>Service | After<br>Executing the<br>Service |

|---------------|------|-----------|------------|-----------------------|------------------------------------|-----------------------------------|

| nu1PointBase  | nu1  | I         | Crypto RAM | 3*u2ModLength<br>+ 12 | Input point                        | Resulting point                   |

| nu1RandomBase | nu1  | I         | Crypto RAM | u2ModLength + 4       | Random                             | Corrupted                         |

| nu1Workspace  | nu1  | I         | Crypto RAM | 3*u2ModLength<br>+ 28 | -                                  | Workspace                         |

#### 43.3.7.7.5 Code Example

```

PUKCL PARAM PUKCLParam;

PPUKCL PARAM pvPUKCLParam = & PUKCLParam;

// ! The Random Number Generator must be initialized and started

\ensuremath{//} ! following the directives given for the RNG on the chip

PUKCL (u2Option) = 0;

// Depending on the option specified, not all fields should be filled

PUKCL _GF2NEcRandomiseCoordinate(nulModBase) = <Base of the ram location of P>;

PUKCL _GF2NEcRandomiseCoordinate(u2ModLength) = <Byte length of P>;

PUKCL _GF2NEcRandomiseCoordinate(nu1CnsBase) = <Base of the ram location of Cns>;

PUKCL GF2NEcRandomiseCoordinate(nulRandomBase) = <Base of the ram location where the the rng

is stored>;

PUKCL _GF2NEcRandomiseCoordinate(nulPointBase) = <Base of the ram location of the point>;

PUKCL GF2NEcRandomiseCoordinate(nu1Workspace) =

<Base of the ram location of the workspace>;

// vPUKCL Process() is a macro command, which populates the service name

// and then calls the library...

vPUKCL Process (GF2NEcRandomiseCoordinate, & PUKCLParam);

if (PUKCL (u2Status) == PUKCL OK)

{

}

else // Manage the error

```

#### 43.3.7.7.6 Constraints

No overlapping between either input and output are allowed. The following conditions must be avoided to ensure that the service works correctly:

- nu1ModBase, nu1CnsBase, nu1PointABase, nu1RandomBase, nu1Workspace are not aligned on 32-bit boundaries

- {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1PointABase, 3\*u2ModLength + 12}, {nu1RandomBase, u2ModLength + 4}, {nu1Workspace, <WorkspaceLength>} are not in Crypto RAM

- u2ModLength is either: < 12, > 0xffc or not a 32-bit length

- All overlapping between {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1PointABase, 3\*u2ModLength + 12}, {nu1RandomBase, u2ModLength + 4} and {nu1Workspace, 3\*u2ModLength + 28}

#### 43.3.7.7.7 Status Returned Values

# Table 43-105. GF2NEcRandomiseCoordinate Service Return Codes

| Returned Status | Importance | Meaning                                 |

|-----------------|------------|-----------------------------------------|

| PUKCL_OK        | -          | The computation passed without problem. |

# TCC – Timer/Counter for Control Applications

| Offset | Name     | Bit Pos. |             |                |  |  |  |

|--------|----------|----------|-------------|----------------|--|--|--|

|        |          | 7:0      | CC[1:0]     | DITHER[5:0]    |  |  |  |

|        |          | 15:8     |             | CC[9:2]        |  |  |  |

| 0x54   | CC4      | 23:16    |             | CC[17:10]      |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 7:0      | CC[1:0]     | DITHER[5:0]    |  |  |  |

|        |          | 15:8     |             | CC[9:2]        |  |  |  |

| 0x58   | CC5      | 23:16    |             | CC[17:10]      |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

| 0x5C   |          |          |             |                |  |  |  |

|        | Reserved |          |             |                |  |  |  |

| 0x63   |          |          |             |                |  |  |  |

|        |          | 7:0      |             | PGEB0[7:0]     |  |  |  |

| 0x64   | PATTBUF  | 15:8     |             | PGVB0[7:0]     |  |  |  |

| 0x66   |          |          |             |                |  |  |  |

|        | Reserved |          |             |                |  |  |  |

| 0x6B   |          |          |             |                |  |  |  |

|        |          | 7:0      | PERBUF[1:0] | DITHERBUF[5:0] |  |  |  |

|        |          | 15:8     |             | PERBUF[9:2]    |  |  |  |

| 0x6C   | PERBUF   | 23:16    |             | PERBUF[17:10]  |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 7:0      | CCBUF[1:0]  | DITHERBUF[5:0] |  |  |  |

|        |          | 15:8     | CCBUF[9:2]  |                |  |  |  |

| 0x70   | CCBUF0   | 23:16    |             | CCBUF[17:10]   |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 7:0      | CCBUF[1:0]  | DITHERBUF[5:0] |  |  |  |

|        |          | 15:8     |             | CCBUF[9:2]     |  |  |  |

| 0x74   | CCBUF1   | 23:16    |             | CCBUF[17:10]   |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 7:0      | CCBUF[1:0]  | DITHERBUF[5:0] |  |  |  |

|        |          | 15:8     |             | CCBUF[9:2]     |  |  |  |

| 0x78   | CCBUF2   | 23:16    |             | CCBUF[17:10]   |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 7:0      | CCBUF[1:0]  | DITHERBUF[5:0] |  |  |  |

|        |          | 15:8     | -           | CCBUF[9:2]     |  |  |  |

| 0x7C   | CCBUF3   | 23:16    |             | CCBUF[17:10]   |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 7:0      | CCBUF[1:0]  | DITHERBUF[5:0] |  |  |  |

|        |          | 15:8     | - •         | CCBUF[9:2]     |  |  |  |

| 0x80   | CCBUF4   | 23:16    |             | CCBUF[17:10]   |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 7:0      | CCBUF[1:0]  | DITHERBUF[5:0] |  |  |  |

|        |          | 15:8     |             | CCBUF[9:2]     |  |  |  |

| 0x84   | CCBUF5   | 23:16    |             | CCBUF[17:10]   |  |  |  |

|        |          | 31:24    |             |                |  |  |  |

|        |          | 01.27    |             |                |  |  |  |

# TCC – Timer/Counter for Control Applications

| Value | Description                                    |  |  |  |

|-------|------------------------------------------------|--|--|--|

| 0     | The Recoverable Fault B interrupt is disabled. |  |  |  |

| 1     | The Recoverable Fault B interrupt is enabled.  |  |  |  |

# Bit 12 – FAULTA Recoverable Fault A Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Recoverable Fault A Interrupt Disable/Enable bit, which enables the Recoverable Fault A interrupt.

| Value | Description                                    |  |  |  |  |

|-------|------------------------------------------------|--|--|--|--|

| 0     | The Recoverable Fault A interrupt is disabled. |  |  |  |  |

| 1     | The Recoverable Fault A interrupt is enabled.  |  |  |  |  |

# Bit 11 – DFS Non-Recoverable Debug Fault Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Debug Fault State Interrupt Disable/Enable bit, which enables the Debug Fault State interrupt.

| Value | Description                                  |  |  |  |

|-------|----------------------------------------------|--|--|--|

| 0     | The Debug Fault State interrupt is disabled. |  |  |  |

| 1     | The Debug Fault State interrupt is enabled.  |  |  |  |

# Bit 3 – ERR Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Error Interrupt Disable/Enable bit, which enables the Compare interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

# Bit 2 – CNT Counter Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Retrigger Interrupt Disable/Enable bit, which enables the Counter interrupt.

| Value | Description                        |

|-------|------------------------------------|

| 0     | The Counter interrupt is disabled. |

| 1     | The Counter interrupt is enabled.  |

# **Bit 1 – TRG** Retrigger Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Retrigger Interrupt Disable/Enable bit, which enables the Retrigger interrupt.

| Value | Description                          |

|-------|--------------------------------------|

| 0     | The Retrigger interrupt is disabled. |

| 1     | The Retrigger interrupt is enabled.  |