#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 120MHz                                                                                |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 51                                                                                    |

| Program Memory Size        | 256KB (256K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 128K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                         |

| Data Converters            | A/D 24x12b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 64-VFQFN Exposed Pad                                                                  |

| Supplier Device Package    | 64-QFN (9x9)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame53j18a-mut            |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**Processor and Architecture**

| Module                         | Source   | Line |  |

|--------------------------------|----------|------|--|

|                                | MC 1     | 87   |  |

|                                | MC 2     | 88   |  |

|                                | MC 3     | 89   |  |

|                                | MC 4     | 90   |  |

|                                | MC 5     | 91   |  |

| TCC1 - Timer Counter Control 1 | CNT A    | 92   |  |

|                                | DFS A    |      |  |

|                                | ERR A    |      |  |

|                                | FAULTA A |      |  |

|                                | FAULTB A |      |  |

|                                | FAULT0 A |      |  |

|                                | FAULT1 A |      |  |

|                                | OVF      |      |  |

|                                | TRG      |      |  |

|                                | UFS A    |      |  |

|                                | MC 0     | 93   |  |

|                                | MC 1     | 94   |  |

|                                | MC 2     | 95   |  |

|                                | MC 3     | 96   |  |

| TCC2 - Timer Counter Control 2 | CNT A    | 97   |  |

|                                | DFS A    |      |  |

|                                | ERR A    |      |  |

|                                | FAULTA A |      |  |

|                                | FAULTB A |      |  |

|                                | FAULT0 A |      |  |

|                                | FAULT1 A |      |  |

|                                | OVF      |      |  |

|                                | TRG      |      |  |

|                                | UFS A    |      |  |

|                                | MC 0     | 98   |  |

|                                | MC 1     | 99   |  |

|                                | MC 2     | 100  |  |

# 12.13.7 Debug Communication Channel x

| Name:     | DCC                  |

|-----------|----------------------|

| Offset:   | 0x10 + n*0x04 [n=01] |

| Reset:    | 0x0000000            |

| Property: | -                    |

| Bit    | 31          | 30  | 29  | 28    | 27             | 26  | 25  | 24  |  |  |

|--------|-------------|-----|-----|-------|----------------|-----|-----|-----|--|--|

|        | DATA[31:24] |     |     |       |                |     |     |     |  |  |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |  |  |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |  |  |

|        |             |     |     |       |                |     |     |     |  |  |

| Bit    | 23          | 22  | 21  | 20    | 19             | 18  | 17  | 16  |  |  |

|        |             |     |     | DATA[ | 23:16]         |     |     |     |  |  |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |  |  |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |  |  |

|        |             |     |     |       |                |     |     |     |  |  |

| Bit    | 15          | 14  | 13  | 12    | 11             | 10  | 9   | 8   |  |  |

|        |             |     |     | DATA  | [15:8]         |     |     |     |  |  |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |  |  |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |  |  |

|        |             |     |     |       |                |     |     |     |  |  |

| Bit    | 7           | 6   | 5   | 4     | 3              | 2   | 1   | 0   |  |  |

|        |             |     |     | DATA  | <b>\</b> [7:0] |     |     |     |  |  |

| Access | R/W         | R/W | R/W | R/W   | R/W            | R/W | R/W | R/W |  |  |

| Reset  | 0           | 0   | 0   | 0     | 0              | 0   | 0   | 0   |  |  |

Bits 31:0 – DATA[31:0] Data Data register.

bits. PDBKUPRAM power domain can be either fully or partially retained or be fully off according to HIBCFG.BRAMCFG bits. If partial option is selected, only the lowest 4KBytes section is retained

- Backup mode: When entering backup mode, the PDCORESW and PDSYSRAM power domains are off. PDBACKUP is still active. As in hibernate mode, PDBKUPRAM power domain can be either fully or partially retained or be fully off according to BKUPCFG.BRAMCFG bits.

- OFF mode:

When entering OFF mode, all the power domains are off.

The table below illustrates the PDRAM state:

|                           |                     |                   | Power Domain State |          |              |  |  |

|---------------------------|---------------------|-------------------|--------------------|----------|--------------|--|--|

| Sleep Mode                | STDBYCFG<br>.RAMCFG | HIBCFG.RA<br>MCFG | PDCORESW           | PDBACKUP | PDSYSRAM     |  |  |

| Active                    | N/A                 | N/A               | active             | active   | active       |  |  |

| Idle                      | N/A                 | N/A               | active             | active   | active       |  |  |

| Standby with sleepwalking | N/A                 | N/A               | active             | active   | active       |  |  |

| Standby - case 1          | RET                 | N/A               | active             | active   | retained     |  |  |

| Standby - case 2          | PARTIAL             | N/A               | active             | active   | 32K retained |  |  |

| Standby - case 3          | OFF                 | N/A               | active             | active   | off          |  |  |

| Hibernate - case<br>1     | N/A                 | RET               | off                | active   | retained     |  |  |

| Hibernate - case<br>2     | N/A                 | PARTIAL           | off                | active   | 32K retained |  |  |

| Hibernate - case<br>3     | N/A                 | OFF               | off                | active   | off          |  |  |

| Backup                    | N/A                 | N/A               | off                | active   | off          |  |  |

| Off                       | N/A                 | N/A               | off                | off      | off          |  |  |

| Table 18-3. Sleep Mode versus PDSYSRAM Power Domain State Overview | Table 18-3. |

|--------------------------------------------------------------------|-------------|

|--------------------------------------------------------------------|-------------|

The table below illustrates the PDBKUPRAM state:

Table 18-4.

Sleep Mode versus PDBKUPRAM Power Domain State Overview

|            |                    |                     | Power Domain State |          |           |  |  |

|------------|--------------------|---------------------|--------------------|----------|-----------|--|--|

| Sleep Mode | HIBCFG.BR<br>AMCFG | BKUPCFG.<br>BRAMCFG | PDCORESW           | PDBACKUP | PDBKUPRAM |  |  |

| Active     | N/A                | N/A                 | active             | active   | active    |  |  |

| Idle       | N/A                | N/A                 | active             | active   | active    |  |  |

| Standby    | N/A                | N/A                 | active             | active   | retained  |  |  |

# 21.10.11 Counter Period in COUNT16 mode (CTRLA.MODE=1)

| Name:     | PER                                      |

|-----------|------------------------------------------|

| Offset:   | 0x1C                                     |

| Reset:    | 0x0000                                   |

| Property: | PAC Write-Protection, Write-Synchronized |

| Bit    | 15       | 14        | 13  | 12  | 11  | 10  | 9   | 8   |  |  |

|--------|----------|-----------|-----|-----|-----|-----|-----|-----|--|--|

|        |          | PER[15:8] |     |     |     |     |     |     |  |  |

| Access | R/W      | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0        | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

|        |          |           |     |     |     |     |     |     |  |  |

| Bit    | 7        | 6         | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|        | PER[7:0] |           |     |     |     |     |     |     |  |  |

| Access | R/W      | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| Reset  | 0        | 0         | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

# Bits 15:0 - PER[15:0] Counter Period

These bits define the value of the 16-bit RTC period in COUNT16 mode (CTRLA.MODE=1).

# **EIC – External Interrupt Controller**

Each interrupt source has an associated interrupt flag. The interrupt flag in the Interrupt Flag Status and Clear register (INTFLAG) is set when an interrupt condition occurs (NMIFLAG for NMI). Each interrupt, except NMI, can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1).

An interrupt request is generated when the interrupt flag is set and the corresponding interrupt is enabled. The interrupt request remains active until the interrupt flag is cleared, the interrupt is disabled, or the EIC is reset. See the INTFLAG register for details on how to clear interrupt flags. The EIC has one interrupt request line for each external interrupt (EXTINTx) and one line for NMI. The user must read the INTFLAG (or NMIFLAG) register to determine which interrupt condition is present.

#### Note:

- 1. Interrupts must be globally enabled for interrupt requests to be generated.

- 2. If an external interrupts (EXTINT) is common on two or more I/O pins, only one will be active (the first one programmed).

#### **Related Links**

#### 10. Processor and Architecture

#### 23.6.7 Events

The EIC can generate the following output events:

• External event from pin (EXTINTx).

Setting an Event Output Control register (EVCTRL.EXTINTEO) enables the corresponding output event. Clearing this bit disables the corresponding output event. Refer to *Event System* for details on configuring the Event System.

When the condition on pin EXTINTx matches the configuration in the CONFIGn register, the corresponding event is generated, if enabled.

# **Related Links**

31. EVSYS - Event System

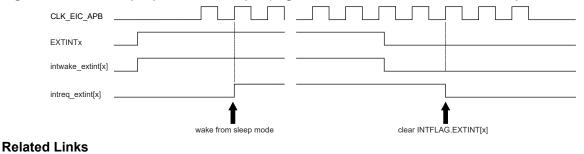

#### 23.6.8 Sleep Mode Operation

In sleep modes, an EXTINTx pin can wake up the device if the corresponding condition matches the configuration in the CONFIG register, and the corresponding bit in the Interrupt Enable Set register (23.8.7 INTENSET) is written to '1'.

#### Figure 23-5. Wake-up Operation Example (High-Level Detection, No Filter, Interrupt Enable Set)

23.8.10 CONFIG

|        | Name:<br>Offset:<br>Reset:<br>Property: | TPSF<br>0x040<br>0x00000FFF<br>- |     |       |     |     |          |     |

|--------|-----------------------------------------|----------------------------------|-----|-------|-----|-----|----------|-----|

| Bit    | 31                                      | 30                               | 29  | 28    | 27  | 26  | 25       | 24  |

|        | ENTXP                                   |                                  |     |       |     |     |          |     |

| Access | R/W                                     |                                  |     |       |     |     |          |     |

| Reset  | 0                                       |                                  |     |       |     |     |          |     |

|        |                                         |                                  |     |       |     |     |          |     |

| Bit    | 23                                      | 22                               | 21  | 20    | 19  | 18  | 17       | 16  |

|        |                                         |                                  |     |       |     |     |          |     |

| Access |                                         |                                  |     |       |     |     |          |     |

| Reset  |                                         |                                  |     |       |     |     |          |     |

| Dit    | 45                                      |                                  | 10  | 10    | 44  | 10  | 0        | 0   |

| Bit    | 15                                      | 14                               | 13  | 12    | 11  | 10  | 9        | 8   |

|        |                                         |                                  |     |       |     |     | DR[11:8] |     |

| Access |                                         |                                  |     |       | R/W | R/W | R/W      | R/W |

| Reset  |                                         |                                  |     |       | 1   | 1   | 1        | 1   |

|        |                                         |                                  |     |       |     |     |          |     |

| Bit    | 7                                       | 6                                | 5   | 4     | 3   | 2   | 1        | 0   |

|        |                                         |                                  |     | TPB1A |     |     |          |     |

| Access | R/W                                     | R/W                              | R/W | R/W   | R/W | R/W | R/W      | R/W |

| Reset  | 1                                       | 1                                | 1   | 1     | 1   | 1   | 1        | 1   |

# 24.9.17 GMAC TX Partial Store and Forward Register

Bit 31 – ENTXP Enable TX Partial Store and Forward Operation

**Bits 11:0 – TPB1ADR[11:0]** Transmit Partial Store and Forward Address Watermark value.

# **PAC - Peripheral Access Controller**

# 27.7.8 Peripheral Interrupt Flag Status - Bridge C

| Name:     | INTFLAGC   |

|-----------|------------|

| Offset:   | 0x1C       |

| Reset:    | 0x00000000 |

| Property: | -          |

These flags are set when a Peripheral Access Error occurs while accessing the peripheral associated with the respective INTFLAGx bit, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to these bits has no effect.

Writing a '1' to these bits will clear the corresponding INTFLAGx interrupt flag.

| Bit    | 31   | 30  | 29   | 28    | 27   | 26   | 25   | 24   |

|--------|------|-----|------|-------|------|------|------|------|

|        |      |     |      |       |      |      |      |      |

| Access |      |     |      |       |      |      |      |      |

| Reset  |      |     |      |       |      |      |      |      |

|        |      |     |      |       |      |      |      |      |

| Bit    | 23   | 22  | 21   | 20    | 19   | 18   | 17   | 16   |

|        |      |     |      |       |      |      |      |      |

| Access |      |     |      |       |      |      |      |      |

| Reset  |      |     |      |       |      |      |      |      |

|        |      |     |      |       |      |      |      |      |

| Bit    | 15   | 14  | 13   | 12    | 11   | 10   | 9    | 8    |

|        |      | CCL | QSPI | PUKCC | ICM  | TRNG | AES  |      |

| Access |      | RW  | RW   | RW    | RW   | RW   | RW   |      |

| Reset  |      | 0   | 0    | 0     | 0    | 0    | 0    |      |

|        |      |     |      |       |      |      |      |      |

| Bit    | 7    | 6   | 5    | 4     | 3    | 2    | 1    | 0    |

|        | PDEC | TC5 | TC4  | TCC3  | TCC2 | GMAC | CAN1 | CAN0 |

| Access | RW   | RW  | RW   | RW    | RW   | RW   | RW   | RW   |

| Reset  | 0    | 0   | 0    | 0     | 0    | 0    | 0    | 0    |

# Bit 14 – CCL Interrupt Flag for CCL

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the CCL, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the CCL interrupt flag.

# Bit 13 – QSPI Interrupt Flag for QSPI

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the QSPI, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the QSPI interrupt flag.

# Bit 12 – PUKCC Interrupt Flag for PUKCC

This flags is set when a Peripheral Access Error occurs while accessing the peripheral associated with the PUKCC, and will generate an interrupt request if INTENCLR/SET.ERR is '1'.

© 2018 Microchip Technology Inc.

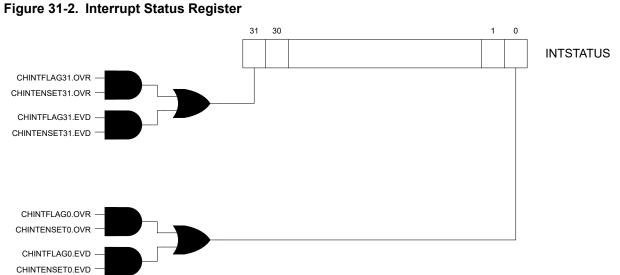

The Event System can arbitrate between all channels with pending interrupts. The arbiter can be configured to prioritize statically or dynamically the incoming events. The priority is evaluated each time a new channel has an interrupt pending, or an interrupt has been cleared. The Channel Pending Interrupt register (INTPEND) will provide the channel number with the highest interrupt priority, and the corresponding channel interrupt flags and status bits.

By default, static arbitration is enabled (PRICTRL.RRENx is '0'), the arbiter will prioritize a low channel number over a high channel number as shown below. When using the status scheme, there is a risk of high channel numbers never being granted access by the arbiter. This can be avoided using a dynamic arbitration scheme.

# Figure 31-3. Static Priority

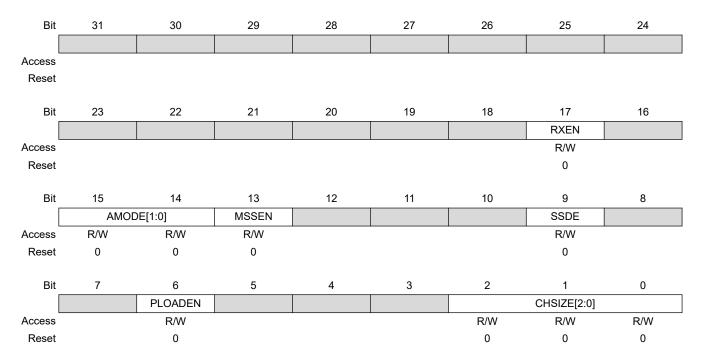

#### 35.8.2 Control B

| Name:     | CTRLB                                                      |

|-----------|------------------------------------------------------------|

| Offset:   | 0x04                                                       |

| Reset:    | 0x0000000                                                  |

| Property: | PAC Write-Protection, Enable-Protected, Write-Synchronized |

#### Bit 17 - RXEN Receiver Enable

Writing '0' to this bit will disable the SPI receiver immediately. The receive buffer will be flushed, data from ongoing receptions will be lost and STATUS.BUFOVF will be cleared.

Writing '1' to CTRLB.RXEN when the SPI is disabled will set CTRLB.RXEN immediately. When the SPI is enabled, CTRLB.RXEN will be cleared, SYNCBUSY.CTRLB will be set and remain set until the receiver is enabled. When the receiver is enabled CTRLB.RXEN will read back as '1'.

Writing '1' to CTRLB.RXEN when the SPI is enabled will set SYNCBUSY.CTRLB, which will remain set until the receiver is enabled, and CTRLB.RXEN will read back as '1'.

This bit is not enable-protected.

| Value                                                                | Description                                |  |  |  |

|----------------------------------------------------------------------|--------------------------------------------|--|--|--|

| 0                                                                    | The receiver is disabled or being enabled. |  |  |  |

| 1 The receiver is enabled or it will be enabled when SPI is enabled. |                                            |  |  |  |

#### Bits 15:14 – AMODE[1:0] Address Mode

These bits set the slave addressing mode when the frame format (CTRLA.FORM) with address is used. They are unused in master mode.

#### 38.8.5.6 Host Interrupt Enable Register Clear

| Name:     | INTENCLR             |

|-----------|----------------------|

| Offset:   | 0x14                 |

| Reset:    | 0x0000               |

| Property: | PAC Write-Protection |

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set (INTENSET) register.

| Bit    | 15      | 14    | 13    | 12     | 11  | 10   | 9     | 8     |

|--------|---------|-------|-------|--------|-----|------|-------|-------|

|        |         |       |       |        |     |      | DDISC | DCONN |

| Access |         |       |       |        |     |      | R/W   | R/W   |

| Reset  |         |       |       |        |     |      | 0     | 0     |

|        |         |       |       |        |     |      |       |       |

| Bit    | 7       | 6     | 5     | 4      | 3   | 2    | 1     | 0     |

|        | RAMACER | UPRSM | DNRSM | WAKEUP | RST | HSOF |       |       |

| Access | R/W     | R/W   | R/W   | R/W    | R/W | R/W  |       |       |

| Reset  | 0       | 0     | 0     | 0      | 0   | 0    |       |       |

**Bit 9 – DDISC** Device Disconnection Interrupt Disable Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Device Disconnection interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                                   |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | The Device Disconnection interrupt is disabled.                                                                                               |  |  |  |

| 1     | The Device Disconnection interrupt is enabled and an interrupt request will be generated when the Device Disconnection interrupt Flag is set. |  |  |  |

Bit 8 – DCONN Device Connection Interrupt Disable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the Device Connection interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                                                                             |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0     | The Device Connection interrupt is disabled.                                                                                            |  |  |  |

| 1     | The Device Connection interrupt is enabled and an interrupt request will be generated when the Device Connection interrupt Flag is set. |  |  |  |

#### Bit 7 – RAMACER RAM Access Interrupt Disable

Writing a zero to this bit has no effect.

Writing a one to this bit will clear the RAM Access interrupt Enable bit and disable the corresponding interrupt request.

| Value | Description                                                                             |  |  |  |

|-------|-----------------------------------------------------------------------------------------|--|--|--|

| 0     | The RAM Access interrupt is disabled.                                                   |  |  |  |

| 1     | The RAM Access interrupt is enabled and an interrupt request will be generated when the |  |  |  |

|       | RAM Access interrupt Flag is set.                                                       |  |  |  |

#### 40.8.10 Host Control 1 Register

| Name:     | HC1R |

|-----------|------|

| Offset:   | 0x28 |

| Reset:    | 0x00 |

| Property: | -    |

| Bit    | 7        | 6       | 5     | 4    | 3       | 2    | 1   | 0       |

|--------|----------|---------|-------|------|---------|------|-----|---------|

|        | CARDDSEL | CARDDTL | EXTDW | DMAS | EL[1:0] | HSEN | DW  | LEDCTRL |

| Access | R/W      | R/W     | R/W   |      |         | R/W  | R/W | R/W     |

| Reset  | 0        | 0       | 0     | 0    | 0       | 0    | 0   | 0       |

Bit 7 – CARDDSEL Card Detect Signal Selection

#### Note:

This register entry is specific to the SD/SDIO operation mode.

This bit selects the source for the card detection.

| ſ | Value | Description                                                          |

|---|-------|----------------------------------------------------------------------|

|   | 0     | The CD pin is selected.                                              |

|   | 1     | The Card Detect Test Level (CARDDTL) is selected (for test purpose). |

# Bit 6 – CARDDTL Card Detect Test Level

#### Note:

This register entry is specific to the SD/SDIO operation mode.

This bit is enabled while the Card Detect Signal Selection (CARDDSEL) is set to 1 and it indicates whether the card is inserted or not.

| Value | Description    |  |

|-------|----------------|--|

| 0     | No card.       |  |

| 1     | Card inserted. |  |

#### Bit 5 – EXTDW Extended Data Width

**Note:** This register entry is specific to the e.MMC operation mode.

This bit controls the 8-bit Bus Width mode for embedded devices. Support of this function is indicated in 8-bit Support for Embedded Device in CA0R. If a device supports the 8-bit mode, this may be set to 1. If this bit is 0, the bus width is controlled by Data Width (DW).

#### Bits 4:3 – DMASEL[1:0] DMA Select

One of the supported DAM modes can be selected. The user must check support of DMA modes by referring the CA0R. Use of selected DMA is determined by DMA Enable (DMAEN) in TMR.

| Value | Name                  | Description                      |  |

|-------|-----------------------|----------------------------------|--|

| 0     | SDMA SDMA is selected |                                  |  |

| 1     | Reserved              | Reserved                         |  |

| 2     | ADMA32                | 32-bit Address ADMA2 is selected |  |

| 3     | Reserved              | Reserved                         |  |

#### 40.8.32 ADMA System Address Register

| Name:     | ASARx      |

|-----------|------------|

| Offset:   | 0x58       |

| Reset:    | 0x00000000 |

| Property: | -          |

| Bit    | 31            | 30  | 29  | 28    | 27       | 26  | 25  | 24  |

|--------|---------------|-----|-----|-------|----------|-----|-----|-----|

|        | ADMASA[31:24] |     |     |       |          |     |     |     |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |               |     |     |       |          |     |     |     |

| Bit    | 23            | 22  | 21  | 20    | 19       | 18  | 17  | 16  |

|        |               |     |     | ADMAS | A[23:16] |     |     |     |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |               |     |     |       |          |     |     |     |

| Bit    | 15            | 14  | 13  | 12    | 11       | 10  | 9   | 8   |

|        | ADMASA[15:8]  |     |     |       |          |     |     |     |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

|        |               |     |     |       |          |     |     |     |

| Bit    | 7             | 6   | 5   | 4     | 3        | 2   | 1   | 0   |

|        | ADMASA[7:0]   |     |     |       |          |     |     |     |

| Access | R/W           | R/W | R/W | R/W   | R/W      | R/W | R/W | R/W |

| Reset  | 0             | 0   | 0   | 0     | 0        | 0   | 0   | 0   |

# Bits 31:0 – ADMASA[31:0] ADMA System Address

This field holds the byte address of the executing command of the descriptor table. At the start of ADMA, the user must set the start address of the descriptor table. The ADMA increments this register address, which points to the next Descriptor line to be fetched.

When the ADMA Error (ADMA) status flag rises, this field holds a valid descriptor address depending on the ADMA Error State (ERRST). The user must program Descriptor Table on 32-bit boundary and set 32-bit boundary address to this register. ADMA2 ignores the lower 2 bits of this register and assumes it to be 0.

**Note:** Most of the Elliptic Curve computations are reduced modulo P. In many functions the reductions are made with the Fast Reduction.

• Cns the Modular Constant (often pointed by {nu1CnsBase,u2ModLength + 12}): This parameter contains the Modular Constant associated to the Modulus

**Important:** The Modular Constant must be calculated before using the GF(p) Elliptic Curves functions by a call to the Setup for Modular Reductions with the GF(p) option (see Modular Reduction Setup in the 43.3.5.1 Modular Reduction section).

# 43.3.6.2 Point Addition

#### 43.3.6.2.1 Purpose

This service is used to perform a point addition, based on a given elliptic curve over GF(p). Please note that:

• This service is not intended to add the same point twice. In this particular case, use the doubling service

(see 43.3.6.4 Fast Point Doubling).

#### 43.3.6.2.2 How to Use the Service

#### 43.3.6.2.3 Description

The operation performed is:

$Pt_C = Pt_A + Pt_B$

In this computation, the following parameters need to be provided:

- A the input point is filled in projective coordinates (X,Y,Z) (pointed by {nu1PointABase, 3\*u2ModLength + 12}). This point can be the Infinite Point.

- B the input point is filled in projective coordinates (X,Y,Z) (pointed by {nu1PointBBase, 3\*u2ModLength + 12}). This point can be the Infinite Point.

- Cns the Fast Modular Constant filled (pointed by {nu1CnsBase,u2ModLength +8})

- P the modulus filled (pointed by {nu1ModBase,u2ModLength +4})

- The workspace not initialized (pointed by {nu1WorkSpace, 5\*u2ModLength +32}

The resulting C point is represented in projective coordinates (X,Y,Z) and is stored at the very same place than the input point A. This Point can be the Infinite Point.

The service name for this operation is *ZpEccAddFast*. This service uses Fast mode and Fast Modular Reduction for computations.

**Important:** Before using this service, ensure that the constant Cns has been calculated with the Setup of the Modular Reduction functions.

# ADC – Analog-to-Digital Converter

#### 45.8.18 Synchronization Busy

| Name:<br>Offset:<br>Reset:<br>Property: |       | SYNCBUSY<br>0x30<br>0x00000000<br>- |         |         |        |            |          |       |

|-----------------------------------------|-------|-------------------------------------|---------|---------|--------|------------|----------|-------|

| Bit                                     | 31    | 30                                  | 29      | 28      | 27     | 26         | 25       | 24    |

|                                         | RBSSW |                                     |         |         |        |            |          |       |

| Access                                  | R     |                                     |         | •       |        |            |          |       |

| Reset                                   | 0     |                                     |         |         |        |            |          |       |

|                                         |       |                                     |         |         |        |            |          |       |

| Bit                                     | 23    | 22                                  | 21      | 20      | 19     | 18         | 17       | 16    |

|                                         |       |                                     |         |         |        |            |          |       |

| Access                                  |       |                                     |         |         |        |            |          |       |

| Reset                                   |       |                                     |         |         |        |            |          |       |

| -                                       |       |                                     | 10      | 10      |        |            |          |       |

| Bit                                     | 15    | 14                                  | 13      | 12      | 11     | 10         | 9        | 8     |

|                                         |       |                                     |         |         | SWTRIG | OFFSETCORR | GAINCORR | WINUT |

| Access                                  |       |                                     |         |         | R      | R          | R        | R     |

| Reset                                   |       |                                     |         |         | 0      | 0          | 0        | 0     |

|                                         |       |                                     |         |         |        |            |          |       |

| Bit                                     | 7     | 6                                   | 5       | 4       | 3      | 2          | 1        | 0     |

|                                         | WINLT | SAMPCTRL                            | AVGCTRL | REFCTRL | CTRLB  | INPUTCTRL  | ENABLE   | SWRST |

| Access                                  | R     | R                                   | R       | R       | R      | R          | R        | R     |

| Reset                                   | 0     | 0                                   | 0       | 0       | 0      | 0          | 0        | 0     |

**Bit 31 – RBSSW** Reset BootStrap Switch Synchronization Busy

# Bit 11 – SWTRIG Software Trigger Synchronization Busy

This bit is cleared when the synchronization of SWTRIG register between the clock domains is complete.

This bit is set when the synchronization of SWTRIG register between clock domains is started.

**Note:** For the slave ADC, this bit is always read zero when the SLAVEEN bit is set (CTRLA.SLAVEEN= 1).

#### Bit 10 - OFFSETCORR Offset Correction Synchronization Busy

This bit is cleared when the synchronization of OFFSETCORR register between the clock domains is complete.

This bit is set when the synchronization of OFFSETCORR register between clock domains is started.

# Bit 9 – GAINCORR Gain Correction Synchronization Busy

This bit is cleared when the synchronization of GAINCORR register between the clock domains is complete.

This bit is set when the synchronization of GAINCORR register between clock domains is started.

#### **Bit 8 – WINUT** Window Monitor Upper Threshold Synchronization Busy

This bit is cleared when the synchronization of WINUT register between the clock domains is complete.

© 2018 Microchip Technology Inc.

DAC – Digital-to-Analog Converter

| Value | Description                                  |

|-------|----------------------------------------------|

| 0     | Filter 0 Result Ready interrupt is disabled. |

| 1     | Filter 0 Result Ready interrupt is enabled.  |

Bit 3 – EMPTY1 Data Buffer 1 Empty Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer 1 Empty Interrupt Enable bit, which disables the Data Buffer 1 Empty interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Data Buffer 1 Empty interrupt is disabled. |

| 1     | The Data Buffer 1 Empty interrupt is enabled.  |

# Bit 2 – EMPTY0 Data Buffer 0 Empty Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer 0 Empty Interrupt Enable bit, which disables the Data Buffer 0 Empty interrupt.

| Value | Description                                    |

|-------|------------------------------------------------|

| 0     | The Data Buffer 0 Empty interrupt is disabled. |

| 1     | The Data Buffer 0 Empty interrupt is enabled.  |

# Bit 1 – UNDERRUN1 Underrun Interrupt Enable for DAC1

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer 1 Underrun Interrupt Enable bit, which disables the Data Buffer 1 Underrun interrupt.

| Value | Description                                       |

|-------|---------------------------------------------------|

| 0     | The Data Buffer 1 Underrun interrupt is disabled. |

| 1     | The Data Buffer 1 Underrun interrupt is enabled.  |

# **Bit 0 – UNDERRUN0** Underrun Interrupt Enable for DAC0

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Data Buffer 0 Underrun Interrupt Enable bit, which disables the Data Buffer 0 Underrun interrupt.

| Valu | le | Description                                       |

|------|----|---------------------------------------------------|

| 0    |    | The Data Buffer 0 Underrun interrupt is disabled. |

| 1    |    | The Data Buffer 0 Underrun interrupt is enabled.  |

TC – Timer/Counter

| Value | Description                                                                               |

|-------|-------------------------------------------------------------------------------------------|

| 0     | Event from Event System is selected as trigger source for capture operation on channel x. |

| 1     | I/O pin is selected as trigger source for capture operation on channel x.                 |

# Bits 16, 17 – CAPTENx Capture Channel x Enable

Bit x of CAPTEN[1:0] selects whether channel x is a capture or a compare channel.

These bits are not synchronized.

| Value | Description                           |

|-------|---------------------------------------|

| 0     | CAPTEN disables capture on channel x. |

| 1     | CAPTEN enables capture on channel x.  |

# Bit 15 – DMAOS DMA One-Shot Trigger Mode

This bit enables the DMA One-shot Trigger Mode.

Writing a '1' to this bit will generate a DMA trigger on TC cycle following a TC\_CTRLBSET\_CMD\_DMAOS command.

Writing a '0' to this bit will generate DMA triggers on each TC cycle.

This bit is not synchronized.

#### Bit 11 – ALOCK Auto Lock

When this bit is set, Lock bit update (LUPD) is set to '1' on each overflow/underflow or re-trigger event.

This bit is not synchronized.

| Value | Description                                                               |

|-------|---------------------------------------------------------------------------|

| 0     | The LUPD bit is not affected on overflow/underflow, and re-trigger event. |

| 1     | The LUPD bit is set on each overflow/underflow or re-trigger event.       |

#### Bits 10:8 – PRESCALER[2:0] Prescaler

These bits select the counter prescaler factor.

These bits are not synchronized.

| Value | Name    | Description             |

|-------|---------|-------------------------|

| 0x0   | DIV1    | Prescaler: GCLK_TC      |

| 0x1   | DIV2    | Prescaler: GCLK_TC/2    |

| 0x2   | DIV4    | Prescaler: GCLK_TC/4    |

| 0x3   | DIV8    | Prescaler: GCLK_TC/8    |

| 0x4   | DIV16   | Prescaler: GCLK_TC/16   |

| 0x5   | DIV64   | Prescaler: GCLK_TC/64   |

| 0x6   | DIV256  | Prescaler: GCLK_TC/256  |

| 0x7   | DIV1024 | Prescaler: GCLK_TC/1024 |

# Bit 7 - ONDEMAND Clock On Demand

This bit selects the clock requirements when the TC is stopped.

In standby mode, if the Run in Standby bit (CTRLA.RUNSTDBY) is '0', ONDEMAND is forced to '0'.

This bit is not synchronized.

# Note:

When a re-trigger event action is configured in the Event Action bits in the Event Control register (EVCTRL.EVACTn=0x1, RETRIGGER), enabling the counter will not start the counter. The counter will start on the next incoming event and restart on corresponding following event.

# Start Event Action

The start action can be selected in the Event Control register (EVCTRL.EVACT0=0x3, START) and can start the counting operation when previously stopped. The event has no effect if the counter is already counting. When the module is enabled, the counter operation starts when the event is received or when a re-trigger software command is applied.

# Note:

When a start event action is configured in the Event Action bits in the Event Control register (EVCTRL.EVACT0=0x3, START), enabling the counter will not start the counter. The counter will start on the next incoming event, but it will not restart on subsequent events.

#### **Count Event Action**

The TCC can count events. When an event is received, the counter increases or decreases the value, depending on direction settings (CTRLBSET.DIR or CTRLBCLR.DIR).

The count event action is selected by the Event Action 0 bit group in the Event Control register (EVCTRL.EVACT0=0x5, COUNT).

#### **Direction Event Action**

The direction event action can be selected in the Event Control register (EVCTRL.EVACT1=0x2, DIR). When this event is used, the asynchronous event path specified in the event system must be configured or selected. The direction event action can be used to control the direction of the counter operation, depending on external events level. When received, the event level overrides the Direction settings (CTRLBSET.DIR or CTRLBCLR.DIR) and the direction bit value is updated accordingly.

#### **Increment Event Action**

The increment event action can be selected in the Event Control register (EVCTRL.EVACT0=0x4, INC) and can change the counter state when an event is received. When the TCE0 event (TCCx\_EV0) is received, the counter increments, whatever the direction setting (CTRLBSET.DIR or CTRLBCLR.DIR) is.

#### **Decrement Event Action**

The decrement event action can be selected in the Event Control register (EVCTRL.EVACT1=0x4, DEC) and can change the counter state when an event is received. When the TCE1 (TCCx\_EV1) event is received, the counter decrements, whatever the direction setting (CTRLBSET.DIR or CTRLBCLR.DIR) is.

# Non-recoverable Fault Event Action

Non-recoverable fault actions can be selected in the Event Control register (EVCTRL.EVACTn=0x7, FAULT). When received, the counter will be stopped and the output of the compare channels is overridden according to the Driver Control register settings (DRVCTRL.NREx and DRVCTRL.NRVx). TCE0 and TCE1 must be configured as asynchronous events.

# Event Action Off

If the event action is disabled (EVCTRL.EVACTn=0x0, OFF), enabling the counter will also start the counter.

# **Related Links**

© 2018 Microchip Technology Inc.

# TCC – Timer/Counter for Control Applications

#### 49.8.12 Interrupt Flag Status and Clear

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x2C<br>0x00000000<br>- |        |        |     |     |     |     |

|--------|-----------------------------------------|------------------------------------|--------|--------|-----|-----|-----|-----|

| Bit    | 23                                      | 22                                 | 21     | 20     | 19  | 18  | 17  | 16  |

|        |                                         |                                    | MCx    | MCx    | MCx | MCx | MCx | MCx |

| Access |                                         |                                    | R/W    | R/W    | R/W | R/W | R/W | R/W |

| Reset  |                                         |                                    | 0      | 0      | 0   | 0   | 0   | 0   |

|        |                                         |                                    |        |        |     |     |     |     |

| Bit    | 15                                      | 14                                 | 13     | 12     | 11  | 10  | 9   | 8   |

|        | FAULTx                                  | FAULTx                             | FAULTB | FAULTA | DFS |     |     |     |

| Access | R/W                                     | R/W                                | R/W    | R/W    | R/W |     |     |     |

| Reset  | 0                                       | 0                                  | 0      | 0      | 0   |     |     |     |

|        |                                         |                                    |        |        |     |     |     |     |

| Bit    | 7                                       | 6                                  | 5      | 4      | 3   | 2   | 1   | 0   |

|        |                                         |                                    |        |        | ERR | CNT | TRG | OVF |

| Access |                                         |                                    |        |        | R/W | R/W | R/W | R/W |

| Reset  |                                         |                                    |        |        | 0   | 0   | 0   | 0   |

Bits 21,20,19,18,17,16 – MCx Match or Capture Channel x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a match with the compare condition or once CCx register contain a valid capture value.

Writing a '0' to one of these bits has no effect.

Writing a '1' to one of these bits will clear the corresponding Match or Capture Channel x interrupt flag

In Capture operation, this flag is automatically cleared when CCx register is read.

#### Bits 15,14 – FAULTx Non-Recoverable Fault x Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Non-Recoverable Fault x occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Non-Recoverable Fault x interrupt flag.

#### Bit 13 – FAULTB Recoverable Fault B Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Recoverable Fault B occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Recoverable Fault B interrupt flag.

#### **Bit 12 – FAULTA** Recoverable Fault A Interrupt Flag

This flag is set on the next CLK\_TCC\_COUNT cycle after a Recoverable Fault B occurs.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Recoverable Fault B interrupt flag.

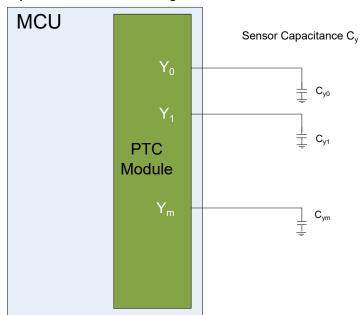

**PTC - Peripheral Touch Controller**

#### Figure 50-4. Self-Capacitance Sensor Arrangement

For more information about designing the touch sensor, refer to Buttons, Sliders and Wheels Touch Sensor Design Guide.

# 50.5.2 Analog-Digital Converter (ADC)

The PTC is using the ADC for signal conversion and acquisition. The ADC must be enabled and configured appropriately to allow correct behavior of the PTC.

# **Related Links**

45. ADC - Analog-to-Digital Converter

# 50.6 Functional Description

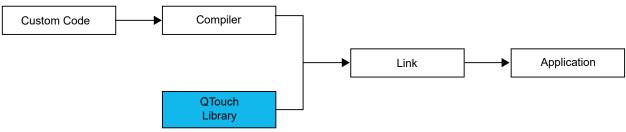

In order to access the PTC, the user must use the Atmel Start QTouch<sup>®</sup> Configurator to configure and link the QTouch Library firmware with the application software. QTouch Library can be used to implement buttons, sliders, and wheels in a variety of combinations on a single interface.

#### Figure 50-5. QTouch Library Usage

For more information about QTouch Library, refer to the QTouch Library Peripheral Touch Controller User Guide.

# I2S - Inter-IC Sound Controller

| DATASIZE[2:0] | Name | Description            |

|---------------|------|------------------------|

| 0x2           | 20   | 20 bits                |

| 0x3           | 18   | 18 bits                |

| 0x4           | 16   | 16 bits                |

| 0x5           | 16C  | 16 bits compact stereo |

| 0x6           | 8    | 8 bits                 |

| 0x7           | 8C   | 8 bits compact stereo  |

# Bit 7 – SLOTADJ Data Slot Formatting Adjust

This field defines left or right adjustment of data samples in the slot.

| SLOTADJ | Name  | Description                    |

|---------|-------|--------------------------------|

| 0x0     | RIGHT | Data is right adjusted in slot |

| 0x1     | LEFT  | Data is left adjusted in slot  |

# Bit 5 – CLKSEL Clock Unit Selection.

| CLKSEL | Name | Description      |

|--------|------|------------------|

| 0x0    | CLK0 | Use Clock Unit 0 |

| 0x1    | CLK1 | Use Clock Unit 1 |

# Bits 1:0 – SERMODE[1:0] Serializer Mode.

| SERMODE[1:0] | Name | Description                                    |

|--------------|------|------------------------------------------------|

| 0x0          | RX   | Receive                                        |

| 0x1          |      | Reserved                                       |

| 0x2          | PDM2 | Receive one PDM data on each serial clock edge |

| 0x3          |      | Reserved                                       |