#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                |

|----------------------------|---------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                    |

| Speed                      | 120MHz                                                                                |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                          |

| Number of I/O              | 81                                                                                    |

| Program Memory Size        | 512KB (512K x 8)                                                                      |

| Program Memory Type        | FLASH                                                                                 |

| EEPROM Size                | -                                                                                     |

| RAM Size                   | 192K x 8                                                                              |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                         |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                                 |

| Oscillator Type            | Internal                                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                         |

| Package / Case             | 100-TQFP                                                                              |

| Supplier Device Package    | 100-TQFP (14x14)                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame53n19a-au             |

|                            |                                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|        | Name:<br>Offset:<br>Reset:<br>Property: | INTFLAG<br>0x06<br>0x00<br>N/A |   |   |   |   |   |     |

|--------|-----------------------------------------|--------------------------------|---|---|---|---|---|-----|

| Bit    | 7                                       | 6                              | 5 | 4 | 3 | 2 | 1 | 0   |

|        |                                         |                                |   |   |   |   |   | EW  |

| Access |                                         |                                |   |   |   |   |   | R/W |

| Reset  |                                         |                                |   |   |   |   |   | 0   |

This flag is cleared by writing a '1' to it.

Interrupt Flag Status and Clear

20.8.6

This flag is set when an Early Warning interrupt occurs, as defined by the EWOFFSET bit group in EWCTRL.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit clears the Early Warning interrupt flag.

- Overflow (OVF): Indicates that the counter has reached its top value and wrapped to zero.

- Tamper (TAMPER): Indicates detection of valid signal on a tamper input pin or tamper event input.

- Compare (CMPn): Indicates a match between the counter value and the compare register.

- Alarm (ALARMn): Indicates a match between the clock value and the alarm register.

- Period n (PERn): The corresponding bit in the prescaler has toggled. Refer to 21.6.8.1 Periodic Intervals for details.

Each interrupt source has an interrupt flag associated with it. The interrupt flag in the Interrupt Flag Status and Clear (INTFLAG) register is set when the interrupt condition occurs. Each interrupt can be individually enabled by setting the corresponding bit in the Interrupt Enable Set register (INTENSET=1), and disabled by setting the corresponding bit in the Interrupt Enable Clear register (INTENCLR=1).

An interrupt request is generated when the interrupt flag is raised and the corresponding interrupt is enabled. The interrupt request remains active until either the interrupt flag is cleared, the interrupt is disabled or the RTC is reset. See the description of the INTFLAG registers for details on how to clear interrupt flags.

All interrupt requests from the peripheral are ORed together on system level to generate one combined interrupt request to the NVIC. Refer to the Nested Vector Interrupt Controller for details. The user must read the INTFLAG register to determine which interrupt condition is present.

**Note:** Interrupts must be globally enabled for interrupt requests to be generated. Refer to the Nested Vector Interrupt Controller for details.

#### **Related Links**

10.2 Nested Vector Interrupt Controller

#### 21.6.5 Events

The RTC can generate the following output events:

- Overflow (OVF): Generated when the counter has reached its top value and wrapped to zero.

- Tamper (TAMPER): Generated on detection of valid signal on a tamper input pin or tamper event input.

- Compare (CMPn): Indicates a match between the counter value and the compare register.

- Alarm (ALARM): Indicates a match between the clock value and the alarm register.

- Period n (PERn): The corresponding bit in the prescaler has toggled. Refer to 21.6.8.1 Periodic Intervals for details.

- Periodic Daily (PERD): Generated when the COUNT/CLOCK has incremented at a fixed period of time.

Setting the Event Output bit in the Event Control Register (EVCTRL.xxxEO=1) enables the corresponding output event. Writing a zero to this bit disables the corresponding output event. Refer to the EVSYS - Event System for details on configuring the event system.

The RTC can take the following actions on an input event:

• Tamper (TAMPEVT): Capture the RTC counter to the timestamp register. See *Tamper Detection*.

Writing a one to an Event Input bit into the Event Control register (EVCTRL.xxxEI) enables the corresponding action on input event. Writing a zero to this bit disables the corresponding action on input event.

#### **Related Links**

31. EVSYS - Event System

## SAMD5x/E5x Family Data Sheet GMAC - Ethernet MAC

| Bit   | Function                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | Used—must be zero for the GMAC to read data to the transmit buffer. The GMAC sets this to one for the first buffer of a frame once it has been successfully transmitted. Software must clear this bit before the buffer can be used again.                                                                                                                                                  |

| 30    | Wrap—marks last descriptor in transmit buffer descriptor list. This can be set for any buffer within the frame.                                                                                                                                                                                                                                                                             |

| 29    | Retry limit exceeded, transmit error detected                                                                                                                                                                                                                                                                                                                                               |

| 28    | Reserved.                                                                                                                                                                                                                                                                                                                                                                                   |

| 27    | Transmit frame corruption due to AHB error—set if an error occurs while midway through reading transmit frame from the AHB, including HRESP errors and buffers exhausted mid frame (if the buffers run out during transmission of a frame then transmission stops, FCS shall be bad and GTXER asserted).<br>Also set if single frame is too large for configured packet buffer memory size. |

| 26    | Late collision, transmit error detected.                                                                                                                                                                                                                                                                                                                                                    |

| 25:23 | Reserved                                                                                                                                                                                                                                                                                                                                                                                    |

| 22:20 | Transmit IP/TCP/UDP checksum generation offload errors:<br>000: No Error.                                                                                                                                                                                                                                                                                                                   |

|       | 001: The Packet was identified as a VLAN type, but the header was not fully complete, or had an error in it.                                                                                                                                                                                                                                                                                |

|       | 010: The Packet was identified as a SNAP type, but the header was not fully complete, or had an error in it.                                                                                                                                                                                                                                                                                |

|       | 011: The Packet was not of an IP type, or the IP packet was invalidly short, or the IP was not of type IPv4/IPv6.                                                                                                                                                                                                                                                                           |

|       | 100: The Packet was not identified as VLAN, SNAP or IP.                                                                                                                                                                                                                                                                                                                                     |

|       | 101: Non supported packet fragmentation occurred. For IPv4 packets, the IP checksum was generated and inserted.                                                                                                                                                                                                                                                                             |

|       | 110: Packet type detected was not TCP or UDP. TCP/UDP checksum was therefore not generated. For IPv4 packets, the IP checksum was generated and inserted.                                                                                                                                                                                                                                   |

|       | 111: A premature end of packet was detected and the TCP/UDP checksum could not be generated.                                                                                                                                                                                                                                                                                                |

| 19:17 | Reserved                                                                                                                                                                                                                                                                                                                                                                                    |

| 16    | No CRC to be appended by MAC. When set, this implies that the data in the buffers already contains a valid CRC, hence no CRC or padding is to be appended to the current frame by the MAC.<br>This control bit must be set for the first buffer in a frame and will be ignored for the subsequent buffers of a frame.                                                                       |

|       | Note that this bit must be clear when using the transmit IP/TCP/UDP checksum generation offload, otherwise checksum generation and substitution will not occur.                                                                                                                                                                                                                             |

| 15    | Last buffer, when set this bit will indicate the last buffer in the current frame has been reached.                                                                                                                                                                                                                                                                                         |

## SAMD5x/E5x Family Data Sheet

## **GMAC** - Ethernet MAC

| Frame Segment                 | Value    |

|-------------------------------|----------|

| UDP (Octet 23)                | 11       |

| IP stuff (Octets 24–29)       |          |

| IP DA (Octets 30–33)          | E000006B |

| Source IP port (Octets 34–35) | —        |

| Dest IP port (Octets 36–37)   | 013F     |

| Other stuff (Octets 38–41)    |          |

| Message type (Octet 42)       | 02       |

| Version PTP (Octet 43)        | 02       |

#### Table 24-9. Example of Sync Frame in 1588 Version 2 (UDP/IPv6) Format

| Frame Segment                 | Value                                  |

|-------------------------------|----------------------------------------|

| Preamble/SFD                  | 55555555555555555555555555555555555555 |

| DA (Octets 0–5)               |                                        |

| SA (Octets 6–11)              |                                        |

| Type (Octets 12–13)           | 86dd                                   |

| IP stuff (Octets 14–19)       |                                        |

| UDP (Octet 20)                | 11                                     |

| IP stuff (Octets 21–37)       | —                                      |

| IP DA (Octets 38–53)          | FF0X0000000018                         |

| Source IP port (Octets 54–55) |                                        |

| Dest IP port (Octets 56–57)   | 013F                                   |

| Other stuff (Octets 58–61)    | —                                      |

| Message type (Octet 62)       | 00                                     |

| Other stuff (Octets 63–93)    | -                                      |

| Version PTP (Octet 94)        | 02                                     |

#### Table 24-10. Example of Pdelay\_Resp Frame in 1588 Version 2 (UDP/IPv6) Format

| Frame Segment           | Value                                  |

|-------------------------|----------------------------------------|

| Preamble/SFD            | 55555555555555555555555555555555555555 |

| DA (Octets 0–5)         |                                        |

| SA (Octets 6–11)        |                                        |

| Type (Octets 12–13)     | 86dd                                   |

| IP stuff (Octets 14–19) | -                                      |

### NVMCTRL – Nonvolatile Memory Controller

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x10    |

| Reset:    | 0x0000  |

| Property: | -       |

Interrupt Flag Status and Clear

25.8.6

| Bit    | 15   | 14   | 13    | 12    | 11    | 10     | 9       | 8        |

|--------|------|------|-------|-------|-------|--------|---------|----------|

|        |      |      |       |       |       | SEEWRC | SEESOVF | SEESFULL |

| Access |      |      |       |       |       | R/W    | R/W     | R/W      |

| Reset  |      |      |       |       |       | 0      | 0       | 0        |

|        |      |      |       |       |       |        |         |          |

| Bit    | 7    | 6    | 5     | 4     | 3     | 2      | 1       | 0        |

|        | SUSP | NVME | ECCDE | ECCSE | LOCKE | PROGE  | ADDRE   | DONE     |

| Access | R/W  | R/W  | R     | R     | R/W   | R/W    | R/W     | R/W      |

| Reset  | 0    | 0    | 0     | 0     | 0     | 0      | 0       | 0        |

## Bit 10 – SEEWRC SEE Write Completed

- Unbuffered mode:

- 0: AHB write is pending.

1: AHB write has completed, and NVM is programmed with correct values.

- Buffered mode:

- 0: AHB write is pending.

- 1: AHB write has completed.

- If SEESTAT.LOAD=0, then the NVM is programmed with correct values.

If SEESTAT.LOAD=1, then data is still pending in the Page Buffer.

#### Bit 9 – SEESOVF Active SEES Overflow

0: No SEES overflow have been detected since the last clear.

1: At least SEES overflow has been detected since the last clear.

This bit can be cleared by writing a one to its bit location.

#### Bit 8 - SEESFULL Active SEES Full

0: The active SEES is not full

1: The active SEES is Full, meaning that the next write will fail if the active sector is not reallocated.

This bit can be cleared by writing a one to its bit location.

#### Bit 7 – SUSP Suspended Write Or Erase Operation

0: No write/suspend has occurred since the last clear.

1: A write or erase operation has been suspended since the last clear.

This bit can be cleared by writing a one to its bit location.

### **ICM - Integrity Check Monitor**

#### 26.8.7 Interrupt Status Register

| Name:     | ISR       |

|-----------|-----------|

| Offset:   | 0x1C      |

| Reset:    | 0x0       |

| Property: | Read-Only |

| Bit    | 31       | 30  | 29             | 28 | 27  | 26    | 25    | 24   |

|--------|----------|-----|----------------|----|-----|-------|-------|------|

|        |          |     |                |    |     |       |       | URAD |

| Access |          |     |                |    |     |       |       | R    |

| Reset  |          |     |                |    |     |       |       | 0    |

|        |          |     |                |    |     |       |       |      |

| Bit    | 23       | 22  | 21             | 20 | 19  | 18    | 17    | 16   |

|        |          | RSU | <b>I</b> [3:0] |    |     | REC   | [3:0] |      |

| Access | R        | R   | R              | R  | R   | R     | R     | R    |

| Reset  | 0        | 0   | 0              | 0  | 0   | 0     | 0     | 0    |

|        |          |     |                |    |     |       |       |      |

| Bit    | 15       | 14  | 13             | 12 | 11  | 10    | 9     | 8    |

|        |          | RWC | C[3:0]         |    |     | RBE   | [3:0] |      |

| Access | R        | R   | R              | R  | R   | R     | R     | R    |

| Reset  | 0        | 0   | 0              | 0  | 0   | 0     | 0     | 0    |

|        |          |     |                |    |     |       |       |      |

| Bit    | 7        | 6   | 5              | 4  | 3   | 2     | 1     | 0    |

|        | RDM[3:0] |     |                |    | RHC | [3:0] |       |      |

| Access | R        | R   | R              | R  | R   | R     | R     | R    |

| Reset  | 0        | 0   | 0              | 0  | 0   | 0     | 0     | 0    |

**Bit 24 – URAD** Undefined Register Access Detection Status The URAD bit is only reset by the SWRST bit in the CTRL register.

The Undefined Register Access Trace bit field in the Undefined Access Status Register (UASR.URAT) indicates the unspecified access type.

| Value | Description                                                                    |

|-------|--------------------------------------------------------------------------------|

| 0     | No undefined register access has been detected since the last SWRST.           |

| 1     | At least one undefined register access has been detected since the last SWRST. |

Bits 23:20 – RSU[3:0] Region Status Updated Detected

RSU[i] is set when a region status updated condition is detected.

Bits 19:16 – REC[3:0] Region End bit Condition Detected

REC[i] is set when an end bit condition is detected.

Bits 15:12 – RWC[3:0] Region Wrap Condition Detected

RWC[i] is set when a wrap condition is detected.

#### Bits 11:8 - RBE[3:0] Region Bus Error

RBE[i] is set when a bus error is detected while hashing memory region i.

© 2018 Microchip Technology Inc.

#### 32.9.1 Data Direction

| Name:     | DIR                  |

|-----------|----------------------|

| Offset:   | 0x00                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to configure one or more I/O pins as an input or output. This register can be manipulated without doing a read-modify-write operation by using the Data Direction Toggle (DIRTGL), Data Direction Clear (DIRCLR) and Data Direction Set (DIRSET) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31 | 30 | 29 | 28    | 27     | 26 | 25 | 24 |

|--------|----|----|----|-------|--------|----|----|----|

|        |    |    |    | DIR[3 | 81:24] |    |    |    |

| Access | RW | RW | RW | RW    | RW     | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

|        |    |    |    |       |        |    |    |    |

| Bit    | 23 | 22 | 21 | 20    | 19     | 18 | 17 | 16 |

|        |    |    |    | DIR[2 | 23:16] |    |    |    |

| Access | RW | RW | RW | RW    | RW     | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

|        |    |    |    |       |        |    |    |    |

| Bit    | 15 | 14 | 13 | 12    | 11     | 10 | 9  | 8  |

|        |    |    |    | DIR[  | 15:8]  |    |    |    |

| Access | RW | RW | RW | RW    | RW     | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

|        |    |    |    |       |        |    |    |    |

| Bit    | 7  | 6  | 5  | 4     | 3      | 2  | 1  | 0  |

|        |    |    |    | DIR   | [7:0]  |    |    |    |

| Access | RW | RW | RW | RW    | RW     | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0      | 0  | 0  | 0  |

|        |    |    |    |       |        |    |    |    |

#### Bits 31:0 - DIR[31:0] Port Data Direction

These bits set the data direction for the individual I/O pins in the PORT group.

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 0     | The corresponding I/O pin in the PORT group is configured as an input.  |

| 1     | The corresponding I/O pin in the PORT group is configured as an output. |

#### 32.9.7 Data Output Value Set

Name:OUTSETOffset:0x18Reset:0x00000000Property:PAC Write-Protection

This register allows the user to set one or more output I/O pin drive levels high, without doing a readmodify-write operation. Changes in this register will also be reflected in the Data Output Value (OUT), Data Output Value Toggle (OUTTGL) and Data Output Value Clear (OUTCLR) registers.

**Tip:** The I/O pins are assembled in pin groups ("PORT groups") with up to 32 pins. Group 0 consists of the PA pins, group 1 is for the PB pins, etc. Each pin group has its own PORT registers, with a 0x80 address spacing. For example, the register address offset for the Data Direction (DIR) register for group 0 (PA00 to PA31) is 0x00, and the register address offset for the DIR register for group 1 (PB00 to PB31) is 0x80.

| Bit    | 31 | 30 | 29 | 28    | 27       | 26 | 25 | 24 |

|--------|----|----|----|-------|----------|----|----|----|

|        |    |    |    | OUTSE | T[31:24] |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 23 | 22 | 21 | 20    | 19       | 18 | 17 | 16 |

|        |    |    |    | OUTSE | T[23:16] |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 15 | 14 | 13 | 12    | 11       | 10 | 9  | 8  |

|        |    |    |    | OUTSE | T[15:8]  |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

| Bit    | 7  | 6  | 5  | 4     | 3        | 2  | 1  | 0  |

|        |    |    |    | OUTS  | ET[7:0]  |    |    |    |

| Access | RW | RW | RW | RW    | RW       | RW | RW | RW |

| Reset  | 0  | 0  | 0  | 0     | 0        | 0  | 0  | 0  |

|        |    |    |    |       |          |    |    |    |

#### Bits 31:0 - OUTSET[31:0] PORT Data Output Value Set

Writing '0' to a bit has no effect.

Writing '1' to a bit will set the corresponding bit in the OUT register, which sets the output drive level high for I/O pins configured as outputs via the Data Direction register (DIR). For pins configured as inputs via Data Direction register (DIR) with pull enabled via the Pull Enable register (PULLEN), these bits will set the input pull direction to an internal pull-up.

## SAMD5x/E5x Family Data Sheet SERCOM USART - SERCOM Synchronous and Asyn...

#### 34.8.12 Length

Name:LENGTHOffset:0x22Reset:0x00Property:PAC Write-Protection, Write-Synchronized

| Bit    | 15  | 14  | 13  | 12  | 11    | 10  | 9    | 8      |

|--------|-----|-----|-----|-----|-------|-----|------|--------|

|        |     |     |     |     |       |     | LENE | N[1:0] |

| Access |     |     |     |     |       |     | R/W  | R/W    |

| Reset  |     |     |     |     |       |     | 0    | 0      |

|        |     |     |     |     |       |     |      |        |

| Bit    | 7   | 6   | 5   | 4   | 3     | 2   | 1    | 0      |

|        |     |     |     | LEN | [7:0] |     |      |        |

| Access | R/W | R/W | R/W | R/W | R/W   | R/W | R/W  | R/W    |

| Reset  | 0   | 0   | 0   | 0   | 0     | 0   | 0    | 0      |

#### Bits 9:8 – LENEN[1:0] Data Length Enable

In 32-bit Extension mode, this bit field configures the length counter either for transmit or receive transactions.

| Value | Description                         |

|-------|-------------------------------------|

| 0x0   | Length counter disabled             |

| 0x1   | Length counter enabled for transmit |

| 0x2   | Length counter enabled for receive  |

| 0x3   | Reserved                            |

#### Bits 7:0 – LEN[7:0] Data Length

In 32-bit Extension mode, this bit field configures the data length after which the flags INTFLAG.RXC or INTFLAG.DRE are raised.

| Value   | Description                        |

|---------|------------------------------------|

| 0x00    | Reserved if LENEN=0x1 or LENEN=0x2 |

| 0x01-0x | Data Length                        |

| FF      |                                    |

#### 38.8.6.5 Pipe Status Register n

| Name:     | PSTATUS              |

|-----------|----------------------|

| Offset:   | 0x106 + (n x 0x20)   |

| Reset:    | 0x00                 |

| Property: | PAC Write-Protection |

| Bit    | 7      | 6      | 5 | 4       | 3 | 2     | 1 | 0    |

|--------|--------|--------|---|---------|---|-------|---|------|

|        | BK1RDY | BK0RDY |   | PFREEZE |   | CURBK |   | DTGL |

| Access | R      | R      |   | R       |   | R     |   | R    |

| Reset  | 0      | 0      |   | 0       |   | 0     |   | 0    |

#### Bit 7 – BK1RDY Bank 1 is ready

Writing a one to the bit EPSTATUSCLR.BK1RDY will clear this bit.

Writing a one to the bit EPSTATUSSET.BK1RDY will set this bit.

This bank is not used for Control pipe.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The bank number 1 is not ready: For IN the bank is empty. For Control/OUT the bank is not      |

|       | yet fill in.                                                                                   |

| 1     | The bank number 1 is ready: For IN the bank is filled full. For Control/OUT the bank is filled |

|       | in.                                                                                            |

#### Bit 6 – BK0RDY Bank 0 is ready

Writing a one to the bit EPSTATUSCLR.BK0RDY will clear this bit.

Writing a one to the bit EPSTATUSSET.BK0RDY will set this bit.

This bank is the only one used for Control pipe.

| Value | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| 0     | The bank number 0 is not ready: For IN the bank is not empty. For Control/OUT the bank is      |

|       | not yet fill in.                                                                               |

| 1     | The bank number 0 is ready: For IN the bank is filled full. For Control/OUT the bank is filled |

|       | in.                                                                                            |

#### Bit 4 – PFREEZE Pipe Freeze

Writing a one to the bit EPSTATUSCLR.PFREEZE will clear this bit.

Writing a one to the bit EPSTATUSSET.PFREEZE will set this bit.

This bit is also set by the hardware:

- When a STALL handshake has been received.

- After a PIPE has been enabled (rising of bit PEN.N).

- When an LPM transaction has completed whatever handshake is returned or the transaction was timed-out.

- When a pipe transfer was completed with a pipe error. See 38.8.6.6 PINTFLAG register.

## SAMD5x/E5x Family Data Sheet

### SD/MMC Host Controller ...

| Value | Name    | Description                                 |

|-------|---------|---------------------------------------------|

| 0     | MASKED  | The DATCRC status flag in EISTR is masked.  |

| 1     | ENABLED | The DATCRC status flag in EISTR is enabled. |

Bit 4 – DATTEO Data Timeout Error Status Enable

| Value | Name    | Description                                 |

|-------|---------|---------------------------------------------|

| 0     | MASKED  | The DATTEO status flag in EISTR is masked.  |

| 1     | ENABLED | The DATTEO status flag in EISTR is enabled. |

Bit 3 – CMDIDX Command Index Error Status Enable

| Value | Name    | Description                                 |

|-------|---------|---------------------------------------------|

| 0     | MASKED  | The CMDIDX status flag in EISTR is masked.  |

| 1     | ENABLED | The CMDIDX status flag in EISTR is enabled. |

Bit 2 – CMDEND Command End Bit Error Status Enable

| Value | Name    | Description                                 |

|-------|---------|---------------------------------------------|

| 0     | MASKED  | The CMDEND status flag in EISTR is masked.  |

| 1     | ENABLED | The CMDEND status flag in EISTR is enabled. |

#### Bit 1 – CMDCRC Command CRC Error Status Enable

| Value | Name    | Description                                 |

|-------|---------|---------------------------------------------|

| 0     | MASKED  | The CMDCRC status flag in EISTR is masked.  |

| 1     | ENABLED | The CMDCRC status flag in EISTR is enabled. |

#### **Bit 0 – CMDTEO** Command Timeout Error Status Enable

| Value | Name    | Description                                 |

|-------|---------|---------------------------------------------|

| 0     | MASKED  | The CMDTEO status flag in EISTR is masked.  |

| 1     | ENABLED | The CMDTEO status flag in EISTR is enabled. |

#### 43.3.5.2.7 Constraints

The following combinations of input values should be avoided in the case of a modular reduction 'alone', meaning that it has not been requested as an option of any other command:

- nu1ModBase,nu1CnsBase, nu1XBase,nu1PrecompBase,nu1ExpBase are not aligned on 32-bit boundaries

- {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8}, {nu1XBase, u2ModLength + 16}, {nu1PrecompBase, <PrecompLength>} are not in Crypto RAM

- {nu1ExpBase,u2ExpLength + 4} has no part in Crypto RAM and PUKCL EXPMOD EXPINPUKCCRAM is specified

- u2ModLength or u2ExpLength are either: < 4, > 0xffc or not a 32-bit length

- None or both PUKCL\_EXPMOD\_REGULARRSA and PUKCL\_EXPMOD\_FASTRSA are specified.

- {nu1PrecompBase,<PrecompLength>} overlaps with either: {nu1ModBase, u2ModLength +4}, {nu1CnsBase, u2ModLength + 8} {nu1XBase, u2ModLength + 16} or {nu1ExpBase, u2ExpLength + 4}

- {nu1XBase,u2ModLength + 16} overlaps with either: {nu1ModBase, u2ModLength + 4}, {nu1CnsBase, u2ModLength + 8} or {nu1ExpBase, u2ExpLength + 4}

- {nu1ModBase, u2ModLength + 4} overlaps {nu1CnsBase, u2ModLength +8}

#### 43.3.5.2.8 Maximum Sizes for the Modular Exponentiation

The following table provides the maximum sizes for the Modular Exponentiation, depending on the window size and the presence of the exponent in Crypto RAM.

- The figures below are calculated supposing that u2ExpLength =u2ModLength.

- In case of the PUKCL\_EXPMOD\_EXPINPUKCCRAM option is specified, for the computation of the maximum acceptable size, it is assumed the Exponent is entirely in the Crypto RAM and its length is equal to the Modulus one.

- Otherwise, the Exponent is entirely out of the Crypto RAM and so the computation do not depend on its length.

The TRNG interrupts can be used to wake up the device from sleep modes. Events connected to the event system can trigger other operations in the system without exiting sleep modes.

#### **Related Links**

PM – Power Manager

Sleep Mode Operation

#### 44.5.3 Clocks

The TRNG bus clock (CLK\_TRNG\_APB) can be enabled and disabled in the Main Clock module, and the default state of CLK\_TRNG\_APB can be found in *Peripheral Clock Masking*.

#### Related Links

15.6.2.6 Peripheral Clock Masking

#### 44.5.4 DMA

Not applicable.

#### 44.5.5 Interrupts

The interrupt request line is connected to the interrupt controller. Using the TRNG interrupt(s) requires the interrupt controller to be configured first. Refer to NVIC - Nested Interrupt *Nested Vector Interrupt Controller* for details.

#### Related Links

10.2 Nested Vector Interrupt Controller

#### 44.5.6 Events

TRNG can generate Events that are used by the Event System (EVSYS) and EVSYS users.

TRNG cannot use any Events from other peripherals, as it is not an Event User.

#### Related Links

31. EVSYS – Event System

#### 44.5.7 Debug Operation

When the CPU is halted in debug mode the TRNG continues normal operation. If the TRNG is configured in a way that requires it to be periodically serviced by the CPU through interrupts or similar, improper operation or data loss may result during debugging.

#### 44.5.8 Register Access Protection

All registers with write-access are optionally write-protected by the Peripheral Access Controller (PAC), except the following register:

Interrupt Flag Status and Clear (INTFLAG) register

Optional write-protection by the Peripheral Access Controller (PAC) is denoted by the "PAC Write-Protection" property in each individual register description.

#### 44.5.9 Analog Connections

Not applicable.

#### 46.8.4 Interrupt Enable Clear

Name:INTENCLROffset:0x04Reset:0x00Property:PAC Write-Protection

This register allows the user to disable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Set register (INTENSET).

| Bit    | 7 | 6 | 5 | 4    | 3 | 2 | 1     | 0     |

|--------|---|---|---|------|---|---|-------|-------|

|        |   |   |   | WIN0 |   |   | COMPx | COMPx |

| Access |   |   |   | R/W  |   |   | R/W   | R/W   |

| Reset  |   |   |   | 0    |   |   | 0     | 0     |

#### Bit 4 – WIN0 Window 0 Interrupt Enable

Reading this bit returns the state of the Window 0 interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit disables the Window 0 interrupt.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Window 0 interrupt is disabled. |

| 1     | The Window 0 interrupt is enabled.  |

#### **Bits 1,0 – COMPx** Comparator x Interrupt Enable

Reading this bit returns the state of the Comparator x interrupt enable.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit disables the Comparator x interrupt.

| Value | Description                             |

|-------|-----------------------------------------|

| 0     | The Comparator x interrupt is disabled. |

| 1     | The Comparator x interrupt is enabled.  |

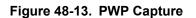

$$f = \frac{1}{T}$$

dutyCycle =  $\frac{t_p}{T}$

Selecting PWP in the Event Action bit group in the Event Control register (EVCTRL.EVACT) enables the TC to perform one capture action on the rising edge and the other one on the falling edge. The period T will be captured into CC1 and the pulse width  $t_p$  in CC0. EVCTRL.EVACT=PPW (period and pulse-width) offers identical functionality, but will capture T into CC0 and  $t_p$  into CC1.

The TC Event Input Invert Enable bit in the Event Control register (EVCTRL.TCINV) is used to select whether the wraparound should occur on the rising edge or the falling edge. If EVCTRL.TCINV=1, the wraparound will happen on the falling edge. In case pin capture is enabled, this can also be achieved by modifying the value of the DRVCTRL.INVENx bit.

The TC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Interrupt flag (INTFLAG.MCx) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

**Note:** The corresponding capture is working only if the channel is enabled in capture mode (CTRLA.CAPTENx=1). If not, the capture action is ignored and the channel is enabled in compare mode of operation. Consequently, both channels must be enabled in order to fully characterize the input.

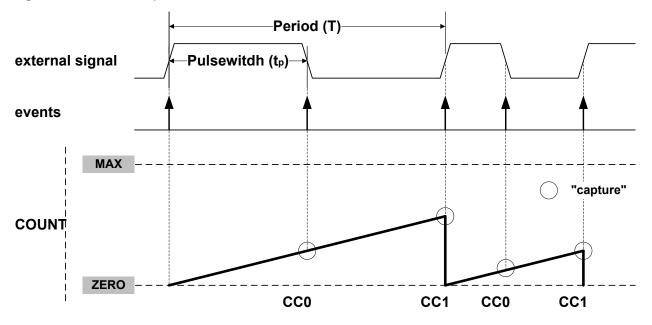

#### 48.6.2.8.3 Pulse-Width Capture Action

The TC performs the input capture on the falling edge of the input signal. When the edge is detected, the counter value is cleared and the TC stops counting. When a rising edge is detected on the input signal, the counter restarts the counting operation. To enable the operation on opposite edges, the input signal to capture must be inverted (refer to DRVCTRL.INVEN or EVCTRL.TCEINV).

## SAMD5x/E5x Family Data Sheet

#### TC – Timer/Counter

The TC can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Interrupt flag (INTFLAG.MCx) is still set, the new timestamp will not be stored and INTFLAG.ERR will be set.

#### 48.6.3 Additional Features

#### 48.6.3.1 One-Shot Operation

When one-shot is enabled, the counter automatically stops on the next counter overflow or underflow condition. When the counter is stopped, the Stop bit in the Status register (STATUS.STOP) is automatically set and the waveform outputs are set to zero.

One-shot operation is enabled by writing a '1' to the One-Shot bit in the Control B Set register (CTRLBSET.ONESHOT), and disabled by writing a '1' to CTRLBCLR.ONESHOT. When enabled, the TC will count until an overflow or underflow occurs and stops counting operation. The one-shot operation can be restarted by a re-trigger software command, a re-trigger event, or a start event. When the counter restarts its operation, STATUS.STOP is automatically cleared.

#### 48.6.3.2 Time-Stamp Capture

This feature is enabled when the Capture Time Stamp (STAMP) Event Action in Event Control register (EVCTRL.EVACT) is selected. The counter TOP value must be smaller than MAX.

When a capture event is detected, the COUNT value is copied into the corresponding Channel x Compare/Capture Value (CCx) register. In case of an overflow, the MAX value is copied into the corresponding CCx register.

When a valid captured value is present in the capture channel register, the corresponding Capture Channel x Interrupt Flag (INTFLAG.MCx) is set.

The timer/counter can detect capture overflow of the input capture channels: When a new capture event is detected while the Capture Channel interrupt flag (INTFLAG.MCx) is still set, the new time-stamp will not be stored and INTFLAG.ERR will be set.

#### 49.8.11 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x28                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

| Bit    | 23     | 22     | 21     | 20     | 19  | 18  | 17  | 16  |

|--------|--------|--------|--------|--------|-----|-----|-----|-----|

|        |        |        | MCx    | MCx    | MCx | MCx | MCx | MCx |

| Access |        |        | R/W    | R/W    | R/W | R/W | R/W | R/W |

| Reset  |        |        | 0      | 0      | 0   | 0   | 0   | 0   |

|        |        |        |        |        |     |     |     |     |

| Bit    | 15     | 14     | 13     | 12     | 11  | 10  | 9   | 8   |

|        | FAULTx | FAULTx | FAULTB | FAULTA | DFS |     |     |     |

| Access | R/W    | R/W    | R/W    | R/W    | R/W |     |     |     |

| Reset  | 0      | 0      | 0      | 0      | 0   |     |     |     |

|        |        |        |        |        |     |     |     |     |

| Bit    | 7      | 6      | 5      | 4      | 3   | 2   | 1   | 0   |

|        |        |        |        |        | ERR | CNT | TRG | OVF |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

# **Bits 21,20,19,18,17,16 – MCx** Match or Capture Channel x Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the corresponding Match or Capture Channel x Interrupt Disable/Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

### Bits 15,14 – FAULTx Non-Recoverable Fault x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Non-Recoverable Fault x Interrupt Disable/Enable bit, which enables the Non-Recoverable Fault x interrupt.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The Non-Recoverable Fault x interrupt is disabled. |

| 1     | The Non-Recoverable Fault x interrupt is enabled.  |

#### Bit 13 – FAULTB Recoverable Fault B Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Recoverable Fault B Interrupt Disable/Enable bit, which enables the Recoverable Fault B interrupt.

## SAMD5x/E5x Family Data Sheet

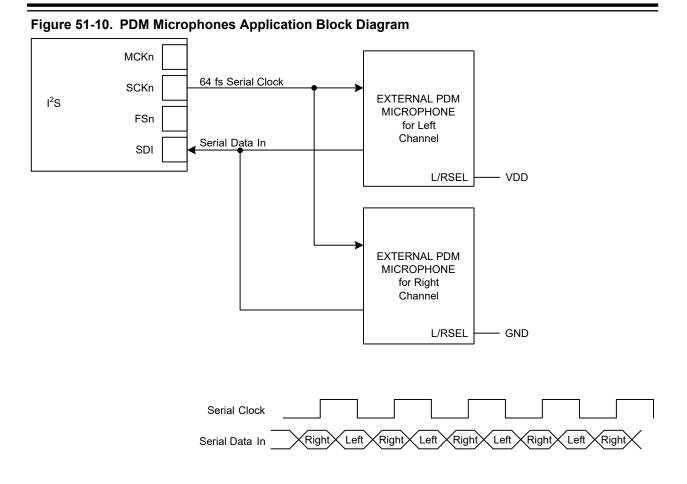

**I2S - Inter-IC Sound Controller**

© 2018 Microchip Technology Inc.

### **I2S - Inter-IC Sound Controller**

#### 51.9.5 Interrupt Flag Status and Clear

| Name:     | INTFLAG |

|-----------|---------|

| Offset:   | 0x14    |

| Reset:    | 0x0000  |

| Property: | -       |

| Bit    | 15 | 14 | 13    | 12    | 11 | 10 | 9      | 8      |

|--------|----|----|-------|-------|----|----|--------|--------|

|        |    |    | TXURx | TXURx |    |    | TXRDYx | TXRDYx |

| Access |    |    | R/W   | R/W   |    |    | R/W    | R/W    |

| Reset  |    |    | 0     | 0     |    |    | 0      | 0      |

|        |    |    |       |       |    |    |        |        |

| Bit    | 7  | 6  | 5     | 4     | 3  | 2  | 1      | 0      |

|        |    |    | RXORx | RXORx |    |    | RXRDYx | RXRDYx |

| Access |    |    | R/W   | R/W   |    |    | R/W    | R/W    |

| Reset  |    |    | 0     | 0     |    |    | 0      | 0      |

#### Bits 13,12 – TXURx Transmit Underrun x [x=1..0]

This flag is cleared by writing a '1' to it.

This flag is set when a Transmit Underrun condition occurs in Sequencer x, and will generate an interrupt request if INTENCLR/SET.TXURx is set to '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transmit Underrun x interrupt flag.

#### Bits 9,8 – TXRDYx Transmit Ready x [x=1..0]

This flag is cleared by writing to DATAx register or writing a '1' to it.

This flag is set when Sequencer x is ready to accept a new data word to be transmitted, and will generate an interrupt request if INTENCLR/SET.TXRDYx is set to '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Transmit Ready x interrupt flag.

#### Bits 4,5 – RXORx Receive Overrun x [x=1..0]

This flag is cleared by writing a '1' to it.

This flag is set when a Receive Overrun condition occurs in Sequencer x, and will generate an interrupt request if INTENCLR/SET.RXORx is set to '1'.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear the Receive Overrun x interrupt flag.

#### Bits 1,0 – RXRDYx Receive Ready x [x=1..0]

This flag is cleared by reading from DATAx register or writing a '1' to it.

This flag is set when a Sequencer x has received a new data word, and will generate an interrupt request if INTENCLR/SET.RXRDYx is set to '1'.

Writing a '0' to this bit has no effect.

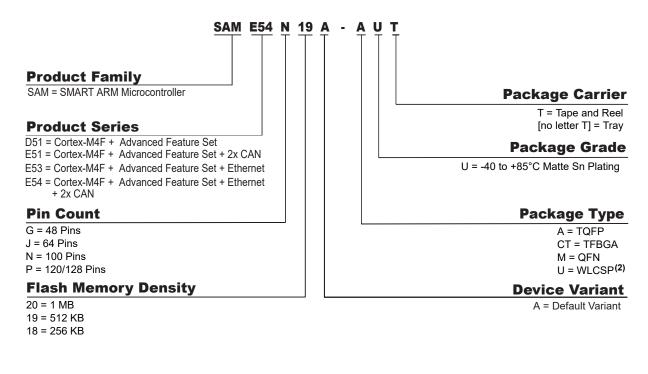

### **Product Identification System**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

### **Microchip Devices Code Protection Feature**

Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

## Legal Notice

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your

© 2018 Microchip Technology Inc.