#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                                        |

|----------------------------|-----------------------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M4F                                                                              |

| Core Size                  | 32-Bit Single-Core                                                                            |

| Speed                      | 120MHz                                                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Number of I/O              | 81                                                                                            |

| Program Memory Size        | 1MB (1M x 8)                                                                                  |

| Program Memory Type        | FLASH                                                                                         |

| EEPROM Size                |                                                                                               |

| RAM Size                   | 256K x 8                                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.63V                                                                                 |

| Data Converters            | A/D 28x12b; D/A 2x12b                                                                         |

| Oscillator Type            | Internal                                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                             |

| Mounting Type              | Surface Mount                                                                                 |

| Package / Case             | 100-TQFP                                                                                      |

| Supplier Device Package    | 100-TQFP (14x14)                                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atsame54n20a-au                     |

|                            |                                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

CMCC - Cortex M Cache Controller

| Offset | Name | Bit Pos. |                 |  |         |           |  |  |  |

|--------|------|----------|-----------------|--|---------|-----------|--|--|--|

|        |      | 7:0      |                 |  | EVENT_  | CNT[7:0]  |  |  |  |

| 0x34   | MOD  | 15:8     | EVENT_CNT[15:8] |  |         |           |  |  |  |

| 0x34   | MSR  | 23:16    |                 |  | EVENT_C | NT[23:16] |  |  |  |

|        |      | 31:24    |                 |  | EVENT_C | NT[31:24] |  |  |  |

## 11.10 Register Description

### SUPC – Supply Controller

| Value | Description                                                                   |

|-------|-------------------------------------------------------------------------------|

| 0     | In standby sleep mode, the BOD33 is enabled and configured in normal mode.    |

| 1     | In standby sleep mode, the BOD33 is enabled and configured in low power mode. |

#### Bits 3:2 – ACTION[1:0] BOD33 Action

These bits are used to select the BOD33 action when the supply voltage crosses below the BOD33 threshold.

These bits are loaded from NVM User Row at start-up.

This field is not synchronized.

| Value | Name  | Description                                             |

|-------|-------|---------------------------------------------------------|

| 0x0   | NONE  | No action                                               |

| 0x1   | RESET | The BOD33 generates a reset                             |

| 0x2   | INT   | The BOD33 generates an interrupt                        |

| 0x3   | BKUP- | The BOD33 puts the device in battery backup sleep mode. |

#### Bit 1 – ENABLE Enable

This bit is loaded from NVM User Row at start-up.

This bit is not enable-protected.

| Value | Description        |

|-------|--------------------|

| 0     | BOD33 is disabled. |

| 1     | BOD33 is enabled.  |

#### Related Links

9.4 NVM User Page Mapping

#### Bit 6 – RUNSTDBY Run In Standby

The bit controls how the voltage reference behaves during standby sleep mode.

| Value | Description                                                                                                                                                                                                                                       |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0     | The voltage reference is halted during standby sleep mode.                                                                                                                                                                                        |

| 1     | The voltage reference is not stopped in standby sleep mode. If VREF.ONDEMAND=1, the voltage reference will be running when a peripheral is requesting it. If VREF.ONDEMAND=0, the voltage reference will always be running in standby sleep mode. |

#### Bit 3 – TSSEL Temperature Sensor Channel Selection

| Value | Description                                      |

|-------|--------------------------------------------------|

| 0     | The Temperature Sensor PTAT channel is selected. |

| 1     | The Temperature Sensor CTAT channel is selected. |

#### **Bit 2 – VREFOE** Voltage Reference Output Enable

| Value | Description                                                                     |

|-------|---------------------------------------------------------------------------------|

| 0     | The Voltage Reference output (INTREF) is not available as an ADC input channel. |

| 1     | The Voltage Reference output (INTREF) is routed to an ADC input channel.        |

#### Bit 1 – TSEN Temperature Sensor Enable

| Value | Description                                                       |

|-------|-------------------------------------------------------------------|

| 0     | Temperature Sensor is disabled.                                   |

| 1     | Temperature Sensor is enabled and routed to an ADC input channel. |

#### 22.8.9 Interrupt Pending

| Name:     | INTPEND |

|-----------|---------|

| Offset:   | 0x20    |

| Reset:    | 0x0000  |

| Property: | -       |

This register allows the user to identify the lowest DMA channel with pending interrupt. An interrupt that handles several channels should consult the INTPEND register to find out which channel number has priority (ignoring/filtering each channel that has its own interrupt line). An interrupt dedicated to only one channel must not use the INTPEND register.

| Bit    | 15   | 14   | 13   | 12     | 11  | 10      | 9     | 8    |

|--------|------|------|------|--------|-----|---------|-------|------|

|        | PEND | BUSY | FERR | CRCERR |     | SUSP    | TCMPL | TERR |

| Access | R    | R    | R    | R/W    |     | R/W     | R/W   | R/W  |

| Reset  | 0    | 0    | 0    | 0      |     | 0       | 0     | 0    |

|        |      |      |      |        |     |         |       |      |

| Bit    | 7    | 6    | 5    | 4      | 3   | 2       | 1     | 0    |

|        |      |      |      |        |     | ID[4:0] |       |      |

| Access |      |      |      | R/W    | R/W | R/W     | R/W   | R/W  |

| Reset  |      |      |      | 0      | 0   | 0       | 0     | 0    |

#### Bit 15 – PEND Pending

This bit will read '1' when the channel selected by Channel ID field (ID) is pending.

#### Bit 14 - BUSY Busy

This bit will read '1' when the channel selected by Channel ID field (ID) is busy.

#### Bit 13 – FERR Fetch Error

This bit will read '1' when the channel selected by Channel ID field (ID) fetched an invalid descriptor.

#### Bit 12 – CRCERR CRC Error

This bit will read '1' when the channel selected by Channel ID field (ID) has a CRC Error Status Flag bit set, and is set when the CRC monitor detects data corruption. Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear it. It will also clear the corresponding flag in the Channel n Interrupt Flag Status and Clear register (CHINTFLAGn), where n is determined by the Channel ID bit field (ID).

#### Bit 10 - SUSP Channel Suspend

This bit will read '1' when the channel selected by Channel ID field (ID) has pending Suspend interrupt.

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will clear it. It will also clear the corresponding flag in the Channel n Interrupt Flag Status and Clear register (CHINTFLAGn), where n is determined by the Channel ID bit field (ID).

#### Bit 9 – TCMPL Transfer Complete

This bit will read '1' when the channel selected by Channel ID field (ID) has pending Transfer Complete interrupt.

Writing a '0' to this bit has no effect.

## **GMAC** - Ethernet MAC

| Offset | Name   | Bit Pos. |             |              |

|--------|--------|----------|-------------|--------------|

|        |        | 23:16    | NFRX[23:16] |              |

|        |        | 31:24    | NFRX[31:24] |              |

|        |        | 7:0      | NFRX[7:0]   |              |

|        |        | 15:8     | NFRX[15:8]  |              |

| 0x0180 | TMXBFR | 23:16    | NFRX[23:16] |              |

|        |        | 31:24    | NFRX[31:24] |              |

|        |        | 7:0      | UFRX[7:0]   |              |

| 0x0184 | UFR    | 15:8     |             | UFRX[9:8]    |

| 0X0164 | UFR    | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | OFRX[7:0]   |              |

| 0x0188 | OFR    | 15:8     |             | OFRX[9:8]    |

| 0X0100 | UFK    | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | JRX[7:0]    |              |

| 0x018C | JR     | 15:8     |             | JRX[9:8]     |

| 0.0100 | JR     | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | FCKR[7:0]   |              |

| 0x0190 | FCSE   | 15:8     |             | FCKR[9:8]    |

| 0.0130 | FCSE   | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | LFER[7:0]   |              |

| 0x0194 | LFFE   | 15:8     |             | LFER[9:8]    |

| 0,0104 |        | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | RXSE[7:0]   |              |

| 0x0198 | RSE    | 15:8     |             | RXSE[9:8]    |

| 0,0100 |        | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | AER[7:0]    |              |

| 0x019C | AE     | 15:8     |             | AER[9:8]     |

|        |        | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | RXRER[7:0]  |              |

| 0x01A0 | RRE    | 15:8     | RXRER[15:8] |              |

|        |        | 23:16    |             | RXRER[17:16] |

|        |        | 31:24    |             |              |

|        |        | 7:0      | RXOVR[7:0]  |              |

| 0x01A4 | ROE    | 15:8     |             | RXOVR[9:8]   |

|        |        | 23:16    |             |              |

|        |        | 31:24    |             |              |

|        |        | 7:0      | HCKER[7:0]  |              |

| 0x01A8 | IHCE   | 15:8     |             |              |

|        | INCL   | 23:16    |             |              |

|        |        | 31:24    |             |              |

**PAC - Peripheral Access Controller**

| Offset | Name    | Bit Pos. |      |     |      |       |         |         |         |         |

|--------|---------|----------|------|-----|------|-------|---------|---------|---------|---------|

|        |         | 15:8     |      | TC3 | TC2  | TCC1  | TCC0    | SERCOM3 | SERCOM2 |         |

|        |         | 23:16    |      |     |      |       |         |         |         | RAMECC  |

|        |         | 31:24    |      |     |      |       |         |         |         |         |

|        | STATUSC | 7:0      | PDEC | TC5 | TC4  | TCC3  | TCC2    | GMAC    | CAN1    | CAN0    |

| 0x3C   |         | 15:8     |      | CCL | QSPI | PUKCC | ICM     | TRNG    | AES     | AC      |

| UXSC   |         | 23:16    |      |     |      |       |         |         |         |         |

|        |         | 31:24    |      |     |      |       |         |         |         |         |

|        |         | 7:0      | ADC0 | TC7 | TC6  | TCC4  | SERCOM7 | SERCOM6 | SERCOM5 | SERCOM4 |

| 0x40   | STATUSD | 15:8     |      |     |      |       | PCC     | I2S     | DAC     | ADC1    |

| 0x40   |         | 23:16    |      |     |      |       |         |         |         |         |

|        |         | 31:24    |      |     |      |       |         |         |         |         |

### 27.7 Register Description

Registers can be 8, 16, or 32 bits wide. Atomic 8-, 16- and 32-bit accesses are supported. In addition, the 8-bit quarters and 16-bit halves of a 32-bit register, and the 8-bit halves of a 16-bit register can be accessed directly.

Some registers are optionally write-protected by the Peripheral Access Controller (PAC). Optional PAC write-protection is denoted by the "PAC Write-Protection" property in each individual register description. For details, refer to the related links.

#### **Related Links**

13.3 Register Synchronization

## OSC32KCTRL – 32KHz Oscillators Controller

29.8.4 Status

|        | Name:<br>Offset:<br>Reset:<br>Property: | STATUS<br>0x0C<br>0x00000000<br>- |    |    |    |             |    |            |

|--------|-----------------------------------------|-----------------------------------|----|----|----|-------------|----|------------|

| Bit    | 31                                      | 30                                | 29 | 28 | 27 | 26          | 25 | 24         |

|        |                                         |                                   |    |    |    |             |    |            |

| Access |                                         |                                   |    |    |    |             |    |            |

| Reset  |                                         |                                   |    |    |    |             |    |            |

| Bit    | 23                                      | 22                                | 21 | 20 | 19 | 18          | 17 | 16         |

| Dit    | 20                                      |                                   | 21 | 20 | 10 |             |    |            |

| Access |                                         |                                   |    |    |    |             |    |            |

| Reset  |                                         |                                   |    |    |    |             |    |            |

|        |                                         |                                   |    |    |    |             |    |            |

| Bit    | 15                                      | 14                                | 13 | 12 | 11 | 10          | 9  | 8          |

|        |                                         |                                   |    |    |    |             |    |            |

| Access |                                         |                                   |    |    |    |             |    |            |

| Reset  |                                         |                                   |    |    |    |             |    |            |

| 5.1    | -                                       | 2                                 | _  |    | 0  | 0           | ,  | 0          |

| Bit    | 7                                       | 6                                 | 5  | 4  | 3  | 2           | 1  | 0          |

|        |                                         |                                   |    |    |    | XOSC32KFAIL |    | XOSC32KRDY |

| Access |                                         |                                   |    |    | R  | R           |    | R          |

| Reset  |                                         |                                   |    |    | 0  | 0           |    | 0          |

#### Bit 3 – XOSC32KSW XOSC32K Clock Switch

|   | Value | Description                                                  |

|---|-------|--------------------------------------------------------------|

| ſ | 0     | XOSC32K is not switched and provided the crystal oscillator. |

|   | 1     | XOSC32K is switched to be provided by the safe clock.        |

#### Bit 2 – XOSC32KFAIL XOSC32K Clock Failure Detector

| Value | Description                               |

|-------|-------------------------------------------|

| 0     | XOSC32K is passing failure detection.     |

| 1     | XOSC32K is not passing failure detection. |

#### Bit 0 - XOSC32KRDY XOSC32K Ready

| Value | Description                                               |

|-------|-----------------------------------------------------------|

| 0     | XOSC32K is not ready.                                     |

| 1     | XOSC32K is stable and ready to be used as a clock source. |

When the USART repetition number reaches the programmed value in CTRLC.MAXITER, the STATUS.ITER bit is set and the internal iteration counter is reset. If the repetition of the character is acknowledged by the receiver before the maximum iteration is reached, the repetitions are stopped and the iteration counter is cleared.

#### **Disable Successive Receive NACK**

The receiver can limit the number of successive NACKs sent back to the remote transmitter. This is programmed by setting the Disable Successive NACK bit (CTRLC.DSNACK). The maximum number of NACKs transmitted is programmed in the CTRLC.MAXITER field. As soon as the maximum is reached, the character is considered as correct, an acknowledge is sent on the line, the STATUS.ITER bit is set and the internal iteration counter is reset.

#### Protocol T=1

When operating in ISO7816 protocol T=1, the transmission is asynchronous (CTRL1.CMODE=0) with one or two stop bits. After the stop bits are sent, the transmitter does not drive the I/O line.

Parity is generated when transmitting and checked when receiving. Parity error detection sets the STATUS.PERR bit, and the erroneous character is written to the receive FIFO. When using T=1 protocol, the receiver does not signal errors on the I/O line and the transmitter does not retransmit.

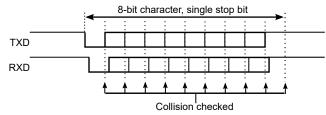

#### 34.6.3.8 Collision Detection

When the receiver and transmitter are connected either through pin configuration or externally, transmit collision can be detected after selecting the Collision Detection Enable bit in the CTRLB register (CTRLB.COLDEN=1). To detect collision, the receiver and transmitter must be enabled (CTRLB.RXEN=1 and CTRLB.TXEN=1).

Collision detection is performed for each bit transmitted by comparing the received value with the transmit value, as shown in the figure below. While the transmitter is idle (no transmission in progress), characters can be received on RxD without triggering a collision.

#### Figure 34-20. Collision Checking

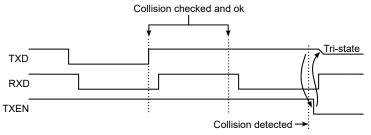

The next figure shows the conditions for a collision detection. In this case, the start bit and the first data bit are received with the same value as transmitted. The second received data bit is found to be different than the transmitted bit at the detection point, which indicates a collision.

#### Figure 34-21. Collision Detected

When a collision is detected, the USART follows this sequence:

**QSPI - Quad Serial Peripheral Interface**

| Figure 37-14. Inst | truction Transmission Waveform 3 |

|--------------------|----------------------------------|

| Write INSTRADDR    | <u>↑</u>                         |

| Write INSTRFRAME   | <u>↑</u>                         |

| cs                 |                                  |

| SCK                |                                  |

| MOSI / DATA0       | A23A22XA21XA20X XA3 XA2 XA1 X A0 |

| INTFLAG.INSTREND.  |                                  |

#### Example 37-4. Example 4

Instruction in Single-bit SPI, without address, without option, with data write in Single-bit SPI.

Command: SET BURST (77h)

- Write 0x0000\_0077 to INSTRCTRL register.

- Write 0x0000\_2090 to INSTRFRAME register.

- Read INSTRFRAME register (dummy read) to synchronize system bus accesses.

- Write data to the system bus memory space (0x0400\_0000–0x0500\_0000). The address of the system bus write accesses is not used.

- Write the LASTXFR bit in CTRLA register to '1'.

- Wait for INTFLAG.INSTREND to rise.

#### Figure 37-15. Instruction Transmission Waveform 4

| Write INSTRFRAME   |                                       |

|--------------------|---------------------------------------|

| CS                 |                                       |

| SCK                |                                       |

| MOSI / DATA0       | ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ ↓ |

| INTFLAG.INSTREND   |                                       |

| Write AHB          | <u> </u>                              |

| Set CTRLA.LASTXFER | <u>↑</u>                              |

#### Example 37-5. Example 5

Instruction in Single-bit SPI, with address in Dual SPI, without option, with data write in Dual SPI.

Command: BYTE/PAGE PROGRAM (02h)

- Write 0x0000\_0002 to INSTRCTRL register.

- Write 0x0000\_30B3 to INSTRFRAME register.

- Read INSTRFRAME register (dummy read) to synchronize system bus accesses.

- Write data to the QSPI system bus memory space (0x040 00000–0x0500\_0000).

The address of the first system bus write access is sent in the instruction frame.

The address of the next system bus write accesses is not used.

• Write LASTXFR bit in CTRLA register to '1'.

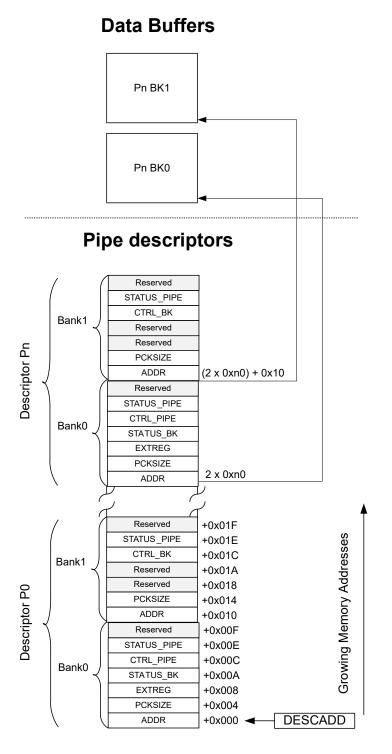

#### 38.8.7 Host Registers - Pipe RAM

38.8.7.1 Pipe Descriptor Structure

#### 39.8.12 Timeout Counter Value

| Name:     | TOCV       |

|-----------|------------|

| Offset:   | 0x2C       |

| Reset:    | 0x0000FFFF |

| Property: | Read-only  |

**Note:** A write access to TOCV reloads the Timeout Counter with the value of TOCV.TOP.

| Bit    | 31  | 30  | 29  | 28  | 27     | 26  | 25  | 24  |

|--------|-----|-----|-----|-----|--------|-----|-----|-----|

|        |     |     |     |     |        |     |     |     |

| Access |     |     |     |     |        |     |     |     |

| Reset  |     |     |     |     |        |     |     |     |

|        |     |     |     |     |        |     |     |     |

| Bit    | 23  | 22  | 21  | 20  | 19     | 18  | 17  | 16  |

|        |     |     |     |     |        |     |     |     |

| Access |     |     |     |     |        |     |     |     |

| Reset  |     |     |     |     |        |     |     |     |

| 5.4    | 45  |     | 10  | 10  |        | 10  | 0   | 2   |

| Bit    | 15  | 14  | 13  | 12  | 11     | 10  | 9   | 8   |

|        |     |     |     |     | [15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 1   | 1   | 1   | 1   | 1      | 1   | 1   | 1   |

|        |     |     |     |     |        |     |     |     |

| Bit    | 7   | 6   | 5   | 4   | 3      | 2   | 1   | 0   |

|        |     |     |     | TOC | [7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W | R/W    | R/W | R/W | R/W |

| Reset  | 1   | 1   | 1   | 1   | 1      | 1   | 1   | 1   |

#### Bits 15:0 – TOC[15:0] Timeout Counter

The Timeout Counter is decremented in multiples of CAN bit times [1...16] depending on the configuration of TSCC.TCP. When decremented to zero, interrupt flag IR.TOO is set and the Timeout Counter is stopped. Start and reset/restart conditions are configured via TOCC.TOS.

## **CAN - Control Area Network**

• when an error occurred during frame transmission

In DAR mode all transmissions are automatically canceled if they are not successful. The corresponding TXBCF bit is set for all unsuccessful transmissions.

| Value | Description                      |

|-------|----------------------------------|

| 0     | No transmission request pending. |

| 1     | Transmission request pending.    |

#### 39.8.39 Tx Buffer Add Request

| Name:     | TXBAR      |

|-----------|------------|

| Offset:   | 0xD0       |

| Reset:    | 0x00000000 |

| Property: | -          |

**Note:** If an add request is applied for a Tx Buffer with pending transmission request (corresponding TXBRP bit is already set), this add request is ignored.

| Bit    | 31         | 30  | 29  | 28    | 27     | 26  | 25  | 24  |  |

|--------|------------|-----|-----|-------|--------|-----|-----|-----|--|

|        | ARn[31:24] |     |     |       |        |     |     |     |  |

| Access | R/W        | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |  |

| Reset  | 0          | 0   | 0   | 0     | 0      | 0   | 0   | 0   |  |

|        |            |     |     |       |        |     |     |     |  |

| Bit    | 23         | 22  | 21  | 20    | 19     | 18  | 17  | 16  |  |

|        |            |     |     | ARn[2 | 23:16] |     |     |     |  |

| Access | R/W        | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |  |

| Reset  | 0          | 0   | 0   | 0     | 0      | 0   | 0   | 0   |  |

|        |            |     |     |       |        |     |     |     |  |

| Bit    | 15         | 14  | 13  | 12    | 11     | 10  | 9   | 8   |  |

|        |            |     |     | ARn[  | 15:8]  |     |     |     |  |

| Access | R/W        | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |  |

| Reset  | 0          | 0   | 0   | 0     | 0      | 0   | 0   | 0   |  |

|        |            |     |     |       |        |     |     |     |  |

| Bit    | 7          | 6   | 5   | 4     | 3      | 2   | 1   | 0   |  |

|        |            |     |     | ARn   | [7:0]  |     |     |     |  |

| Access | R/W        | R/W | R/W | R/W   | R/W    | R/W | R/W | R/W |  |

| Reset  | 0          | 0   | 0   | 0     | 0      | 0   | 0   | 0   |  |

#### Bits 31:0 - ARn[31:0] Add Request

Each Tx Buffer has its own Add Request bit.

Writing a '1' will set the corresponding Add Request bit; writing a '0' has no impact. This enables the Host to set transmission requests for multiple Tx Buffers with one write to TXBAR. TXBAR bits are set only for those Tx Buffers configured via TXBC. When no Tx scan is running, the bits are reset immediately, else the bits remain set until the Tx scan process has completed.

#### 40.8.2 Block Size Register

| Name:     | BSR    |

|-----------|--------|

| Offset:   | 0x04   |

| Reset:    | 0x0000 |

| Property: | -      |

| Bit    | 15  | 14  | 13            | 12    | 11      | 10  | 9     | 8       |

|--------|-----|-----|---------------|-------|---------|-----|-------|---------|

|        |     |     | BOUNDARY[2:0] |       |         |     | BLKSI | ZE[9:8] |

| Access |     |     |               |       |         |     | R/W   | R/W     |

| Reset  |     | 0   | 0             | 0     |         |     | 0     | 0       |

|        |     |     |               |       |         |     |       |         |

| Bit    | 7   | 6   | 5             | 4     | 3       | 2   | 1     | 0       |

|        |     |     |               | BLKSI | ZE[7:0] |     |       |         |

| Access | R/W | R/W | R/W           | R/W   | R/W     | R/W | R/W   | R/W     |

| Reset  | 0   | 0   | 0             | 0     | 0       | 0   | 0     | 0       |

#### Bits 14:12 - BOUNDARY[2:0] SDMA Buffer Boundary

This field specifies the size of the contiguous buffer in the system memory. The SDMA transfer waits at every boundary specified by this field and the peripheral generates the DMA Interrupt to instruct the software to update SSAR. If this field is set to 0 (buffer size = 4 Kbytes), the lowest 12 bits of SSAR.ADDRESS point to data in the contiguous buffer, and the upper 20 bits point to the location of the buffer in the system memory. This function is active when the DMA Enable bit in the Transfer Mode Register (TMR.DMAEN) is '1'.

| Value | Name | Description        |

|-------|------|--------------------|

| 0     | 4K   | 4-Kbyte boundary   |

| 1     | 8K   | 8-Kbyte boundary   |

| 2     | 16K  | 16-Kbyte boundary  |

| 3     | 32K  | 32-Kbyte boundary  |

| 4     | 64K  | 64-Kbyte boundary  |

| 5     | 128K | 128-Kbyte boundary |

| 6     | 256k | 256-Kbyte boundary |

| 7     | 512K | 512-Kbyte boundary |

#### Bits 9:0 – BLKSIZE[9:0] Transfer Block Size

This field specifies the block size of data transfers for CMD17, CMD18, CMD24, CMD25 and CMD53. Values ranging from 1 to 512 can be set. It can be accessed only if no transaction is executing (i.e., after a transaction has stopped). Read operations during transfers may return an invalid value, and write operations are ignored.

#### 40.8.5 Transfer Mode Register

| Name:     | TMR    |

|-----------|--------|

| Offset:   | 0x0C   |

| Reset:    | 0x0000 |

| Property: | -      |

This register is used to control data transfers. The user shall set this register before issuing a command which transfers data (refer to bit DPSEL in CR), or before issuing a Resume command. The user must save the value of this register when the data transfer is suspended (as a result of a Suspend command) and restore it before issuing a Resume command. To prevent data loss, this register cannot be written while data transactions are in progress. Writes to this register are ignored when bit PSR.CMDINHD is '1'.

|        | MSBSEL | BC           | CEN       | BCR.BLKCN              | т    | Function        |      |       |  |

|--------|--------|--------------|-----------|------------------------|------|-----------------|------|-------|--|

|        | 0      | Do           | on't care | Don't care             |      | Single Transfer |      |       |  |

|        | 1      | 0            |           | Don't care             |      | Infinite Trans  | fer  |       |  |

|        | 1      | 1            |           | Not Zero               |      | Multiple Trar   | sfer |       |  |

|        | 1      | 1 1 Zero Sta |           | Stop Multiple Transfer |      |                 |      |       |  |

| Bit    | 15     | 14           | 13        | 12                     | 11   | 10              | 9    | 8     |  |

| Access |        |              |           |                        |      |                 |      |       |  |

| Reset  |        |              |           |                        |      |                 |      |       |  |

| Bit    | 7      | 6            | 5         | 4                      | 3    | 2               | 1    | 0     |  |

|        |        |              | MSBSEL    | DTDSEL                 | ACMD | EN[1:0]         | BCEN | DMAEN |  |

| Access |        |              | R/W       | R/W                    | R/W  | R/W             | R/W  | R/W   |  |

| Reset  |        |              | 0         | 0                      | 0    | 0               | 0    | 0     |  |

#### Table 40-1. Determining the Transfer Type

#### Bit 5 – MSBSEL Multi/Single Block Selection

Write this bit to '1' when issuing multiple-block transfer commands using DAT line(s). For any other commands, write this bit to 0. If this bit is 0, it is not necessary to write BCR to '1' (refer to Table 1-4).

#### Bit 4 – DTDSEL Data Transfer Direction Selection

This bit defines the direction of the DAT lines data transfers. Write this bit to '1' to transfer data from the device (SD Card/SDIO/e.MMC) to the peripheral. Write this bit to '0' for all other commands.

| Value | Name  | Description                                    |

|-------|-------|------------------------------------------------|

| 0     | WRITE | Writes data from the peripheral to the device. |

| 1     | READ  | Reads data from the device to the peripheral.  |

#### Bits 3:2 - ACMDEN[1:0] Auto Command Enable

Two methods can be used to stop Multiple-block read and write operation:

1. Auto CMD12: when the ACMDEN field is set to 1, the peripheral issues CMD12 automatically when the last block transfer is completed. An Auto CMD12 error is indicated to ACESR. Auto CMD12 is not enabled if the command does not require CMD12.

## ADC – Analog-to-Digital Converter

#### Bit 0 - FLUSHEI Flush Event Input Enable

For a slave ADC, this bit has no effect when the respective SLAVEEN bit is set (CTRLA.SLAVEEN= 1).

| Value | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 0     | A flush and new conversion will not be triggered on any incoming event. |

| 1     | A flush and new conversion will be triggered on any incoming event.     |

#### 48.7.1.6 Interrupt Enable Set

Name:INTENSETOffset:0x09Reset:0x00Property:PAC Write-Protection

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear register (INTENCLR).

| Bit    | 7 | 6 | 5   | 4   | 3 | 2 | 1   | 0   |

|--------|---|---|-----|-----|---|---|-----|-----|

|        |   |   | MC1 | MC0 |   |   | ERR | OVF |

| Access |   |   | R/W | R/W |   |   | R/W | R/W |

| Reset  |   |   | 0   | 0   |   |   | 0   | 0   |

**Bit 5 – MC1** Match or Capture Channel x Interrupt Enable Writing a '0' to these bits has no effect.

Writing a '1' to MCx will set the corresponding Match or Capture Channel x Interrupt Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| C     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

Bit 4 – MC0 Match or Capture Channel x Interrupt Enable

Writing a '0' to these bits has no effect.

Writing a '1' to MCx will set the corresponding Match or Capture Channel x Interrupt Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

#### Bit 1 – ERR Error Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Error Interrupt Enable bit, which enables the Error interrupt.

| Value | Description                      |

|-------|----------------------------------|

| 0     | The Error interrupt is disabled. |

| 1     | The Error interrupt is enabled.  |

Bit 0 – OVF Overflow Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Overflow Interrupt Enable bit, which enables the Overflow interrupt request.

| Value | Description                         |

|-------|-------------------------------------|

| 0     | The Overflow interrupt is disabled. |

| 1     | The Overflow interrupt is enabled.  |

#### 49.8.11 Interrupt Enable Set

| Name:     | INTENSET             |

|-----------|----------------------|

| Offset:   | 0x28                 |

| Reset:    | 0x0000000            |

| Property: | PAC Write-Protection |

This register allows the user to enable an interrupt without doing a read-modify-write operation. Changes in this register will also be reflected in the Interrupt Enable Clear (INTENCLR) register.

| Bit    | 23     | 22     | 21     | 20     | 19  | 18  | 17  | 16  |

|--------|--------|--------|--------|--------|-----|-----|-----|-----|

|        |        |        | MCx    | MCx    | MCx | MCx | MCx | MCx |

| Access |        |        | R/W    | R/W    | R/W | R/W | R/W | R/W |

| Reset  |        |        | 0      | 0      | 0   | 0   | 0   | 0   |

|        |        |        |        |        |     |     |     |     |

| Bit    | 15     | 14     | 13     | 12     | 11  | 10  | 9   | 8   |

|        | FAULTx | FAULTx | FAULTB | FAULTA | DFS |     |     |     |

| Access | R/W    | R/W    | R/W    | R/W    | R/W |     |     |     |

| Reset  | 0      | 0      | 0      | 0      | 0   |     |     |     |

|        |        |        |        |        |     |     |     |     |

| Bit    | 7      | 6      | 5      | 4      | 3   | 2   | 1   | 0   |

|        |        |        |        |        | ERR | CNT | TRG | OVF |

| Access |        |        |        |        | R/W | R/W | R/W | R/W |

| Reset  |        |        |        |        | 0   | 0   | 0   | 0   |

# **Bits 21,20,19,18,17,16 – MCx** Match or Capture Channel x Interrupt Enable Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the corresponding Match or Capture Channel x Interrupt Disable/Enable bit, which enables the Match or Capture Channel x interrupt.

| Value | Description                                           |

|-------|-------------------------------------------------------|

| 0     | The Match or Capture Channel x interrupt is disabled. |

| 1     | The Match or Capture Channel x interrupt is enabled.  |

### Bits 15,14 – FAULTx Non-Recoverable Fault x Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Non-Recoverable Fault x Interrupt Disable/Enable bit, which enables the Non-Recoverable Fault x interrupt.

| Value | Description                                        |

|-------|----------------------------------------------------|

| 0     | The Non-Recoverable Fault x interrupt is disabled. |

| 1     | The Non-Recoverable Fault x interrupt is enabled.  |

#### Bit 13 – FAULTB Recoverable Fault B Interrupt Enable

Writing a '0' to this bit has no effect.

Writing a '1' to this bit will set the Recoverable Fault B Interrupt Disable/Enable bit, which enables the Recoverable Fault B interrupt.

The PDEC is enabled by writing a '1' to the Enable bit in the Control A register (CTRLA.ENABLE). The PDEC is disabled by writing a '0' to CTRLA.ENABLE.

In QDEC or HALL operation modes, PDEC decoding is enabled writing a START command in the Control B Set register (CTRLBSET.CMD=START). The PDEC decoding is disabled writing a STOP command in the Control B Set register (CTRLBSET.CMD=STOP).

The PDEC is reset by writing a '1' to the Software Reset bit in the Control A register (CTRLA.SWRST). All registers in the PDEC, except DBGCTRL, will be reset to their initial state, and the PDEC will be disabled.

The PDEC should be disabled before the PDEC is reset to avoid undefined behavior.

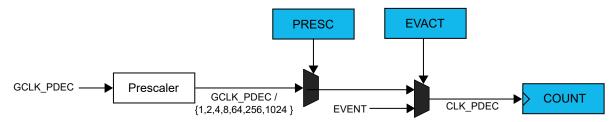

#### 53.6.2.3 Prescaler Selection

The GCLK\_PDEC is fed into the internal prescaler. Prescaler outputs from 1 to 1/1024 are directly available for selection by the counter and all selections are available in Prescaler register (PRESC). If the prescaler value is higher than 0x01, the counter update condition is executed on the next prescaled clock pulse.

If the counter is set to count events, the internal prescaler is bypassed and the GCLK\_PDEC clock is automatically selected during operation. The prescaler clock is also enabled when the input filtering is required.

#### Figure 53-2. Prescaler Selection

#### 53.6.2.4 Input Selection and Filtering

The QDEC and HALL operations require three inputs, as shown in the Block Diagram. Each input can either be a dedicated I/O pin or an Event system channel. This is selected by writing to the corresponding Event x Enable bit in the Event Control register (EVCTRL.EVEIx) or Pin x Enable bit in the Control A register (CTRLA.PINENx).

The I/O input pin active level can be inverted by writing to the corresponding Pin x Inversion Enable bit in Control A register (CTRLA.PINVENx). In the same way, the event input active level can be inverted by writing to the corresponding Inverted Event x Input Enable bit in Event Control register (EVCTRL.EVINVx).

All input signals can be filtered before they are fed into the control logic. The FILTER register is used to configure the minimum duration for which the input signal has to be valid. The input signal minimum duration must be FILTER\*  $t_{GCLK\ PDEC}$ .

#### Figure 53-3. Input Signal Filtering

| Pescaled Clock                 |      |

|--------------------------------|------|

| (Signal 0, Signal 1, Signal 2) | XXXX |

| Filter Out                     | XX   |

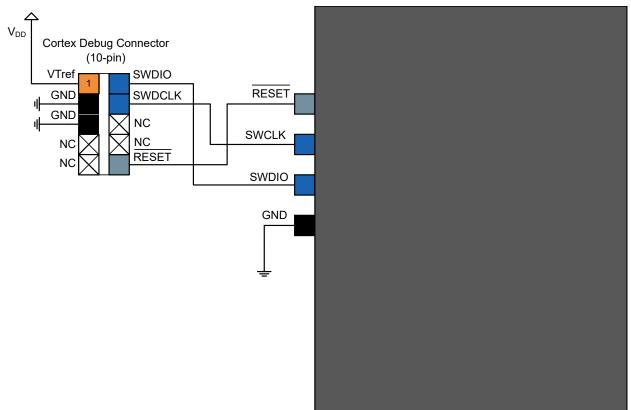

### **Schematic Checklist**

Figure 56-14. Cortex Debug Connector (10-pin)

Table 56-8. Cortex Debug Connector (10-pin)

| Header Signal Name | Description                                                      |

|--------------------|------------------------------------------------------------------|

| SWDCLK             | Serial wire clock pin                                            |

| SWDIO              | Serial wire bidirectional data pin                               |

| RESET              | Target device reset pin, active low                              |

| VTref              | Target voltage sense, should be connected to the device $V_{DD}$ |

| GND                | Ground                                                           |

#### 56.7.2 20-pin IDC JTAG Connector

For debuggers and/or programmers that support the 20-pin IDC JTAG Connector, e.g. the SAM-ICE, the signals should be connected as shown in Figure 56-15 with details described in Table 56-9.