Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Core Size32-Bit Single-CSpeed120MHzConnectivityCANbus, EBI/EUPeripheralsBrown-out DetNumber of I/O99Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C CMounting TypeSurface MountPackage / Case128-TQFP |                                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Speed120MHzConnectivityCANbus, EBI/EIPeripheralsBrown-out DetNumber of I/O99Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C ofMounting TypeSurface MountPackage / Case128-TQFP                        | 8-M4F                                                                            |

| ConnectivityCANbus, EBI/EIPeripheralsBrown-out DetNumber of I/O99Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C (1000)Mounting TypeSurface MountPackage / Case128-TQFP                               | ore                                                                              |

| PeripheralsBrown-out DetNumber of I/O99Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C ofMounting TypeSurface MountPackage / Case128-TQFP                                                             |                                                                                  |

| Number of I/O99Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C (1000)Mounting TypeSurface MountPackage / Case128-TQFP                                                                                 | MI, Ethernet, I <sup>2</sup> C, IrDA, LINbus, MMC/SD, QSPI, SPI, UART/USART, USB |

| Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C ofMounting TypeSurface MountPackage / Case128-TQFP                                                                                                    | ect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                                  |

| Program Memory TypeFLASHEEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C (Mounting TypeSurface MountPackage / Case128-TQFP                                                                                                                                    |                                                                                  |

| EEPROM Size-RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C ofMounting TypeSurface MountPackage / Case128-TQFP                                                                                                                                                           |                                                                                  |

| RAM Size256K x 8Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C (Mounting TypeSurface MountPackage / Case128-TQFP                                                                                                                                                                        |                                                                                  |

| Voltage - Supply (Vcc/Vdd)1.71V ~ 3.63VData ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°C (Mounting TypeSurface MountPackage / Case128-TQFP128 TOFP (14)                                                                                                                                                                           |                                                                                  |

| Data ConvertersA/D 32x12b; DOscillator TypeInternalOperating Temperature-40°C ~ 85°CMounting TypeSurface MountPackage / Case128-TQFP128 TOFP (14%)                                                                                                                                                                                                                   |                                                                                  |

| Oscillator Type Internal<br>Operating Temperature -40°C ~ 85°C (<br>Mounting Type Surface Mount<br>Package / Case 128-TQFP                                                                                                                                                                                                                                           |                                                                                  |

| Operating Temperature-40°C ~ 85°C (Mounting TypeSurface MountPackage / Case128-TQFP128 TOFP (14)                                                                                                                                                                                                                                                                     | /A 2x12b                                                                         |

| Mounting Type Surface Mount   Package / Case 128-TQFP   120 TOFP (14)                                                                                                                                                                                                                                                                                                |                                                                                  |

| Package / Case 128-TQFP                                                                                                                                                                                                                                                                                                                                              | (TA)                                                                             |

| 120 TOED (14)                                                                                                                                                                                                                                                                                                                                                        |                                                                                  |

| Supplier Device Package 128-TQFP (14x                                                                                                                                                                                                                                                                                                                                |                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                      | (14)                                                                             |

| Purchase URL https://www.e-                                                                                                                                                                                                                                                                                                                                          | xfl.com/product-detail/microchip-technology/atsame54p20a-au                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

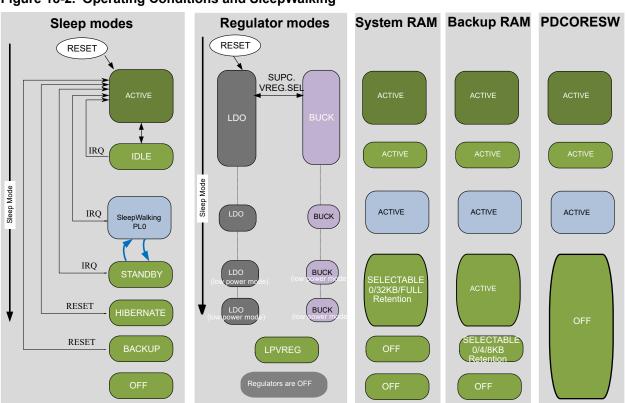

**PM – Power Manager**

# Figure 18-2. Operating Conditions and SleepWalking

#### 18.6.4.2 Wake-Up Time

As shown in the figure below, total wake-up time depends on:

Latency due to Power Domain Gating:

Usually, wake-up time is measured with the assumption that the power domains are already in active state. When using Power Domain Gating, changing a power domain from OFF to active state will take a certain time, refer to Electrical Characteristics. If all power domains were already in active state in standby sleep mode, this latency is zero.

- Latency due to Regulator effect: • As example, if the device is in standby sleep mode using the main voltage regulator (MAINVREG) in low power mode, the voltage level is lower than the one used in active mode. When the device wakes up, it takes a certain amount of time for the main regulator to transition to the voltage level corresponding to active mode, causing additional wake-up time.

- Latency due to the CPU clock source wake-up time.

- Latency due to the NVM memory access. Note: NVM and MAINVREG latencies can be reduced by setting the Fast Wake-Up bits in the Standby Configuration register (STDBYCFG.FASTWKUP).

# 21.10.13 General Purpose n

| Name:     | GP                   |

|-----------|----------------------|

| Offset:   | 0x40 + n*0x04 [n=03] |

| Reset:    | 0x0000000            |

| Property: | -                    |

| Bit    | 31  | 30  | 29  | 28               | 27    | 26  | 25  | 24  |

|--------|-----|-----|-----|------------------|-------|-----|-----|-----|

|        |     |     |     | GP[3             | 1:24] |     |     |     |

| Access | R/W | R/W | R/W | R/W              | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                | 0     | 0   | 0   | 0   |

|        |     |     |     |                  |       |     |     |     |

| Bit    | 23  | 22  | 21  | 20               | 19    | 18  | 17  | 16  |

|        |     |     |     | GP[2             | 3:16] |     |     |     |

| Access | R/W | R/W | R/W | R/W              | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                | 0     | 0   | 0   | 0   |

|        |     |     |     |                  |       |     |     |     |

| Bit    | 15  | 14  | 13  | 12               | 11    | 10  | 9   | 8   |

|        |     |     |     | GP[ <sup>*</sup> | 15:8] |     |     |     |

| Access | R/W | R/W | R/W | R/W              | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                | 0     | 0   | 0   | 0   |

|        |     |     |     |                  |       |     |     |     |

| Bit    | 7   | 6   | 5   | 4                | 3     | 2   | 1   | 0   |

|        |     |     |     | GP               | 7:0]  |     |     |     |

| Access | R/W | R/W | R/W | R/W              | R/W   | R/W | R/W | R/W |

| Reset  | 0   | 0   | 0   | 0                | 0     | 0   | 0   | 0   |

# Bits 31:0 - GP[31:0] General Purpose

These bits are for user-defined general purpose use, see 21.6.8.4 General Purpose Registers.

# DMAC – Direct Memory Access Controller

| Offset       | Name                     | Bit Pos.   |      |          |        |           |          |       |            |            |

|--------------|--------------------------|------------|------|----------|--------|-----------|----------|-------|------------|------------|

| 0xCB         |                          |            |      |          |        |           |          |       |            |            |

| 0xCC         | CHINTENCLR8              | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xCD         | CHINTENSET8              | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xCE         | CHINTFLAG8               | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xCF         | CHSTATUS8                | 7:0        |      |          |        |           | CRCERR   | FERR  | BUSY       | PEND       |

|              |                          | 7:0        |      | RUNSTDBY |        |           |          |       | ENABLE     | SWRST      |

| 0xD0         | CHCTRLA9                 | 15:8       |      |          |        | TRIG      | SRC[7:0] |       |            |            |

| 0XD0         | GHOTTLENS                | 23:16      |      |          | TRIGA  | CT[1:0]   |          |       |            |            |

|              |                          | 31:24      |      |          | THRESH | IOLD[1:0] |          | BURST | LEN[3:0]   |            |

| 0xD4         | CHCTRLB9                 | 7:0        |      |          |        |           |          |       | CME        | [1:0]      |

| 0xD5         | CHPRILVL9                | 7:0        |      |          |        |           |          |       | PRIL       | ′L[1:0]    |

| 0xD6         | CHEVCTRL9                | 7:0        | EVOE | EVIE     | EVOMO  | DDE[1:0]  |          |       | EVACT[2:0] |            |

| 0xD7         |                          |            |      |          |        |           |          |       |            |            |

|              | Reserved                 |            |      |          |        |           |          |       |            |            |

| 0xDB         |                          | _          |      |          |        |           |          |       |            |            |

| 0xDC         | CHINTENCLR9              | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xDD         | CHINTENSET9              | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xDE         | CHINTFLAG9               | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xDF         | CHSTATUS9                | 7:0        |      |          |        |           | CRCERR   | FERR  | BUSY       | PEND       |

|              |                          | 7:0        |      | RUNSTDBY |        |           |          |       | ENABLE     | SWRST      |

| 0xE0         | CHCTRLA10                | 15:8       |      |          |        |           | SRC[7:0] |       |            |            |

|              |                          | 23:16      |      |          |        | CT[1:0]   |          | BUBOT |            |            |

| 0.54         |                          | 31:24      |      |          | THRESH | IOLD[1:0] |          | BURST | LEN[3:0]   |            |

| 0xE4         | CHCTRLB10                | 7:0        |      |          |        |           |          |       |            | 0[1:0]     |

| 0xE5<br>0xE6 | CHPRILVL10<br>CHEVCTRL10 | 7:0<br>7:0 | EVOE | EVIE     | EVONO  | DE[1:0]   |          |       | EVACT[2:0] | L[1.0]     |

| 0xE0         | CHEVETREIU               | 7.0        | EVOE | EVIE     | EVOINC |           |          |       | EVACT[2.0] |            |

|              | Reserved                 |            |      |          |        |           |          |       |            |            |

| <br>0xEB     | Reserved                 |            |      |          |        |           |          |       |            |            |

| 0xEC         | CHINTENCLR10             | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xED         | CHINTENSET10             | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xEE         | CHINTFLAG10              | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xEF         | CHSTATUS10               | 7:0        |      |          |        |           | CRCERR   | FERR  | BUSY       | PEND       |

|              |                          | 7:0        |      | RUNSTDBY |        |           |          |       | ENABLE     | SWRST      |

| 0. 50        |                          | 15:8       |      |          |        | TRIG      | SRC[7:0] |       |            | . <u> </u> |

| 0xF0         | CHCTRLA11                | 23:16      |      |          | TRIGA  | CT[1:0]   |          |       |            |            |

|              |                          | 31:24      |      |          | THRESH | IOLD[1:0] |          | BURST | LEN[3:0]   |            |

| 0xF4         | CHCTRLB11                | 7:0        |      |          |        |           |          |       | CME        | [1:0]      |

| 0xF5         | CHPRILVL11               | 7:0        |      |          |        |           |          |       | PRIL       | ′L[1:0]    |

| 0xF6         | CHEVCTRL11               | 7:0        | EVOE | EVIE     | EVOMO  | DDE[1:0]  |          |       | EVACT[2:0] |            |

| 0xF7         |                          |            |      |          |        |           |          |       |            |            |

|              | Reserved                 |            |      |          |        |           |          |       |            |            |

| 0xFB         |                          |            |      |          |        |           |          |       |            |            |

| 0xFC         | CHINTENCLR11             | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xFD         | CHINTENSET11             | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

| 0xFE         | CHINTFLAG11              | 7:0        |      |          |        |           |          | SUSP  | TCMPL      | TERR       |

# **EIC – External Interrupt Controller**

#### **Related Links**

23.6.3 External Pin Processing

#### 23.6.2 Basic Operation

#### 23.6.2.1 Initialization

The EIC must be initialized in the following order:

- 1. Enable CLK\_EIC\_APB

- 2. If required, configure the NMI by writing the Non-Maskable Interrupt Control register (NMICTRL)

- 3. Enable GCLK\_EIC or CLK\_ULP32K when one of the following configuration is selected:

- the NMI uses edge detection or filtering.

- one EXTINT uses filtering.

- one EXTINT uses synchronous edge detection.

- one EXTINT uses debouncing.

GCLK\_EIC is used when a frequency higher than 32KHz is required for filtering.

CLK\_ULP32K is recommended when power consumption is the priority. For CLK\_ULP32K write a '1' to the Clock Selection bit in the Control A register (CTRLA.CKSEL).

- 4. Configure the EIC input sense and filtering by writing the Configuration n register (CONFIG).

- 5. Optionally, enable the asynchronous mode.

- 6. Optionally, enable the debouncer mode.

- 7. Enable the EIC by writing a '1' to CTRLA.ENABLE.

The following bits are enable-protected, meaning that it can only be written when the EIC is disabled (CTRLA.ENABLE=0):

Clock Selection bit in Control A register (CTRLA.CKSEL)

The following registers are enable-protected:

- Event Control register (EVCTRL)

- Configuration n register (CONFIG).

- External Interrupt Asynchronous Mode register (23.8.9 ASYNCH)

- Debouncer Enable register (23.8.11 DEBOUNCEN)

- Debounce Prescaler register (23.8.12 DPRESCALER)

Enable-protected bits in the CTRLA register can be written at the same time when setting CTRLA.ENABLE to '1', but not at the same time as CTRLA.ENABLE is being cleared.

Enable-protection is denoted by the "Enable-Protected" property in the register description.

Related Links 23.8.10 CONFIG

#### 23.6.2.2 Enabling, Disabling, and Resetting

The EIC is enabled by writing a '1' the Enable bit in the Control A register (CTRLA.ENABLE). The EIC is disabled by writing CTRLA.ENABLE to '0'.

The EIC is reset by setting the Software Reset bit in the Control register (CTRLA.SWRST). All registers in the EIC will be reset to their initial state, and the EIC will be disabled.

Refer to the CTRLA register description for details.

- 4. Write address of transmit buffer descriptor list and control information to GMAC register transmit buffer queue pointer.

- 5. The transmit circuits can then be enabled by writing to the Network Control register.

#### 24.7.1.4 Address Matching

The GMAC register pair hash address and the four Specific Address register pairs must be written with the required values. Each register pair comprises of a bottom register and top register, with the bottom register being written first. The address matching is disabled for a particular register pair after the bottom register has been written and re-enabled when the top register is written. Each register pair may be written at any time, regardless of whether the receive circuits are enabled or disabled.

As an example, to set Specific Address register 1 to recognize destination address 21:43:65:87:A9:CB, the following values are written to Specific Address register 1 bottom and Specific Address register 1 top:

- Specific Address register 1 bottom bits 31:0 (0x98): 0x8765\_4321.

- Specific Address register 1 top bits 31:0 (0x9C): 0x0000\_CBA9.

### 24.7.1.5 PHY Maintenance

The PHY Maintenance register is implemented as a shift register. Writing to the register starts a shift operation which is signalled as complete when bit two is set in the Network Status register (about 2000 MCK cycles later when bits 18:16 are set to 010 in the Network Configuration register). An interrupt is generated as this bit is set.

During this time, the MSB of the register is output on the MDIO pin and the LSB updated from the MDIO pin with each Management Data Clock (MDC) cycle. This causes the transmission of a PHY management frame on MDIO. See section 22.2.4.5 of the IEEE 802.3 standard.

Reading during the shift operation will return the current contents of the shift register. At the end of the management operation the bits will have shifted back to their original locations. For a read operation the data bits are updated with data read from the PHY. It is important to write the correct values to the register to ensure a valid PHY management frame is produced.

The Management Data Clock (MDC) should not toggle faster than 2.5 MHz (minimum period of 400 ns), as defined by the IEEE 802.3 standard. MDC is generated by dividing down MCK. Three bits in the Network Configuration register determine by how much MCK should be divided to produce MDC.

#### 24.7.1.6 Interrupts

There are 18 interrupt conditions that are detected within the GMAC. The conditions are ORed to make a single interrupt. Depending on the overall system design this may be passed through a further level of interrupt collection (interrupt controller). On receipt of the interrupt signal, the CPU enters the interrupt handler. Refer to the device interrupt controller documentation to identify that it is the GMAC that is generating the interrupt. To ascertain which interrupt, read the Interrupt Status register. Note that in the default configuration this register will clear itself after being read, though this may be configured to be write-one-to-clear if desired.

At reset all interrupts are disabled. To enable an interrupt, write to Interrupt Enable register with the pertinent interrupt bit set to 1. To disable an interrupt, write to Interrupt Disable register with the pertinent interrupt bit set to 1. To check whether an interrupt is enabled or disabled, read Interrupt Mask register. If the bit is set to 1, the interrupt is disabled.

#### 24.7.1.7 Transmitting Frames

The procedure to set up a frame for transmission is the following:

1. Enable transmit in the Network Control register.

|        | Name:<br>Offset:<br>Reset:<br>Property: | NSC<br>0x0DC<br>0x00000000<br>- |     |       |          |          |          |     |

|--------|-----------------------------------------|---------------------------------|-----|-------|----------|----------|----------|-----|

| Bit    | 31                                      | 30                              | 29  | 28    | 27       | 26       | 25       | 24  |

|        |                                         |                                 |     |       |          |          |          |     |

| Access |                                         |                                 |     |       |          |          |          |     |

| Reset  |                                         |                                 |     |       |          |          |          |     |

|        |                                         |                                 |     |       |          |          |          |     |

| Bit    | 23                                      | 22                              | 21  | 20    | 19       | 18       | 17       | 16  |

|        |                                         |                                 |     |       | NANOSE   | C[21:16] |          |     |

| Access |                                         |                                 | R/W | R/W   | R/W      | R/W      | R/W      | R/W |

| Reset  |                                         |                                 | 0   | 0     | 0        | 0        | 0        | 0   |

|        |                                         |                                 |     |       |          |          |          |     |

| Bit    | 15                                      | 14                              | 13  | 12    | 11       | 10       | 9        | 8   |

|        |                                         |                                 |     | NANOS | EC[15:8] |          |          |     |

| Access | R/W                                     | R/W                             | R/W | R/W   | R/W      | R/W      | R/W      | R/W |

| Reset  | 0                                       | 0                               | 0   | 0     | 0        | 0        | 0        | 0   |

|        |                                         |                                 |     |       |          |          |          |     |

| Bit    | 7                                       | 6                               | 5   | 4     | 3        | 2        | 1        | 0   |

|        |                                         |                                 |     | NANOS | EC[7:0]  |          | <u>.</u> |     |

| Access | R/W                                     | R/W                             | R/W | R/W   | R/W      | R/W      | R/W      | R/W |

| Reset  | 0                                       | 0                               | 0   | 0     | 0        | 0        | 0        | 0   |

|        |                                         |                                 |     |       |          |          |          |     |

## 24.9.31 GMAC 1588 Timer Nanosecond Comparison Register

Bits 21:0 – NANOSEC[21:0] 1588 Timer Nanosecond Comparison Value

Value is compared to the bits [45:24] of the TSU timer count value (upper 22 bits of nanosecond value).

### 24.9.69 GMAC 1024 to 1518 Byte Frames Received Register

| Name:     | TBFR1518   |

|-----------|------------|

| Offset:   | 0x17C      |

| Reset:    | 0x00000000 |

| Property: | Read-Only  |

| 31 | 30                                               | 29                                                                                                                                                    | 28                                                                                                                                                                                                                          | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 26                                                                                                                                                                                                                                                                                                                                                                                                               | 25                                                                                                                                                                                                                                                                                                                                                  | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |                                                  |                                                                                                                                                       | NFRX                                                                                                                                                                                                                        | [31:24]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R  | R                                                | R                                                                                                                                                     | R                                                                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0  | 0                                                | 0                                                                                                                                                     | 0                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |                                                  |                                                                                                                                                       |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 23 | 22                                               | 21                                                                                                                                                    | 20                                                                                                                                                                                                                          | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18                                                                                                                                                                                                                                                                                                                                                                                                               | 17                                                                                                                                                                                                                                                                                                                                                  | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|    |                                                  |                                                                                                                                                       | NFRX                                                                                                                                                                                                                        | [23:16]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R  | R                                                | R                                                                                                                                                     | R                                                                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0  | 0                                                | 0                                                                                                                                                     | 0                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |                                                  |                                                                                                                                                       |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 15 | 14                                               | 13                                                                                                                                                    | 12                                                                                                                                                                                                                          | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10                                                                                                                                                                                                                                                                                                                                                                                                               | 9                                                                                                                                                                                                                                                                                                                                                   | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |                                                  |                                                                                                                                                       | NFR>                                                                                                                                                                                                                        | ([15:8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R  | R                                                | R                                                                                                                                                     | R                                                                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0  | 0                                                | 0                                                                                                                                                     | 0                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |                                                  |                                                                                                                                                       |                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 7  | 6                                                | 5                                                                                                                                                     | 4                                                                                                                                                                                                                           | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 2                                                                                                                                                                                                                                                                                                                                                                                                                | 1                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    |                                                  |                                                                                                                                                       | NFR                                                                                                                                                                                                                         | X[7:0]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| R  | R                                                | R                                                                                                                                                     | R                                                                                                                                                                                                                           | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R                                                                                                                                                                                                                                                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                   | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 0  | 0                                                | 0                                                                                                                                                     | 0                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0                                                                                                                                                                                                                                                                                                                                                                                                                | 0                                                                                                                                                                                                                                                                                                                                                   | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|    | R<br>0<br>23<br>R<br>0<br>15<br>R<br>0<br>7<br>R | R   R     0   0     23   22     R   R     0   0     15   14     R   R     0   0     7   6     R   R     R   R     R   R     R   R     R   R     R   R | R     R     R       0     0     0       23     22     21       R     R     R       0     0     0       15     14     13       R     R     R       0     0     0       7     6     5       R     R     R       R     R     R | R     R     R     R     R     R     R     R     R     Q     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O | R   R   R   R   R   R     0   0   0   0   0   0   0     23   22   21   20   19   19     23   22   21   20   19     NFRX[23:16]   NFRX[23:16]   NFRX[23:16]   11     R   R   R   R   R     0   0   0   0   0     15   14   13   12   11     NFRX[15:8]   NFRX[15:8]   NFRX[15:8]   NFRX[15:8]     R   R   R   R   R     0   0   0   0   0     7   6   5   4   3     NFRX[7:0]   NFRX[7:0]   NFRX[7:0]   NFRX[7:0] | R   R   R   R   R   R     0   0   0   0   0   0     23   22   21   20   19   18     NFRX[23:16]     R   R   R   R   R     0   0   0   0   0   0     15   14   13   12   11   10     NFRX[15:8]   NFRX[15:8]     R   R   R   R   R     0   0   0   0   0   0     7   6   5   4   3   2     NFRX[7:0]   NFRX[7:0]   NFRX[7:0]   NFRX[7:0]   NFRX[7:0] | NFRX[31:24]     R   R   R   R   R   R   R     0   0   0   0   0   0   0   0     23   22   21   20   19   18   17     23   22   21   20   19   18   17     NFRX[23:16]   NFRX[23:16]   NFRX[23:16]   NFRX[15:0]   NFRX[15:0]   NFRX[15:0]     R   R   R   R   R   R   R   R   R     0   0   0   0   0   0   0   0   0     15   14   13   12   11   10   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9   9 |

Bits 31:0 - NFRX[31:0] 1024 to 1518 Byte Frames Received without Error

This bit field counts the number of 1024 to 1518 byte frames successfully received without error, i.e., no underrun and not too many retries.

ICM - Integrity Check Monitor

| Register Address | Address Offset / Byte Lane |             |            |           |  |  |  |

|------------------|----------------------------|-------------|------------|-----------|--|--|--|

|                  | 0x3 / 31:24                | 0x2 / 23:16 | 0x1 / 15:8 | 0x0 / 7:0 |  |  |  |

| 0x000 UIHVAL0    | 01                         | 23          | 45         | 67        |  |  |  |

| 0x004 UIHVAL1    | 89                         | ab          | cd         | ef        |  |  |  |

| 0x008 UIHVAL2    | fe                         | dc          | ba         | 98        |  |  |  |