Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-VDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-DFN (3x3)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15313-e-rf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3             | Bit 2     | Bit 1       | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|----------|----------|----------|---------------|-------------------|-----------|-------------|----------|-----------------------|----------------------------|

| Bank 60 |          |          |          |          |               |                   |           |             |          |                       |                            |

|         |          |          |          | CPU COF  | RE REGISTERS; | see Table 4-3 for | specifics |             |          |                       |                            |

| 1E0Ch   | _        |          |          |          | Unimpler      | mented            |           |             |          | _                     | —                          |

| 1E0Dh   | _        |          |          |          | Unimpler      | mented            |           |             |          | -                     | _                          |

| 1E0Eh   | _        |          |          |          | Unimpler      | mented            |           |             |          | _                     | _                          |

| 1E0Fh   | CLCDATA  | —        | _        | _        | _             | MLC4OUT           | MLC3OUT   | MLC2OUT     | MLC1OUT  | xxxx                  | uuuu                       |

| 1E10h   | CLCCON   | LC1EN    | _        | LC10UT   | LC1INTP       | LC1INTN           |           | LC1MODE<2:0 | )>       | 0-00 0000             | 0-00 0000                  |

| 1E11h   | CLC1POL  | LC1POL   | _        | _        | _             | LC1G4POL          | LC1G3POL  | LC1G2POL    | LC1G1POL | 0 xxxx                | 0 uuuu                     |

| 1E12h   | CLC1SEL0 | —        | _        |          |               | LC1E              | 01S<5:0>  |             |          | xx xxxx               | uu uuuu                    |

| 1E13h   | CLC1SEL1 | _        | _        |          |               | LC1E              | )2S<5:0>  |             |          | xx xxxx               | uu uuuu                    |

| 1E14h   | CLC1SEL2 | _        | _        |          |               | LC1E              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E15h   | CLC1SEL3 | —        | _        |          |               | LC1D              | )4S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E16h   | CLC1GLS0 | LC1G1D4T | LC1G4D3N | LC1G1D3T | LC1G1D3N      | LC1G1D2T          | LC1G1D2N  | LC1G1D1T    | LC1G1D1N | XXXX XXXX             | uuuu uuu                   |

| 1E17h   | CLC1GLS1 | LC1G2D4T | LC1G4D3N | LC1G2D3T | LC1G2D3N      | LC1G2D2T          | LC1G2D2N  | LC1G2D1T    | LC1G2D1N | XXXX XXXX             | นนนน นนนเ                  |

| 1E18h   | CLC1GLS2 | LC1G3D4T | LC1G4D3N | LC1G3D3T | LC1G3D3N      | LC1G3D2T          | LC1G3D2N  | LC1G3D1T    | LC1G3D1N | XXXX XXXX             | uuuu uuu                   |

| 1E19h   | CLC1GLS3 | LC1G4D4T | LC1G4D3N | LC1G4D3T | LC1G4D3N      | LC1G4D2T          | LC1G4D2N  | LC1G4D1T    | LC1G4D1N | XXXX XXXX             | uuuu uuu                   |

| 1E1Ah   | CLC2CON  | LC2EN    | _        | LC2OUT   | LC2INTP       | LC2INTN           |           | LC2MODE<2:0 | )>       | 0-00 0000             | 0-00 000                   |

| 1E1Bh   | CLC2POL  | LC2POL   | _        | _        |               | LC2G4POL          | LC2G3POL  | LC2G2POL    | LC2G1POL | 0 xxxx                | 0 uuu                      |

| 1E1Ch   | CLC2SEL0 | _        | _        |          | •             | LC2E              | D1S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Dh   | CLC2SEL1 | _        | _        |          |               | LC2               | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Eh   | CLC2SEL2 | —        | _        |          |               | LC2E              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E1Fh   | CLC2SEL3 | —        | _        |          |               | LC2E              | )4S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E20h   | CLC2GLS0 | LC2G1D4T | LC2G4D3N | LC2G1D3T | LC2G1D3N      | LC2G1D2T          | LC2G1D2N  | LC2G1D1T    | LC2G1D1N | XXXX XXXX             | นนนน นนนเ                  |

| 1E21h   | CLC2GLS1 | LC2G2D4T | LC2G4D3N | LC2G2D3T | LC2G2D3N      | LC2G2D2T          | LC2G2D2N  | LC2G2D1T    | LC2G2D1N | XXXX XXXX             | นนนน นนนเ                  |

| 1E22h   | CLC2GLS2 | LC2G3D4T | LC2G4D3N | LC2G3D3T | LC2G3D3N      | LC2G3D2T          | LC2G3D2N  | LC2G3D1T    | LC2G3D1N | xxxx xxxx             | นนนน นนนา                  |

| 1E23h   | CLC2GLS3 | LC2G4D4T | LC2G4D3N | LC2G4D3T | LC2G4D3N      | LC2G4D2T          | LC2G4D2N  | LC2G4D1T    | LC2G4D1N | xxxx xxxx             | นนนน นนนา                  |

| 1E24h   | CLC3CON  | LC3EN    | —        | LC3OUT   | LC3INTP       | LC3INTN           |           | LC3MODE     |          | 0-00 0000             | 0-00 000                   |

| 1E25h   | CLC3POL  | LC3POL   | _        | _        | _             | LC3G4POL          | LC3G3POL  | LC3G2POL    | LC3G1POL | 0 xxxx                | 0 uuu                      |

| 1E26h   | CLC3SEL0 | —        | —        |          |               | LC3E              | 01S<5:0>  |             |          | xx xxxx               | uu uuuu                    |

| 1E27h   | CLC3SEL1 | —        | —        |          |               | LC3E              | )2S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E28h   | CLC3SEL2 | _        | —        |          |               | LC3E              | 03S<5:0>  |             |          | xx xxxx               | uu uuu                     |

| 1E29h   | CLC3SEL3 | —        | —        |          |               | LC3E              | 04S<5:0>  |             |          | xx xxxx               | uu uuuu                    |

| 1E2Ah   | CLC3GLS0 | LC3G1D4T | LC3G4D3N | LC3G1D3T | LC3G1D3N      | LC3G1D2T          | LC3G1D2N  | LC3G1D1T    | LC3G1D1N | xxxx xxxx             | นนนน นนนเ                  |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

DS40001897A-page 61

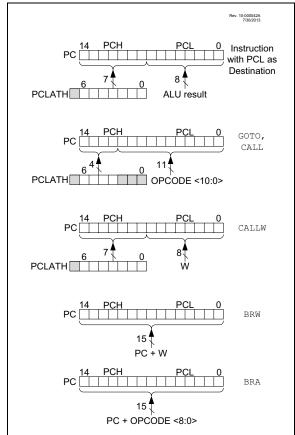

## 4.4 PCL and PCLATH

The Program Counter (PC) is 15 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<14:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 4-3 shows the five situations for the loading of the PC.

FIGURE 4-3: LOADING OF PC IN DIFFERENT SITUATIONS

#### 4.4.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<14:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper seven bits to the PCLATH register. When the lower eight bits are written to the PCL register, all 15 bits of the program counter will change to the values contained in the PCLATH register.

#### 4.4.2 COMPUTED GOTO

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). When performing a table read using a computed GOTO method, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block). Refer to Application Note AN556, *"Implementing a Table Read"* (DS00556).

#### 4.4.3 COMPUTED FUNCTION CALLS

A computed function CALL allows programs to maintain tables of functions and provide another way to execute state machines or look-up tables. When performing a table read using a computed function CALL, care should be exercised if the table location crosses a PCL memory boundary (each 256-byte block).

If using the CALL instruction, the PCH<2:0> and PCL registers are loaded with the operand of the CALL instruction. PCH<6:3> is loaded with PCLATH<6:3>.

The CALLW instruction enables computed calls by combining PCLATH and W to form the destination address. A computed CALLW is accomplished by loading the W register with the desired address and executing CALLW. The PCL register is loaded with the value of W and PCH is loaded with PCLATH.

#### 4.4.4 BRANCHING

The branching instructions add an offset to the PC. This allows relocatable code and code that crosses page boundaries. There are two forms of branching, BRW and BRA. The PC will have incremented to fetch the next instruction in both cases. When using either branching instruction, a PCL memory boundary may be crossed.

If using BRW, load the W register with the desired unsigned address and execute BRW. The entire PC will be loaded with the address PC + 1 + W.

If using BRA, the entire PC will be loaded with PC + 1 + the signed value of the operand of the BRA instruction.

## 9.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register.

#### 9.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register select the system clock source and the frequency that are used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same, and will be immediately ready. The device may enter Sleep while waiting for the switch as described in **Section 9.3.3 "Clock Switch and Sleep"**.

When the new oscillator is ready, the New Oscillator is Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of PIR1 become set (CSWIF = 1). If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the new Oscillator's READY bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- set CSWHOLD = 0 so the switch can complete, or

- copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

Changing the clock post-divider without changing the clock source (e.g., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

#### 9.3.2 PLL INPUT SWITCH

Switching between the PLL and any non-PLL source is managed as described above. The input to the PLL is established when NOSC selects the PLL, and maintained by the COSC setting.

When NOSC and COSC select the PLL with different input sources, the system continues to run using the COSC setting, and the new source is enabled per NOSC. When the new oscillator is ready (and CSWHOLD = 0), system operation is suspended while the PLL input is switched and the PLL acquires lock.

Note: If the PLL fails to lock, the FSCM will trigger.

#### 9.3.3 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

### 10.3 Interrupts During Sleep

Interrupts can be used to wake from Sleep. To wake from Sleep, the peripheral must be able to operate without the system clock. The interrupt source must have the appropriate Interrupt Enable bit(s) set prior to entering Sleep.

On waking from Sleep, if the GIE bit is also set, the processor will branch to the interrupt vector. Otherwise, the processor will continue executing instructions after the SLEEP instruction. The instruction directly after the SLEEP instruction will always be executed before branching to the ISR. Refer to **Section 11.0 "Power-Saving Operation Modes"** for more details.

#### 10.4 INT Pin

The INT pin can be used to generate an asynchronous edge-triggered interrupt. Refer to Figure 10-3. This interrupt is enabled by setting the INTE bit of the PIE0 register. The INTEDG bit of the INTCON register determines on which edge the interrupt will occur. When the INTEDG bit is set, the rising edge will cause the interrupt. When the INTEDG bit is clear, the falling edge will cause the interrupt. The INTF bit of the PIR0 register will be set when a valid edge appears on the INT pin. If the GIE and INTE bits are also set, the processor will redirect program execution to the interrupt vector.

### 10.5 Automatic Context Saving

Upon entering an interrupt, the return PC address is saved on the stack. Additionally, the following registers are automatically saved in the shadow registers:

- W register

- STATUS register (except for TO and PD)

- BSR register

- FSR registers

- PCLATH register

Upon exiting the Interrupt Service Routine, these registers are automatically restored. Any modifications to these registers during the ISR will be lost. If modifications to any of these registers are desired, the corresponding shadow register should be modified and the value will be restored when exiting the ISR. The shadow registers are available in Bank 31 and are readable and writable. Depending on the user's application, other registers may also need to be saved.

| R/W-0/0        | R/W-0/0                                                      | R/W-0/0                                                                                        | R/W-0/0        | U-0          | U-0              | U-0            | R/W-0/0      |  |  |

|----------------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------|----------------|--------------|------------------|----------------|--------------|--|--|

| CLC4IE         | CLC3IE                                                       | CLC2IE                                                                                         | CLC1IE         | —            | —                | _              | TMR1GIE      |  |  |

| bit 7          |                                                              |                                                                                                |                |              |                  |                | bit 0        |  |  |

|                |                                                              |                                                                                                |                |              |                  |                |              |  |  |

| Legend:        |                                                              |                                                                                                |                |              |                  |                |              |  |  |

| R = Readab     | ole bit                                                      | W = Writable                                                                                   | bit            | •            | mented bit, read |                |              |  |  |

| u = Bit is un  | ichanged                                                     | x = Bit is unkr                                                                                | nown           | -n/n = Value | at POR and BO    | R/Value at all | other Resets |  |  |

| '1' = Bit is s | et                                                           | '0' = Bit is cle                                                                               | ared           | HS = Hardwa  | are set          |                |              |  |  |

| bit 7          | 1 = CLC4 ir                                                  | C4 Interrupt Ena<br>nterrupt enabled                                                           | b              |              |                  |                |              |  |  |

| bit 6          | <b>CLC3IE:</b> CLC<br>1 = CLC3 ir                            | CLC3IE: CLC3 Interrupt Enable bit<br>1 = CLC3 interrupt enabled<br>0 = CLC3 interrupt disabled |                |              |                  |                |              |  |  |

| bit 5          | 1 = CLC2 ir                                                  | C2 Interrupt Ena<br>nterrupt enabled<br>nterrupt disable                                       | b              |              |                  |                |              |  |  |

| bit 4          | 1 = CLC1 ir                                                  | C1 Interrupt Ena<br>nterrupt enableo<br>nterrupt disable                                       | t              |              |                  |                |              |  |  |

| bit 3-1        | Unimplemer                                                   | nted: Read as '                                                                                | 0'             |              |                  |                |              |  |  |

| bit 0          | 1 = Enables                                                  | imer1 Gate Inte<br>s the Timer1 ga<br>s the Timer1 ga                                          | te acquisition | interrupt    |                  |                |              |  |  |

| S              | Bit PEIE of the IN<br>set to enable a<br>controlled by regis | ny peripheral                                                                                  | interrupt      |              |                  |                |              |  |  |

#### REGISTER 10-7: PIE5: PERIPHERAL INTERRUPT ENABLE REGISTER 5

#### REGISTER 10-11: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| R/W/HS-0/0                                                                                                                                                                             | R/W/HS-0/0                                                                                                                              | U-0                                                                   | U-0                                             | U-0                   | U-0              | U-0            | R/W/HS-0/0      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------|-----------------------|------------------|----------------|-----------------|--|--|--|

| OSFIF                                                                                                                                                                                  | CSWIF                                                                                                                                   | —                                                                     | _                                               | _                     | —                | _              | ADIF            |  |  |  |

| bit 7                                                                                                                                                                                  |                                                                                                                                         |                                                                       |                                                 |                       |                  |                | bit 0           |  |  |  |

|                                                                                                                                                                                        |                                                                                                                                         |                                                                       |                                                 |                       |                  |                | I               |  |  |  |

| Legend:                                                                                                                                                                                |                                                                                                                                         |                                                                       |                                                 |                       |                  |                |                 |  |  |  |

| R = Readable                                                                                                                                                                           | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'                                                                    |                                                                       |                                                 |                       |                  |                |                 |  |  |  |

| u = Bit is unc                                                                                                                                                                         | nanged                                                                                                                                  | x = Bit is unkr                                                       | nown                                            | -n/n = Value          | at POR and BOI   | R/Value at all | other Resets    |  |  |  |

| '1' = Bit is set                                                                                                                                                                       |                                                                                                                                         | '0' = Bit is clea                                                     | ared                                            | HS = Hardwa           | are set          |                |                 |  |  |  |

| bit 7 <b>OSFIF</b> : Oscillator Fail-Safe Interrupt Flag bit<br>1 = Oscillator fail-safe interrupt has occurred (must be cleared in software)<br>0 = No oscillator fail-safe interrupt |                                                                                                                                         |                                                                       |                                                 |                       |                  |                |                 |  |  |  |

| bit 6                                                                                                                                                                                  | 1 = The clock<br>operation                                                                                                              | k Switch Comp<br>switch module<br>(must be clear<br>switch does no    | indicates an i<br>ed in software                | nterrupt condit<br>e) | ion and is ready | to complete t  | he clock switch |  |  |  |

| bit 5-1                                                                                                                                                                                | Unimplemen                                                                                                                              | ted: Read as '                                                        | 0'                                              |                       |                  |                |                 |  |  |  |

| bit 0                                                                                                                                                                                  |                                                                                                                                         |                                                                       |                                                 |                       |                  |                |                 |  |  |  |

| co<br>its<br>Er<br>ປະ<br>ຊຸ                                                                                                                                                            | errupt flag bits a<br>ndition occurs, r<br>corresponding o<br>able bit, GIE, o<br>ser software<br>propriate interru<br>or to enabling a | egardless of the<br>enable bit or the<br>of the INTCON<br>should ensu | e state of<br>le Global<br>register.<br>ure the |                       |                  |                |                 |  |  |  |

## 11.0 POWER-SAVING OPERATION MODES

The purpose of the Power-Down modes is to reduce power consumption. There are three Power-Down modes: DOZE mode, IDLE mode, and SLEEP mode.

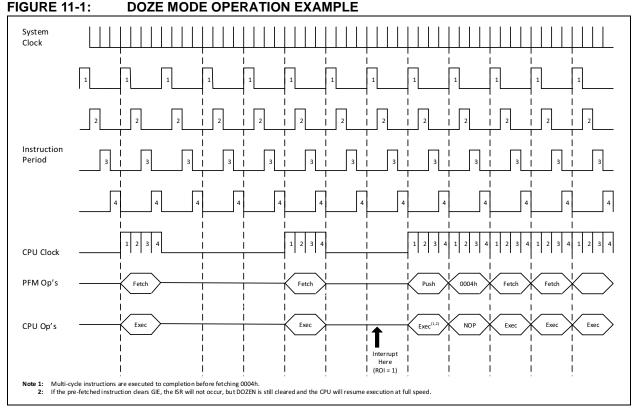

## 11.1 DOZE Mode

DOZE mode allows for power saving by reducing CPU operation and program memory (PFM) access, without affecting peripheral operation. DOZE mode differs from Sleep mode because the system oscillators continue to

operate, while only the CPU and PFM are affected. The reduced execution saves power by eliminating unnecessary operations within the CPU and memory.

When the Doze Enable (DOZEN) bit is set (DOZEN = 1), the CPU executes only one instruction cycle out of every N cycles as defined by the DOZE<2:0> bits of the CPUDOZE register. For example, if DOZE<2:0> = 100, the instruction cycle ratio is 1:32. The CPU and memory execute for one instruction cycle and then lay idle for 31 instruction cycles. During the unused cycles, the peripherals continue to operate at the system clock speed.

## 11.1.1 DOZE OPERATION

The Doze operation is illustrated in Figure 11-1. For this example:

- Doze enable (DOZEN) bit set (DOZEN = 1)

- DOZE<2:0> = 001 (1:4) ratio

- Recover-on-Interrupt (ROI) bit set (ROI = 1)

As with normal operation, the PFM fetches for the next instruction cycle. The Q-clocks to the peripherals continue throughout.

#### 14.2 PORTA Registers

#### 14.2.1 DATA REGISTER

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 14-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). Example 14.2.8 shows how to initialize PORTA.

Reading the PORTA register (Register 14-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch (LATA).

The PORT data latch LATA (Register 14-3) holds the output port data, and contains the latest value of a LATA or PORTA write.

#### EXAMPLE 14-1: INITIALIZING PORTA

| ; initia | ports are in | illustrates<br>ORTA register. The<br>itialized in the same |

|----------|--------------|------------------------------------------------------------|

| BANKSEL  | PORTA        | ;                                                          |

| CLRF     | PORTA        | ;Init PORTA                                                |

| BANKSEL  | LATA         | ;Data Latch                                                |

| CLRF     | LATA         | ;                                                          |

| BANKSEL  | ANSELA       | ;                                                          |

| CLRF     | ANSELA       | ;digital I/O                                               |

| BANKSEL  | TRISA        | ;                                                          |

| MOVLW    | B'00111000'  | ;Set RA<5:3> as inputs                                     |

| MOVWF    | TRISA        | ;and set RA<2:0> as                                        |

|          |              | ;outputs                                                   |

## 14.2.2 DIRECTION CONTROL

The TRISA register (Register 14-2) controls the PORTA pin output drivers, even when they are being used as analog inputs. The user should ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

#### 14.2.3 OPEN-DRAIN CONTROL

The ODCONA register (Register 14-6) controls the open-drain feature of the port. Open-drain operation is independently selected for each pin. When an ODCONA bit is set, the corresponding port output becomes an open-drain driver capable of sinking current only. When an ODCONA bit is cleared, the corresponding port output pin is the standard push-pull drive capable of sourcing and sinking current.

| Note: | It is not necessary to set open-drain control when using the pin for I <sup>2</sup> C; the I <sup>2</sup> C |

|-------|-------------------------------------------------------------------------------------------------------------|

|       | module controls the pin and makes the pin open-drain.                                                       |

### 14.2.4 SLEW RATE CONTROL

The SLRCONA register (Register 14-7) controls the slew rate option for each port pin. Slew rate control is independently selectable for each port pin. When an SLRCONA bit is set, the corresponding port pin drive is slew rate limited. When an SLRCONA bit is cleared, The corresponding port pin drive slews at the maximum rate possible.

#### 14.2.5 INPUT THRESHOLD CONTROL

The INLVLA register (Register 14-8) controls the input voltage threshold for each of the available PORTA input pins. A selection between the Schmitt Trigger CMOS or the TTL Compatible thresholds is available. The input threshold is important in determining the value of a read of the PORTA register and also the level at which an interrupt-on-change occurs, if that feature is enabled. See Table 37-4 for more information on threshold levels.

| Note: | Changing the input threshold selection should be performed while all peripheral |

|-------|---------------------------------------------------------------------------------|

|       | modules are disabled. Changing the                                              |

|       | threshold level during the time a module is                                     |

|       | active may inadvertently generate a                                             |

|       | transition associated with an input pin,                                        |

|       | regardless of the actual voltage level on                                       |

|       | that pin.                                                                       |

# PIC16(L)F15313/23

| U-0              | R/W-0/0                         | U-0                                              | R/W-0/0 | U-0            | U-0              | U-0            | R/W-0/0      |

|------------------|---------------------------------|--------------------------------------------------|---------|----------------|------------------|----------------|--------------|

| —                | UART1MD                         | —                                                | MSSP1MD | —              | —                | _              | CWG1MD       |

| bit 7            |                                 |                                                  |         |                |                  |                | bit 0        |

|                  |                                 |                                                  |         |                |                  |                |              |

| Legend:          |                                 |                                                  |         |                |                  |                |              |

| R = Readable     | bit                             | W = Writable I                                   | oit     | U = Unimplem   | ented bit, read  | as '0'         |              |

| u = Bit is unch  | anged                           | x = Bit is unkn                                  | own     | -n/n = Value a | t POR and BOR    | R/Value at all | other Resets |

| '1' = Bit is set |                                 | '0' = Bit is clea                                | ared    | q = Value dep  | ends on conditio | on             |              |

|                  |                                 |                                                  |         |                |                  |                |              |

| bit 7            | Unimplement                     | ed: Read as '0                                   | ,       |                |                  |                |              |

| bit 6            | •••••                           | isable EUSAR <sup>-</sup><br>1 module disab      |         |                |                  |                |              |

|                  | 0 = EUSART                      | 1 module enab                                    | ed      |                |                  |                |              |

| bit 5            | Unimplement                     | ed: Read as '0                                   | ,       |                |                  |                |              |

| bit 4            |                                 | isable MSSP1                                     |         |                |                  |                |              |

|                  |                                 | nodule disabled<br>nodule enabled                | -       |                |                  |                |              |

| bit 3-1          | •                               | ed: Read as '0                                   |         |                |                  |                |              |

| bit 0            | <b>CWG1MD:</b> Di<br>1 = CWG1 m | sable CWG1 bi<br>odule disabled<br>odule enabled |         |                |                  |                |              |

#### REGISTER 16-5: PMD4: PMD CONTROL REGISTER 4

| Name     | Bit 7 Bit 6 |        | Bit 5     | Bit 5 Bit 4 |             | Bit 3 Bit 2 |             | Bit 1 Bit 0 |                |

|----------|-------------|--------|-----------|-------------|-------------|-------------|-------------|-------------|----------------|

| FVRCON   | FVREN       | FVRRDY | TSEN      | TSRNG       | CDAFVR<1:0> |             | ADFVR<1:0>  |             | on page<br>210 |

| ADCON0   |             |        | CHS<      | 5:0>        |             |             | GO/DONE     | ADON        | 223            |

| ADCON1   | ADFM        |        | ADCS<2:0> |             |             | —           | ADPREF<1:0> |             | 224            |

| DAC1CON0 | DAC1EN      |        | DAC10E1   | DAC10E2     | DAC1PS      | SS<1:0>     | _           | DAC1NSS     | 232            |

TABLE 18-1: SUMMARY OF REGISTERS ASSOCIATED WITH FIXED VOLTAGE REFERENCE

Legend: -= unimplemented locations read as '0'. Shaded cells are not used with the Fixed Voltage Reference.

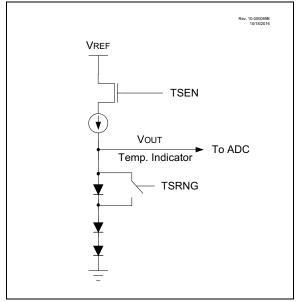

## 19.0 TEMPERATURE INDICATOR MODULE

This family of devices is equipped with a temperature circuit designed to measure the operating temperature of the silicon die. The main purpose of the temperature indicator module is to provide a temperature-dependent voltage that can be measured by the Analog-to-Digital Converter.

The circuit's range of operating temperature falls between -40°C and +125°C. The circuit may be used as a temperature threshold detector or a more accurate temperature indicator, depending on the level of calibration performed. A one-point calibration allows the circuit to indicate a temperature closely surrounding that point. A two-point calibration allows the circuit to sense the entire range of temperature more accurately.

## **19.1 Module Operation**

The temperature indicator module consists of a temperature-sensing circuit that provides a voltage to the device ADC. The analog voltage output, VTSENSE, varies inversely to the device temperature. The output of the temperature indicator is referred to as VOUT.

Figure 19-1 shows a simplified block diagram of the temperature indicator module.

#### FIGURE 19-1: TEMPERATURE INDICATOR BLOCK DIAGRAM

The output of the circuit is measured using the internal Analog-to-Digital Converter. A channel is reserved for the temperature circuit output. Refer to Section 20.0 "Analog-to-Digital Converter (ADC) Module" for detailed information.

The ON/OFF bit for the module is located in the FVRCON register. See **Section 18.0** "**Fixed Voltage Reference (FVR)**" for more information. The circuit is enabled by setting the TSEN bit of the FVRCON register. When the module is disabled, the circuit draws no current.

The circuit operates in either High or Low range. Refer to **Section 19.5** "**Temperature Indicator Range**" for more details on the range settings.

## **19.2 Estimation of Temperature**

This section describes how the sensor voltage can be used to estimate the temperature of the module. To use the sensor, the output voltage, VTSENSE, is measured and the corresponding temperature is determined. Equation 19-1 provides an estimate for the die temperature based on the VTSENSE value.

## EQUATION 19-1: SENSOR TEMPERATURE

$$T_{SENSE} = V_{TSENSE} \times (Mt) + T_{OFFSET}$$

Where:

Mt = 1/Mv, where Mv = sensor voltage sensitivity (V/°C). TOFFSET is the temperature difference between the theoretical temperature and the actual temperature.

| ADC Clock P         | eriod (TAD) |                             | Device Frequency (Fosc)     |                             |                             |                               |                             |  |

|---------------------|-------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------|-------------------------------|-----------------------------|--|

| ADC<br>Clock Source | ADCS<2:0>   | 32 MHz 20 MHz 16 MHz        |                             | 16 MHz                      | 8 MHz                       | 4 MHz                         | 1 MHz                       |  |

| Fosc/2              | 000         | 62.5ns <sup>(2)</sup>       | 100 ns <sup>(2)</sup>       | 125 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>         | 2.0 μs                      |  |

| Fosc/4              | 100         | 125 ns <sup>(2)</sup>       | 200 ns <sup>(2)</sup>       | 250 ns <sup>(2)</sup>       | 500 ns <sup>(2)</sup>       | 1.0 μs                        | 4.0 μs                      |  |

| Fosc/8              | 001         | 0.5 μs <sup>(2)</sup>       | 400 ns <sup>(2)</sup>       | 0.5 μs <sup>(2)</sup>       | 1.0 μs                      | 2.0 μs                        | 8.0 μs <sup>(3)</sup>       |  |

| Fosc/16             | 101         | 800 ns                      | 800 ns                      | 1.0 μs                      | 2.0 μs                      | 4.0 μs                        | 16.0 μs <sup>(3)</sup>      |  |

| Fosc/32             | 010         | 1.0 μs                      | 1.6 μs                      | 2.0 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>         | 32.0 μs <sup>(2)</sup>      |  |

| Fosc/64             | 110         | 2.0 μs                      | 3.2 μs                      | 4.0 μs                      | 8.0 μs <sup>(3)</sup>       | 16.0 μs <b><sup>(2)</sup></b> | 64.0 μs <sup>(2)</sup>      |  |

| ADCRC               | x11         | 1.0-6.0 μs <sup>(1,4)</sup>   | 1.0-6.0 μs <sup>(1,4)</sup> |  |

#### TABLE 20-1: ADC CLOCK PERIOD (TAD) Vs. DEVICE OPERATING FREQUENCIES

**Legend:** Shaded cells are outside of recommended range.

Note 1: See TAD parameter for ADCRC source typical TAD value.

**2:** These values violate the required TAD time.

**3:** Outside the recommended TAD time.

**4:** The ADC clock period (TAD) and total ADC conversion time can be minimized when the ADC clock is derived from the system clock FOSC. However, the ADCRC oscillator source must be used when conversions are to be performed with the device in Sleep mode.

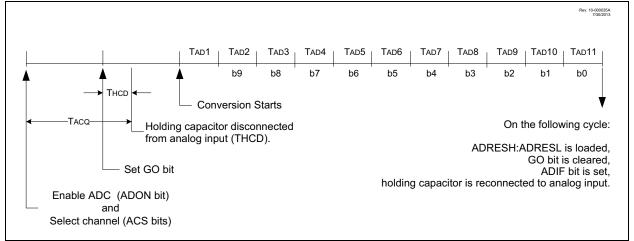

### FIGURE 20-2: ANALOG-TO-DIGITAL CONVERSION TAD CYCLES

## 20.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 20-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 20-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 20-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 20-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =

$$50^{\circ}C$$

and external impedance of  $10k\Omega 5.0V$  VDD

$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$

$= TAMP + TC + TCOFF$

$= 2\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

*The value for TC can be approximated with the following equations:*

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} V_{APPLIED}\left(1 - e^{\frac{-TC}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{(2^{n+1}) - 1}\right) \qquad ;combining [1] and [2]$$

*Note:* Where n = number of bits of the ADC.

Solving for TC:

ł

$$Tc = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 2\mu s + 1.37 + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

**Note 1:** The VAPPLIED has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is  $10 \text{ k}\Omega$ . This is required to meet the pin leakage specification.

| Name            | Bit 7                                                                      | Bit 6           | Bit 5         | Bit 4            | Bit 3            | Bit 2 | Bit 1 | Bit 0  | Register<br>on Page |

|-----------------|----------------------------------------------------------------------------|-----------------|---------------|------------------|------------------|-------|-------|--------|---------------------|

| TMR0L           | Holding Regi                                                               | ster for the Le | ast Significa | nt Byte of the 1 | 6-bit TMR0 Regis | ter   |       |        | 260*                |

| TMR0H           | Holding Register for the Most Significant Byte of the 16-bit TMR0 Register |                 |               |                  |                  |       |       |        | 260*                |

| T0CON0          | T0EN — T0OUT T016BIT T0OUTPS<3:0>                                          |                 |               |                  |                  |       | 263   |        |                     |

| T0CON1          | T0CS<2:0> T0ASYNC T0CKPS<3:0>                                              |                 |               |                  |                  |       | 264   |        |                     |

| <b>T0CKIPPS</b> | —                                                                          | —               |               |                  | T0CKIPPS         | <5:0> |       |        | 191                 |

| TMR0PPS         | —                                                                          | _               |               |                  | TMR0PPS<         | <5:0> |       |        | 191                 |

| T1GCON          | GE                                                                         | GPOL            | GTM           | GSPM             | GGO/DONE         | GVAL  | —     | —      | 275                 |

| INTCON          | GIE                                                                        | PEIE            | _             | _                | —                | —     | —     | INTEDG | 121                 |

| PIR0            | —                                                                          | —               | TMR0IF        | IOCIF            | —                | —     | —     | INTF   | 130                 |

| PIE0            | —                                                                          |                 | TMR0IE        | IOCIE            | _                | —     | —     | INTE   | 122                 |

### TABLE 25-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

Legend: — = Unimplemented location, read as '0'. Shaded cells are not used by the Timer0 module. \* Page with Register information.

#### REGISTER 28-1: CCPxCON: CCPx CONTROL REGISTER (CONTINUED)

- bit 3-0 MODE<3:0>: CCPx Mode Select bits<sup>(1)</sup>

- 1111 1100 = PWM mode (Timer2 as the timer source)

- 1110 = Reserved

- 1101 = Reserved

- 1100 = Reserved

- 1011 = Compare mode: output will pulse 0-1-0; Clears TMR1

- 1010 = Compare mode: output will pulse 0-1-0

- 1001 = Compare mode: clear output on compare match

- 1000 = Compare mode: set output on compare match

- 0111 = Capture mode: every 16th rising edge of CCPx input

- 0110 = Capture mode: every 4th rising edge of CCPx input

- 0101 = Capture mode: every rising edge of CCPx input

- 0100 = Capture mode: every falling edge of CCPx input

- 0011 = Capture mode: every edge of CCPx input

- 0010 = Compare mode: toggle output on match

- 0001 = Compare mode: toggle output on match; clear TMR1

- 0000 = Capture/Compare/PWM off (resets CCPx module)

- **Note 1:** All modes will set the CCPxIF bit, and will trigger an ADC conversion if CCPx is selected as the ADC trigger source.

### 30.13 Register Definitions: CWG Control

Long bit name prefixes for the CWG peripherals are shown in Section 1.1 "Register and Bit Naming Conventions".

#### REGISTER 30-1: CWG1CON0: CWG1 CONTROL REGISTER 0

| R/W-0/0 | R/W/HC-0/0        | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0   | R/W-0/0 |

|---------|-------------------|-----|-----|-----|---------|-----------|---------|

| EN      | LD <sup>(1)</sup> | —   | —   | —   |         | MODE<2:0> |         |

| bit 7   |                   |     |     |     |         |           | bit 0   |

| Legend:                    |                      |                                                       |

|----------------------------|----------------------|-------------------------------------------------------|

| HC = Bit is cleared by har | dware                | HS = Bit is set by hardware                           |

| R = Readable bit           | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged       | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set           | '0' = Bit is cleared | q = Value depends on condition                        |

| bit 7   | EN: CWG1 Enable bit                                       |

|---------|-----------------------------------------------------------|

|         | 1 = Module is enabled                                     |

|         | 0 = Module is disabled                                    |

| bit 6   | LD: CWG1 Load Buffer bits <sup>(1)</sup>                  |

|         | 1 = Buffers to be loaded on the next rising/falling event |

|         | 0 = Buffers not loaded                                    |

| bit 5-3 | Unimplemented: Read as '0'                                |

| bit 2-0 | MODE<2:0>: CWG1 Mode bits                                 |

|         | 111 = Reserved                                            |

|         | 110 = Reserved                                            |

|         | 101 = CWG outputs operate in Push-Pull mode               |

|         | 100 = CWG outputs operate in Half-Bridge mode             |

|         | 011 = CWG outputs operate in Reverse Full-Bridge mode     |

|         | 010 = CWG outputs operate in Forward Full-Bridge mode     |

|         | 001 = CWG outputs operate in Synchronous Steering mode    |

|         | 000 = CWG outputs operate in Steering mode                |

|         |                                                           |

**Note 1:** This bit can only be set after EN = 1 and cannot be set in the same instruction that EN is set.

## 31.0 CONFIGURABLE LOGIC CELL (CLC)

The Configurable Logic Cell (CLCx) module provides programmable logic that operates outside the speed limitations of software execution. The logic cell selects from 40 input signals and, through the use of configurable gates, reduces the inputs to four logic lines that drive one of eight selectable single-output logic functions.

Input sources are a combination of the following:

- · I/O pins

- Internal clocks

- · Peripherals

- · Register bits

The output can be directed internally to peripherals and to an output pin.

The CLC modules available are shown in Table 31-1.

TABLE 31-1: AVAILABLE CLC MODULES

| Device            | CLC1 | CLC2 | CLC3 | CLC4 |

|-------------------|------|------|------|------|

| PIC16(L)F15313/23 | •    | •    | ٠    | ٠    |

| Note: | The CLC1, CLC2, CLC3 and CLC4 are            |

|-------|----------------------------------------------|

|       | four separate module instances of the        |

|       | same CLC module design. Throughout           |

|       | this section, the lower case 'x' in register |

|       | and bit names is a generic reference to      |

|       | the CLC number (which should be substi-      |

|       | tuted with 1, 2, 3, or 4 during code devel-  |

|       | opment). For example, the control register   |

|       | is generically described in this chapter as  |

|       | CLCxCON, but the actual device registers     |

|       | are CLC1CON, CLC2CON, CLC3CON                |

|       | and CLC4CON. Similarly, the LCxEN bit        |

|       | represents the LC1EN, LC2EN, LC3EN           |

|       | and LC4EN bits.                              |

Refer to Figure 31-1 for a simplified diagram showing signal flow through the CLCx.

Possible configurations include:

- Combinatorial Logic

- AND

- NAND

- AND-OR

- AND-OR-INVERT

- OR-XOR

- OR-XNOR

- Latches

- S-R

- Clocked D with Set and Reset

- Transparent D with Set and Reset

- Clocked J-K with Reset

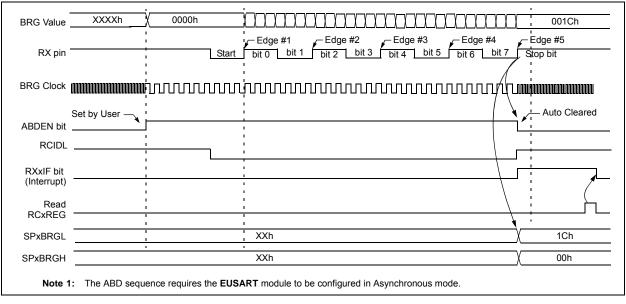

#### 33.3.1 AUTO-BAUD DETECT

The EUSART module supports automatic detection and calibration of the baud rate.

In the Auto-Baud Detect (ABD) mode, the clock to the BRG is reversed. Rather than the BRG clocking the incoming RX signal, the RX signal is timing the BRG. The Baud Rate Generator is used to time the period of a received 55h (ASCII "U") which is the Sync character for the LIN bus. The unique feature of this character is that it has five rising edges including the Stop bit edge.

Setting the ABDEN bit of the BAUD1CON register starts the auto-baud calibration sequence. While the ABD sequence takes place, the EUSART state machine is held in Idle. On the first rising edge of the receive line, after the Start bit, the SP1BRG begins counting up using the BRG counter clock as shown in Figure 33-6. The fifth rising edge will occur on the RX pin at the end of the eighth bit period. At that time, an accumulated value totaling the proper BRG period is left in the SP1BRGH, SP1BRGL register pair, the ABDEN bit is automatically cleared and the RX1IF interrupt flag is set. The value in the RC1REG needs to be read to clear the RX1IF interrupt. RC1REG content should be discarded. When calibrating for modes that do not use the SP1BRGH register the user can verify that the SP1BRGL register did not overflow by checking for 00h in the SP1BRGH register.

The BRG auto-baud clock is determined by the BRG16 and BRGH bits as shown in Table 33-1. During ABD, both the SP1BRGH and SP1BRGL registers are used as a 16-bit counter, independent of the BRG16 bit setting. While calibrating the baud rate period, the SP1BRGH and SP1BRGL registers are clocked at 1/8th the BRG base clock rate. The resulting byte measurement is the average bit time when clocked at full speed.

- Note 1: If the WUE bit is set with the ABDEN bit, auto-baud detection will occur on the byte <u>following</u> the Break character (see Section 33.3.3 "Auto-Wake-up on Break").

- 2: It is up to the user to determine that the incoming character baud rate is within the range of the selected BRG clock source. Some combinations of oscillator frequency and EUSART baud rates are not possible.

- 3: During the auto-baud process, the auto-baud counter starts counting at one. Upon completion of the auto-baud sequence, to achieve maximum accuracy, subtract 1 from the SP1BRGH:SP1BRGL register pair.

#### TABLE 33-1: BRG COUNTER CLOCK RATES

| BRG16 | BRGH | BRG Base<br>Clock | BRG ABD<br>Clock |

|-------|------|-------------------|------------------|

| 0     | 0    | Fosc/64           | Fosc/512         |

| 0     | 1    | Fosc/16           | Fosc/128         |

| 1     | 0    | Fosc/16           | Fosc/128         |

| 1     | 1    | Fosc/4            | Fosc/32          |

**Note:** During the ABD sequence, SP1BRGL and SP1BRGH registers are both used as a 16-bit counter, independent of the BRG16 setting.

#### FIGURE 33-6: AUTOMATIC BAUD RATE CALIBRATION

# PIC16(L)F15313/23

| ΜΟΥΨΙ            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                              |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                          |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| RESET            | Software Reset                                                                 |

|------------------|--------------------------------------------------------------------------------|

| Syntax:          | [label] RESET                                                                  |

| Operands:        | None                                                                           |

| Operation:       | Execute a device Reset. Resets the $\overline{RI}$ flag of the PCON register.  |

| Status Affected: | None                                                                           |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |  |

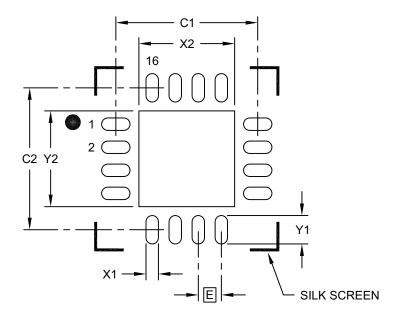

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                               |    |             |      | •    |

|-------------------------------|----|-------------|------|------|

| Units                         |    | MILLIMETERS |      |      |

| Dimension Limits              |    | MIN         | NOM  | MAX  |

| Contact Pitch E               |    | 0.65 BSC    |      |      |

| Optional Center Pad Width     | X2 |             |      | 2.70 |

| Optional Center Pad Length Y2 |    |             |      | 2.70 |

| Contact Pad Spacing C1        |    |             | 4.00 |      |

| Contact Pad Spacing           | C2 |             | 4.00 |      |

| Contact Pad Width (X16)       | X1 |             |      | 0.35 |

| Contact Pad Length (X16)      |    |             |      | 0.80 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2257A