Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| 20000                      |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 6                                                                           |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 8-VDFN Exposed Pad                                                          |

| Supplier Device Package    | 8-DFN (3x3)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15313t-i-rf |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                               |        |                           |                            |                                                                    |             |             |            |           |           | ,                     |                            |

|-------------------------------|--------|---------------------------|----------------------------|--------------------------------------------------------------------|-------------|-------------|------------|-----------|-----------|-----------------------|----------------------------|

| Bank Offset<br>Bank 0-Bank 63 | Name   | Bit 7                     | Bit 6                      | Bit 5                                                              | Bit 4       | Bit 3       | Bit 2      | Bit 1     | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| All Banks                     |        |                           |                            |                                                                    |             |             |            |           |           |                       |                            |

| x00h or x80h                  | INDF0  | Addressing<br>physical re | i this locatioi<br>gister) | n uses cont                                                        | ents of FSF | R0H/FSR0L   | to address | data memo | ry (not a | XXXX XXXX             | XXXX XXXX                  |

| x01h or x81h                  | INDF1  | Addressing physical re    | this location<br>gister)   | n uses cont                                                        | ents of FSF | R1H/FSR1L   | to address | data memo | ry (not a | XXXX XXXX             | xxxx xxxx                  |

| x02h or x82h                  | PCL    |                           |                            |                                                                    | PC          | CL          |            |           |           | 0000 0000             | 0000 0000                  |

| x03h or x83h                  | STATUS | _                         | _                          | _                                                                  | TO          | PD          | Z          | DC        | С         | 1 1000                | q quuu                     |

| x04h or x84h                  | FSR0L  | FSR0L                     | Indirect Da                | ta Memory                                                          | Address 0 I | Low Pointer |            |           |           | 0000 0000             | uuuu uuuu                  |

| x05h or x85h                  | FSR0H  | FSR0H                     | Indirect Da                | ta Memory                                                          | Address 0 I | High Pointe | r          |           |           | 0000 0000             | 0000 0000                  |

| x06h or x86h                  | FSR1L  | FSR1L                     | Indirect Da                | ta Memory                                                          | Address 1 I | Low Pointer |            |           |           | 0000 0000             | uuuu uuuu                  |

| x07h or x87h                  | FSR1H  | FSR1H                     | Indirect Da                | ta Memory                                                          | Address 1 I | High Pointe | r          |           |           | 0000 0000             | 0000 0000                  |

| x08h or x88h                  | BSR    | _                         | _                          |                                                                    |             | BSR         | <5:0>      |           |           | 00 0000               | 00 0000                    |

| x09h or x89h                  | WREG   | Working Re                | egister                    |                                                                    |             |             |            |           |           | 0000 0000             | uuuu uuuu                  |

| x0Ah or x8Ah                  | PCLATH | -                         | Write Buffe                | Write Buffer for the upper 7 bits of the Program Counter -000 0000 |             |             |            |           |           | -000 0000             |                            |

| x0Bh or x8Bh                  | INTCON | GIE                       | PEIE                       | _                                                                  | _           | _           | _          | _         | INTEDG    | 001                   | 001                        |

TABLE 4-9:

SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (ALL BANKS)

Legend:  $\mathbf{x}$  = unknown,  $\mathbf{u}$  = unchanged,  $\mathbf{q}$  = depends on condition, - = unimplemented, read as '0',  $\mathbf{r}$  = reserved. Shaded locations unimplemented, read as '0'.

Note 1: These Registers can be accessed from any bank.

| REGIST  | ER 5-7:      | REVIS    | SIONID      | : REVIS | SION ID | REGIS     | STER     |   |             |          |    |   |   |

|---------|--------------|----------|-------------|---------|---------|-----------|----------|---|-------------|----------|----|---|---|

| R       | R            | R        | R           | R       | R       | R         | R        | R | R           | R        | R  | R | R |

| 1       | 0            |          | MJRREV<5:0> |         |         |           |          |   | MNRREV<5:0> |          |    |   |   |

| bit 13  |              | bit (    |             |         |         |           |          |   | bit 0       |          |    |   |   |

|         |              |          |             |         |         |           |          |   |             |          |    |   |   |

| Legend: |              |          |             |         |         |           |          |   |             |          |    |   |   |

|         | R = Read     | able bit |             |         |         |           |          |   |             |          |    |   |   |

|         | '0' = Bit is | cleared  |             |         |         | '1' = Bit | t is set |   | x = Bit     | is unkno | wn |   |   |

| r       |              |          |             |         |         |           |          |   |             |          |    |   |   |

bit 13-12 **Fixed Value**: Read-only bits These bits are fixed with value '10' for all devices included in this data sheet.

bit 11-6MJRREV<5:0>: Major Revision ID bits<br/>These bits are used to identify a major revision.bit 5-0MNRREV<5:0>: Minor Revision ID bits<br/>These bits are used to identify a minor revision.

© 2017 Microchip Technology Inc.

#### 9.3 Clock Switching

The system clock source can be switched between external and internal clock sources via software using the New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register.

#### 9.3.1 NEW OSCILLATOR SOURCE (NOSC) AND NEW DIVIDER SELECTION REQUEST (NDIV) BITS

The New Oscillator Source (NOSC) and New Divider selection request (NDIV) bits of the OSCCON1 register select the system clock source and the frequency that are used for the CPU and peripherals.

When new values of NOSC and NDIV are written to OSCCON1, the current oscillator selection will continue to operate while waiting for the new clock source to indicate that it is stable and ready. In some cases, the newly requested source may already be in use, and is ready immediately. In the case of a divider-only change, the new and old sources are the same, and will be immediately ready. The device may enter Sleep while waiting for the switch as described in **Section 9.3.3 "Clock Switch and Sleep"**.

When the new oscillator is ready, the New Oscillator is Ready (NOSCR) bit of OSCCON3 and the Clock Switch Interrupt Flag (CSWIF) bit of PIR1 become set (CSWIF = 1). If Clock Switch Interrupts are enabled (CSWIE = 1), an interrupt will be generated at that time. The Oscillator Ready (ORDY) bit of OSCCON3 can also be polled to determine when the oscillator is ready in lieu of an interrupt.

If the Clock Switch Hold (CSWHOLD) bit of OSCCON3 is clear, the oscillator switch will occur when the new Oscillator's READY bit (NOSCR) is set, and the interrupt (if enabled) will be serviced at the new oscillator setting.

If CSWHOLD is set, the oscillator switch is suspended, while execution continues using the current (old) clock source. When the NOSCR bit is set, software should:

- set CSWHOLD = 0 so the switch can complete, or

- copy COSC into NOSC to abandon the switch.

If DOZE is in effect, the switch occurs on the next clock cycle, whether or not the CPU is operating during that cycle.

Changing the clock post-divider without changing the clock source (e.g., changing Fosc from 1 MHz to 2 MHz) is handled in the same manner as a clock source change, as described previously. The clock source will already be active, so the switch is relatively quick. CSWHOLD must be clear (CSWHOLD = 0) for the switch to complete.

The current COSC and CDIV are indicated in the OSCCON2 register up to the moment when the switch actually occurs, at which time OSCCON2 is updated and ORDY is set. NOSCR is cleared by hardware to indicate that the switch is complete.

#### 9.3.2 PLL INPUT SWITCH

Switching between the PLL and any non-PLL source is managed as described above. The input to the PLL is established when NOSC selects the PLL, and maintained by the COSC setting.

When NOSC and COSC select the PLL with different input sources, the system continues to run using the COSC setting, and the new source is enabled per NOSC. When the new oscillator is ready (and CSWHOLD = 0), system operation is suspended while the PLL input is switched and the PLL acquires lock.

Note: If the PLL fails to lock, the FSCM will trigger.

#### 9.3.3 CLOCK SWITCH AND SLEEP

If OSCCON1 is written with a new value and the device is put to Sleep before the switch completes, the switch will not take place and the device will enter Sleep mode.

When the device wakes from Sleep and the CSWHOLD bit is clear, the device will wake with the 'new' clock active, and the clock switch interrupt flag bit (CSWIF) will be set.

When the device wakes from Sleep and the CSWHOLD bit is set, the device will wake with the 'old' clock active and the new clock will be requested again.

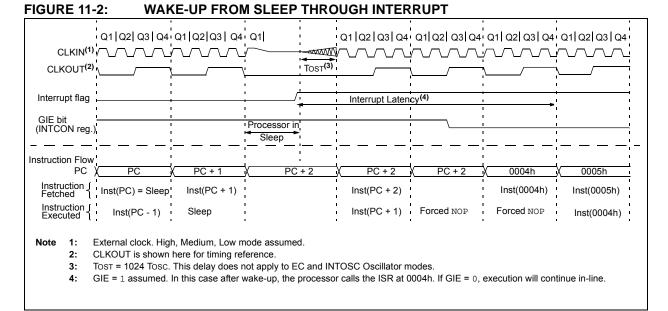

#### 11.2.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source, with the exception of the clock switch interrupt, has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction

- SLEEP instruction will execute as a NOP

- WDT and WDT prescaler will not be cleared

- TO bit of the STATUS register will not be set

- PD bit of the STATUS register will not be cleared

- If the interrupt occurs **during or after** the execution of a **SLEEP** instruction

- SLEEP instruction will be completely executed

- Device will immediately wake-up from Sleep

- WDT and WDT prescaler will be cleared

- TO bit of the STATUS register will be set

- PD bit of the STATUS register will be cleared

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

#### 11.2.3 LOW-POWER SLEEP MODE

The PIC16F15313/23 device contains an internal Low Dropout (LDO) voltage regulator, which allows the device I/O pins to operate at voltages up to 5.5V while the internal device logic operates at a lower voltage. The LDO and its associated reference circuitry must remain active when the device is in Sleep mode.

The PIC16F15313/23 allows the user to optimize the operating current in Sleep, depending on the application requirements.

Low-Power Sleep mode can be selected by setting the VREGPM bit of the VREGCON register. Depending on the configuration of these bits, the LDO and reference circuitry are placed in a low-power state when the device is in Sleep.

#### 11.2.3.1 Sleep Current vs. Wake-up Time

In the default operating mode, the LDO and reference circuitry remain in the normal configuration while in Sleep. The device is able to exit Sleep mode quickly since all circuits remain active. In Low-Power Sleep mode, when waking-up from Sleep, an extra delay time is required for these circuits to return to the normal configuration and stabilize.

The Low-Power Sleep mode is beneficial for applications that stay in Sleep mode for long periods of time. The Normal mode is beneficial for applications that need to wake from Sleep quickly and frequently.

#### 11.2.3.2 Peripheral Usage in Sleep

Some peripherals that can operate in Sleep mode will not operate properly with the Low-Power Sleep mode selected. The Low-Power Sleep mode is intended for use with these peripherals:

- Brown-out Reset (BOR)

- Watchdog Timer (WDT)

- · External interrupt pin/interrupt-on-change pins

- Timer1 (with external clock source)

It is the responsibility of the end user to determine what is acceptable for their application when setting the VREGPM settings in order to ensure operation in Sleep.

| Note: | The PIC16LF15313/23 does not have a       |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|

|       | configurable Low-Power Sleep mode.        |  |  |  |  |  |  |  |  |  |

|       | PIC16LF15313/23 is an unregulated         |  |  |  |  |  |  |  |  |  |

|       | device and is always in the lowest power  |  |  |  |  |  |  |  |  |  |

|       | state when in Sleep, with no wake-up time |  |  |  |  |  |  |  |  |  |

|       | penalty. This device has a lower maximum  |  |  |  |  |  |  |  |  |  |

|       | VDD and I/O voltage than the              |  |  |  |  |  |  |  |  |  |

|       | PIC16F15313/23. See Section 37.0          |  |  |  |  |  |  |  |  |  |

|       | "Electrical Specifications" for more      |  |  |  |  |  |  |  |  |  |

|       | information.                              |  |  |  |  |  |  |  |  |  |

#### 11.3 IDLE Mode

When the Idle Enable (IDLEN) bit is clear (IDLEN = 0), the SLEEP instruction will put the device into full Sleep mode (see **Section 11.2 "Sleep Mode**"). When IDLEN is set (IDLEN = 1), the SLEEP instruction will put the device into IDLE mode. In IDLE mode, the CPU and memory operations are halted, but the peripheral clocks continue to run. This mode is similar to DOZE mode, except that in IDLE both the CPU and PFM are shut off.

| Note: | Peripherals using Fosc will continue      |  |  |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | running while in Idle (but not in Sleep). |  |  |  |  |  |  |  |  |  |  |

|       | Peripherals using HFINTOSCLFINTOSC        |  |  |  |  |  |  |  |  |  |  |

|       | will continue running in both Idle and    |  |  |  |  |  |  |  |  |  |  |

|       | Sleep.                                    |  |  |  |  |  |  |  |  |  |  |

**Note:** If CLKOUT is enabled (CLKOUT = 0, Configuration Word 1), the output will continue operating while in Idle.

#### 11.3.1 IDLE AND INTERRUPTS

IDLE mode ends when an interrupt occurs (even if GIE = 0), but IDLEN is not changed. The device can re-enter IDLE by executing the SLEEP instruction.

If Recover-on-Interrupt is enabled (ROI = 1), the interrupt that brings the device out of Idle also restores full-speed CPU execution when doze is also enabled.

#### 11.3.2 IDLE AND WDT

When in IDLE, the WDT Reset is blocked and will instead wake the device. The WDT wake-up is not an interrupt, therefore ROI does not apply.

Note: The WDT can bring the device out of IDLE, in the same way it brings the device out of Sleep. The DOZEN bit is not affected.

### 14.0 I/O PORTS

#### TABLE 14-1: PORT AVAILABILITY PER DEVICE

| Device         | PORTA | PORTC |

|----------------|-------|-------|

| PIC16(L)F15313 | •     |       |

| PIC16(L)F15323 | •     | •     |

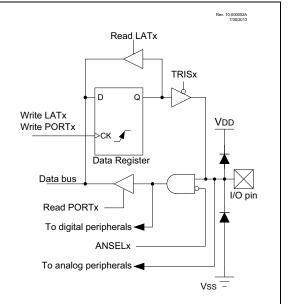

Each port has standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 14-1.

#### FIGURE 14-1: GENERIC I/O PORT OPERATION

#### 14.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 15.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

| R/W-0/0                      | U-0                                                          | R-0                                            | R/W-0/0        | R/W-0/0             | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |

|------------------------------|--------------------------------------------------------------|------------------------------------------------|----------------|---------------------|------------------|------------------|--------------|--|--|--|

| T0EN                         |                                                              | TOOUT                                          | T016BIT        |                     | TOOUT            | PS<3:0>          |              |  |  |  |

| bit 7                        |                                                              |                                                |                |                     |                  |                  | bit C        |  |  |  |

|                              |                                                              |                                                |                |                     |                  |                  |              |  |  |  |

| Legend:                      |                                                              |                                                |                |                     |                  |                  |              |  |  |  |

| R = Readable                 | e bit                                                        | W = Writable                                   | bit            | U = Unimplen        | nented bit, read | 1 as '0'         |              |  |  |  |

| u = Bit is uncl              | hanged                                                       | x = Bit is unk                                 | nown           | -n/n = Value a      | at POR and BO    | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is set             |                                                              | '0' = Bit is cle                               | ared           |                     |                  |                  |              |  |  |  |

|                              |                                                              |                                                |                |                     |                  |                  |              |  |  |  |

| bit 7                        | TOEN: Timer(                                                 |                                                |                |                     |                  |                  |              |  |  |  |

|                              |                                                              | lule is enabled                                |                | )<br>vest power mod |                  |                  |              |  |  |  |

| bit 6                        |                                                              | ited: Read as                                  |                | vest power mot      |                  |                  |              |  |  |  |

| bit 5                        | -                                                            |                                                |                |                     |                  |                  |              |  |  |  |

| DIL D                        | Timer0 output                                                | er0 Output bit (i<br>t bit                     | eau-oniy)      |                     |                  |                  |              |  |  |  |

| bit 4                        | -                                                            | er0 Operating                                  | as 16-bit Time | er Select bit       |                  |                  |              |  |  |  |

| 1 = Timer0 is a 16-bit timer |                                                              |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 0 = Timer0 is                                                | an 8-bit timer                                 |                |                     |                  |                  |              |  |  |  |

| bit 3-0                      | TOOUTPS<3:0>: Timer0 output postscaler (divider) select bits |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 1111 = 1:16  <br>1110 = 1:15                                 |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 1101 = 1:14                                                  |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 1100 = 1:13                                                  |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 1011 <b>= 1:12</b>                                           | Postscaler                                     |                |                     |                  |                  |              |  |  |  |

|                              | 1010 = 1:11 I                                                |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 1001 = 1:10                                                  |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 1000 = 1:9 P                                                 |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 0111 = 1:8 P                                                 |                                                |                |                     |                  |                  |              |  |  |  |

|                              |                                                              | 0110 = 1:7 Postscaler<br>0101 = 1:6 Postscaler |                |                     |                  |                  |              |  |  |  |

|                              | 0101 = 1.01                                                  |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 0011 = 1:4 P                                                 |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 0010 = 1:3 P                                                 |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 0001 = 1:2 P                                                 |                                                |                |                     |                  |                  |              |  |  |  |

|                              | 0000 = 1:1 P                                                 | ostecolor                                      |                |                     |                  |                  |              |  |  |  |

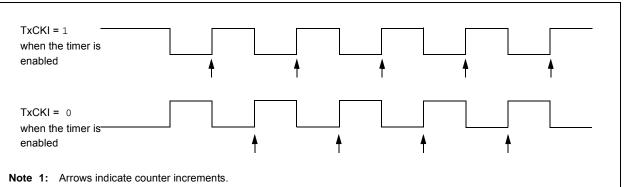

2: In Counter mode, a falling edge must be registered by the counter prior to the first incrementing rising edge of the clock.

| R/W/HC-0/0        | R/W-0/0                                                                            | R/W-0/0                     | R/W-0/0        | R/W-0/0                            | R/W-0/0        | R/W-0/0 | R/W-0/0 |  |  |  |  |

|-------------------|------------------------------------------------------------------------------------|-----------------------------|----------------|------------------------------------|----------------|---------|---------|--|--|--|--|

| 0N <sup>(1)</sup> |                                                                                    | CKPS<2:0>                   |                |                                    | OUTP           | S<3:0>  |         |  |  |  |  |

| bit 7             |                                                                                    |                             |                |                                    |                |         | bit 0   |  |  |  |  |

|                   |                                                                                    |                             |                |                                    |                |         |         |  |  |  |  |

| Legend:           |                                                                                    |                             |                |                                    |                |         |         |  |  |  |  |

| R = Readable      |                                                                                    | W = Writable                |                | U = Unimplemented bit, read as '0' |                |         |         |  |  |  |  |

| u = Bit is unch   | is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Res |                             |                |                                    |                |         |         |  |  |  |  |

| '1' = Bit is set  |                                                                                    | '0' = Bit is clea           | ared           | HC = Bit is cle                    | eared by hardv | vare    |         |  |  |  |  |

|                   |                                                                                    | <b>a</b>                    |                |                                    |                |         |         |  |  |  |  |

| bit 7             | ON: Timerx                                                                         |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 1 = Timerx                                                                         | is on<br>is off: all counte | ra and stata n | achinas ara ra                     | act            |         |         |  |  |  |  |

| h:+ 0 4           |                                                                                    |                             |                |                                    | sei            |         |         |  |  |  |  |

| bit 6-4           |                                                                                    | : Timer2-type Cl            | ock Prescale   | Select bits                        |                |         |         |  |  |  |  |

|                   | 111 = 1:128 Prescaler                                                              |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 110 = 1:64 Prescaler<br>101 = 1:32 Prescaler                                       |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 100 = 1:16 Prescaler                                                               |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 011 = 1:8 Prescaler                                                                |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 010 = 1:4 P                                                                        | escaler                     |                |                                    |                |         |         |  |  |  |  |

|                   | 001 = 1:2 P                                                                        |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 000 = 1:1 P                                                                        | rescaler                    |                |                                    |                |         |         |  |  |  |  |

| bit 3-0           | OUTPS<3:0>: Timerx Output Postscaler Select bits                                   |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 1111 = 1:16                                                                        |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 1110 = 1:15 Postscaler                                                             |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 1101 = 1:14 Postscaler<br>1100 = 1:13 Postscaler                                   |                             |                |                                    |                |         |         |  |  |  |  |

|                   |                                                                                    |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 1011 = 1:12 Postscaler<br>1010 = 1:11 Postscaler                                   |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 1001 = 1:10                                                                        |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 1000 = 1:9 Postscaler                                                              |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 0111 = 1:8 Postscaler                                                              |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 0110 = 1:7 Postscaler                                                              |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 0101 = 1:6 F                                                                       |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 0100 = 1:5 F                                                                       |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 0011 = 1:4 F<br>0010 = 1:3 F                                                       |                             |                |                                    |                |         |         |  |  |  |  |

|                   | 0010 = 1.3 F                                                                       |                             |                |                                    |                |         |         |  |  |  |  |

|                   |                                                                                    |                             |                |                                    |                |         |         |  |  |  |  |

#### REGISTER 27-2: T2CON: TIMER2 CONTROL REGISTER

Note 1: In certain modes, the ON bit will be auto-cleared by hardware. See Section 27.5 "Operation Examples".

| R/W-0/0          | U-0          | U-0                                    | U-0           | R/W-x/u          | R/W-x/u          | R/W-x/u          | R/W-x/u      |

|------------------|--------------|----------------------------------------|---------------|------------------|------------------|------------------|--------------|

| LCxPOL           | —            | —                                      | _             | LCxG4POL         | LCxG3POL         | LCxG2POL         | LCxG1POL     |

| bit 7            |              |                                        |               |                  |                  |                  | bit 0        |

|                  |              |                                        |               |                  |                  |                  |              |

| Legend:          |              |                                        |               |                  |                  |                  |              |

| R = Readable     | bit          | W = Writable                           | bit           | U = Unimpler     | mented bit, read | l as '0'         |              |

| u = Bit is unch  | anged        | x = Bit is unkn                        | iown          | -n/n = Value a   | at POR and BO    | R/Value at all o | other Resets |

| '1' = Bit is set |              | '0' = Bit is clea                      | ared          |                  |                  |                  |              |

|                  |              |                                        |               |                  |                  |                  |              |

| bit 7            | LCxPOL: CLO  | CxOUT Output                           | Polarity Con  | trol bit         |                  |                  |              |

|                  |              | ut of the logic o                      |               |                  |                  |                  |              |

|                  |              | ut of the logic o                      |               | erted            |                  |                  |              |

| bit 6-4          | •            | ted: Read as 'o                        |               |                  |                  |                  |              |

| bit 3            |              | Gate 3 Output I                        | -             |                  |                  |                  |              |

|                  | •            | 0                                      |               | n applied to the | logic cell       |                  |              |

| h:# 0            |              | ut of gate 3 is r                      |               |                  |                  |                  |              |

| bit 2            |              | Gate 2 Output I                        | ,             |                  | 1                |                  |              |

|                  |              | ut of gate 2 is i<br>ut of gate 2 is r |               | n applied to the | logic cell       |                  |              |

| bit 1            | •            | Gate 1 Output I                        |               | rol bit          |                  |                  |              |

|                  |              |                                        | ,             | applied to the   | logic cell       |                  |              |

|                  | 0 = The outp | ut of gate 1 is r                      | not inverted  |                  | 0                |                  |              |

| bit 0            | LCxG1POL:    | Gate 0 Output I                        | Polarity Cont | rol bit          |                  |                  |              |

|                  | •            | •                                      |               | n applied to the | logic cell       |                  |              |

|                  | 0 = The outp | ut of gate 0 is r                      | not inverted  |                  |                  |                  |              |

#### REGISTER 31-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

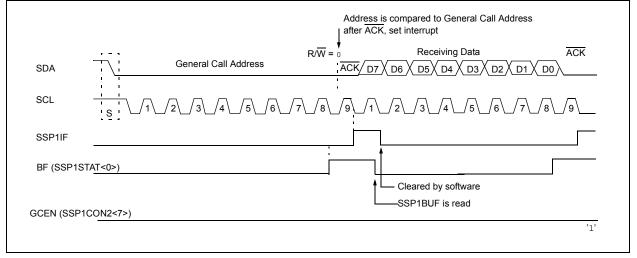

#### 32.5.8 GENERAL CALL ADDRESS SUPPORT

The addressing procedure for the  $I^2C$  bus is such that the first byte after the Start condition usually determines which device will be the slave addressed by the master device. The exception is the general call address which can address all devices. When this address is used, all devices should, in theory, respond with an acknowledge.

The general call address is a reserved address in the  $I^2C$  protocol, defined as address  $0 \ge 0.00$ . When the GCEN bit of the SSP1CON2 register is set, the slave module will automatically ACK the reception of this address regardless of the value stored in SSP1ADD. After the slave clocks in an address of all zeros with the R/W bit clear, an interrupt is generated and slave software can read SSP1BUF and respond. Figure 32-24 shows a general call reception sequence.

In 10-bit Address mode, the UA bit will not be set on the reception of the general call address. The slave will prepare to receive the second byte as data, just as it would in 7-bit mode.

If the AHEN bit of the SSP1CON3 register is set, just as with any other address reception, the slave hardware will stretch the clock after the eighth falling edge of SCL. The slave must then set its ACKDT value and release the clock with communication progressing as it would normally.

32.5.9 SSP MASK REGISTER

An SSP Mask (SSP1MSK) register (Register 32-5) is available in I<sup>2</sup>C Slave mode as a mask for the value held in the SSP1SR register during an address comparison operation. A zero ('0') bit in the SSP1MSK register has the effect of making the corresponding bit of the received address a "don't care". This register is reset to all '1's upon any Reset condition and, therefore, has no effect on standard SSP operation until written with a mask value.

The SSP Mask register is active during:

- 7-bit Address mode: address compare of A<7:1>.

- 10-bit Address mode: address compare of A<7:0> only. The SSP mask has no effect during the reception of the first (high) byte of the address.

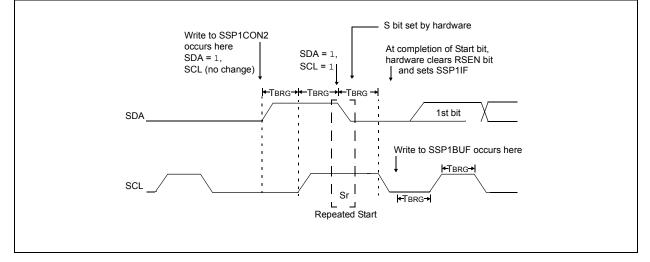

### 32.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 32-27) occurs when the RSEN bit of the SSP1CON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSP1CON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSP1STAT register will be set. The SSP1IF bit will not be set until the Baud Rate Generator has timed out.

- Note 1: If RSEN is programmed while any other event is in progress, it will not take effect.

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

#### FIGURE 32-27: REPEATED START CONDITION WAVEFORM

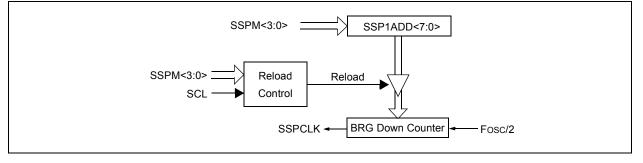

#### 32.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSP1ADD register (Register 32-6). When a write occurs to SSP1BUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 32-40 triggers the value from SSP1ADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 32-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSP1ADD.

#### EQUATION 32-1:

$FCLOCK = \frac{FOSC}{(SSP1ADD + 1)(4)}$

#### FIGURE 32-40: BAUD RATE GENERATOR BLOCK DIAGRAM

**Note:** Values of 0x00, 0x01 and 0x02 are not valid for SSP1ADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

#### TABLE 32-2: MSSP CLOCK RATE W/BRG

| Fosc   | Fcy   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 37-4 to ensure the system is designed to support IOL requirements.

| U-0            | U-0                                                       | U-0                           | U-0  | R/W-0/0                            | R/W-0/0 | R/W-0/0        | R/W-0/0      |  |  |  |  |

|----------------|-----------------------------------------------------------|-------------------------------|------|------------------------------------|---------|----------------|--------------|--|--|--|--|

| _              | _                                                         | _                             | _    |                                    | CLKRC   | LK<3:0>        |              |  |  |  |  |

| bit 7          |                                                           |                               |      |                                    |         |                | bit (        |  |  |  |  |

| Legend:        |                                                           |                               |      |                                    |         |                |              |  |  |  |  |

| R = Readab     | ole bit                                                   | W = Writable b                | oit  | U = Unimplemented bit, read as '0' |         |                |              |  |  |  |  |

| u = Bit is un  | unchanged x = Bit is unknown -n/n = Value at POR and BOR/ |                               |      |                                    |         | R/Value at all | other Resets |  |  |  |  |

| '1' = Bit is s | et                                                        | '0' = Bit is clea             | ared |                                    |         |                |              |  |  |  |  |

|                |                                                           |                               |      |                                    |         |                |              |  |  |  |  |

| bit 7-4        | -                                                         | ted: Read as '0               |      |                                    |         |                |              |  |  |  |  |

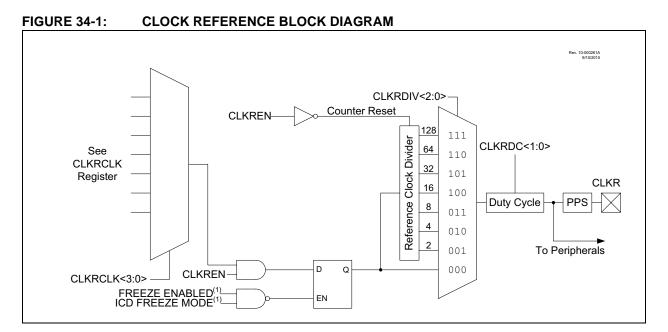

| oit 3-0        | CLKRCLK<3                                                 | CLKRCLK<3:0>: CLKR Input bits |      |                                    |         |                |              |  |  |  |  |

|                | Clock Selection                                           | Clock Selection               |      |                                    |         |                |              |  |  |  |  |

|                | 1111 = Rese                                               | rved                          |      |                                    |         |                |              |  |  |  |  |

|                | •                                                         |                               |      |                                    |         |                |              |  |  |  |  |

|                | •                                                         |                               |      |                                    |         |                |              |  |  |  |  |

|                | •<br>1011 = Rese                                          | nvod                          |      |                                    |         |                |              |  |  |  |  |

|                | 1011 = Rese<br>1010 = LC4                                 |                               |      |                                    |         |                |              |  |  |  |  |

|                | $1010 = LC4_{1001}$                                       |                               |      |                                    |         |                |              |  |  |  |  |

|                | 1000 = LC2                                                |                               |      |                                    |         |                |              |  |  |  |  |

|                | 0111 = LC1                                                |                               |      |                                    |         |                |              |  |  |  |  |

|                | 0110 = NCO                                                |                               |      |                                    |         |                |              |  |  |  |  |

|                | 0101 = Rese                                               | rved                          |      |                                    |         |                |              |  |  |  |  |

|                |                                                           | TOSC (31.25 k                 |      |                                    |         |                |              |  |  |  |  |

|                |                                                           | TOSC (500 kHz                 | z)   |                                    |         |                |              |  |  |  |  |

|                | 0010 = LFIN                                               |                               |      |                                    |         |                |              |  |  |  |  |

|                | 0001 = HFIN                                               | IOSC                          |      |                                    |         |                |              |  |  |  |  |

#### TABLE 34-1: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK REFERENCE OUTPUT

| Name     | Bit 7  | Bit 6 | Bit 5 | Bit 4       | Bit 3                | Bit 2  | Bit 1 | Bit 0 | Register<br>on Page |  |  |

|----------|--------|-------|-------|-------------|----------------------|--------|-------|-------|---------------------|--|--|

| CLKRCON  | CLKREN |       |       | CLKRD       | DC<1:0> CLKRDIV<2:0> |        |       |       | 441                 |  |  |

| CLKRCLK  | —      | _     | _     | _           |                      |        | 442   |       |                     |  |  |

| CLCxSELy | —      | _     |       |             | LCxDy                | S<5:0> |       |       | 352                 |  |  |

| RxyPPS   | _      | _     | _     | RxyPPS<4:0> |                      |        |       |       | 192                 |  |  |

|          |        |       |       |             |                      |        |       |       |                     |  |  |

Legend: — = unimplemented, read as '0'. Shaded cells are not used by the CLKR module.

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ label ] BCF f,b                                                   |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label]BTFSC f,b                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = 0</b>                                                                                                                                                                                                       |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b', in register 'f', is '0', the next<br>instruction is discarded, and a NOP is<br>executed instead, making this a<br>2-cycle instruction. |

BTFSS

| BRA              | Relative Branch                                                                                                                                                                                                                                 |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BRA   label<br>[ <i>label</i> ] BRA   \$+k                                                                                                                                                                                     |

| Operands:        | -256 $\leq$ label - PC + 1 $\leq$ 255 -256 $\leq$ k $\leq$ 255                                                                                                                                                                                  |

| Operation:       | $(PC) + 1 + k \rightarrow PC$                                                                                                                                                                                                                   |

| Status Affected: | None                                                                                                                                                                                                                                            |

| Description:     | Add the signed 9-bit literal 'k' to the<br>PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + k. This instruction is a<br>2-cycle instruction. This branch has a<br>limited range. |

| Syntax:          | [ <i>label</i> ] BRW                                                                                                                                                                                          |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                                                                          |

| Operation:       | $(PC) + (W) \to PC$                                                                                                                                                                                           |

| Status Affected: | None                                                                                                                                                                                                          |

| Description:     | Add the contents of W (unsigned) to<br>the PC. Since the PC will have<br>incremented to fetch the next<br>instruction, the new address will be<br>PC + 1 + (W). This instruction is a<br>2-cycle instruction. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [label]BSF f,b                                                      |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f \le b >)$                                         |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                             |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b < 7 \end{array}$                                                                                                                                                |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                            |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next instruction<br>is discarded and a NOP is executed<br>instead, making this a 2-cycle<br>instruction. |

Bit Test f, Skip if Set

| MOVIW            | Move INDFn to W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVIW ++FSRn<br>[ <i>label</i> ] MOVIWFSRn<br>[ <i>label</i> ] MOVIW FSRn++<br>[ <i>label</i> ] MOVIW FSRn<br>[ <i>label</i> ] MOVIW k[FSRn]                                                                                                                                                                                                                                                                                                                                        |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01,10,11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Operation:       | $\begin{split} &\text{INDFn} \rightarrow W \\ &\text{Effective address is determined by} \\ &\text{•} \ &\text{FSR} + 1 \ (\text{preincrement}) \\ &\text{•} \ &\text{FSR} + 1 \ (\text{predecrement}) \\ &\text{•} \ &\text{FSR} + k \ (\text{relative offset}) \\ &\text{After the Move, the FSR value will be} \\ &\text{either:} \\ &\text{•} \ &\text{FSR} + 1 \ (\text{all increments}) \\ &\text{•} \ &\text{FSR} - 1 \ (\text{all decrements}) \\ &\text{•} \ &\text{Unchanged} \end{split}$ |

| Status Affected: | Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h -FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

#### MOVLB Move literal to BSR

| Syntax:          | [ label ] MOVLB k                                                    |

|------------------|----------------------------------------------------------------------|

| Operands:        | $0 \le k \le$                                                        |

| Operation:       | $k \rightarrow BSR$                                                  |

| Status Affected: | None                                                                 |

| Description:     | The 6-bit literal 'k' is loaded into the Bank Select Register (BSR). |

| MOVLP            | Move literal to PCLATH                                                                         |

|------------------|------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]MOVLP k                                                                        |

| Operands:        | $0 \leq k \leq 127$                                                                            |

| Operation:       | $k \rightarrow PCLATH$                                                                         |

| Status Affected: | None                                                                                           |

| Description:     | The 7-bit literal 'k' is loaded into the PCLATH register.                                      |

| MOVLW            | Move literal to W                                                                              |

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                       |

| Operands:        | $0 \le k \le 255$                                                                              |

| Operation:       | $k \rightarrow (W)$                                                                            |

| Status Affected: | None                                                                                           |

| Description:     | The 8-bit literal 'k' is loaded into W reg-<br>ister. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                              |

| Cycles:          | 1                                                                                              |

| Example:         | MOVLW 0x5A                                                                                     |

|                  | After Instruction<br>W = 0x5A                                                                  |

| MOVWF            | Move W to f                                                                                    |

| Syntax:          | [ <i>label</i> ] MOVWF f                                                                       |

| Operands:        | $0 \leq f \leq 127$                                                                            |

| Operation:       | $(W) \rightarrow (f)$                                                                          |

| Status Affected: | None                                                                                           |

| Description:     | Move data from W register to register 'f'.                                                     |

| Words:           | 1                                                                                              |

| Cycles:          | 1                                                                                              |

| Example:         | MOVWF LATA                                                                                     |

|                  | Before Instruction                                                                             |

|                  | LATA = 0xFF                                                                                    |

$\label{eq:W} \begin{array}{l} W = 0x4F\\ \mbox{After Instruction}\\ \mbox{LATA} = 0x4F\\ \mbox{W} = 0x4F \end{array}$

| ΜΟΥΨΙ            | Move W to INDFn                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWI ++FSRn<br>[ <i>label</i> ] MOVWIFSRn<br>[ <i>label</i> ] MOVWI FSRn++<br>[ <i>label</i> ] MOVWI FSRn<br>[ <i>label</i> ] MOVWI k[FSRn]                                                                                                                                                                                                                                                                  |

| Operands:        | n ∈ [0,1]<br>mm ∈ [00,01, 10, 11]<br>-32 ≤ k ≤ 31                                                                                                                                                                                                                                                                                                                                                                              |

| Operation:       | $\label{eq:W} \begin{split} W &\rightarrow INDFn \\ \text{Effective address is determined by} \\ \bullet \ FSR + 1 \ (\text{preincrement}) \\ \bullet \ FSR + 1 \ (\text{preincrement}) \\ \bullet \ FSR + k \ (\text{relative offset}) \\ \text{After the Move, the FSR value will be either:} \\ \bullet \ FSR + 1 \ (\text{all increments}) \\ \bullet \ FSR + 1 \ (\text{all increments}) \\ \text{Unchanged} \end{split}$ |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh. Incrementing/decrementing it beyond these bounds will cause it to wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

| RESET            | Software Reset                                                                 |  |  |  |  |

|------------------|--------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] RESET                                                                  |  |  |  |  |

| Operands:        | None                                                                           |  |  |  |  |

| Operation:       | Execute a device Reset. Resets the $\overline{RI}$ flag of the PCON register.  |  |  |  |  |

| Status Affected: | None                                                                           |  |  |  |  |

| Description:     | This instruction provides a way to<br>execute a hardware Reset by<br>software. |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                                           |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETFIE k                                                                                                                                                                                       |  |  |  |  |

| Operands:        | None                                                                                                                                                                                                            |  |  |  |  |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                         |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                            |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed<br>and Top-of-Stack (TOS) is loaded in<br>the PC. Interrupts are enabled by<br>setting Global Interrupt Enable bit,<br>GIE (INTCON<7>). This is a 2-cycle<br>instruction. |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                               |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                               |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                                          |  |  |  |  |

|                  | After Interrupt<br>PC = TOS<br>GIE = 1                                                                                                                                                                          |  |  |  |  |