Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 256 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15323-e-p |

# 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- · Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Device Information Area (DIA)

- Device Configuration Information (DCI)

- Revision ID

- · Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- · PCL and PCLATH

- Stack

- · Indirect Addressing

- · NVMREG access

# 4.1 Program Memory Organization

The enhanced mid-range core has a 15-bit program counter capable of addressing 32K x 14 program memory space. Table 4-1 shows the memory sizes implemented. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

# TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device            | Program Memory Size (Words) | Last Program Memory Address |

|-------------------|-----------------------------|-----------------------------|

| PIC16(L)F15313/23 | 2048                        | 07FFh                       |

TABLE 4-4: PIC16(L)F15313/23 MEMORY MAP, BANKS 0-7

|      | BANK 0               |        | BANK 1        |       | BANK 2        |        | BANK 3        |        | BANK 4        |        | BANK 5        |       | BANK 6        |        | BANK 7        |

|------|----------------------|--------|---------------|-------|---------------|--------|---------------|--------|---------------|--------|---------------|-------|---------------|--------|---------------|

| 000h |                      | 080h   |               | 100h  |               | 180h   |               | 200h   |               | 280h   |               | 300h  |               | 380h   |               |

|      | Core Register        |        | Core Register |       | Core Register |        | Core Register |        | Core Register |        | Core Register |       | Core Register |        | Core Register |

|      | (Table 4-3)          |        | (Table 4-3)   |       | (Table 4-3)   |        | (Table 4-3)   |        | (Table 4-3)   |        | (Table 4-3)   |       | (Table 4-3)   |        | (Table 4-3)   |

| 00Bh |                      | 08Bh   |               | 10Bh  |               | 18Bh   |               | 20Bh   |               | 28Bh   |               | 30Bh  |               | 38Bh   |               |

| 00Ch | PORTA                | 08Ch   |               | 10Ch  | _             | 18Ch   | SSP1BUF       | 20Ch   | TMR1L         | 28Ch   | TMR2          | 30Ch  | CCPR1L        | 38Ch   | PWM6DCL       |

| 00Dh | _                    | 08Dh   | _             | 10Dh  | _             | 18Dh   | SSP1ADD       | 20Dh   | TMR1H         | 28Dh   | PR2           | 30Dh  | CCPR1H        | 38Dh   | PWM6DCH       |

| 00Eh | PORTC <sup>(2)</sup> | 08Eh   | _             | 10Eh  | _             | 18Eh   | SSP1MASK      | 20Eh   | T1CON         | 28Eh   | T2CON         | 30Eh  | CCP1CON       | 38Eh   | PWM6CON       |

| 00Fh | _                    | 08Fh   |               | 10Fh  | _             | 18Fh   | SSP1STAT      | 20Fh   | T1GCON        | 28Fh   | T2HLT         | 30Fh  | CCP1CAP       | 38Fh   | _             |

| 010h | _                    | 090h   | _             | 110h  | _             | 190h   | SSP1CON1      | 210h   | T1GATE        | 290h   | T2CLK         | 310h  | CCPR2L        | 390h   | _             |

| 011h | _                    | 091h   | _             | 111h  |               | 191h   | SSP1CON2      | 211h   | T1CLK         | 291h   | T2ERS         | 311h  | CCPR2H        | 391h   | _             |

| 012h | TRISA                | 092h   | _             | 112h  | _             | 192h   | SSP1CON3      | 212h   | 1             | 292h   | _             | 312h  | CCP2CON       | 392h   | _             |

| 013h | _                    | 093h   | _             | 113h  | _             | 193h   | _             | 213h   | 1             | 293h   |               | 313h  | CCP2CAP       | 393h   | _             |

| 014h | TRISC <sup>(2)</sup> | 094h   |               | 114h  | _             | 194h   | _             | 214h   | _             | 294h   | _             | 314h  | PWM3DCL       | 394h   | _             |

| 015h | _                    | 095h   | _             | 115h  | _             | 195h   | _             | 215h   | I             | 295h   | _             | 315h  | PWM3DCH       | 395h   | _             |

| 016h | _                    | 096h   | _             | 116h  | _             | 196h   | _             | 216h   | I             | 296h   | _             | 316h  | PWM3CON       | 396h   | _             |

| 017h | -                    | 097h   | -             | 117h  | _             | 197h   | _             | 217h   | _             | 297h   | -             | 317h  |               | 397h   | _             |

| 018h | LATA                 | 098h   | _             | 118h  | _             | 198h   | _             | 218h   | _             | 298h   | -             | 318h  | PWM4DCL       | 398h   | _             |

| 019h | _                    | 099h   | _             | 119h  | RC1REG1       | 199h   | _             | 219h   |               | 299h   | _             | 319h  | PWM4DCH       | 399h   | _             |

| 01Ah | LATC <sup>(2)</sup>  | 09Ah   | -             | 11Ah  | TX1REG1       | 19Ah   | _             | 21Ah   | _             | 29Ah   | -             | 31Ah  | PWM4CON       | 39Ah   | _             |

| 01Bh | _                    | 09Bh   | ADRESL        | 11Bh  | SP1BRG1L      | 19Bh   | _             | 21Bh   | _             | 29Bh   | _             | 31Bh  | _             | 39Bh   | _             |

| 01Ch | _                    | 09Ch   | ADRESH        | 11Ch  | SP1BRG1H      | 19Ch   | _             | 21Ch   | _             | 29Ch   | _             | 31Ch  | PWM5DCL       | 39Ch   | _             |

| 01Dh | _                    | 09Dh   | ADCON0        | 11Dh  | RC1STA1       | 19Dh   | _             | 21Dh   | I             | 29Dh   | _             | 31Dh  | PWM5DCH       | 39Dh   | _             |

| 01Eh | _                    | 09Eh   | ADCON1        | 11Eh  | TX1STA1       | 19Eh   | _             | 21Eh   | _             | 29Eh   | -             | 31Eh  | PWM5CON       | 39Eh   | _             |

| 01Fh | -                    | 09Fh   | ADACT         | 11Fh  | BAUD1CON1     | 19Fh   | _             | 21Fh   | _             | 29Fh   | -             | 31Fh  | _             | 39Fh   | _             |

| 020h |                      | 0A0h   |               | 120h  |               | 1A0h   |               | 220h   |               | 2A0h   |               | 320h  |               | 3A0h   |               |

|      |                      |        |               |       |               |        |               |        |               |        |               |       |               |        |               |

|      |                      |        |               |       |               |        |               |        |               |        |               |       |               |        |               |

|      |                      |        | General       |       | General       |        |               |        |               |        |               | 32Fh  |               |        |               |

|      |                      |        | Purpose       |       | Purpose       |        | Unimplemented |        | Unimplemented |        | Unimplemented | 330h  | Unimplemented |        | Unimplemented |

|      | General              |        | Register      |       | Register      |        | Read as '0'   |        | Read as '0'   |        | Read as '0'   | 000   | Read as '0'   |        | Read as '0'   |

|      | Purpose              |        | 80 Bytes      |       | 80 Bytes      |        |               |        |               |        |               |       |               |        |               |

|      | Register             |        |               |       |               |        |               |        |               |        |               |       |               |        |               |

|      | 96 Bytes             |        |               |       |               |        |               |        |               |        |               |       |               |        |               |

|      |                      | 0EFh   |               | 16Fh  |               | 1EFh   |               | 26Fh   |               | 2EFh   |               | 36Fh  |               | 3EFh   |               |

|      |                      | 0F0h   | Common RAM    | 170h  | Common RAM    | 1F0h   | Common RAM    | 270h   | Common RAM    | 2F0h   | Common RAM    | 370h  | Common RAM    | 3F0h   | Common RAM    |

|      |                      | 01 011 | Accesses      | 17011 | Accesses      | 11 011 | Accesses      | 27011  | Accesses      | 21 011 | Accesses      | 37011 | Accesses      | 31 011 | Accesses      |

| 0755 |                      | 0FFh   | 70h-7Fh       | 17Fh  | 70h-7Fh       | 1FFh   | 70h-7Fh       | 27Fh   | 70h-7Fh       | 2FFh   | 70h-7Fh       | 2755  | 70h-7Fh       | 3FFh   | 70h-7Fh       |

| 07Fh |                      | UFFN   | 7 011 71 11   | 17FN  | 7 7 11 11     | IFFN   | 70117111      | _ ∠/⊦n | 70117111      | ∠⊦⊦n   | 70117111      | 37Fh  | 70117111      | 3FFN   | 7 011 71 11   |

Note 1: Unimplemented locations read as '0'.

2: Present only in PIC16(L)F15323.

# REGISTER 10-2: PIE0: PERIPHERAL INTERRUPT ENABLE REGISTER 0

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | R/W-0/0 |

|-------|-----|---------|---------|-----|-----|-----|---------|

| _     | _   | TMR0IE  | IOCIE   | _   | _   |     | INTE    |

| bit 7 |     |         |         |     |     |     | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHS = Hardware set

bit 7-6 Unimplemented: Read as '0' bit 5 TMR0IE: Timer0 Overflow Interrupt Enable bit 1 = Enables the Timer0 interrupt 0 = Disables the Timer0 interrupt bit 4 IOCIE: Interrupt-on-Change Interrupt Enable bit 1 = Enables the IOC change interrupt 0 = Disables the IOC change interrupt bit 3-1 Unimplemented: Read as '0' bit 0 **INTE:** INT External Interrupt Flag bit<sup>(1)</sup> 1 = Enables the INT external interrupt 0 = Disables the INT external interrupt

Note 1: The External Interrupt GPIO pin is selected by INTPPS (Register 15-1).

Note: Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by PIE1-PIE7. Interrupt sources controlled by the PIE0 register do not require PEIE to be set in order to allow interrupt vectoring (when GIE is set).

# REGISTER 10-12: PIR2: PERIPHERAL INTERRUPT REQUEST REGISTER 2

| U-0   | R/W/HS-0/0 | U-0 | U-0 | U-0 | U-0 | R/W/HS-0/0          | R/W/HS-0/0 |

|-------|------------|-----|-----|-----|-----|---------------------|------------|

| _     | ZCDIF      |     | _   | -   | _   | C2IF <sup>(1)</sup> | C1IF       |

| bit 7 |            |     |     |     |     |                     | bit 0      |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HS = Hardware set                                     |

bit 7 **Unimplemented**: Read as '0'

bit 6 ZCDIF: Zero-Cross Detect (ZCD1) Interrupt Flag bit

1 = An enabled rising and/or falling ZCD1 event has been detected (must be cleared in software)

0 = No ZCD1 event has occurred

bit 5-2 **Unimplemented**: Read as '0'

bit 1 C2IF: Comparator C2 Interrupt Flag bit

1 = Comparator 2 interrupt asserted (must be cleared in software)

0 = Comparator 2 interrupt not asserted

bit 0 C1IF: Comparator C1 Interrupt Flag bit

1 = Comparator 1 interrupt asserted (must be cleared in software)

0 = Comparator 1 interrupt not asserted

Note 1: Present only on PIC16(L)F15323.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 20-4: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

| R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |

|---------|-------------|---------|---------|---------|---------|---------|---------|--|

|         |             |         | ADRES   | 6<9:2>  |         |         |         |  |

| bit 7   | bit 7 bit 0 |         |         |         |         |         |         |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **ADRES<9:2>**: ADC Result Register bits Upper eight bits of 10-bit conversion result

# REGISTER 20-5: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

| ADRES   | S<1:0>  | _       | _       | _       | _       | _       | _       |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 ADRES<1:0>: ADC Result Register bits

Lower two bits of 10-bit conversion result

bit 5-0 **Reserved**: Do not use.

# TABLE 21-1: SUMMARY OF REGISTERS ASSOCIATED WITH THE DAC1 MODULE

| Name                   | Bit 7  | Bit 6 | Bit 5   | Bit 4      | Bit 3          | Bit 2 | Bit 1 | Bit 0   | Register on page |

|------------------------|--------|-------|---------|------------|----------------|-------|-------|---------|------------------|

| DAC1CON0               | DAC1EN | _     | DAC10E1 | DAC10E2    | 2 DAC1PSS<1:0> |       | _     | DAC1NSS | 232              |

| DAC1CON1               | _      | _     | _       | DAC1R<4:0> |                |       |       |         |                  |

| CM1PSEL                | _      | _     | _       | — PCH<2:0> |                |       |       | 252     |                  |

| CM2PSEL <sup>(1)</sup> | _      | _     | _       | — PCH<2:0> |                |       |       | 252     |                  |

**Legend:** — = Unimplemented location, read as '0'. Shaded cells are not used with the DAC module.

Note 1: Present on PIC16(L)F15323 only.

#### 23.2 Comparator Control

Each comparator has two control registers: CMxCON0 and CMxCON1.

The CMxCON0 register (see Register 23-1) contains Control and Status bits for the following:

- Enable

- Output

- · Output polarity

- · Hysteresis enable

- · Timer1 output synchronization

The CMxCON1 register (see Register 23-2) contains Control bits for the following:

- Interrupt on positive/negative edge enables

- The CMxNSEL and CMxPSEL (Register 23-3 and Register 23-4) contain control bits for the following:

- Positive input channel selection

- Negative input channel selection

#### 23.2.1 COMPARATOR ENABLE

Setting the CxON bit of the CMxCON0 register enables the comparator for operation. Clearing the CxON bit disables the comparator resulting in minimum current consumption.

#### 23.2.2 COMPARATOR OUTPUT

The output of the comparator can be monitored by reading either the CxOUT bit of the CMxCON0 register or the MCxOUT bit of the CMOUT register.

The comparator output can also be routed to an external pin through the RxyPPS register (Register 15-2). The corresponding TRIS bit must be clear to enable the pin as an output.

Note 1: The internal output of the comparator is latched with each instruction cycle. Unless otherwise specified, external outputs are not latched.

#### 23.2.3 COMPARATOR OUTPUT POLARITY

Inverting the output of the comparator is functionally equivalent to swapping the comparator inputs. The polarity of the comparator output can be inverted by setting the CxPOL bit of the CMxCON0 register. Clearing the CxPOL bit results in a non-inverted output.

Table 23-2 shows the output state versus input conditions, including polarity control.

TABLE 23-2: COMPARATOR OUTPUT STATE VS. INPUT CONDITIONS

| Input Condition | CxPOL | CxOUT |  |  |

|-----------------|-------|-------|--|--|

| CxVn > CxVp     | 0     | 0     |  |  |

| CxVn < CxVp     | 0     | 1     |  |  |

| CxVn > CxVp     | 1     | 1     |  |  |

| CxVn < CxVp     | 1     | 0     |  |  |

# REGISTER 26-2: T1GCON: TIMER1 GATE CONTROL REGISTER

| R/W-0/u | R/W-0/u | R/W-0/u | R/W-0/u | R/W/HC-0/u | R-x/x | U-0 | U-0   |

|---------|---------|---------|---------|------------|-------|-----|-------|

| GE      | GPOL    | GTM     | GSPM    | GGO/DONE   | GVAL  | _   | _     |

| bit 7   |         |         |         |            |       |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | HC = Bit is cleared by hardware                       |

|         | •                                                                                    |

|---------|--------------------------------------------------------------------------------------|

|         |                                                                                      |

| bit 7   | GE: Timer1 Gate Enable bit                                                           |

|         | $\underline{If\;ON=0}:$                                                              |

|         | This bit is ignored                                                                  |

|         | If ON = 1:                                                                           |

|         | 1 = Timer1 counting is controlled by the Timer1 gate function                        |

| 1 '' 0  | 0 = Timer1 is always counting                                                        |

| bit 6   | GPOL: Timer1 Gate Polarity bit                                                       |

|         | 1 = Timer1 gate is active-high (Timer1 counts when gate is high)                     |

|         | 0 = Timer1 gate is active-low (Timer1 counts when gate is low)                       |

| bit 5   | GTM: Timer1 Gate Toggle Mode bit                                                     |

|         | 1 = Timer1 Gate Toggle mode is enabled                                               |

|         | 0 = Timer1 Gate Toggle mode is disabled and toggle flip-flop is cleared              |

|         | Timer1 gate flip-flop toggles on every rising edge.                                  |

| bit 4   | GSPM: Timer1 Gate Single-Pulse Mode bit                                              |

|         | 1 = Timer1 Gate Single-Pulse mode is enabled                                         |

|         | 0 = Timer1 Gate Single-Pulse mode is disabled                                        |

| bit 3   | GGO/DONE: Timer1 Gate Single-Pulse Acquisition Status bit                            |

|         | 1 = Timer1 gate single-pulse acquisition is ready, waiting for an edge               |

|         | 0 = Timer1 gate single-pulse acquisition has completed or has not been started       |

|         | This bit is automatically cleared when GSPM is cleared                               |

| bit 2   | GVAL: Timer1 Gate Value Status bit                                                   |

|         | Indicates the current state of the Timer1 gate that could be provided to TMR1H:TMR1L |

|         | Unaffected by Timer1 Gate Enable (GE)                                                |

| bit 1-0 | Unimplemented: Read as '0'                                                           |

# REGISTER 29-2: PWMxDCH: PWM DUTY CYCLE HIGH BITS

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | PWMxE   | C<9:2>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-0 **PWMxDC<9:2>:** PWM Duty Cycle Most Significant bits

These bits are the MSbs of the PWM duty cycle. The two LSbs are found in PWMxDCL Register.

#### REGISTER 29-3: PWMxDCL: PWM DUTY CYCLE LOW BITS

| R/W-x/u | R/W-x/u | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|-----|-----|-----|-----|-----|-------|

| PWMxD   | C<1:0>  | _   | _   | _   | _   | _   | _     |

| bit 7   |         |     |     |     |     |     | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 **PWMxDC<1:0>:** PWM Duty Cycle Least Significant bits

These bits are the LSbs of the PWM duty cycle. The MSbs are found in PWMxDCH Register.

bit 5-0 **Unimplemented:** Read as '0'

# REGISTER 31-2: CLCxPOL: SIGNAL POLARITY CONTROL REGISTER

| R/W-0/0 | U-0 | U-0 | U-0 | R/W-x/u  | R/W-x/u  | R/W-x/u  | R/W-x/u  |

|---------|-----|-----|-----|----------|----------|----------|----------|

| LCxPOL  | _   | _   | _   | LCxG4POL | LCxG3POL | LCxG2POL | LCxG1POL |

| bit 7   |     |     |     | •        |          |          | bit 0    |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | LCxPOL: CLCxOUT Output Polarity Control bit  1 = The output of the logic cell is inverted  0 = The output of the logic cell is not inverted |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-4 | Unimplemented: Read as '0'                                                                                                                  |

| bit 3   | LCxG4POL: Gate 3 Output Polarity Control bit                                                                                                |

|         | <ul><li>1 = The output of gate 3 is inverted when applied to the logic cell</li><li>0 = The output of gate 3 is not inverted</li></ul>      |

| bit 2   | LCxG3POL: Gate 2 Output Polarity Control bit                                                                                                |

|         | <ul><li>1 = The output of gate 2 is inverted when applied to the logic cell</li><li>0 = The output of gate 2 is not inverted</li></ul>      |

| bit 1   | LCxG2POL: Gate 1 Output Polarity Control bit                                                                                                |

|         | 1 = The output of gate 1 is inverted when applied to the logic cell 0 = The output of gate 1 is not inverted                                |

| bit 0   | LCxG1POL: Gate 0 Output Polarity Control bit                                                                                                |

|         | <ul><li>1 = The output of gate 0 is inverted when applied to the logic cell</li><li>0 = The output of gate 0 is not inverted</li></ul>      |

#### 32.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 32.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

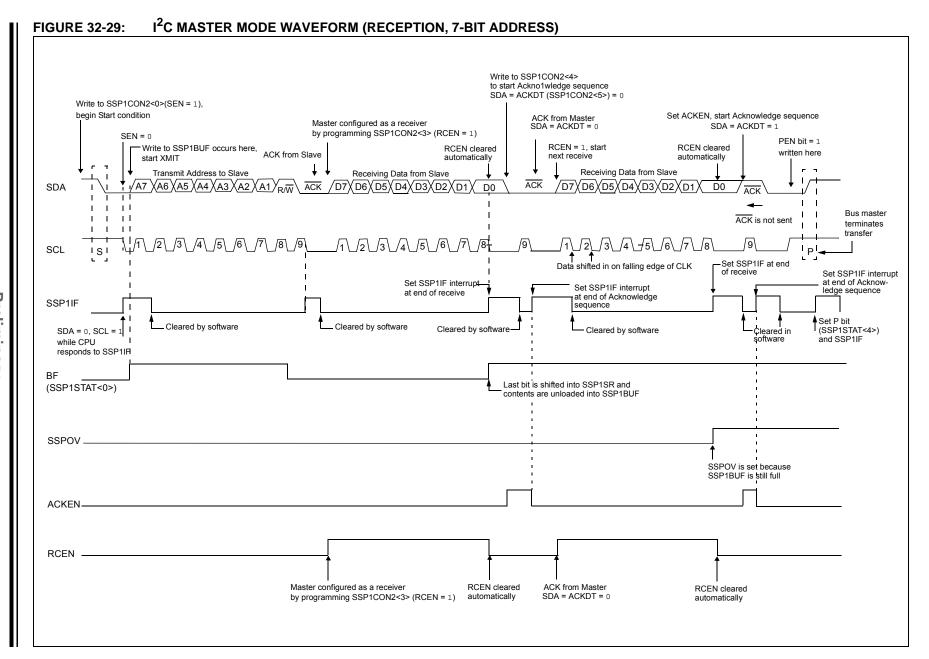

# 32.4 I<sup>2</sup>C MODE OPERATION

All MSSP  $I^2C$  communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the PIC<sup>®</sup> microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external  $I^2C$  devices.

#### 32.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

# 32.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

#### 32.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

Note 1: Any device pin can be selected for SDA and SCL functions with the PPS peripheral. These functions are bidirectional. The SDA input is selected with the SSPDATPPS registers. The SCL input is selected with the SSPCLKPPS registers. Outputs are selected with the RxyPPS registers. It is the user's responsibility to make the selections so that both the input and the output for each function is on the same pin.

PIC16(L)F15313/2

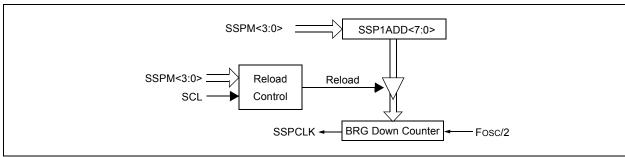

#### 32.7 BAUD RATE GENERATOR

The MSSP module has a Baud Rate Generator available for clock generation in both I<sup>2</sup>C and SPI Master modes. The Baud Rate Generator (BRG) reload value is placed in the SSP1ADD register (Register 32-6). When a write occurs to SSP1BUF, the Baud Rate Generator will automatically begin counting down.

Once the given operation is complete, the internal clock will automatically stop counting and the clock pin will remain in its last state.

An internal signal "Reload" in Figure 32-40 triggers the value from SSP1ADD to be loaded into the BRG counter. This occurs twice for each oscillation of the

module clock line. The logic dictating when the reload signal is asserted depends on the mode the MSSP is being operated in.

Table 32-4 demonstrates clock rates based on instruction cycles and the BRG value loaded into SSP1ADD.

#### **EQUATION 32-1:**

$$FCLOCK = \frac{FOSC}{(SSP1ADD + I)(4)}$$

FIGURE 32-40: BAUD RATE GENERATOR BLOCK DIAGRAM

Note: Values of 0x00, 0x01 and 0x02 are not valid for SSP1ADD when used as a Baud Rate Generator for I<sup>2</sup>C. This is an implementation limitation.

TABLE 32-2: MSSP CLOCK RATE W/BRG

| Fosc   | FcY   | BRG Value | FCLOCK<br>(2 Rollovers of BRG) |

|--------|-------|-----------|--------------------------------|

| 32 MHz | 8 MHz | 13h       | 400 kHz                        |

| 32 MHz | 8 MHz | 19h       | 308 kHz                        |

| 32 MHz | 8 MHz | 4Fh       | 100 kHz                        |

| 16 MHz | 4 MHz | 09h       | 400 kHz                        |

| 16 MHz | 4 MHz | 0Ch       | 308 kHz                        |

| 16 MHz | 4 MHz | 27h       | 100 kHz                        |

| 4 MHz  | 1 MHz | 09h       | 100 kHz                        |

**Note:** Refer to the I/O port electrical specifications in Table 37-4 to ensure the system is designed to support IoL requirements.

# 33.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See Section 9.2.2.2 "Internal Oscillator Frequency Adjustment" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see Section 33.3.1 "Auto-Baud Detect"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

TABLE 36-3: INSTRUCTION SET (CONTINUED)

| Mnemonic,<br>Operands |      | <b>Description</b> C                          |        |     | 14-Bit | Opcode | )    | Status   | Notes |

|-----------------------|------|-----------------------------------------------|--------|-----|--------|--------|------|----------|-------|

|                       |      |                                               |        | MSb |        |        | LSb  | Affected | Notes |

|                       |      | CONTROL OPERA                                 | TIONS  |     |        |        |      |          |       |

| BRA                   | k    | Relative Branch                               | 2      | 11  | 001k   | kkkk   | kkkk |          |       |

| BRW                   | _    | Relative Branch with W                        | 2      | 00  | 0000   | 0000   | 1011 |          |       |

| CALL                  | k    | Call Subroutine                               | 2      | 10  | 0kkk   | kkkk   | kkkk |          |       |

| CALLW                 | _    | Call Subroutine with W                        | 2      | 00  | 0000   | 0000   | 1010 |          |       |

| GOTO                  | k    | Go to address                                 | 2      | 10  | 1kkk   | kkkk   | kkkk |          |       |

| RETFIE                | k    | Return from interrupt                         | 2      | 00  | 0000   | 0000   | 1001 |          |       |

| RETLW                 | k    | Return with literal in W                      | 2      | 11  | 0100   | kkkk   | kkkk |          |       |

| RETURN                | _    | Return from Subroutine                        | 2      | 00  | 0000   | 0000   | 1000 |          |       |

|                       |      | INHERENT OPERA                                | TIONS  |     |        |        |      |          |       |

| CLRWDT                | _    | Clear Watchdog Timer                          | 1      | 00  | 0000   | 0110   | 0100 | TO, PD   |       |

| NOP                   | _    | No Operation                                  | 1      | 00  | 0000   | 0000   | 0000 |          |       |

| RESET                 | _    | Software device Reset                         | 1      | 00  | 0000   | 0000   | 0001 |          |       |

| SLEEP                 | _    | Go into Standby or IDLE mode                  | 1      | 00  | 0000   | 0110   | 0011 | TO, PD   |       |

| TRIS                  | f    | Load TRIS register with W                     | 1      | 00  | 0000   | 0110   | Offf |          |       |

|                       |      | C-COMPILER OPT                                | IMIZED |     |        |        |      |          | li li |

| ADDFSR                | n, k | Add Literal k to FSRn                         | 1      | 11  | 0001   | 0nkk   | kkkk |          |       |

| MOVIW                 | n mm | Move Indirect FSRn to W with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 0nmm | Z        | 2, 3  |

|                       |      | modifier, mm                                  |        |     |        |        |      |          |       |

|                       | k[n] | Move INDFn to W, Indexed Indirect.            | 1      | 11  | 1111   | 0nkk   | kkkk | Z        | 2     |

| MOVWI                 | n mm | Move W to Indirect FSRn with pre/post inc/dec | 1      | 00  | 0000   | 0001   | 1nmm |          | 2, 3  |

|                       |      | modifier, mm                                  |        |     |        |        |      |          |       |

|                       | k[n] | Move W to INDFn, Indexed Indirect.            | 1      | 11  | 1111   | 1nkk   | kkkk |          | 2     |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

<sup>3:</sup> See Table in the MOVIW and MOVWI instruction descriptions.

| CALL             | Call Subroutine                                                                                                                                                                                                       |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] CALL k                                                                                                                                                                                                        |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                                                  |

| Operation:       | (PC)+ 1 $\rightarrow$ TOS,<br>k $\rightarrow$ PC<10:0>,<br>(PCLATH<6:3>) $\rightarrow$ PC<14:11>                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Call Subroutine. First, return address (PC + 1) is pushed onto the stack. The 11-bit immediate address is loaded into PC bits <10:0>. The upper bits of the PC are loaded from PCLATH. CALL is a 2-cycle instruction. |

| CLRWDT                      | Clear Watchdog Timer                                                                                                                                                                                        |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:                     | [ label ] CLRWDT                                                                                                                                                                                            |

| Operands:                   | None                                                                                                                                                                                                        |

| Operation: Status Affected: | $\begin{array}{l} 00h \rightarrow WDT \\ 0 \rightarrow \underline{WDT} \text{ prescaler,} \\ 1 \rightarrow \overline{TO} \\ 1 \rightarrow \overline{PD} \\ \hline \overline{TO}, \overline{PD} \end{array}$ |

| Description:                | CLRWDT instruction resets the Watchdog Timer. It also resets the prescaler of the WDT. Status bits $\overline{\text{TO}}$ and $\overline{\text{PD}}$ are set.                                               |

| CALLW            | Subroutine Call With W                                                                                                                                                                                                |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] CALLW                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                  |

| Operation:       | $(PC) +1 \rightarrow TOS,$<br>$(W) \rightarrow PC<7:0>,$<br>$(PCLATH<6:0>) \rightarrow PC<14:8>$                                                                                                                      |

| Status Affected: | None                                                                                                                                                                                                                  |

| Description:     | Subroutine call with W. First, the return address (PC + 1) is pushed onto the return stack. Then, the contents of W is loaded into PC<7:0>, and the contents of PCLATH into PC<14:8>. CALLW is a 2-cycle instruction. |

| COMF             | Complement f                                                                                                                                       |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] COMF f,d                                                                                                                                 |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                 |

| Operation:       | $(\bar{f}) \rightarrow (destination)$                                                                                                              |

| Status Affected: | Z                                                                                                                                                  |

| Description:     | The contents of register 'f' are complemented. If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'. |

| CLRF             | Clear f                                                        |

|------------------|----------------------------------------------------------------|

| Syntax:          | [label] CLRF f                                                 |

| Operands:        | $0 \leq f \leq 127$                                            |

| Operation:       | $00h \to (f)$ $1 \to Z$                                        |

| Status Affected: | Z                                                              |

| Description:     | The contents of register 'f' are cleared and the Z bit is set. |

| DECF             | Decrement f                                                                                                                              |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] DECF f,d                                                                                                                       |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                       |  |  |  |  |

| Operation:       | (f) - 1 $\rightarrow$ (destination)                                                                                                      |  |  |  |  |

| Status Affected: | Z                                                                                                                                        |  |  |  |  |

| Description:     | Decrement register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |

| CLRW             | Clear W                                     |  |  |  |  |

|------------------|---------------------------------------------|--|--|--|--|

| Syntax:          | [label] CLRW                                |  |  |  |  |

| Operands:        | None                                        |  |  |  |  |

| Operation:       | $00h \to (W)$ $1 \to Z$                     |  |  |  |  |

| Status Affected: | Z                                           |  |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set. |  |  |  |  |

| MOVWI            | Move W to INDFn                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] MOVWI ++FSRn<br>[ label ] MOVWIFSRn<br>[ label ] MOVWI FSRn++<br>[ label ] MOVWI FSRn<br>[ label ] MOVWI k[FSRn]                                                                                                                                                                                                 |  |  |  |  |

| Operands:        | $\begin{split} n &\in [0,1] \\ mm &\in [00,01,10,11] \\ -32 &\leq k \leq 31 \end{split}$                                                                                                                                                                                                                                   |  |  |  |  |

| Operation:       | <ul> <li>W → INDFn</li> <li>Effective address is determined by</li> <li>FSR + 1 (preincrement)</li> <li>FSR - 1 (predecrement)</li> <li>FSR + k (relative offset)</li> <li>After the Move, the FSR value will be either:</li> <li>FSR + 1 (all increments)</li> <li>FSR - 1 (all decrements)</li> <li>Unchanged</li> </ul> |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Mode          | Syntax | mm |

|---------------|--------|----|

| Preincrement  | ++FSRn | 00 |

| Predecrement  | FSRn   | 01 |

| Postincrement | FSRn++ | 10 |

| Postdecrement | FSRn   | 11 |

Description:

This instruction is used to move data between W and one of the indirect registers (INDFn). Before/after this move, the pointer (FSRn) is updated by pre/post incrementing/decrementing it.

**Note:** The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the FSRn.

FSRn is limited to the range 0000h-FFFFh.

Incrementing/decrementing it beyond these bounds will cause it to

wrap-around.

The increment/decrement operation on FSRn WILL NOT affect any Status bits.

| NOP              | No Operation                                                             |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] NOP                                                            |  |  |  |  |  |

| Operands:        | None                                                                     |  |  |  |  |  |

| Operation:       | No operation                                                             |  |  |  |  |  |

| Status Affected: | None                                                                     |  |  |  |  |  |

| Description:     | No operation.                                                            |  |  |  |  |  |

| Words:           | 1                                                                        |  |  |  |  |  |

| Cycles:          | 1                                                                        |  |  |  |  |  |

| Example:         | NOP                                                                      |  |  |  |  |  |

| RESET            | Software Reset                                                           |  |  |  |  |  |

| Syntax:          | [label] RESET                                                            |  |  |  |  |  |

| Operands:        | None                                                                     |  |  |  |  |  |

| Operation:       | Execute a device Reset. Resets the RI flag of the PCON register.         |  |  |  |  |  |

| Status Affected: | None                                                                     |  |  |  |  |  |

| Description:     | This instruction provides a way to execute a hardware Reset by software. |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                                    |  |  |  |  |  |

| Syntax:          | [ label ] RETFIE k                                                       |  |  |  |  |  |

| Operands:        | None                                                                     |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC,$ $1 \rightarrow GIE$                                |  |  |  |  |  |

| RETFIE           | Return from Interrupt                                                                                                                                                                            |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] RETFIE k                                                                                                                                                                               |  |  |  |  |  |

| Operands:        | None                                                                                                                                                                                             |  |  |  |  |  |

| Operation:       | $TOS \rightarrow PC,$ $1 \rightarrow GIE$                                                                                                                                                        |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |  |  |

| Description:     | Return from Interrupt. Stack is POPed and Top-of-Stack (TOS) is loaded in the PC. Interrupts are enabled by setting Global Interrupt Enable bit, GIE (INTCON<7>). This is a 2-cycle instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                                                |  |  |  |  |  |

| Example:         | RETFIE                                                                                                                                                                                           |  |  |  |  |  |

|                  | After Interrupt PC = TOS GIE = 1                                                                                                                                                                 |  |  |  |  |  |

TABLE 37-18: TIMERO AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

|               | r <b>d Operating (</b><br>ng Temperatur |                                                                      | nless otherwis<br>≤ +125°C   | e stated)      |                                    |          |               |       |                    |

|---------------|-----------------------------------------|----------------------------------------------------------------------|------------------------------|----------------|------------------------------------|----------|---------------|-------|--------------------|

| Param.<br>No. | Sym.                                    | Characteristic                                                       |                              |                | Min.                               | Тур†     | Max.          | Units | Conditions         |

| 40*           | Тт0Н                                    | T0CKI High Pulse Width                                               |                              | No Prescaler   | 0.5 Tcy + 20                       | _        | _             | ns_   |                    |

|               |                                         |                                                                      | With Prescaler               |                | 10                                 | _        |               | ns-   |                    |

| 41*           | TT0L                                    | T0CKI Low F                                                          | ulse Width                   | No Prescaler   | 0.5 Tcy + 20                       | _        | -/            | /ns / |                    |

|               |                                         | With Prescaler                                                       |                              | 10             | _                                  | _\       | N.S           |       |                    |

| 42*           | Тт0Р                                    | T0CKI Period                                                         | i                            |                | Greater of:<br>20 or TCY + 40<br>N |          |               | ns    | N = prescale value |

| 45*           | T⊤1H                                    | T1CKI High                                                           | gh Synchronous, No Prescaler |                | 0.5 Tcy + 20                       | _\       | T-            | ns    |                    |

|               |                                         | Time                                                                 | Synchronous, v               | vith Prescaler | 15                                 | _ \      | 7/            | ns    |                    |

|               |                                         |                                                                      | Asynchronous                 |                | 30 ^                               | _        | $\backslash$  | ns    |                    |

| 46*           | TT1L                                    | T1CKI Low<br>Time                                                    | Synchronous, N               | lo Prescaler   | 0.5 Tcy + 20                       | \_       | /-/           | ns    |                    |

|               |                                         |                                                                      | Synchronous, v               | vith Prescaler | 15                                 | /-/      | $\rightarrow$ | ns    |                    |

|               |                                         |                                                                      | Asynchronous                 |                | 30                                 | 7        | >-            | ns    |                    |

| 47*           | Тт1Р                                    | T1CKI Input<br>Period                                                | Synchronous                  | ,              | Greater of:<br>30 or TCY + 40<br>N |          | / _           | ns    | N = prescale value |

|               |                                         |                                                                      | Asynchronous                 |                | 60                                 | <u> </u> | _             | ns    |                    |

| 49*           | TCKEZTMR1                               | Delay from External Clock Edge to Timer 2 Tosc — Timers in Sync mode |                              |                |                                    |          | ,             |       |                    |

These parameters are characterized but not tested.

Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Preliminary** © 2017 Microchip Technology Inc. DS40001897A-page 478

#### 40.0 PACKAGING INFORMATION

#### 40.1 **Package Marking Information**

# 8-Lead PDIP (300 mil)

8-Lead SOIC (3.90 mm)

8-Lead UDFN (3x3x0.9 mm)

**Example**

Example

Example

Customer-specific information Legend: XX...X

> Year code (last digit of calendar year) Υ ΥY Year code (last 2 digits of calendar year) WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC® designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3) can be found on the outer packaging for this package.

In the event the full Microchip part number cannot be marked on one line, it will Note: be carried over to the next line, thus limiting the number of available characters for customer-specific information.

**Preliminary** © 2017 Microchip Technology Inc. DS40001897A-page 492

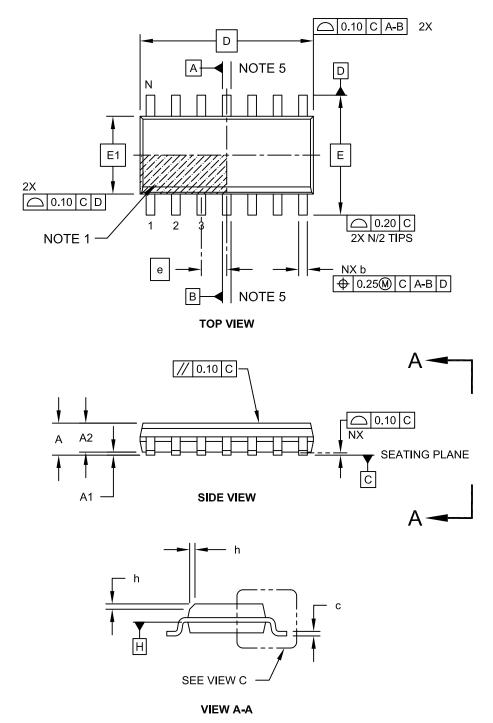

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing No. C04-065C Sheet 1 of 2