Welcome to **E-XFL.COM**

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Details                    |                                                                            |

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 12                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                       |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 14-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15323-i-sl |

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address           | Name                                                                                   | Bit 7                   | Bit 6              | Bit 5              | Bit 4         | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------|----------------------------------------------------------------------------------------|-------------------------|--------------------|--------------------|---------------|----------|-------|-------|-------|-----------------------|----------------------------|

| Bank 4            |                                                                                        |                         |                    |                    |               |          |       |       |       |                       |                            |

|                   | CPU CORE REGISTERS; see Table 4-3 for specifics                                        |                         |                    |                    |               |          |       |       |       |                       |                            |

| 20Ch              | 20Ch TMR1L Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                         |                    |                    |               |          |       |       |       | 0000 0000             | uuuu uuuu                  |

| 20Dh              | TMR1H                                                                                  | Holding Register for th | e Most Significant | Byte of the 16-bit | TMR1 Register |          |       |       |       | 0000 0000             | uuuu uuuu                  |

| 20Eh              | T1CON                                                                                  | _                       | ı                  | CKPS               | <1:0>         | _        | SYNC  | RD16  | ON    | 00 -000               | uu -u0u                    |

| 20Fh              | T1GCON                                                                                 | GE                      | GPOL               | GTM                | GSPM          | GGO/DONE | GVAL  | _     | _     | 0000 0x               | uuuu ux                    |

| 210h              | T1GATE                                                                                 | GSS<4:0>                |                    |                    |               |          |       |       |       | 0 0000                | u uuuu                     |

| 211h              | T1CLK                                                                                  | _                       | CS<3:0>            |                    |               |          |       |       | 0000  | uuuu                  |                            |

| 212h<br>—<br>21Fh | — Unimplemented                                                                        |                         |                    |                    |               |          |       |       | _     | _                     |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address            | Name                                            | Bit 7  | Bit 6  | Bit 5        | Bit 4    | Bit 3          | Bit 2   | Bit 1   | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|--------------------|-------------------------------------------------|--------|--------|--------------|----------|----------------|---------|---------|----------|-----------------------|----------------------------|

| Bank 18            |                                                 |        |        |              |          |                |         |         |          |                       |                            |

|                    | CPU CORE REGISTERS; see Table 4-3 for specifics |        |        |              |          |                |         |         |          |                       |                            |

| 90Ch               | FVRCON                                          | FVREN  | FVRRDY | TSEN         | TSRNG    | CDAFV          | 'R<1:0> | ADF     | FVR<1:0> | 0x00 xxxx             | 0q00 uuuu                  |

| 90Dh               | _                                               |        |        |              | Unimpler | mented         |         |         |          | _                     | _                          |

| 90Eh               | DAC1CON0                                        | EN     | _      | OE1          | OE2      | PSS<1:0> — NSS |         |         | NSS      | 0-00 00-0             | 0-00 00-0                  |

| 90Fh               | DAC1CON1                                        | _      | _      | — DAC1R<4:0> |          |                |         |         |          | 0 0000                | 0 0000                     |

| 910h Unimplemented |                                                 |        |        |              |          | _              | _       |         |          |                       |                            |

| 91Fh               | ZCDCON                                          | ZCDSEN | _      | ZCDOUT       | ZCDPOL   | _              | _       | ZCDINTP | ZCDINTN  | 0-x000                | 0-x000                     |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

TABLE 9-1: NOSC/COSC BIT SETTINGS

| NOSC<2:0>/<br>COSC<2:0> | Clock Source                              |

|-------------------------|-------------------------------------------|

| 111                     | EXTOSC <sup>(1)</sup>                     |

| 110                     | HFINTOSC <sup>(2)</sup>                   |

| 101                     | LFINTOSC                                  |

| 100                     | Reserved                                  |

| 011                     | Reserved (operates like<br>NOSC = 110)    |

| 010                     | EXTOSC with 4x PLL <sup>(1)</sup>         |

| 001                     | HFINTOSC with 2x PLL <sup>(1)</sup>       |

| 000                     | Reserved (it operates like<br>NOSC = 110) |

Note 1: EXTOSC configured by the FEXTOSC bits of Configuration Word 1 (Register 5-1).

2: HFINTOSC settings are configured with the HFFRQ bits of the OSCFRQ register (Register 9-6).

### TABLE 9-2: NDIV/CDIV BIT SETTINGS

| NDIV<3:0>/<br>CDIV<3:0> | Clock divider |

|-------------------------|---------------|

| 1111-1010               | Reserved      |

| 1001                    | 512           |

| 1000                    | 256           |

| 0111                    | 128           |

| 0110                    | 64            |

| 0101                    | 32            |

| 0100                    | 16            |

| 0011                    | 8             |

| 0010                    | 4             |

| 0001                    | 2             |

| 0000                    | 1             |

### REGISTER 9-3: OSCCON3: OSCILLATOR CONTROL REGISTER 3

| R/W/HC-0/0 | U-0 | U-0 | R-0/0 | R-0/0 | U-0 | U-0 | U-0   |

|------------|-----|-----|-------|-------|-----|-----|-------|

| CSWHOLD    | _   | _   | ORDY  | NOSCR | _   | _   | _     |

| bit 7      |     |     |       |       |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7 CSWHOLD: Clock Switch Hold bit

1 = Clock switch will hold (with interrupt) when the oscillator selected by NOSC is ready

0 = Clock switch may proceed when the oscillator selected by NOSC is ready; if this bit

is clear at the time that NOSCR becomes '1', the switch will occur

bit 6-5 **Unimplemented:** Read as '0'.

bit 4 **ORDY:** Oscillator Ready bit (read-only)

1 = OSCCON1 = OSCCON2; the current system clock is the clock specified by NOSC

0 = A clock switch is in progress

bit 3 **NOSCR:** New Oscillator is Ready bit (read-only)

1 = A clock switch is in progress and the oscillator selected by NOSC indicates a "ready" condition

0 = A clock switch is not in progress, or the NOSC-selected oscillator is not yet ready

bit 2-0 Unimplemented: Read as '0'

# 10.6 Register Definitions: Interrupt Control

# REGISTER 10-1: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-1/1 |

|---------|---------|-----|-----|-----|-----|-----|---------|

| GIE     | PEIE    | _   | _   | _   | _   | _   | INTEDG  |

| bit 7   |         |     |     |     |     |     | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7   | <b>GIE:</b> Global Interrupt Enable bit 1 = Enables all active interrupts 0 = Disables all interrupts                                  |

|---------|----------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all active peripheral interrupts<br>0 = Disables all peripheral interrupts |

| bit 5-1 | Unimplemented: Read as '0'                                                                                                             |

| bit 0   | INTEDG: Interrupt Edge Select bit  1 = Interrupt on rising edge of INT pin  0 = Interrupt on falling edge of INT pin                   |

Note:

| Interrupt flag bits are set when an in | terrupt  |

|----------------------------------------|----------|

| condition occurs, regardless of the s  | state of |

| its corresponding enable bit or the    | Global   |

| Enable bit, GIE, of the INTCON re      | egister. |

| User software should ensure            | the      |

| appropriate interrupt flag bits are    | clear    |

| prior to enabling an interrupt.        |          |

### REGISTER 10-4: PIE2: PERIPHERAL INTERRUPT ENABLE REGISTER 2

| U-0   | R/W-0/0 | U-0 | U-0 | U-0 | U-0 | R/W-0/0             | R/W-0/0 |

|-------|---------|-----|-----|-----|-----|---------------------|---------|

| _     | ZCDIE   | _   | _   | _   | _   | C2IE <sup>(1)</sup> | C1IE    |

| bit 7 |         |     |     |     |     |                     | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7 Unimplemented: Read as '0' bit 6 **ZCDIE:** Zero-Cross Detection (ZCD) Interrupt Enable bit 1 = Enables the ZCD interrupt 0 = Disables the ZCD interrupt bit 5-2 Unimplemented: Read as '0' bit 1 C2IE: Comparator C2 Interrupt Enable bit 1 = Enables the Comparator C2 interrupt 0 = Disables the Comparator C2 interrupt bit 0 C1IE: Comparator C1 Interrupt Enable bit 1 = Enables the Comparator C1 interrupt 0 = Disables the Comparator C1 interrupt

Note 1: Present only on PIC16(L)F15323.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt controlled by registers PIE1-PIE7.

# 14.3 Register Definitions: PORTA

#### REGISTER 14-1: PORTA: PORTA REGISTER

| U-0   | U-0 | R/W-x/u | R/W-x/u | R-x/u | R/W-x/u | R/W-x/u | R/W-x/u |

|-------|-----|---------|---------|-------|---------|---------|---------|

| _     | _   | RA5     | RA4     | RA3   | RA2     | RA1     | RA0     |

| bit 7 |     |         |         |       |         |         | bit 0   |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is cleared

bit 7-6 Unimplemented: Read as '0'

bit 5-0 RA<5:0>: PORTA I/O Value bits<sup>(1)</sup>

1 = Port pin is  $\geq$  VIH 0 = Port pin is  $\leq$  VIL

**Note 1:** Writes to PORTA are actually written to corresponding LATA register. Reads from PORTA register returns of actual I/O pin values.

### REGISTER 14-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|-----|---------|---------|---------|

| _     | _   | TRISA5  | TRISA4  | _   | TRISA2  | TRISA1  | TRISA0  |

| bit 7 |     |         |         |     |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-4 TRISA<5:4>: PORTA Tri-State Control bits

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

bit 3 **Unimplemented**: Read as '0'

bit 2-0 TRISA<2:0>: PORTA Tri-State Control bits

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

TABLE 15-2: PPS INPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15323)

| INDUT CLONAL         | L. A.B. Market         | Default     |                           | Remappable to Pins of PORTx |       |  |

|----------------------|------------------------|-------------|---------------------------|-----------------------------|-------|--|

| INPUT SIGNAL<br>NAME | Input Register<br>Name | Location at | Reset Value (xxxPPS<4:0>) | PIC16(L)F15323              |       |  |

|                      | 1100                   | POR         | (mail 1 0 1 mor )         | PORTA                       | PORTC |  |

| INT                  | INTPPS                 | RA2         | 00010                     | •                           | •     |  |

| T0CKI                | T0CKIPPS               | RA2         | 00010                     | •                           | •     |  |

| T1CKI                | T1CKIPSS               | RA5         | 00101                     | •                           | •     |  |

| T1G                  | T1GPPS                 | RA4         | 00100                     | •                           | •     |  |

| T2IN                 | T2INPPS                | RA5         | 00101                     | •                           | •     |  |

| CCP1                 | CCP1PPS                | RC5         | 10101                     | •                           | •     |  |

| CCP2                 | CCP2PPS                | RC3         | 10011                     | •                           | •     |  |

| CWG1IN               | CWG1INPPS              | RA2         | 00010                     | •                           | •     |  |

| CLCIN0               | CLCIN0PPS              | RC3         | 10011                     | •                           | •     |  |

| CLCIN1               | CLCIN1PPS              | RC4         | 10100                     | •                           | •     |  |

| CLCIN2               | CLCIN2PPS              | RC1         | 10001                     | •                           | •     |  |

| CLCIN3               | CLCIN3PPS              | RA5         | 00101                     | •                           | •     |  |

| ADACT                | ADACTPPS               | RC2         | 10010                     | •                           | •     |  |

| SCK1/SCL1            | SSP1CLKPPS             | RC0         | 10000                     | •                           | •     |  |

| SDI1/SDA1            | SSP1DATPPS             | RC1         | 10001                     | •                           | •     |  |

| SS1                  | SSP1SS1PPS             | RC3         | 10011                     | •                           | •     |  |

| RX1/DT1              | RX1DTPPS               | RC5         | 10101                     | •                           | •     |  |

| CK1                  | TX1CKPPS               | RC4         | 10100                     | •                           | •     |  |

TABLE 15-3: PPS INPUT REGISTER VALUES

| Desired Input Pin  | Value to Write to Register |

|--------------------|----------------------------|

| RA0                | 0x00                       |

| RA1                | 0x01                       |

| RA2                | 0x02                       |

| RA3                | 0x03                       |

| RA4                | 0x04                       |

| RA5                | 0x05                       |

| RC0 <sup>(1)</sup> | 0x10                       |

| RC1 <sup>(1)</sup> | 0x11                       |

| RC2 <sup>(1)</sup> | 0x12                       |

| RC3 <sup>(1)</sup> | 0x13                       |

| RC4 <sup>(1)</sup> | 0x14                       |

| RC5 <sup>(1)</sup> | 0x15                       |

Note 1: Present on PIC16(L)F15323 only.

# 15.8 Register Definitions: PPS Input Selection

## REGISTER 15-1: xxxPPS: PERIPHERAL xxx INPUT SELECTION(1)

| U-0   | U-0 | R/W-q/u | R/W-q/u | R/W/q/u | R/W-q/u | R/W-q/u | R/W-q/u |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   |         |         | xxxPF   | PS<5:0> |         |         |

| bit 7 |     |         |         |         |         |         | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared | q = value depends on peripheral                       |

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **xxxPPS<5:0>:** Peripheral xxx Input Selection bits

See Table 15-1 and Table 15-2.

**Note 1:** The "xxx" in the register name "xxxPPS" represents the input signal function name, such as "INT", "T0CKI", "RX", etc. This register summary shown here is only a prototype of the array of actual registers, as each input function has its own dedicated SFR (ex: INTPPS, T0CKIPPS, RXPPS, etc.).

2: Each specific input signal may only be mapped to a subset of these I/O pins, as shown in Table 15-1 and Table 15-2. Attempting to map an input signal to a non-supported I/O pin will result in undefined behavior. For example, the "INT" signal map be mapped to any PORTA or PORTB pin. Therefore, the INTPPS register may be written with values from 0x00-0x0F (corresponding to RA0-RB7). Attempting to write 0x10 or higher to the INTPPS register is not supported and will result in undefined behavior.

TABLE 15-6: SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

| Name                  | Bit 7 | Bit 6 | Bit 5         | Bit 4          | Bit 3 | Bit 2      | Bit 1 | Bit 0     | Register on page |

|-----------------------|-------|-------|---------------|----------------|-------|------------|-------|-----------|------------------|

| PPSLOCK               | _     | _     | _             | _              | _     | _          | _     | PPSLOCKED | 192              |

| INTPPS                | _     | _     |               |                | INT   | PPS<5:0>   |       |           | 191              |

| T0CKIPPS              | _     | _     |               |                | T0Ck  | (IPPS<5:0> |       |           | 191              |

| T1CKIPPS              | _     | _     |               |                | T1Ck  | (IPPS<5:0> |       |           | 191              |

| T1GPPS                | _     | _     |               |                | T1G   | PPS<5:0>   |       |           | 191              |

| T2INPPS               |       |       |               |                | T2IN  | IPPS<5:0>  |       |           | 191              |

| CCP1PPS               | _     | _     |               |                | CCP   | 1PPS<5:0>  |       |           | 191              |

| CCP2PPS               | _     | _     |               |                | CCP   | 2PPS<5:0>  |       |           | 191              |

| CWG1PPS               | _     | _     |               |                | CWG   | 1PPS<5:0>  |       |           | 191              |

| SSP1CLKPPS            | _     | _     |               |                | SSP1C | LKPPS<5:0  | >     |           | 191              |

| SSP1DATPPS            | _     | _     |               |                | SSP1D | ATPPS<5:0  | >     |           | 191              |

| SSP1SSPPS             | _     | _     |               |                | SSP18 | SSPPS<5:0> |       |           | 191              |

| RX1DTPPS              | _     | _     |               |                | RX1D  | TPPS<5:0>  |       |           | 191              |

| TX1CKPPS              | _     | _     |               |                | TX1C  | KPPS<5:0>  |       |           | 191              |

| CLCIN0PPS             | _     | _     |               |                | CLCIN | NOPPS<5:0> |       |           | 191              |

| CLCIN1PPS             | _     | _     |               | CLCIN1PPS<5:0> |       |            |       |           | 191              |

| CLCIN2PPS             | _     | _     |               |                | CLCIN | 12PPS<5:0> |       |           | 191              |

| CLCIN3PPS             | _     | _     |               |                | CLCIN | N3PPS<5:0> |       |           | 191              |

| ADACTPPS              | _     | _     |               |                | ADAC  | TPPS<5:0>  |       |           | 191              |

| RA0PPS                | _     | _     | _             |                |       | RA0PPS<    | 1:0>  |           | 192              |

| RA1PPS                | _     | _     | _             |                |       | RA1PPS<    | 1:0>  |           | 192              |

| RA2PPS                | _     | _     | _             |                |       | RA2PPS<    | 1:0>  |           | 192              |

| RA3PPS                | _     | _     | _             |                |       | RA3PPS<    | 1:0>  |           | 192              |

| RA4PPS                | _     | _     | _             |                |       | RA4PPS<    | 1:0>  |           | 192              |

| RA5PPS                | _     | _     | _             |                |       | RA5PPS<    | 1:0>  |           | 192              |

| RC0PPS <sup>(1)</sup> | _     | _     | _             |                |       | RC0PPS<    | 1:0>  |           | 192              |

| RC1PPS <sup>(1)</sup> | _     | _     | _             |                |       | RC1PPS<    | 1:0>  |           | 192              |

| RC2PPS <sup>(1)</sup> | _     | _     | _             | — RC2PPS<4:0>  |       |            |       | 192       |                  |

| RC3PPS <sup>(1)</sup> | _     | _     | _             |                |       | RC3PPS<    | 4:0>  |           | 192              |

| RC4PPS <sup>(1)</sup> | _     | _     | _             | — RC4PPS<4:0>  |       |            |       | 192       |                  |

| RC5PPS <sup>(1)</sup> | _     | _     | _             | — RC5PPS<4:0>  |       |            |       |           | 192              |

| RC6PPS <sup>(1)</sup> | _     | _     | — RC6PPS<4:0> |                |       |            |       | 192       |                  |

| RC7PPS <sup>(1)</sup> | _     | _     | _             |                |       | RC7PPS<    | 4:0>  |           | 192              |

**Legend:** — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

Note 1: Present on PIC16(L)F15323 only.

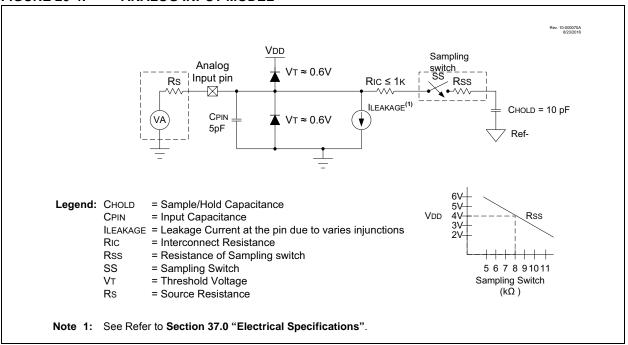

## 20.3 ADC Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (Chold) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 20-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor Chold. The sampling switch (Rss) impedance varies over the device voltage (VDD), refer to Figure 20-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the

source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an ADC acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 20-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### **EQUATION 20-1: ACQUISITION TIME EXAMPLE**

Assumptions: Temperature =  $50^{\circ}$ C and external impedance of  $10k\Omega 5.0V VDD$

$$TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient$$

=  $TAMP + TC + TCOFF$

=  $2\mu s + TC + [(Temperature - 25°C)(0.05\mu s/°C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{(2^{n+1})-1}\right) = V_{CHOLD}$$

;[1] VCHOLD charged to within 1/2 lsb

$$V_{APPLIED} \left( 1 - e^{\frac{-Tc}{RC}} \right) = V_{CHOLD}$$

;[2] VCHOLD charge response to VAPPLIED

$$V_{APPLIED}\left(1-e^{\frac{-Tc}{RC}}\right) = V_{APPLIED}\left(1-\frac{1}{(2^{n+1})-1}\right)$$

; combining [1] and [2]

*Note:* Where n = number of bits of the ADC.

Solving for TC:

$$TC = -C_{HOLD}(RIC + RSS + RS) \ln(1/2047)$$

$$= -10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$$

$$= 1.37\mu s$$

Therefore:

$$TACQ = 2\mu s + 1.37 + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 4.62\mu s

- Note 1: The VAPPLIED has no effect on the equation, since it cancels itself out.

- 2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

- **3:** The maximum recommended impedance for analog sources is 10 kΩ. This is required to meet the pin leakage specification.

FIGURE 20-4: ANALOG INPUT MODEL

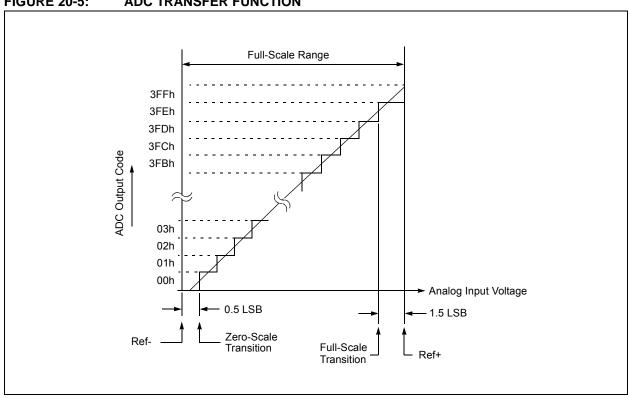

### FIGURE 20-5: ADC TRANSFER FUNCTION

**FIGURE 31-2: INPUT DATA SELECTION AND GATING Data Selection** LCx\_in-Data GATE 1 LCxD1G1T lcxd1T lcxd1N LCxD1G1N LCx\_in-LCxD2G1T LCxD1S<5:0> LCxD2G1N -lcxg1 LCx\_in-LCxD3G1T LCxG1POL lcxd2T LCxD3G1N lcxd2N LCxD4G1T LCx\_in-LCxD2S<5:0> LCxD4G1N LCx\_in-Data GATE 2 lcxg2 lcxd3T (Same as Data GATE 1) lcxd3N Data GATE 3 LCx\_in--lcxg3 LCxD3S<5:0> (Same as Data GATE 1) Data GATE 4 LCx\_in--lcxg4 (Same as Data GATE 1) lcxd4T lcxd4N LCx\_in-LCxD4S<5:0>

# REGISTER 31-8: CLCxGLS1: GATE 1 LOGIC SELECT REGISTER

| R/W-x/u  |

|----------|----------|----------|----------|----------|----------|----------|----------|

| LCxG2D4T | LCxG2D4N | LCxG2D3T | LCxG2D3N | LCxG2D2T | LCxG2D2N | LCxG2D1T | LCxG2D1N |

| bit 7    |          |          |          |          |          |          | bit 0    |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7 | LCxG2D4T: Gate 1 Data 4 True (non-inverted) bit                                                        |

|-------|--------------------------------------------------------------------------------------------------------|

|       | 1 = CLCIN3 (true) is gated into CLCx Gate 1                                                            |

|       | 0 = CLCIN3 (true) is not gated into CLCx Gate 1                                                        |

| bit 6 | LCxG2D4N: Gate 1 Data 4 Negated (inverted) bit                                                         |

|       | 1 = CLCIN3 (inverted) is gated into CLCx Gate 1<br>0 = CLCIN3 (inverted) is not gated into CLCx Gate 1 |

| bit 5 | LCxG2D3T: Gate 1 Data 3 True (non-inverted) bit                                                        |

|       | 1 = CLCIN2 (true) is gated into CLCx Gate 1                                                            |

|       | 0 = CLCIN2 (true) is not gated into CLCx Gate 1                                                        |

| bit 4 | LCxG2D3N: Gate 1 Data 3 Negated (inverted) bit                                                         |

|       | 1 = CLCIN2 (inverted) is gated into CLCx Gate 1                                                        |

|       | 0 = CLCIN2 (inverted) is not gated into CLCx Gate 1                                                    |

| bit 3 | LCxG2D2T: Gate 1 Data 2 True (non-inverted) bit                                                        |

|       | 1 = CLCIN1 (true) is gated into CLCx Gate 1                                                            |

|       | 0 = CLCIN1 (true) is not gated into CLCx Gate 1                                                        |

| bit 2 | LCxG2D2N: Gate 1 Data 2 Negated (inverted) bit                                                         |

|       | 1 = CLCIN1 (inverted) is gated into CLCx Gate 1                                                        |

|       | 0 = CLCIN1 (inverted) is not gated into CLCx Gate 1                                                    |

| bit 1 | LCxG2D1T: Gate 1 Data 1 True (non-inverted) bit                                                        |

|       | 1 = CLCIN0 (true) is gated into CLCx Gate 1                                                            |

|       | 0 = CLCIN0 (true) is not gated into CLCx Gate1                                                         |

| bit 0 | LCxG2D1N: Gate 1 Data 1 Negated (inverted) bit                                                         |

|       | 1 = CLCIN0 (inverted) is gated into CLCx Gate 1                                                        |

|       | 0 = CLCIN0 (inverted) is not gated into CLCx Gate 1                                                    |

|       |                                                                                                        |

PIC16(L)F15313/23

#### REGISTER 32-4: SSP1CON3: SSP1 CONTROL REGISTER 3

| R-0/0                 | R/W-0/0 |

|-----------------------|---------|---------|---------|---------|---------|---------|---------|

| ACKTIM <sup>(3)</sup> | PCIE    | SCIE    | BOEN    | SDAHT   | SBCDE   | AHEN    | DHEN    |

| bit 7                 |         | •       | •       |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

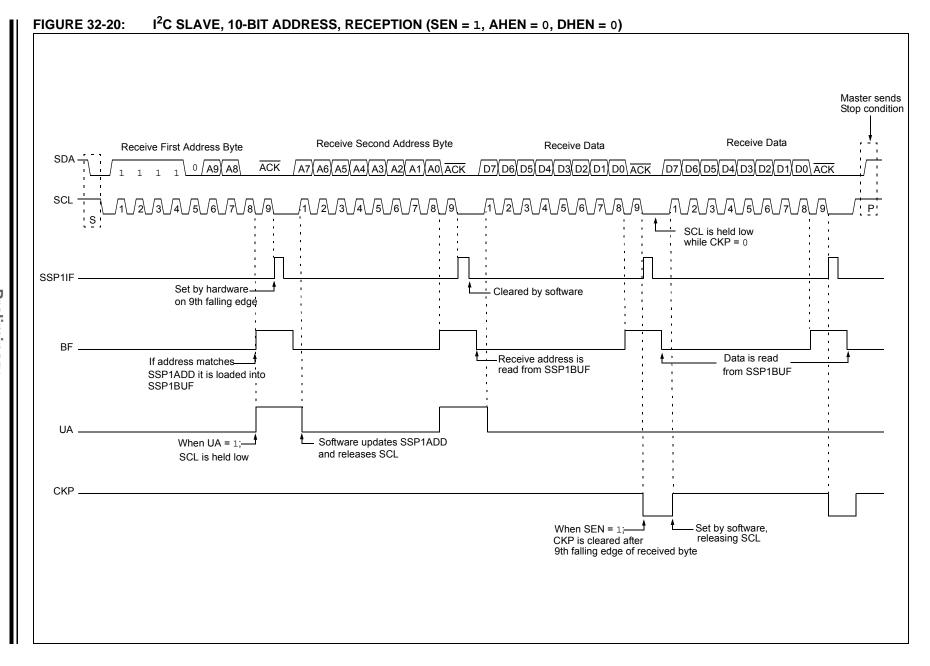

bit 7 ACKTIM: Acknowledge Time Status bit (I<sup>2</sup>C mode only)<sup>(3)</sup>

1 = Indicates the I<sup>2</sup>C bus is in an Acknowledge sequence, set on 8<sup>th</sup> falling edge of SCL clock

0 = Not an Acknowledge sequence, cleared on 9<sup>TH</sup> rising edge of SCL clock

bit 6 **PCIE**: Stop Condition Interrupt Enable bit (I<sup>2</sup>C mode only)

1 = Enable interrupt on detection of Stop condition

0 = Stop detection interrupts are disabled<sup>(2)</sup>

bit 5 SCIE: Start Condition Interrupt Enable bit (I<sup>2</sup>C mode only)

1 = Enable interrupt on detection of Start or Restart conditions

0 = Start detection interrupts are disabled<sup>(2)</sup>

bit 4 **BOEN:** Buffer Overwrite Enable bit

In SPI Slave mode:(1)

1 = SSPBUF updates every time that a new data byte is shifted in ignoring the BF bit

0 = If new byte is received with BF bit of the SSPSTAT register already set, SSPOV bit of the SSPCON1 register is set, and the buffer is not updated

In I<sup>2</sup>C Master mode and SPI Master mode:

This bit is ignored.

In I<sup>2</sup>C Slave mode:

1 = SSPBUF is updated and  $\overline{ACK}$  is generated for a received address/data byte, ignoring the state of the SSPOV bit only if the BF bit = 0.

0 = SSPBUF is only updated when SSPOV is clear

bit 3 SDAHT: SDA Hold Time Selection bit (I<sup>2</sup>C mode only)

1 = Minimum of 300 ns hold time on SDA after the falling edge of SCL

0 = Minimum of 100 ns hold time on SDA after the falling edge of SCL

bit 2 SBCDE: Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

If, on the rising edge of SCL, SDA is sampled low when the module is outputting a high state, the BCL1IF bit of the PIR3 register is set, and bus goes idle

1 = Enable slave bus collision interrupts

0 = Slave bus collision interrupts are disabled

bit 1 AHEN: Address Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the eighth falling edge of SCL for a matching received address byte; CKP bit of the SSPCON1 register will be cleared and the SCL will be held low.

0 = Address holding is disabled

bit 0 **DHEN:** Data Hold Enable bit (I<sup>2</sup>C Slave mode only)

1 = Following the eighth falling edge of SCL for a received data byte; slave hardware clears the CKP bit of the SSP-CON1 register and SCL is held low.

0 = Data holding is disabled

**Note** 1: For daisy-chained SPI operation; allows the user to ignore all but the last received byte. SSPOV is still set when a new byte is received and BF = 1, but hardware continues to write the most recent byte to SSPBUF.

2: This bit has no effect in Slave modes that Start and Stop condition detection is explicitly listed as enabled.

3: The ACKTIM Status bit is only active when the AHEN bit or DHEN bit is set.

| SLEEP            | Enter Sleep mode                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] SLEEP                                                                                                                                                                                              |

| Operands:        | None                                                                                                                                                                                                         |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow \underline{WDT} \text{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow \overline{PD} \end{array}$                                       |

| Status Affected: | TO, PD                                                                                                                                                                                                       |

| Description:     | The power-down Status bit, $\overline{PD}$ is cleared. Time-out Status bit, $\overline{TO}$ is set. Watchdog Timer and its prescaler are cleared. See <b>Section 11.2 "Sleep Mode"</b> for more information. |

| SUBWF            | Subtract W from f                                                                                                                                                              |                 |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|

| Syntax:          | [ label ] SL                                                                                                                                                                   | JBWF f,d        |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                             |                 |  |  |  |  |  |

| Operation:       | (f) - (W) $\rightarrow$ (destination)                                                                                                                                          |                 |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                       |                 |  |  |  |  |  |

| Description:     | Subtract (2's complement method) W register from register 'f'. If 'd' is '0', the result is stored in the W register. If 'd' is '1', the result is stored back in register 'f. |                 |  |  |  |  |  |

|                  | <b>C</b> = 0                                                                                                                                                                   | W > f           |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                          | $W \le f$       |  |  |  |  |  |

|                  | DC = 0                                                                                                                                                                         | W<3:0> > f<3:0> |  |  |  |  |  |

|                  | DC = 1                                                                                                                                                                         | W<3:0> ≤ f<3:0> |  |  |  |  |  |

Subtract W from f with Borrow

**SUBWFB**

Syntax:

| SUBLW            | Subtract W from literal                                                                                                  |                 |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|--|--|

| Syntax:          | [ label ] SU                                                                                                             | JBLW k          |  |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                      |                 |  |  |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                |                 |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                 |                 |  |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the 8-bit literal 'k'. The result is placed in the W register. |                 |  |  |  |  |  |  |

|                  | C = 0                                                                                                                    | W > k           |  |  |  |  |  |  |

|                  | C = 1                                                                                                                    | $W \le k$       |  |  |  |  |  |  |

|                  | DC = 0                                                                                                                   | W<3:0> > k<3:0> |  |  |  |  |  |  |

|                  | DC = 1                                                                                                                   | W<3:0> ≤ k<3:0> |  |  |  |  |  |  |

| Operands: Operation: Status Affected: Description: | $\begin{split} 0 &\leq f \leq 127 \\ d &\in [0,1] \\ (f) - (W) - (\overline{B}) \rightarrow dest \\ C, DC, Z \\ \text{Subtract W and the BORROW flag} \\ (CARRY) \text{ from register 'f' (2's complement method). If 'd' is '0', the result is stored in W. If 'd' is '1', the result is stored back in register 'f'.} \end{split}$ |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SWAPF                                              | Swap Nibbles in f                                                                                                                                                                                                                                                                                                                    |

| Cuptou                                             |                                                                                                                                                                                                                                                                                                                                      |

| Syntax:                                            | [ label ] SWAPF f,d                                                                                                                                                                                                                                                                                                                  |

| Operands:                                          | [ label ] SWAPF f,d<br>$0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                                                                            |

| •                                                  | $0 \le f \le 127$                                                                                                                                                                                                                                                                                                                    |

| Operands:                                          | $0 \le f \le 127$<br>$d \in [0,1]$<br>$(f < 3:0 >) \rightarrow (destination < 7:4 >),$                                                                                                                                                                                                                                               |

SUBWFB f {,d}

TABLE 37-8: INTERNAL OSCILLATOR PARAMETERS(1)

| Standard Operating Conditions (unless otherwise stated) |          |                                                 |              |                          |               |            |                          |  |  |

|---------------------------------------------------------|----------|-------------------------------------------------|--------------|--------------------------|---------------|------------|--------------------------|--|--|

| Param.<br>No.                                           | Sym.     | Characteristic                                  | Min.         | Тур†                     | Max.          | Units      | Conditions               |  |  |

| OS50                                                    | FHFOSC   | Precision Calibrated HFINTOSC Frequency         | _            | 4<br>8<br>12<br>16<br>32 | _             | MHz        | (Note 2)                 |  |  |

| OS51                                                    | FHFOSCLP | Low-Power Optimized HFINTOSC Frequency          | _            | 1<br>2                   | _             | MHz<br>MHz |                          |  |  |

| OS52                                                    | FMFOSC   | Internal Calibrated MFINTOSC Frequency          | _            | 500                      | _             | kHz        | 7/~                      |  |  |

| OS53                                                    | FLFOSC   | Internal LFINTOSC Frequency                     | _            | 31 ,                     | $\overline{}$ | kHz        |                          |  |  |

| OS54                                                    | THFOSCST | HFINTOSC<br>Wake-up from Sleep Start-up<br>Time | _            | 11<br>50                 | 20            | μs         | VREGPM = 0<br>VREGPM = 1 |  |  |

| OS56                                                    | TLFOSCST | LFINTOSC<br>Wake-up from Sleep Start-up Time    | $ \uparrow $ | 0.2                      |               | ms         |                          |  |  |

- † Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

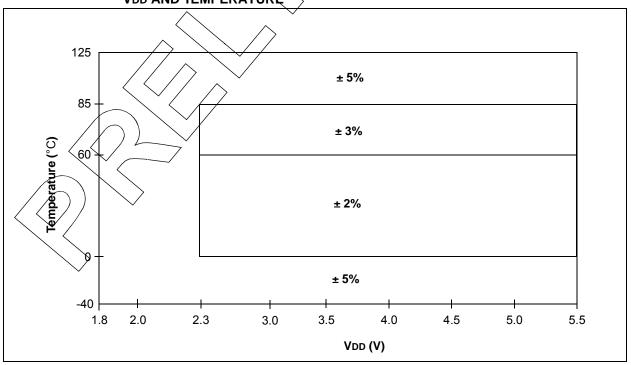

- 2: See Figure 37-6: Precision Calibrated HFINTOSC Frequency Accuracy Over Device VDD and Temperature.

FIGURE 37-6: PRECISION CALIBRATED HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

**TABLE 37-23: SPI MODE REQUIREMENTS**

| Standard Operating Conditions (unless otherwise stated) |                       |                                          |                |      |      |       |                              |

|---------------------------------------------------------|-----------------------|------------------------------------------|----------------|------|------|-------|------------------------------|

| Param.<br>No.                                           | Symbol                | Characteristic                           | Min.           | Typ† | Max. | Units | Conditions                   |

| SP70*                                                   | TssL2scH,<br>TssL2scL | SS↓ to SCK↓ or SCK↑ input                | 2.25*TcY       | _    | _    | ns    |                              |

| SP71*                                                   | TscH                  | SCK input high time (Slave mode)         | Tcy + 20       | _    |      | nø    |                              |

| SP72*                                                   | TscL                  | SCK input low time (Slave mode)          | Tcy + 20       | _    | _ `  | ns    |                              |

| SP73*                                                   | TDIV2SCH,<br>TDIV2SCL | Setup time of SDI data input to SCK edge | 100            |      | 1 /  | ns    |                              |

| SP74*                                                   | TSCH2DIL,<br>TSCL2DIL | Hold time of SDI data input to SCK edge  | 100            | _    |      | AS.   | 7                            |

| SP75*                                                   | TDOR                  | SDO data output rise time                | _              | 10   | 25   | ns    | $3.0V \le VDD \le 5.5V$      |

|                                                         |                       |                                          |                | 25   | ₹0 ⟨ | ns    | $1.8V \leq V_{DD} \leq 5.5V$ |

| SP76*                                                   | TDOF                  | SDO data output fall time                | _              | 10   | 25   | ns    |                              |

| SP77*                                                   | TssH2DoZ              | SS↑ to SDO output high-impedance         | 10             | 7    | 50 ° | ns    |                              |

| SP78*                                                   | TscR                  | SCK output rise time                     | \ \ \ \ \ \ \  | 10   | _/25 | ns    | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                                         |                       | (Master mode)                            | < \- \         | 25   | 50   | ns    | $1.8V \leq V_{DD} \leq 5.5V$ |

| SP79*                                                   | TscF                  | SCK output fall time (Master mode)       | \_\ `          | 10   | 25   | ns    |                              |

| SP80*                                                   | TscH2DoV,             | SDO data output valid after SCK edge     | / //           | _    | 50   | ns    | $3.0V \leq V_{DD} \leq 5.5V$ |

|                                                         | TscL2doV              |                                          | <u> </u>       | _    | 145  | ns    | $1.8V \leq V_{DD} \leq 5.5V$ |

| SP81*                                                   | TDOV2scH,<br>TDOV2scL | SDO data output setup to SCK edge        | 1 TCy          | _    | _    | ns    |                              |

| SP82*                                                   | TssL2DoV              | SDO data output valid after SS√ edge     | <del>\</del> \ | _    | 50   | ns    |                              |

| SP83*                                                   | TscH2ssH,<br>TscL2ssH | SS ↑ after SCK edge                      | 1.5 Tcy + 40   | _    | _    | ns    |                              |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

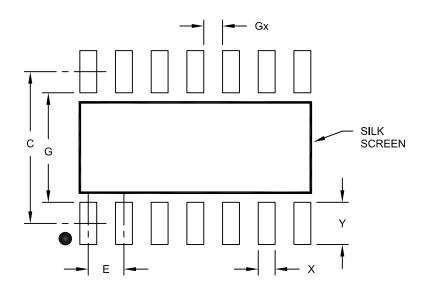

# 14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                       | Units  | MILLIMETERS |      |      |  |

|-----------------------|--------|-------------|------|------|--|

| Dimension             | Limits | MIN         | NOM  | MAX  |  |

| Contact Pitch         | E      | 1,27 BSC    |      |      |  |

| Contact Pad Spacing   | С      |             | 5.40 |      |  |

| Contact Pad Width     | Х      |             |      | 0.60 |  |

| Contact Pad Length    | Υ      |             |      | 1.50 |  |

| Distance Between Pads | Gx     | 0.67        |      |      |  |

| Distance Between Pads | G      | 3.90        |      |      |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A