Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f15323t-i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

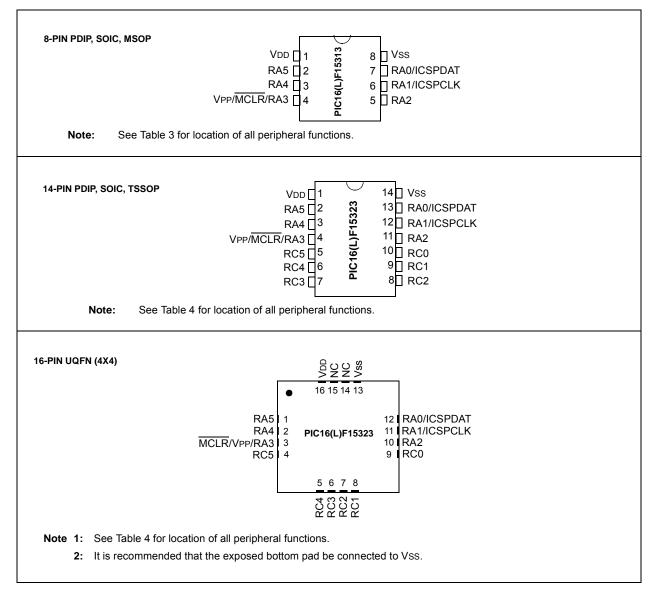

#### **PIN DIAGRAMS**

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | Name       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------------------------------------|------------|-------|-------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|

| Bank 21-59                                      | Bank 21-59 |       |       |       |       |       |       |       |       |                       |                            |

| CPU CORE REGISTERS; see Table 4-3 for specifics |            |       |       |       |       |       |       |       |       |                       |                            |

| x0Ch/<br>x8Ch<br>Unimplemented                  |            |       |       |       |       |       |       |       | _     |                       |                            |

| Legend:                                         |            |       |       |       |       |       |       |       |       |                       |                            |

| Address | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4         | Bit 3             | Bit 2     | Bit 1        | Bit 0    | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|----------|----------|----------|----------|---------------|-------------------|-----------|--------------|----------|-----------------------|----------------------------|

| Bank 60 |          |          |          |          |               |                   |           |              |          |                       |                            |

|         |          |          |          | CPU COF  | RE REGISTERS; | see Table 4-3 for | specifics |              |          |                       |                            |

| 1E0Ch   | _        |          |          |          | Unimpler      | mented            |           |              |          | _                     | —                          |

| 1E0Dh   | _        |          |          |          | Unimpler      | mented            |           |              |          | -                     | _                          |

| 1E0Eh   | _        |          |          |          | Unimpler      | mented            |           |              |          | _                     | _                          |

| 1E0Fh   | CLCDATA  | —        | _        | _        | _             | MLC4OUT           | MLC3OUT   | MLC2OUT      | MLC1OUT  | xxxx                  | uuuu                       |

| 1E10h   | CLCCON   | LC1EN    | _        | LC10UT   | LC1INTP       | LC1INTN           |           | LC1MODE<2:0  | )>       | 0-00 0000             | 0-00 0000                  |

| 1E11h   | CLC1POL  | LC1POL   | _        | _        | _             | LC1G4POL          | LC1G3POL  | LC1G2POL     | LC1G1POL | 0 xxxx                | 0 uuuu                     |

| 1E12h   | CLC1SEL0 | —        | _        |          |               | LC1E              | 01S<5:0>  |              |          | xx xxxx               | uu uuuu                    |

| 1E13h   | CLC1SEL1 | _        | _        |          |               | LC1E              | )2S<5:0>  |              |          | xx xxxx               | uu uuuu                    |

| 1E14h   | CLC1SEL2 | _        | _        |          |               | LC1E              | 03S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E15h   | CLC1SEL3 | —        | _        |          |               | LC1D              | )4S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E16h   | CLC1GLS0 | LC1G1D4T | LC1G4D3N | LC1G1D3T | LC1G1D3N      | LC1G1D2T          | LC1G1D2N  | LC1G1D1T     | LC1G1D1N | XXXX XXXX             | uuuu uuu                   |

| 1E17h   | CLC1GLS1 | LC1G2D4T | LC1G4D3N | LC1G2D3T | LC1G2D3N      | LC1G2D2T          | LC1G2D2N  | LC1G2D1T     | LC1G2D1N | XXXX XXXX             | นนนน นนนเ                  |

| 1E18h   | CLC1GLS2 | LC1G3D4T | LC1G4D3N | LC1G3D3T | LC1G3D3N      | LC1G3D2T          | LC1G3D2N  | LC1G3D1T     | LC1G3D1N | XXXX XXXX             | uuuu uuu                   |

| 1E19h   | CLC1GLS3 | LC1G4D4T | LC1G4D3N | LC1G4D3T | LC1G4D3N      | LC1G4D2T          | LC1G4D2N  | LC1G4D1T     | LC1G4D1N | XXXX XXXX             | uuuu uuu                   |

| 1E1Ah   | CLC2CON  | LC2EN    | _        | LC2OUT   | LC2INTP       | LC2INTN           |           | LC2MODE<2:0> |          |                       | 0-00 000                   |

| 1E1Bh   | CLC2POL  | LC2POL   | _        | _        |               | LC2G4POL          | LC2G3POL  | LC2G2POL     | LC2G1POL | 0 xxxx                | 0 uuu                      |

| 1E1Ch   | CLC2SEL0 | _        | _        |          | •             | LC2               | D1S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E1Dh   | CLC2SEL1 | _        | _        |          |               | LC2               | )2S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E1Eh   | CLC2SEL2 | —        | _        |          |               | LC2E              | 03S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E1Fh   | CLC2SEL3 | —        | _        |          |               | LC2E              | )4S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E20h   | CLC2GLS0 | LC2G1D4T | LC2G4D3N | LC2G1D3T | LC2G1D3N      | LC2G1D2T          | LC2G1D2N  | LC2G1D1T     | LC2G1D1N | XXXX XXXX             | นนนน นนนเ                  |

| 1E21h   | CLC2GLS1 | LC2G2D4T | LC2G4D3N | LC2G2D3T | LC2G2D3N      | LC2G2D2T          | LC2G2D2N  | LC2G2D1T     | LC2G2D1N | XXXX XXXX             | นนนน นนนเ                  |

| 1E22h   | CLC2GLS2 | LC2G3D4T | LC2G4D3N | LC2G3D3T | LC2G3D3N      | LC2G3D2T          | LC2G3D2N  | LC2G3D1T     | LC2G3D1N | xxxx xxxx             | นนนน นนนเ                  |

| 1E23h   | CLC2GLS3 | LC2G4D4T | LC2G4D3N | LC2G4D3T | LC2G4D3N      | LC2G4D2T          | LC2G4D2N  | LC2G4D1T     | LC2G4D1N | xxxx xxxx             | นนนน นนนเ                  |

| 1E24h   | CLC3CON  | LC3EN    | —        | LC3OUT   | LC3INTP       | LC3INTN           |           | LC3MODE      |          | 0-00 0000             | 0-00 000                   |

| 1E25h   | CLC3POL  | LC3POL   | _        | _        | _             | LC3G4POL          | LC3G3POL  | LC3G2POL     | LC3G1POL | 0 xxxx                | 0 uuu                      |

| 1E26h   | CLC3SEL0 | —        | —        |          |               | LC3E              | 01S<5:0>  |              |          | xx xxxx               | uu uuuu                    |

| 1E27h   | CLC3SEL1 | —        | —        |          |               | LC3E              | )2S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E28h   | CLC3SEL2 | _        | —        |          |               | LC3E              | 03S<5:0>  |              |          | xx xxxx               | uu uuu                     |

| 1E29h   | CLC3SEL3 | —        | —        |          |               | LC3E              | 04S<5:0>  |              |          | xx xxxx               | uu uuuu                    |

| 1E2Ah   | CLC3GLS0 | LC3G1D4T | LC3G4D3N | LC3G1D3T | LC3G1D3N      | LC3G1D2T          | LC3G1D2N  | LC3G1D1T     | LC3G1D1N | xxxx xxxx             | นนนน นนนเ                  |

#### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

DS40001897A-page 61

## PIC16(L)F15313/23

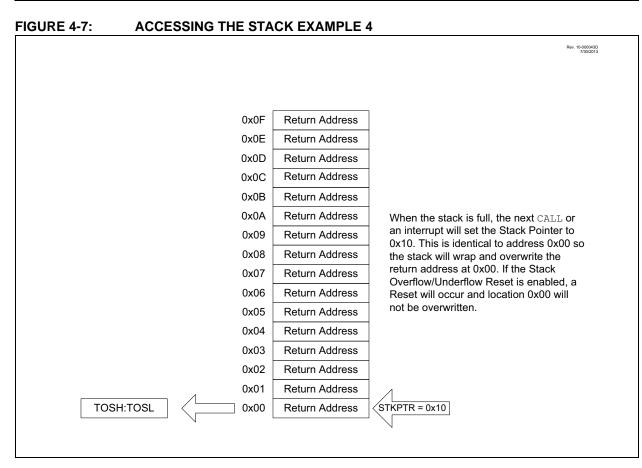

#### 4.5.2 OVERFLOW/UNDERFLOW RESET

If the STVREN bit in Configuration Words (Register 5-2) is programmed to '1', the device will be Reset if the stack is PUSHed beyond the sixteenth level or POPed beyond the first level, setting the appropriate bits (STKOVF or STKUNF, respectively) in the PCON register.

#### 4.6 Indirect Addressing

The INDFn registers are not physical registers. Any instruction that accesses an INDFn register actually accesses the register at the address specified by the File Select Registers (FSR). If the FSRn address specifies one of the two INDFn registers, the read will return '0' and the write will not occur (though Status bits may be affected). The FSRn register value is created by the pair FSRnH and FSRnL.

The FSR registers form a 16-bit address that allows an addressing space with 65536 locations. These locations are divided into three memory regions:

- Traditional/Banked Data Memory

- Linear Data Memory

- Program Flash Memory

#### REGISTER 5-3: CONFIGURATION WORD 3: WINDOWED WATCHDOG (CONTINUED)

bit 4-0 WDTCPS<4:0>: WDT Period Select bits

| WDTCPS           | Value     | Divider R | r Ratio Typical Time Out<br>(FIN = 31 kHz) |        | - Software Control<br>of WDTPS? |

|------------------|-----------|-----------|--------------------------------------------|--------|---------------------------------|

| 11111 <b>(1)</b> | 01011     | 1:65536   | 2 <sup>16</sup>                            | 2 s    | Yes                             |

| 11110            | 11110     |           | _                                          |        |                                 |

| <br>10011        | <br>10011 | 1:32      | 2 <sup>5</sup>                             | 1 ms   | No                              |

| 10010            | 10010     | 1:8388608 | 2 <sup>23</sup>                            | 256 s  |                                 |

| 10001            | 10001     | 1:4194304 | 2 <sup>22</sup>                            | 128 s  |                                 |

| 10000            | 10000     | 1:2097152 | 2 <sup>21</sup>                            | 64 s   |                                 |

| 01111            | 01111     | 1:1048576 | 2 <sup>20</sup>                            | 32 s   |                                 |

| 01110            | 01110     | 1:524299  | 2 <sup>19</sup>                            | 16 s   |                                 |

| 01101            | 01101     | 1:262144  | 2 <sup>18</sup>                            | 8 s    |                                 |

| 01100            | 01100     | 1:131072  | 2 <sup>17</sup>                            | 4 s    |                                 |

| 01011            | 01011     | 1:65536   | 2 <sup>16</sup>                            | 2 s    |                                 |

| 01010            | 01010     | 1:32768   | 2 <sup>15</sup>                            | 1 s    |                                 |

| 01001            | 01001     | 1:16384   | 2 <sup>14</sup>                            | 512 ms | No                              |

| 01000            | 01000     | 1:8192    | 2 <sup>13</sup>                            | 256 ms |                                 |

| 00111            | 00111     | 1:4096    | 2 <sup>12</sup>                            | 128 ms |                                 |

| 00110            | 00110     | 1:2048    | 2 <sup>11</sup>                            | 64 ms  |                                 |

| 00101            | 00101     | 1:1024    | 2 <sup>10</sup>                            | 32 ms  |                                 |

| 00100            | 00100     | 1:512     | 2 <sup>9</sup>                             | 16 ms  | ]                               |

| 00011            | 00011     | 1:256     | 2 <sup>8</sup>                             | 8 ms   | ]                               |

| 00010            | 00010     | 1:128     | 27                                         | 4 ms   | ]                               |

| 00001            | 00001     | 1:64      | 2 <sup>6</sup>                             | 2 ms   | ]                               |

| 00000            | 00000     | 1:32      | 2 <sup>5</sup>                             | 1 ms   |                                 |

Note 1: 0b11111 is the default value of the WDTCPS bits.

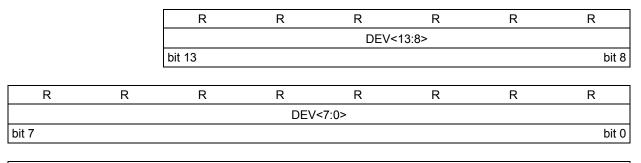

#### 5.6 Device ID and Revision ID

The 14-bit Device ID word is located at 8006h and the 14-bit Revision ID is located at 8005h. These locations are read-only and cannot be erased or modified.

Development tools, such as device programmers and debuggers, may be used to read the Device ID, Revision ID and Configuration Words. These locations can also be read from the NVMCON register.

#### 5.7 Register Definitions: Device and Revision

#### REGISTER 5-6: DEVID: DEVICE ID REGISTER

#### Legend:

R = Readable bit

'1' = Bit is set '0' = Bit is cleared

bit 13-0 **DEV<13:0>:** Device ID bits

| Device       | DEVID<13:0> Values        |  |  |  |  |  |  |

|--------------|---------------------------|--|--|--|--|--|--|

| PIC16F15313  | 11 0000 1011 1110 (30BEh) |  |  |  |  |  |  |

| PIC16LF15313 | 11 0000 1011 1111 (30BFh) |  |  |  |  |  |  |

| PIC16F15323  | 11 0000 1100 0000 (30C0h) |  |  |  |  |  |  |

| PIC16LF15323 | 11 0000 1100 0001 (30C1h) |  |  |  |  |  |  |

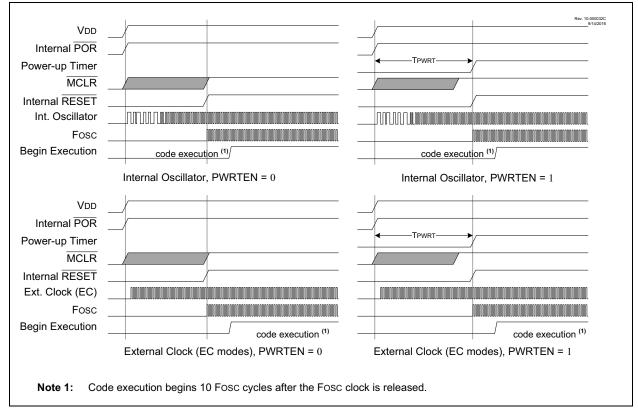

#### 8.11 Start-up Sequence

Upon the release of a POR or BOR, the following must occur before the device will begin executing:

- 1. Power-up Timer runs to completion (if enabled).

- 2. Oscillator start-up timer runs to completion (if required for oscillator source).

- 3. MCLR must be released (if enabled).

The total time-out will vary based on oscillator configuration and Power-up Timer Configuration. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information.

The Power-up Timer runs independently of MCLR Reset. If MCLR is kept low long enough, the Power-up Timer and oscillator start-up timer will expire. This is useful for testing purposes or to synchronize more than one device operating in parallel. See Figure 8-3.

FIGURE 8-3: RESET START-UP SEQUENCE

#### 12.1 Independent Clock Source

The WDT can derive its time base from either the 31 kHz LFINTOSC or 31.25 kHz MFINTOSC internal oscillators, depending on the value of either the WDTCCS<2:0> Configuration bits or the WDTCS<2:0> bits of WDTCON1. Time intervals in this chapter are based on a minimum nominal interval of 1 ms. See **Section 37.0 "Electrical Specifications"** for LFINTOSC and MFINTOSC tolerances.

#### 12.2 WDT Operating Modes

The Watchdog Timer module has four operating modes controlled by the WDTE<1:0> bits in Configuration Words. See Table 12-1.

#### 12.2.1 WDT IS ALWAYS ON

When the WDTE bits of Configuration Words are set to '11', the WDT is always on.

WDT protection is active during Sleep.

#### 12.2.2 WDT IS OFF IN SLEEP

When the WDTE bits of Configuration Words are set to '10', the WDT is on, except in Sleep.

WDT protection is not active during Sleep.

#### 12.2.3 WDT CONTROLLED BY SOFTWARE

When the WDTE bits of Configuration Words are set to '01', the WDT is controlled by the SWDTEN bit of the WDTCON0 register.

#### 12.2.4 WDT IS OFF

When the WDTE bits of the Configuration Word are set to '00', the WDT is always OFF.

WDT protection is unchanged by Sleep. See Table 12-1 for more details.

| WDTE<1:0> | SWDTEN | Device<br>Mode | WDT<br>Mode |

|-----------|--------|----------------|-------------|

| 11        | Х      | Х              | Active      |

| 10        | 37     | Awake          | Active      |

| TO        | Х      | Sleep          | Disabled    |

| 0.1       | 1      | Х              | Active      |

| 01        | 0      | Х              | Disabled    |

| 00        | х      | Х              | Disabled    |

#### TABLE 12-1: WDT OPERATING MODES

#### 12.3 Time-Out Period

The WDTPS bits of the WDTCON0 register set the time-out period from 1 ms to 256 seconds (nominal). After a Reset, the default time-out period is two seconds.

#### 12.4 Watchdog Window

The Watchdog Timer has an optional Windowed mode that is controlled by the WDTCWS<2:0> Configuration bits and WINDOW<2:0> bits of the WDTCON1 register. In the Windowed mode, the CLRWDT instruction must occur within the allowed window of the WDT period. Any CLRWDT instruction that occurs outside of this window will trigger a window violation and will cause a WDT Reset, similar to a WDT time out. See Figure 12-2 for an example.

The window size is controlled by the WDTCWS<2:0> Configuration bits, or the WINDOW<2:0> bits of WDTCON1, if WDTCWS<2:0> = 111.

In the event of a <u>window</u> violation, a Reset will be generated and the WDTWV bit of the PCON register will be cleared. This bit is set by a POR or can be set in firmware.

#### 12.5 Clearing the WDT

The WDT is cleared when any of the following conditions occur:

- Any Reset

- Valid CLRWDT instruction is executed

- · Device enters Sleep

- · Device wakes up from Sleep

- · WDT is disabled

- Oscillator Start-up Timer (OST) is running

- Any write to the WDTCON0 or WDTCON1 registers

#### 12.5.1 CLRWDT CONSIDERATIONS (WINDOWED MODE)

When in Windowed mode, the WDT must be armed before a CLRWDT instruction will clear the timer. This is performed by reading the WDTCON0 register. Executing a CLRWDT instruction without performing such an arming action will trigger a window violation.

See Table 12-2 for more information.

#### 12.6 Operation During Sleep

When the device enters Sleep, the WDT is cleared. If the WDT is enabled during Sleep, the WDT resumes counting. When the device exits Sleep, the WDT is cleared again.

The WDT remains clear until the OST, if enabled, completes. See Section 9.0 "Oscillator Module (with Fail-Safe Clock Monitor)" for more information on the OST.

When a WDT time-out occurs while the device is in Sleep, no Reset is generated. Instead, the device wakes up and resumes operation. The TO and PD bits in the STATUS register are changed to indicate the event. The RWDT bit in the PCON register can also be used. See Section 4.3.2.1 "STATUS Register" for more information.

PIC16(L)F15313/23

### 14.0 I/O PORTS

#### TABLE 14-1: PORT AVAILABILITY PER DEVICE

| Device         | PORTA | PORTC |

|----------------|-------|-------|

| PIC16(L)F15313 | •     |       |

| PIC16(L)F15323 | •     | •     |

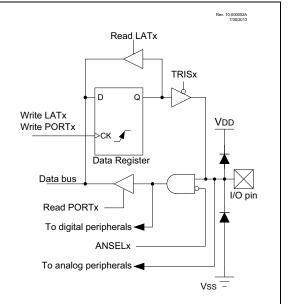

Each port has standard registers for its operation. These registers are:

- PORTx registers (reads the levels on the pins of the device)

- LATx registers (output latch)

- TRISx registers (data direction)

- ANSELx registers (analog select)

- WPUx registers (weak pull-up)

- INLVLx (input level control)

- SLRCONx registers (slew rate)

- ODCONx registers (open-drain)

Most port pins share functions with device peripherals, both analog and digital. In general, when a peripheral is enabled on a port pin, that pin cannot be used as a general purpose output; however, the pin can still be read.

The Data Latch (LATx registers) is useful for read-modify-write operations on the value that the I/O pins are driving.

A write operation to the LATx register has the same effect as a write to the corresponding PORTx register. A read of the LATx register reads of the values held in the I/O PORT latches, while a read of the PORTx register reads the actual I/O pin value.

Ports that support analog inputs have an associated ANSELx register. When an ANSEL bit is set, the digital input buffer associated with that bit is disabled.

Disabling the input buffer prevents analog signal levels on the pin between a logic high and low from causing excessive current in the logic input circuitry. A simplified model of a generic I/O port, without the interfaces to other peripherals, is shown in Figure 14-1.

#### FIGURE 14-1: GENERIC I/O PORT OPERATION

#### 14.1 I/O Priorities

Each pin defaults to the PORT data latch after Reset. Other functions are selected with the peripheral pin select logic. See **Section 15.0** "**Peripheral Pin Select** (**PPS**) **Module**" for more information.

Analog input functions, such as ADC and comparator inputs, are not shown in the peripheral pin select lists. These inputs are active when the I/O pin is set for Analog mode using the ANSELx register. Digital output functions may continue to control the pin when it is in Analog mode.

Analog outputs, when enabled, take priority over the digital outputs and force the digital output driver to the high-impedance state.

#### 20.4 Register Definitions: ADC Control

#### REGISTER 20-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0              | R/W-0/0                                   | R/W-0/0            | R/W-0/0           | R/W-0/0             | R/W-0/0              | R/W-0/0 |

|------------------|----------------------|-------------------------------------------|--------------------|-------------------|---------------------|----------------------|---------|

|                  |                      | CHS<                                      | 5:0>               |                   |                     | GO/DONE              | ADON    |

| bit 7            |                      |                                           |                    |                   |                     |                      | bit (   |

| Legend:          |                      |                                           |                    |                   |                     |                      |         |

| R = Readable     | bit                  | W = Writable bit                          |                    | U = Unimpleme     | nted bit, read as ' | ʻ0'                  |         |

| u = Bit is unch  | anged                | x = Bit is unknow                         | vn                 | -n/n = Value at F | POR and BOR/Va      | alue at all other Re | sets    |

| '1' = Bit is set |                      | '0' = Bit is cleare                       | d                  |                   |                     |                      |         |

|                  |                      |                                           |                    |                   |                     |                      |         |

| bit 7-2          |                      | Analog Channel Sele                       | (-)                |                   |                     |                      |         |

|                  | 111111 =             | FVR Buffer 2 refere                       |                    |                   |                     |                      |         |

|                  | 111110 =<br>111101 = | FVR 1Buffer 1 refer<br>DAC1 output voltag |                    |                   |                     |                      |         |

|                  | 111101 =             | Temperature senso                         | (m)                |                   |                     |                      |         |

|                  | 1110011 =            | AVss (Analog Grou                         |                    |                   |                     |                      |         |

|                  | 010111 =             | Reserved                                  | iu)                |                   |                     |                      |         |

|                  | 010110 =             | Reserved                                  |                    |                   |                     |                      |         |

|                  | 010101 =             | RC5 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010100 =             | RC4 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010011 =             | RC3 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010010 =             | RC2 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010001 =             | RC1 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010000 =             | RC0 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 001111 =             | Reserved                                  |                    |                   |                     |                      |         |

|                  | •                    |                                           |                    |                   |                     |                      |         |

|                  | •                    |                                           |                    |                   |                     |                      |         |

|                  | •                    |                                           |                    |                   |                     |                      |         |

|                  | 000110 =             | Reserved                                  |                    |                   |                     |                      |         |

|                  | 000101 =             | RA5 <sup>(5)</sup>                        |                    |                   |                     |                      |         |

|                  | 000100 =             | RA4 <sup>(5)</sup>                        |                    |                   |                     |                      |         |

|                  | 000011 =<br>000010 = | RA3<br>RA2                                |                    |                   |                     |                      |         |

|                  | 000010 =             | RAZ<br>RA1                                |                    |                   |                     |                      |         |

|                  | 0000001 -            | RA1<br>RA0                                |                    |                   |                     |                      |         |

| bit 1            | GO/DONE: /           | ADC Conversion Stat                       | us bit             |                   |                     |                      |         |

|                  | 1 = ADC cor          | version cycle in prog                     | ress. Setting this | bit starts an ADC | conversion cycle    |                      |         |

|                  | This bit is          | s automatically cleare                    | d by hardware w    | hen the ADC conv  | version has comp    | leted.               |         |

|                  | 0 = ADC cor          | version completed/ne                      | ot in progress     |                   |                     |                      |         |

| bit 0            | ADON: ADC            | Enable bit                                |                    |                   |                     |                      |         |

|                  | 1 = ADC is e         |                                           |                    |                   |                     |                      |         |

|                  | 0 = ADC is d         | lisabled and consume                      | es no operating o  | current           |                     |                      |         |

| Note 1: S        | ee Section 21 0      | "5-Bit Digital-to-Ana                     | alog Converter     | (DAC1) Module" f  | or more informati   | ion                  |         |

|                  |                      | "Fixed Voltage Refe                       | •                  | . ,               |                     |                      |         |

|                  |                      | "Temperature Indic                        | • •                |                   |                     |                      |         |

|                  |                      |                                           |                    |                   |                     |                      |         |

- 4: Present only on the PIC16(L)F15323.

- 5: The analog functionality on the channels RA4 and RA5 is disabled when the system clock source is an external oscillator.

#### REGISTER 23-3: CMxNSEL: COMPARATOR Cx NEGATIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | _   | _   | _   |         | NCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

#### Legend:

| Logonal              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-3 | Unimplemented: Read as '0'                              |

|---------|---------------------------------------------------------|

| bit 2-0 | NCH<2:0>: Comparator Negative Input Channel Select bits |

|         | 111 = CxVN connects to AVss                             |

|         | 110 = CxVN connects to FVR Buffer 2                     |

|         | 101 = CxVN unconnected                                  |

|         | 100 = CxVN unconnected                                  |

|         |                                                         |

- 011 = CxVN connects to CxIN3- pin

- 010 = CxVN connects to CxIN2- pin

- 001 = CxVN connects to CxIN1- pin

- 000 = CxVN connects to CxIN0- pin

#### REGISTER 23-4: CMxPSEL: COMPARATOR Cx POSITIVE INPUT SELECT REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |

|-------|-----|-----|-----|-----|---------|----------|---------|

| _     | _   | _   | —   | —   |         | PCH<2:0> |         |

| bit 7 |     |     |     |     |         |          | bit 0   |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-3 Unimplemented: Read as '0'

bit 2-0 PCH<2:0>: Comparator Positive Input Channel Select bits

- 111 = CxVP connects to AVss

- 110 = CxVP connects to FVR Buffer 2

- 101 = CxVP connects to DAC output

- 100 = CxVP unconnected

- 011 = CxVP unconnected

- 010 = CxVP unconnected

- 001 = CxVP connects to CxIN1+ pin

- 000 = CxVP connects to CxIN0+ pin

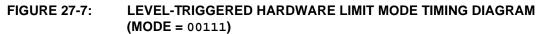

#### 27.5.4 LEVEL-TRIGGERED HARDWARE LIMIT MODE

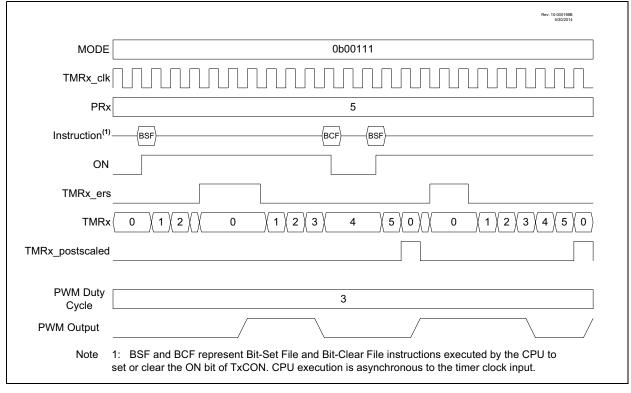

In the Level-Triggered Hardware Limit Timer modes the counter is reset by high or low levels of the external signal TMRx\_ers, as shown in Figure 27-7. Selecting MODE<4:0> = 0.0110 will cause the timer to reset on a low level external signal. Selecting MODE<4:0> = 0.0111 will cause the timer to reset on a high level external signal. In the example, the counter is reset while TMRx\_ers = 1. ON is controlled by BSF and BCF instructions. When ON = 0 the external signal is ignored.

When the CCP uses the timer as the PWM time base then the PWM output will be set high when the timer starts counting and then set low only when the timer count matches the CCPRx value. The timer is reset when either the timer count matches the PRx value or two clock periods after the external Reset signal goes true and stays true.

The timer starts counting, and the PWM output is set high, on either the clock following the PRx match or two clocks after the external Reset signal relinquishes the Reset. The PWM output will remain high until the timer counts up to match the CCPRx pulse width value. If the external Reset signal goes true while the PWM output is high then the PWM output will remain high until the Reset signal is released allowing the timer to count up to match the CCPRx value.

#### 28.3.4 TIMER2 TIMER RESOURCE

This device has a newer version of the Timer2 module that has many new modes, which allow for greater customization and control of the PWM signals than on older parts. Refer to **Section 27.5** "**Operation Examples**" for examples of PWM signal generation using the different modes of Timer2. The CCP operation requires that the timer used as the PWM time base has the FOSC/4 clock source selected

#### 28.3.5 PWM PERIOD

The PWM period is specified by the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 28-1.

#### EQUATION 28-1: PWM PERIOD

$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$ (TMR2 Prescale Value)

Note 1: Tosc = 1/Fosc

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCPx pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is transferred from the CCPRxL/H register pair into a 10-bit buffer.

| Note: | The Timer postscaler (see Section 27.4 |

|-------|----------------------------------------|

|       | "Timer2 Interrupt") is not used in the |

|       | determination of the PWM frequency.    |

#### 28.3.6 PWM DUTY CYCLE

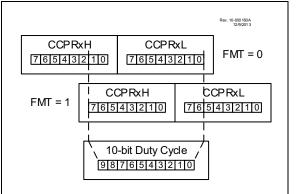

The PWM duty cycle is specified by writing a 10-bit value to the CCPRxH:CCPRxL register pair. The alignment of the 10-bit value is determined by the CCPRxFMT bit of the CCPxCON register (see Figure 28-5). The CCPRxH:CCPRxL register pair can be written to at any time; however the duty cycle value is not latched into the 10-bit buffer until after a match between PR2 and TMR2.

Equation 28-2 is used to calculate the PWM pulse width.

Equation 28-3 is used to calculate the PWM duty cycle ratio.

#### FIGURE 28-5: PWM

#### **PWM 10-BIT ALIGNMENT**

#### EQUATION 28-2: PULSE WIDTH

Pulse Width = (CCPRxH:CCPRxL register pair) •

TOSC • (TMR2 Prescale Value)

#### EQUATION 28-3: DUTY CYCLE RATIO

Duty Cycle Ratio =

$$\frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$$

CCPRxH:CCPRxL register pair are used to double buffer the PWM duty cycle. This double buffering provides for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 28-4).

#### 28.3.7 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 28-4.

#### EQUATION 28-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

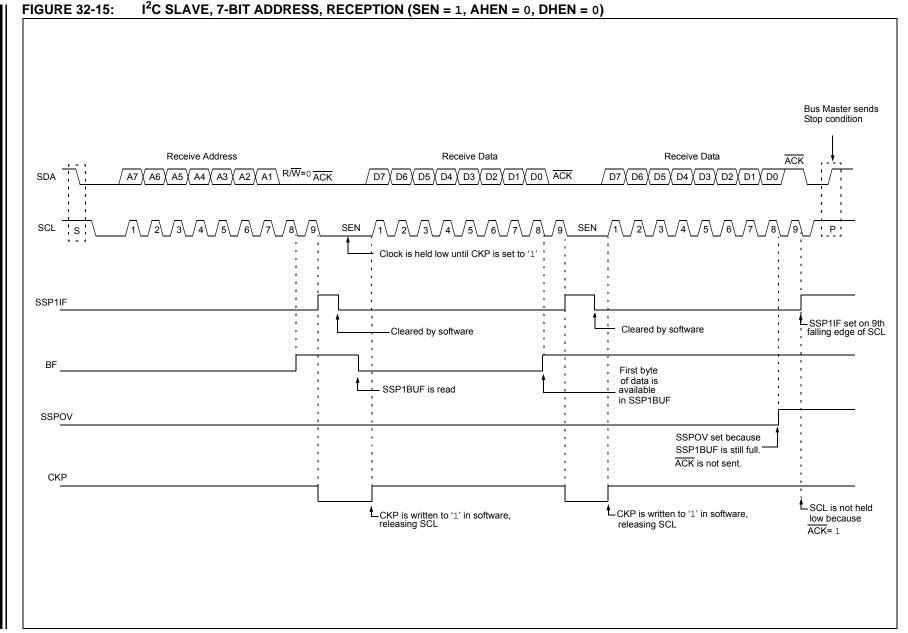

### **FIGURE 32-15:**

PIC16(L)F15313/23

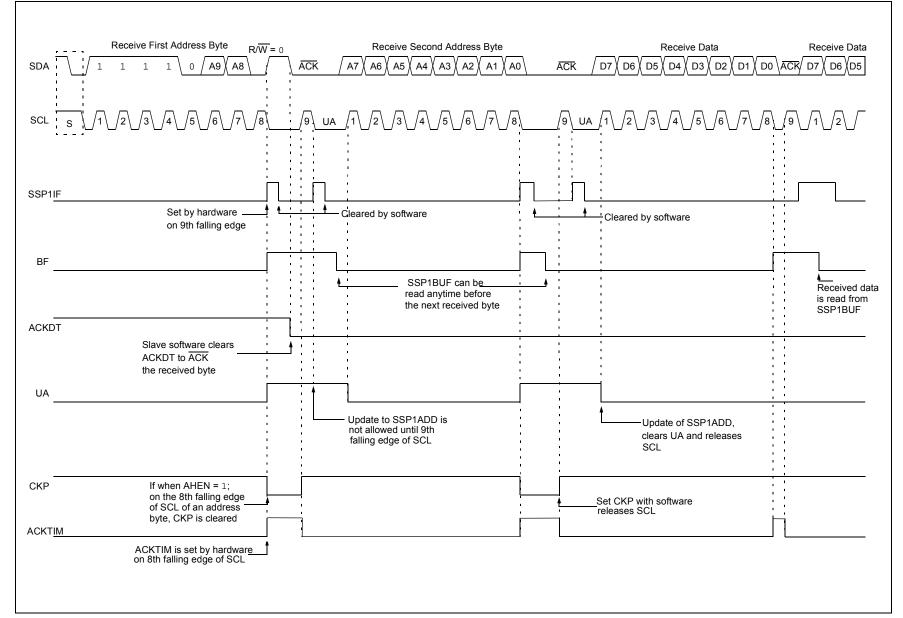

#### FIGURE 32-21: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 1, DHEN = 0)

Preliminary

PIC16(L)F15313/23

#### 33.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TX1STA register configures the device for synchronous operation. Clearing the CSRC bit of the TX1STA register configures the device as a slave. Clearing the SREN and CREN bits of the RC1STA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RC1STA register enables the EUSART.

#### 33.4.2.1 EUSART Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 33.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode.

If two words are written to the TX1REG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TX1REG register.

- 3. The TX1IF bit will not be set.

- After the first character has been shifted out of TSR, the TX1REG register will transfer the second character to the TSR and the TX1IF bit will now be set.

- 5. If the PEIE and TX1IE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

- 33.4.2.2 Synchronous Slave Transmission Set-up:

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- 4. If interrupts are desired, set the TX1IE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TX1REG register.

#### 37.3 **DC Characteristics**

| 37.3                                                                  |          | aracteristics                |                                                         |                                |                     |          | $\wedge$                             |  |  |  |

|-----------------------------------------------------------------------|----------|------------------------------|---------------------------------------------------------|--------------------------------|---------------------|----------|--------------------------------------|--|--|--|

| TABLE 37-1: SUPPLY VOLTAGE                                            |          |                              |                                                         |                                |                     |          |                                      |  |  |  |

| PIC16LF15313/23                                                       |          |                              | Standard Operating Conditions (unless otherwise stated) |                                |                     |          |                                      |  |  |  |

| PIC16F15313/23                                                        |          |                              |                                                         |                                |                     |          |                                      |  |  |  |

| Param.<br>No.                                                         | Sym.     | Characteristic               | Min.                                                    | n. Typ.† Max. Units Conditions |                     |          |                                      |  |  |  |

| Supply Voltage                                                        |          |                              |                                                         |                                |                     |          |                                      |  |  |  |

| D002                                                                  | Vdd      |                              | 1.8<br>2.5                                              |                                | 3.6<br>3.6          | ∨<br>★   | Fosc ≤ 16 MHz<br>Fosc > 16 MHz       |  |  |  |

| D002                                                                  | Vdd      |                              | 2.3<br>2.5                                              |                                | 5.5<br>5.5          | √<br>√ √ | Fosc ≤ 16 MHz<br>Føsç ≥ 16 MHz       |  |  |  |

| RAM Data Retention <sup>(1)</sup>                                     |          |                              |                                                         |                                |                     |          | ~_~                                  |  |  |  |

| D003                                                                  | Vdr      |                              | 1.5                                                     | _                              | $\langle \rangle$   | V \      | Device in Sleep mode                 |  |  |  |

| D003                                                                  | Vdr      |                              | 1.7                                                     | -~                             |                     | Y        | Device in Sleep mode                 |  |  |  |

| Power-on Reset Release Voltage <sup>(2)</sup>                         |          |                              |                                                         |                                |                     |          |                                      |  |  |  |

| D004                                                                  | VPOR     |                              | —                                                       | /1,6                           | $\overline{/}$      | V        | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| D004                                                                  | VPOR     |                              |                                                         | 1.6                            | Ń                   | > V      | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| Power-o                                                               | on Reset | Rearm Voltage <sup>(2)</sup> |                                                         | $\langle \ \rangle$            | $\langle \ \rangle$ | ·        |                                      |  |  |  |

| D005                                                                  | VPORR    |                              | $ \neq \ell$                                            | 8.0                            | $\searrow$          | V        | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| D005                                                                  | VPORR    |                              |                                                         | 1,5                            | > -                 | V        | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| VDD Rise Rate to ensure internal Power-on Reset signal <sup>(2)</sup> |          |                              |                                                         |                                |                     |          |                                      |  |  |  |

| D006                                                                  | SVDD     | $\land$                      | 0.05                                                    | $\searrow$                     |                     | V/ms     | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

| D006                                                                  | SVDD     |                              | 0.05                                                    | $\rangle$ –                    | —                   | V/ms     | BOR or LPBOR disabled <sup>(3)</sup> |  |  |  |

† Data in "Typ." column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

2: See Figure 37-3, POR and POR REARM with Slow Rising VDD.

3: See Table 37-11 for BQR and LPBOR trip point information. = F device

4:

| TABLE 37-18: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

|               | Standard Operating Conditions (unless otherwise stated) |                           |                                               |                            |                            |        |                       |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|---------------------------------------------------------|---------------------------|-----------------------------------------------|----------------------------|----------------------------|--------|-----------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | ng Temperatur                                           |                           |                                               | e stateu)                  |                            |        | -                     |                    | $\sum_{i=1}^{n} \sum_{j=1}^{n} \sum_{i=1}^{n} \sum_{j=1}^{n} \sum_{i$ |

| Param.<br>No. | Sym.                                                    |                           | Characteristic                                | Min.                       | Тур†                       | Max.   | Units                 | Conditions         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 40*           | T⊤0H                                                    | T0CKI High I              | T0CKI High Pulse Width No Presc               |                            | 0.5 Tcy + 20               | 1      | —                     | ns                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                         |                           |                                               | With Prescaler             | 10                         | _      | —                     | / ns               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 41*           | TT0L                                                    | T0CKI Low F               | ulse Width                                    | No Prescaler               | 0.5 TCY + 20               | _      | _/                    | /ns /              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                         |                           |                                               | With Prescaler             | 10                         | _      |                       | NS                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 42*           | TT0P                                                    | T0CKI Period              | ł                                             | Greater of:                | _                          | _      | ns <                  | N = prescale value |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |                                                         |                           |                                               | 20 or <u>Tcy + 40</u><br>N | $\square$                  |        |                       | $\searrow$         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 45*           | T⊤1H                                                    | T1CKI High                | Synchronous, No Prescaler                     |                            | 0.5 TCY + 20               | _/     | $\sim$                | ns                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |