Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5КВ (2К х 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 224 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                         |

| Mounting Type              | Through Hole                                                               |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 8-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15313-e-p |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 4.0 MEMORY ORGANIZATION

These devices contain the following types of memory:

- Program Memory

- Configuration Words

- Device ID

- User ID

- Program Flash Memory

- Device Information Area (DIA)

- Device Configuration Information (DCI)

- Revision ID

- Data Memory

- Core Registers

- Special Function Registers

- General Purpose RAM

- Common RAM

The following features are associated with access and control of program memory and data memory:

- PCL and PCLATH

- Stack

- Indirect Addressing

- NVMREG access

#### TABLE 4-1: DEVICE SIZES AND ADDRESSES

| Device            | Program Memory Size (Words) | Last Program Memory Address |

|-------------------|-----------------------------|-----------------------------|

| PIC16(L)F15313/23 | 2048                        | 07FFh                       |

#### 4.1 **Program Memory Organization**

The enhanced mid-range core has a 15-bit program counter capable of addressing  $32K \times 14$  program memory space. Table 4-1 shows the memory sizes implemented. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 4-1).

## 5.2 Register Definitions: Configuration Words

| REGISTER         | 5-1: CO                                                                                                                                              | NFIGURATIO                                                                                                                                                                                     | N WORD 1:                                                                          | OSCILLATO                                                                     | DRS                             |                                |                    |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|---------------------------------|--------------------------------|--------------------|

|                  |                                                                                                                                                      | R/P-1                                                                                                                                                                                          | U-1                                                                                | R/P-1                                                                         | U-1                             | U-1                            | R/P-1              |

|                  |                                                                                                                                                      | FCMEN                                                                                                                                                                                          | _                                                                                  | CSWEN                                                                         | _                               | _                              | CLKOUTEN           |

|                  |                                                                                                                                                      | bit 13                                                                                                                                                                                         |                                                                                    |                                                                               |                                 |                                | bit 8              |

| U-1              | R/P-1                                                                                                                                                | R/P-1                                                                                                                                                                                          | R/P-1                                                                              | U-1                                                                           | R/P-1                           | R/P-1                          | R/P-1              |

|                  | RSTOSC2                                                                                                                                              | RSTOSC1                                                                                                                                                                                        | RSTOSC0                                                                            |                                                                               | FEXTOSC2                        | FEXTOSC1                       | FEXTOSC0           |

| bit 7            | K310302                                                                                                                                              | K310301                                                                                                                                                                                        | K310300                                                                            | —                                                                             | FEAT0302                        | FEXIOSCI                       | bit                |

|                  |                                                                                                                                                      |                                                                                                                                                                                                |                                                                                    |                                                                               |                                 |                                |                    |

| Legend:          |                                                                                                                                                      |                                                                                                                                                                                                |                                                                                    |                                                                               |                                 |                                |                    |

| R = Readable     | e bit                                                                                                                                                | P = Programma                                                                                                                                                                                  | able bit                                                                           | x = Bit is unkn                                                               | own                             | U = Unimpleme<br>'1'           | nted bit, read as  |

| '0' = Bit is cle | ared                                                                                                                                                 | '1' = Bit is set                                                                                                                                                                               |                                                                                    | W = Writable b                                                                | bit                             | n = Value when<br>Erase        | blank or after Bul |

| bit 13           | FCMEN: Fail-<br>1 = FSCM ti<br>0 = FSCM ti                                                                                                           |                                                                                                                                                                                                | or Enable bit                                                                      |                                                                               |                                 |                                |                    |

| bit 12           | Unimplemen                                                                                                                                           | ted: Read as '1'                                                                                                                                                                               |                                                                                    |                                                                               |                                 |                                |                    |

| bit 11           | 1 = Writing to                                                                                                                                       | ck Switch Enable<br>o NOSC and NDI<br>SC and NDIV bits                                                                                                                                         | / is allowed                                                                       | nged by user sof                                                              | tware                           |                                |                    |

| bit 10-9         | Unimplemen                                                                                                                                           | ted: Read as '1'                                                                                                                                                                               |                                                                                    |                                                                               |                                 |                                |                    |

| bit 8            | <u>lf FEXTOSC</u><br>1 = CLKOUT                                                                                                                      | Clock Out Enable<br>= EC (high, mid ou<br>function is disable<br>function is enable<br>pred.                                                                                                   | <u>· low) or Not En</u><br>ed; I/O or oscill                                       | ator function on                                                              |                                 |                                |                    |

| bit 7            | -                                                                                                                                                    | ted: Read as '1'                                                                                                                                                                               |                                                                                    |                                                                               |                                 |                                |                    |

| bit 6-4          | This value is 1      111 =    EXTO      110 =    HFIN      101 =    LFIN      100 =    Rese      011 =    Rese      010 =    EXTO      001 =    EXTO | DSC operating pe<br>TOSC with HFFR<br>TOSC<br>rved                                                                                                                                             | value for COSC<br>FEXTOSC bits<br>Q = 3 ' b010<br>with EXTOSC of<br>with EXTOSC of | C and selects the<br>s (device manufa<br>operating per FE<br>operating per FE | acturing default)<br>XTOSC bits | ed by user softwa              | re.                |

| bit 3            | Unimplemen                                                                                                                                           | ted: Read as '1'                                                                                                                                                                               |                                                                                    |                                                                               |                                 |                                |                    |

| bit 2-0          | 111 = EC (I<br>110 = EC (I<br>101 = EC (I<br>100 = Oscil<br>011 = Rese<br>010 = HS (I<br>001 = XT (C                                                 | 0>:FEXTOSC Ex<br>External Clock) at<br>External Clock) fo<br>External Clock) be<br>lator not enabled<br>rved (do not use)<br>Crystal oscillator)<br>Crystal oscillator)<br>Crystal oscillator) | ove 8 MHz; PF<br>100 kHz to 8 M<br>low 100 kHz<br>above 4 MHz; F<br>above 100 kHz, | M set to high po<br>MHz; PFM set to<br>PFM set to high  <br>below 4 MHz; F    | wer (device manumedium power    | ıfacturing default)<br>n power |                    |

### REGISTER 5-1: CONFIGURATION WORD 1: OSCILLATORS

### 8.14 Power Control (PCONx) Registers

The Power Control (PCONx) registers contain flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Reset Instruction Reset (RI)

- MCLR Reset (RMCLR)

- Watchdog Timer Reset (RWDT)

- Watchdog Timer Window Violation Reset

(WDTWV)

- Stack Underflow Reset (STKUNF)

- Stack Overflow Reset (STKOVF)

- Memory Violation Reset (MEMV)

The PCON0 register bits are shown in Register 8-2. The PCON1 register bits are shown in Register 8-3.

Hardware will change the corresponding register bit during the Reset process; if the Reset was not caused by the condition, the bit remains unchanged (Table 8-4).

Software should reset the bit to the inactive state after the restart (hardware will not reset the bit).

Software may also set any PCON bit to the active state, so that user code may be tested, but no reset action will be generated.

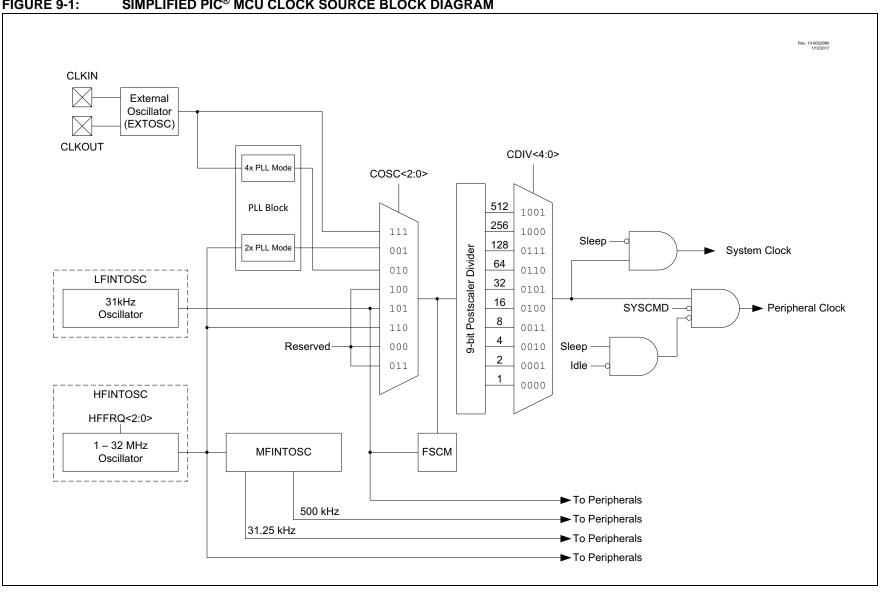

#### SIMPLIFIED PIC<sup>®</sup> MCU CLOCK SOURCE BLOCK DIAGRAM FIGURE 9-1:

PIC16(L)F15313/23

| U-0                                     | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> | R/W <sup>(3)</sup> -q/q <sup>(1)</sup> R/W <sup>(3)</sup> -q | /q <sup>(1)</sup> U-0                                 | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> | R/W <sup>(4)</sup> -q/q <sup>(2)</sup> |  |

|-----------------------------------------|----------------------------------------|--------------------------------------------------------------|-------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|--|

| -                                       | WDTCS<2:0>                             |                                                              | -                                                     |                                        | WINDOW<2:0>                            |                                        |  |

| bit 7                                   |                                        |                                                              |                                                       |                                        |                                        | bit 0                                  |  |

|                                         |                                        |                                                              |                                                       |                                        |                                        |                                        |  |

| Legend:                                 |                                        |                                                              |                                                       |                                        |                                        |                                        |  |

| R = Readable bit W = Writable bit       |                                        | U = Unimple                                                  | emented bit, read                                     | as '0'                                 |                                        |                                        |  |

| u = Bit is unchanged x = Bit is unknown |                                        | -n/n = Value                                                 | -n/n = Value at POR and BOR/Value at all other Resets |                                        |                                        |                                        |  |

| '1' = Bit is se                         | <u>e</u> t                             | '0' = Bit is cleared                                         | q = Value depends on condition                        |                                        |                                        |                                        |  |

| ʻ0' |

|-----|

| •   |

bit 6-4 WDTCS<2:0>: Watchdog Timer Clock Select bits

111 = Reserved

•

- •

- 010 = Reserved

001 = MFINTOSC 31.25 kHz

- 000 = LFINTOSC 31 kHz

- bit 3 Unimplemented: Read as '0'

- bit 2-0 WINDOW<2:0>: Watchdog Timer Window Select bits

| WINDOW<2:0> | Window delay<br>Percent of time | Window opening<br>Percent of time |

|-------------|---------------------------------|-----------------------------------|

| 111         | N/A                             | 100                               |

| 110         | 12.5                            | 87.5                              |

| 101         | 25                              | 75                                |

| 100         | 37.5                            | 62.5                              |

| 011         | 50                              | 50                                |

| 010         | 62.5                            | 37.5                              |

| 001         | 75                              | 25                                |

| 000         | 87.5                            | 12.5                              |

Note 1: If WDTCCS <2:0> in CONFIG3 = 111, the Reset value of WDTCS<2:0> is 000.

2: The Reset value of WINDOW<2:0> is determined by the value of WDTCWS<2:0> in the CONFIG3 register.

**3:** If WDTCCS<2:0> in CONFIG3  $\neq$  111, these bits are read-only.

4: If WDTCWS<2:0> in CONFIG3  $\neq$  111, these bits are read-only.

| Name    | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Register<br>on Page |

|---------|-------|-------|---------|---------|---------|---------|---------|---------|---------------------|

| PORTA   | _     |       | RA5     | RA4     | RA3     | RA2     | RA1     | RA0     | 175                 |

| TRISA   | _     | _     | TRISA5  | TRISA4  | _       | TRISA2  | TRISA1  | TRISA0  | 175                 |

| LATA    | _     | _     | LATA5   | LATA4   | _       | LATA2   | LATA1   | LATA0   | 176                 |

| ANSELA  | _     | _     | ANSA5   | ANSA4   | _       | ANSA2   | ANSA1   | ANSA0   | 176                 |

| WPUA    |       | _     | WPUA5   | WPUA4   | WPUA3   | WPUA2   | WPUA1   | WPUA0   | 177                 |

| ODCONA  |       | _     | ODCA5   | ODCA4   | —       | ODCA2   | ODCA1   | ODCA0   | 177                 |

| SLRCONA |       |       | SLRA5   | SLRA4   | —       | SLRA2   | SLRA1   | SLRA0   | 178                 |

| INLVLA  | _     | _     | INLVLA5 | INLVLA4 | INLVLA3 | INLVLA2 | INLVLA1 | INLVLA0 | 178                 |

#### TABLE 14-2: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

Legend: x = unknown, u = unchanged, – = unimplemented locations read as '0'. Shaded cells are not used by PORTA.

| REGISTER                                                                                                                              | R 16-2: PMC                                                                                      | D1: PMD CON                                          | TROL REGIS | STER 1         |                  |                  |              |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------|------------|----------------|------------------|------------------|--------------|

| R/W-0/0                                                                                                                               | U-0                                                                                              | U-0                                                  | U-0        | U-0            | R/W-0/0          | R/W-0/0          | R/W-0/0      |

| NCO1MD                                                                                                                                |                                                                                                  | _                                                    | _          | —              | TMR2MD           | TMR1MD           | TMR0MD       |

| bit 7                                                                                                                                 |                                                                                                  |                                                      |            |                |                  |                  | bit 0        |

|                                                                                                                                       |                                                                                                  |                                                      |            |                |                  |                  |              |

| Legend:                                                                                                                               |                                                                                                  |                                                      |            |                |                  |                  |              |

| R = Readab                                                                                                                            | ole bit                                                                                          | W = Writable                                         | bit        | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is un                                                                                                                         | ichanged                                                                                         | x = Bit is unk                                       | nown       | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is s                                                                                                                        | et                                                                                               | '0' = Bit is cle                                     | eared      | q = Value dep  | ends on condit   | ion              |              |

| bit 7<br>bit 6-3                                                                                                                      | 1 = NCO1 r<br>0 = NCO1 r                                                                         | Disable Numeric<br>nodule disablec<br>nodule enabled |            |                |                  |                  |              |

| bit 6-3 Unimplemented: Read as '0'<br>bit 2 TMR2MD: Disable Timer TMR2 bit<br>1 = Timer2 module disabled<br>0 = Timer2 module enabled |                                                                                                  |                                                      |            |                |                  |                  |              |

| bit 1                                                                                                                                 | t 1 TMR1MD: Disable Timer TMR1 bit<br>1 = Timer1 module disabled<br>0 = Timer1 module enabled    |                                                      |            |                |                  |                  |              |

| bit 0                                                                                                                                 | <b>TMR0MD:</b> Disable Timer TMR0 bit<br>1 = Timer0 module disabled<br>0 = Timer0 module enabled |                                                      |            |                |                  |                  |              |

| U-0              | U-0                                | R/W-0/0           | R/W-0/0 | R/W-0/0                                               | R/W-0/0 | R/W-0/0 | R/W-0/0 |  |

|------------------|------------------------------------|-------------------|---------|-------------------------------------------------------|---------|---------|---------|--|

| —                | —                                  | IOCCP5            | IOCCP4  | IOCCP3                                                | IOCCP2  | IOCCP1  | IOCCP0  |  |

| bit 7            |                                    | •                 |         |                                                       |         |         | bit 0   |  |

|                  |                                    |                   |         |                                                       |         |         |         |  |

| Legend:          |                                    |                   |         |                                                       |         |         |         |  |

| R = Readable b   | R = Readable bit W = Writable bit  |                   |         | U = Unimplemented bit, read as '0'                    |         |         |         |  |

| u = Bit is uncha | it is unchanged x = Bit is unknown |                   |         | -n/n = Value at POR and BOR/Value at all other Resets |         |         |         |  |

| '1' = Bit is set |                                    | '0' = Bit is clea | ared    |                                                       |         |         |         |  |

### REGISTER 17-4: IOCCP: INTERRUPT-ON-CHANGE PORTC POSITIVE EDGE REGISTER<sup>(1)</sup>

bit 7-6 Unimplemented: read as '0'

bit 5-0 **IOCCP<5:0>:** Interrupt-on-Change PORTC Positive Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a positive-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

**Note 1:** Present only in PIC16(L)F15323.

#### REGISTER 17-5: IOCCN: INTERRUPT-ON-CHANGE PORTC NEGATIVE EDGE REGISTER<sup>(1)</sup>

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| —     | —   | IOCCN5  | IOCCN4  | IOCCN3  | IOCCN2  | IOCCN1  | IOCCN0  |

| bit 7 |     |         |         |         |         |         | bit 0   |

|       |     |         |         |         |         |         |         |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 5-0

IOCCN<5:0>: Interrupt-on-Change PORTC Negative Edge Enable bits

- 1 = Interrupt-on-Change enabled on the pin for a negative-going edge. IOCCFx bit and IOCIF flag will be set upon detecting an edge.

- 0 = Interrupt-on-Change disabled for the associated pin

**Note 1:** Present only in PIC16(L)F15323.

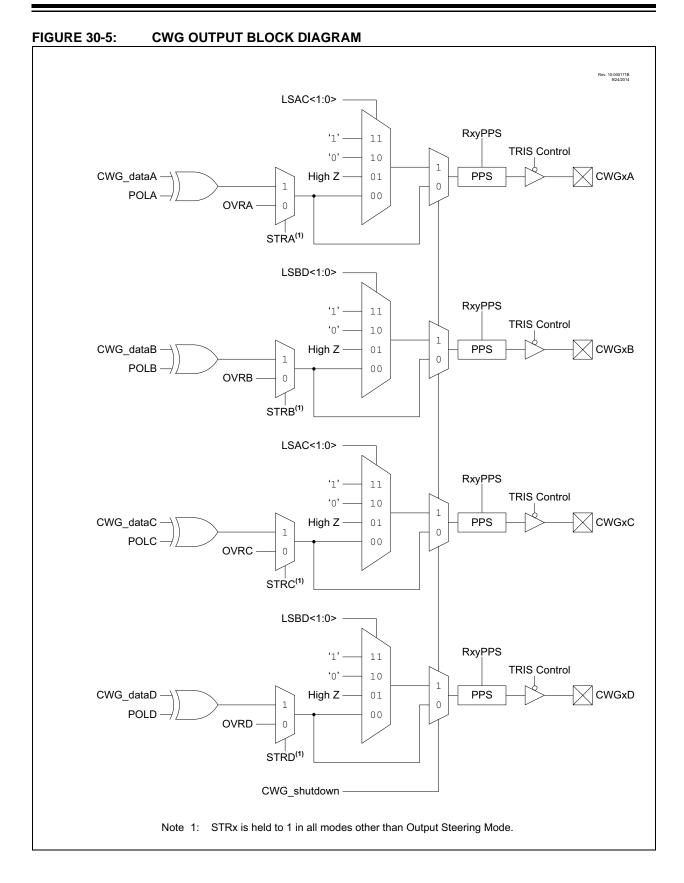

| R/W/HS-0/0                 | R/W-0/0                                | R/W-0/0                        | R/W-1/1         | R/W-0/0                   | R/W-1/1         | U-0             | U-0            |

|----------------------------|----------------------------------------|--------------------------------|-----------------|---------------------------|-----------------|-----------------|----------------|

| SHUTDOWN <sup>(1, 2)</sup> | REN                                    | LSBE                           | )<1:0>          | LSAC                      | <1:0>           | _               | _              |

| bit 7                      |                                        |                                |                 |                           |                 |                 | bit 0          |

|                            |                                        |                                |                 |                           |                 |                 |                |

| Legend:                    |                                        |                                |                 |                           |                 |                 |                |

| HC = Bit is cleared        | by hardware                            |                                |                 | HS = Bit is se            | et by hardware  |                 |                |

| R = Readable bit           |                                        | W = Writable                   | e bit           | U = Unimplei              | mented bit, rea | d as '0'        |                |

| u = Bit is unchange        | ed                                     | x = Bit is unk                 | nown            | -n/n = Value a            | at POR and BC   | R/Value at al   | l other Resets |

| '1' = Bit is set           |                                        | '0' = Bit is cle               | eared           | q = Value de              | pends on condi  | ition           |                |

| L:1 7                      |                                        |                                | Event Ote       | 4                         |                 |                 |                |

| bit 7                      |                                        | I: Auto-Shutdo                 |                 | tus bit <sup>(1, 2)</sup> |                 |                 |                |

|                            |                                        | -Shutdown sta<br>-shutdown eve |                 | be                        |                 |                 |                |

| bit 6                      |                                        | estart Enable                  |                 | cu                        |                 |                 |                |

|                            | 1 = Auto-res                           |                                | DIL             |                           |                 |                 |                |

|                            | 0 = Auto-res                           |                                |                 |                           |                 |                 |                |

| bit 5-4                    | LSBD<1:0>:                             | CWG1B and                      | CWG1D Auto      | -Shutdown Sta             | te Control bits |                 |                |

|                            | 11 <b>=A logic</b> '                   | 1' is placed or                | n CWG1B/D w     | hen an auto-sh            | nutdown event i | is present      |                |

|                            |                                        |                                |                 | hen an auto-sh            |                 |                 |                |

|                            |                                        |                                |                 | an auto-shutdo            |                 |                 |                |

|                            | band in                                |                                | e pin, includin | g polarity, is pla        | iced on CWG II  | B/D after the r | equired dead-  |

| bit 3-2                    |                                        |                                | CWG1C Auto      | -Shutdown Sta             | te Control hits |                 |                |

|                            |                                        |                                |                 | hen an auto-sh            |                 | is present      |                |

|                            |                                        |                                |                 | hen an auto-sh            |                 |                 |                |

|                            |                                        |                                |                 | an auto-shutdo            |                 |                 |                |

|                            | 00 =The inac<br>band in                |                                | e pin, includin | g polarity, is pla        | iced on CWG1/   | A/C after the r | equired dead-  |

| bit 1-0                    | Unimplemen                             | nted: Read as                  | · '0'           |                           |                 |                 |                |

| Note 1: This b<br>configu  | it may be wri <sup>.</sup><br>uration. | tten while EN                  | = 0 (CWG1       | CON0 register             | ) to place the  | outputs into    | the shutdown   |

|                            |                                        |                                |                 |                           |                 |                 | e              |

### REGISTER 30-5: CWG1AS0: CWG1 AUTO-SHUTDOWN CONTROL REGISTER 0

2: The outputs will remain in auto-shutdown state until the next rising edge of the input signal after this bit is cleared.

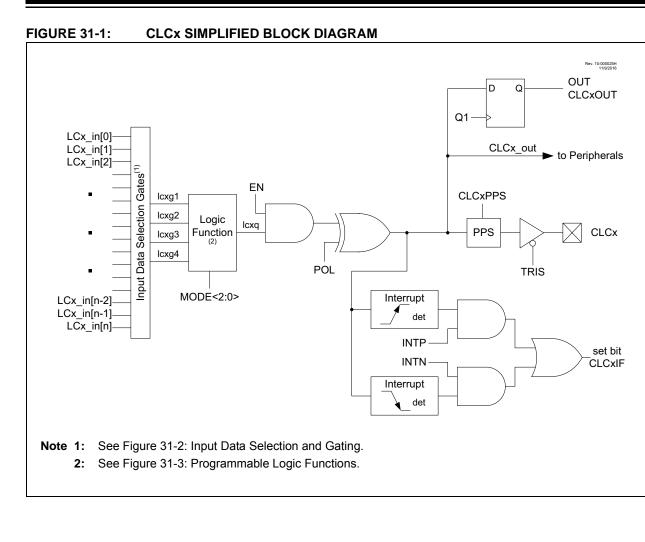

| R/W-x/u          | R/W-x/u      | R/W-x/u                                | R/W-x/u         | R/W-x/u        | R/W-x/u          | R/W-x/u          | R/W-x/u     |

|------------------|--------------|----------------------------------------|-----------------|----------------|------------------|------------------|-------------|

| LCxG4D4T         | LCxG4D4N     | LCxG4D3T                               | LCxG4D3N        | LCxG4D2T       | LCxG4D2N         | LCxG4D1T         | LCxG4D1N    |

| bit 7            |              |                                        |                 |                |                  |                  | bit C       |

|                  |              |                                        |                 |                |                  |                  |             |

| Legend:          |              |                                        |                 |                |                  |                  |             |

| R = Readable     | bit          | W = Writable                           | bit             | U = Unimpler   | nented bit, read | as '0'           |             |

| u = Bit is unch  | anged        | x = Bit is unknown                     |                 | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |              | '0' = Bit is clea                      | ared            |                |                  |                  |             |

|                  |              |                                        |                 |                |                  |                  |             |

| bit 7            |              | Gate 3 Data 4 T                        |                 |                |                  |                  |             |

|                  |              | (true) is gated i<br>(true) is not gat |                 |                |                  |                  |             |

| bit 6            |              | Gate 3 Data 4 I                        |                 |                |                  |                  |             |

|                  |              | (inverted) is ga                       | •               | ,              |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

| bit 5            |              | Sate 3 Data 3 T                        | •               |                |                  |                  |             |

|                  |              | (true) is gated i                      | ,               |                |                  |                  |             |

|                  | 0 = CLCIN2 ( | (true) is not gat                      | ted into CLCx   | Gate 3         |                  |                  |             |

| bit 4            | LCxG4D3N:    | Gate 3 Data 3 I                        | Negated (inver  | rted) bit      |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

|                  |              | (inverted) is no                       | 0               |                |                  |                  |             |

| bit 3            |              | Gate 3 Data 2 T                        |                 | ,              |                  |                  |             |

|                  |              | (true) is gated i<br>(true) is not gat |                 |                |                  |                  |             |

| bit 2            |              | Gate 3 Data 2 I                        |                 |                |                  |                  |             |

|                  |              | (inverted) is ga                       | •               |                |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

| bit 1            |              | Sate 4 Data 1 T                        |                 |                |                  |                  |             |

|                  |              | (true) is gated i                      |                 |                |                  |                  |             |

|                  | 0 = CLCIN0   | (true) is not gat                      | ted into CLCx   | Gate 3         |                  |                  |             |

| bit 0            | LCxG4D1N:    | Gate 3 Data 1 I                        | Negated (inver  | rted) bit      |                  |                  |             |

|                  |              | (inverted) is ga                       |                 |                |                  |                  |             |

|                  | 0 = CLCIN0   | (inverted) is no                       | t gated into CL | _Cx Gate 3     |                  |                  |             |

### REGISTER 31-10: CLCxGLS3: GATE 3 LOGIC SELECT REGISTER

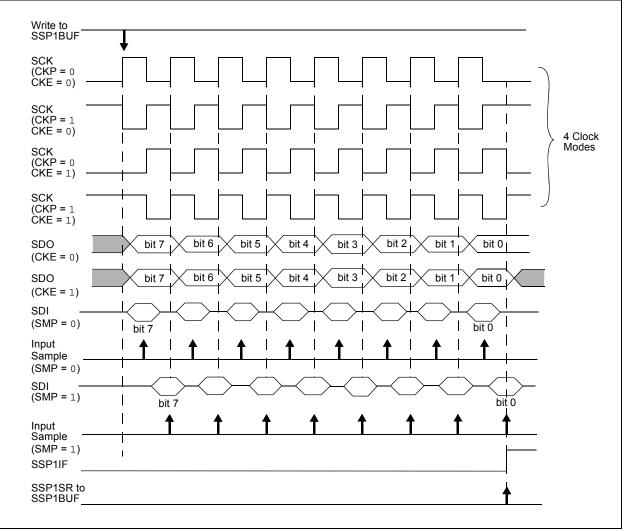

#### 32.2.3 SPI MASTER MODE

The master can initiate the data transfer at any time because it controls the SCK line. The master determines when the slave (Processor 2, Figure 32-5) is to broadcast data by the software protocol.

In Master mode, the data is transmitted/received as soon as the SSP1BUF register is written to. If the SPI is only going to receive, the SDO output could be disabled (programmed as an input). The SSP1SR register will continue to shift in the signal present on the SDI pin at the programmed clock rate. As each byte is received, it will be loaded into the SSP1BUF register as if a normal received byte (interrupts and Status bits appropriately set). The clock polarity is selected by appropriately programming the CKP bit of the SSP1CON1 register and the CKE bit of the SSP1STAT register. This then, would give waveforms for SPI communication as shown in Figure 32-6, Figure 32-8, Figure 32-9 and Figure 32-10, where the MSB is transmitted first. In Master mode, the SPI clock rate (bit rate) is user programmable to be one of the following:

- Fosc/4 (or Tcy)

- Fosc/16 (or 4 \* Tcy)

- Fosc/64 (or 16 \* Tcy)

- Timer2 output/2

- Fosc/(4 \* (SSP1ADD + 1))

Figure 32-6 shows the waveforms for Master mode.

When the CKE bit is set, the SDO data is valid before there is a clock edge on SCK. The change of the input sample is shown based on the state of the SMP bit. The time when the SSP1BUF is loaded with the received data is shown.

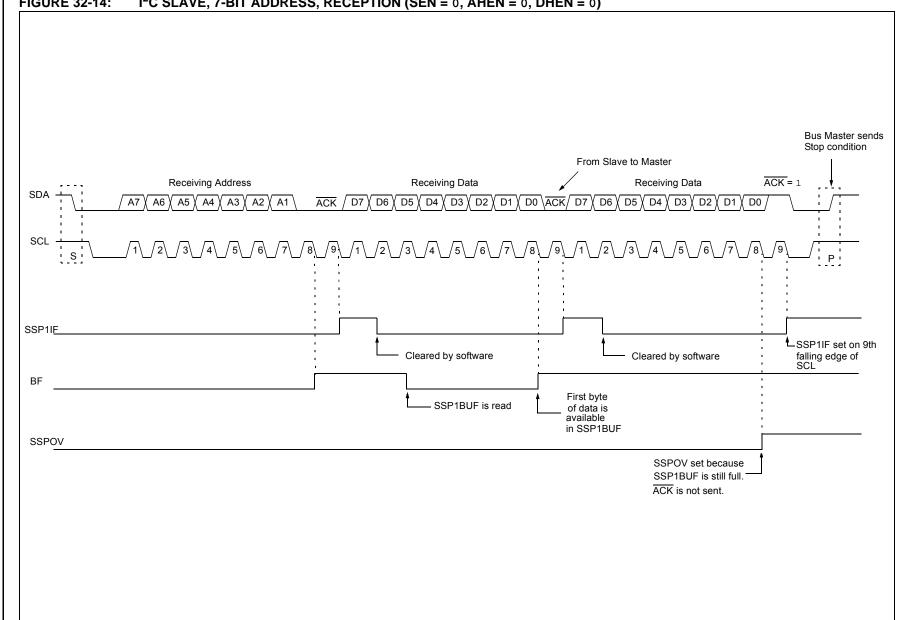

#### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 0, DHEN = 0) FIGURE 32-14:

#### 32.5.3.3 7-bit Transmission with Address Hold Enabled

Setting the AHEN bit of the SSP1CON3 register enables additional clock stretching and interrupt generation after the eighth falling edge of a received matching address. Once a matching address has been clocked in, CKP is cleared and the SSP1IF interrupt is set.

Figure 32-19 displays a standard waveform of a 7-bit address slave transmission with AHEN enabled.

- 1. Bus starts Idle.

- Master sends Start condition; the S bit of SSP1STAT is set; SSP1IF is set if interrupt on Start detect is enabled.

- Master sends matching address with R/W bit set. After the eighth falling edge of the SCL line the CKP bit is cleared and SSP1IF interrupt is generated.

- 4. Slave software clears SSP1IF.

- 5. Slave software reads ACKTIM bit of SSP1CON3 register, and  $R/\overline{W}$  and  $D/\overline{A}$  of the SSP1STAT register to determine the source of the interrupt.

- 6. Slave reads the address value from the SSP1BUF register clearing the BF bit.

- Slave software decides from this information if it wishes to ACK or not ACK and sets the ACKDT bit of the SSP1CON2 register accordingly.

- 8. Slave sets the CKP bit releasing SCL.

- 9. Master clocks in the  $\overline{ACK}$  value from the slave.

- 10. Slave hardware automatically clears the CKP bit and sets SSP1IF after the ACK if the R/W bit is set.

- 11. Slave software clears SSP1IF.

- 12. Slave loads value to transmit to the master into SSP1BUF setting the BF bit.

Note: <u>SSP1BUF</u> cannot be loaded until after the ACK.

13. Slave sets the CKP bit releasing the clock.

- 14. Master clocks out the data from the slave and sends an ACK value on the ninth SCL pulse.

- 15. Slave hardware copies the ACK value into the ACKSTAT bit of the SSP1CON2 register.

- 16. Steps 10-15 are repeated for each byte transmitted to the master from the slave.

- 17. If the master sends a not  $\overline{ACK}$  the slave releases the bus allowing the master to send a Stop and end the communication.

Note: Master must send a not ACK on the last byte to ensure that the slave releases the SCL line to receive a Stop.

| RETLW            | Return with literal in W                                                                                                                                                      |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                             |  |  |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                                  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                          |  |  |  |  |  |

| Description:     | The W register is loaded with the 8-bit<br>literal 'k'. The program counter is<br>loaded from the top of the stack (the<br>return address). This is a 2-cycle<br>instruction. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                             |  |  |  |  |  |

| Cycles:          | 2                                                                                                                                                                             |  |  |  |  |  |

| Example:         | CALL TABLE;W contains table<br>;offset value<br>• ;W now has table value                                                                                                      |  |  |  |  |  |

| TABLE            | •<br>•<br>ADDWF PC ;W = offset<br>RETLW k1 ;Begin table<br>RETLW k2 ;<br>•<br>•<br>•<br>RETLW kn ; End of table                                                               |  |  |  |  |  |

|                  | Before Instruction<br>W = 0x07                                                                                                                                                |  |  |  |  |  |

| DEIDIE    | instructio | л   |             |

|-----------|------------|-----|-------------|

|           | W =        | = ( | 0x07        |

| After Ins | struction  |     |             |

|           | W =        | = ۱ | value of k8 |

|           |            |     |             |

#### RETURN Return from Subroutine

| Syntax:          | [label] RETURN                                                                                                                                        |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operands:        | None                                                                                                                                                  |

| Operation:       | $TOS \rightarrow PC$                                                                                                                                  |

| Status Affected: | None                                                                                                                                                  |

| Description:     | Return from subroutine. The stack is<br>POPed and the top of the stack (TOS)<br>is loaded into the program counter.<br>This is a 2-cycle instruction. |

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                  | C = 0                                                                                                                                                                                                             |  |  |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |  |  |  |  |

|                  | $W = 1100 \ 1100$                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |  |  |  |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                                                                        |

| Operation:       | See description below                                                                                                                                                                                              |

| Status Affected: | С                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

© 2017 Microchip Technology Inc.

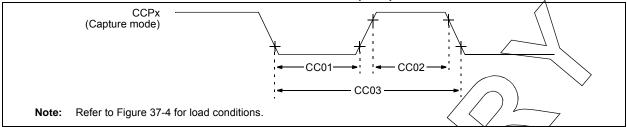

#### FIGURE 37-13: **CAPTURE/COMPARE/PWM TIMINGS (CCP)**

#### TABLE 37-19: CAPTURE/COMPARE/PWM REQUIREMENTS (CCP)

|               | Standard Operating Conditions (unless otherwise stated)      Operating Temperature    -40°C ≤ TA ≤ +125°C |                      |                |                       |                               |                          |       |                    |

|---------------|-----------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|-------------------------------|--------------------------|-------|--------------------|

| Param.<br>No. | Sym.                                                                                                      | Characteri           | stic           | Min.                  | Typt                          | Max                      | Units | Conditions         |

| CC01*         | TccL                                                                                                      | CCPx Input Low Time  | No Prescaler   | 0.5Tcy + 20           | X                             | <u> </u>                 | \ ns  |                    |

|               |                                                                                                           |                      | With Prescaler | 20/                   | -                             | $\overline{\mathcal{A}}$ | ns    |                    |

| CC02*         | TccH                                                                                                      | CCPx Input High Time | No Prescaler   | 0.5Tcy + 20           |                               | /                        | ns    |                    |

|               |                                                                                                           |                      | With Prescaler | 20                    | $\langle \mathcal{A} \rangle$ | —                        | ns    |                    |

| CC03*         | TccP                                                                                                      | CCPx Input Period    |                | <u>3Toy + 40</u><br>N |                               | > -                      | ns    | N = prescale value |

These parameters are characterized but not tested. Data in "Typ" column is at 3.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not † tested.

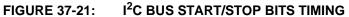

## TABLE 37-24: I<sup>2</sup>C BUS START/STOP BITS REQUIREMENTS

| Standard Operating Conditions (unless otherwise stated) |         |                 |              |      |            |      |       |                                    |  |

|---------------------------------------------------------|---------|-----------------|--------------|------|------------|------|-------|------------------------------------|--|

| Param.<br>No.                                           | Symbol  | Characteristic  |              | Min. | Тур        | Max. | Units | Conditions                         |  |

| SP90*                                                   | TSU:STA | Start condition | 100 kHz mode | 4700 | $\searrow$ | _    | ns    | Only relevant for Repeated Start   |  |

|                                                         |         | Setup time      | 400 kHz mode | 600  | _          | _    |       | condition                          |  |

| SP91*                                                   | THD:STA | Start condition | 100 kHzmode  | 4000 | _          | _    | ns    | After this period, the first clock |  |

|                                                         |         | Hold time       | 400 kHz modę | 600  | —          | _    |       | pulse is generated                 |  |

| SP92*                                                   | TSU:STO | Stop condition  | 100 kHz mode | 4700 | _          | _    | ns    |                                    |  |

|                                                         |         | Setup time      | 400 kHz mode | 600  | _          | _    |       |                                    |  |

| SP93                                                    | THD:STO | Stop condition  | 100 kHz mode | 4000 | _          | _    | ns    |                                    |  |

|                                                         |         | Hold time       | 400 kHz mode | 600  | _          |      |       |                                    |  |

\* These parameters are characterized but not tested.

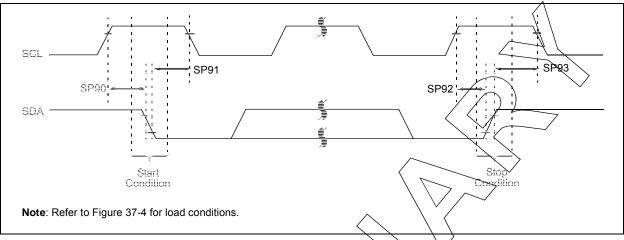

## FIGURE 37-22: /I<sup>2</sup>C BUS DATA TIMING

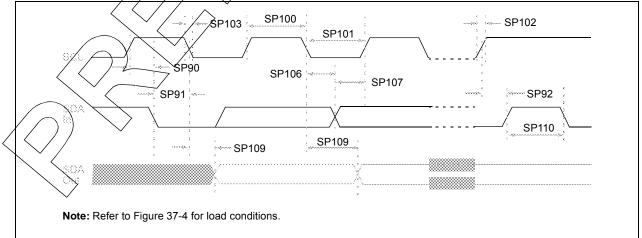

### 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-257A Sheet 1 of 2

## **Worldwide Sales and Service**

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://www.microchip.com/ support Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

**Chicago** Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453 Tel: 317-536-2380

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608 Tel: 951-273-7800

Raleigh, NC Tel: 919-844-7510

New York, NY Tel: 631-435-6000

San Jose, CA Tel: 408-735-9110 Tel: 408-436-4270

Canada - Toronto Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

Hong Kong Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Dongguan Tel: 86-769-8702-9880

China - Guangzhou Tel: 86-20-8755-8029

**China - Hangzhou** Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

**China - Hong Kong SAR** Tel: 852-2943-5100 Fax: 852-2401-3431

China - Nanjing Tel: 86-25-8473-2460 Fax: 86-25-8473-2470

**China - Qingdao** Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-3326-8000 Fax: 86-21-3326-8021

China - Shenyang Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

China - Xiamen Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-3019-1500

Japan - Osaka Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

**Japan - Tokyo** Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

**Singapore** Tel: 65-6334-8870 Fax: 65-6334-8850

**Taiwan - Hsin Chu** Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung Tel: 886-7-213-7830 Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

**Denmark - Copenhagen** Tel: 45-4450-2828 Fax: 45-4485-2829

Finland - Espoo Tel: 358-9-4520-820

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

France - Saint Cloud Tel: 33-1-30-60-70-00

**Germany - Garching** Tel: 49-8931-9700 **Germany - Haan** Tel: 49-2129-3766400

**Germany - Heilbronn** Tel: 49-7131-67-3636

Germany - Karlsruhe Tel: 49-721-625370

Germany - Munich Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Rosenheim** Tel: 49-8031-354-560

Israel - Ra'anana Tel: 972-9-744-7705

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Padova Tel: 39-049-7625286

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

Norway - Trondheim Tel: 47-7289-7561

Poland - Warsaw Tel: 48-22-3325737

Romania - Bucharest Tel: 40-21-407-87-50

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Gothenberg Tel: 46-31-704-60-40

Sweden - Stockholm Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820