Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Betans                     |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 6                                                                            |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-VDFN Exposed Pad                                                           |

| Supplier Device Package    | 8-DFN (3x3)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15313t-i-rf |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADLL -      | -10. SI LOI                                     | ALTONCTION                                                                                              | IN EQUOTEIN                   |  | DANKS 0- | 03 (0014111 |  |                       |                            |           |           |

|--------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------------------------------|--|----------|-------------|--|-----------------------|----------------------------|-----------|-----------|

| Address      | Name                                            | Bit 7         Bit 6         Bit 5         Bit 4         Bit 3         Bit 2         Bit 1         Bit 0 |                               |  |          |             |  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |           |           |

| Bank 1       |                                                 |                                                                                                         |                               |  |          |             |  |                       |                            |           |           |

|              | CPU CORE REGISTERS; see Table 4-3 for specifics |                                                                                                         |                               |  |          |             |  |                       |                            |           |           |

| 08Ch<br>09Ah | _                                               |                                                                                                         | Unimplemented                 |  |          |             |  |                       |                            |           | —         |

| 09Bh         | ADRESL                                          | ADC Result Register I                                                                                   | LOW                           |  |          |             |  |                       |                            | XXXX XXXX | uuuu uuuu |

| 09Ch         | ADRESH                                          | ADC Result Register H                                                                                   | High                          |  |          |             |  |                       |                            | XXXX XXXX | uuuu uuuu |

| 09Dh         | ADCON0                                          |                                                                                                         | CHS<5:0> GO/DONE ADON         |  |          |             |  |                       |                            | 0000 0000 | 0000 0000 |

| 09Eh         | ADCON1                                          | ADFM                                                                                                    | DFM ADCS<2:0> — — ADPREF<1:0> |  |          |             |  |                       | 000000                     | 000000    |           |

| 09Fh         | ADACT                                           | _                                                                                                       | — — — ADACT<4:0>              |  |          |             |  |                       |                            | 0 0000    | 0 0000    |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address | Name                                        | Bit 7                                | Bit 6             | Bit 5 | Bit 4         | Bit 3             | Bit 2     | Bit 1    | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|---------------------------------------------|--------------------------------------|-------------------|-------|---------------|-------------------|-----------|----------|-------|-----------------------|----------------------------|

| Bank 6  |                                             |                                      |                   |       |               |                   |           |          |       |                       |                            |

|         |                                             |                                      |                   |       |               | see Table 4-3 for | specifics |          |       |                       |                            |

|         |                                             |                                      |                   |       | CE REGIOTERO, |                   | specifics |          |       |                       |                            |

| 30Ch    | CCPR1L Capture/Compare/PWM Register 1 (LSB) |                                      |                   |       |               |                   |           |          |       | xxxx xxxx             | սսսս սսսս                  |

| 30Dh    | CCPR1H                                      | Capture/Compare/PWM Register 1 (MSB) |                   |       |               |                   |           |          |       |                       | սսսս սսսս                  |

| 30Eh    | CCP1CON                                     | EN                                   | —                 | OUT   | FMT           |                   | МО        | DE<3:0>  |       | 0-00 0000             | 0-00 0000                  |

| 30Fh    | CCP1CAP                                     | —                                    | —                 | —     | —             | —                 |           | CTS<2:0> |       | 000                   | 000                        |

| 310h    | CCPR2L                                      | Capture/Compare/P\                   | NM Register 2 (LS | SB)   |               |                   |           |          |       | xxxx xxxx             | սսսս սսսս                  |

| 311h    | CCPR2H                                      | Capture/Compare/P\                   | NM Register 2 (M  | SB)   |               |                   |           |          |       | xxxx xxxx             | սսսս սսսս                  |

| 312h    | CCP2CON                                     | EN                                   | —                 | OUT   | FMT           | MODE<3:0>         |           |          |       | 0-00 0000             | 0-00 0000                  |

| 313h    | CCP2CAP                                     | —                                    | —                 | —     | —             | —                 |           | CTS<2:0> |       | 000                   | 000                        |

| 314h    | PWM3DCL                                     | DC<1:                                | 0>                | —     | —             | —                 | —         | —        | _     | xx                    | uu                         |

| 315h    | PWM3DCH                                     |                                      |                   |       | DC<           | 9:0>              |           |          |       | xxxx xxxx             | uuuu uuuu                  |

| 316h    | PWM3CON                                     | EN                                   | —                 | OUT   | POL           | —                 | —         | —        | —     | 0-00                  | 0-00                       |

| 317h    | —                                           |                                      |                   |       | Unimple       | mented            |           |          |       | —                     | —                          |

| 318h    | PWM4DCL                                     | DC<1:                                | 0>                | —     | —             | —                 | —         | —        | _     | xx                    | uu                         |

| 319h    | PWM4DCH                                     |                                      |                   |       | DC<           | 9:0>              |           |          |       | xxxx xxxx             | uuuu uuuu                  |

| 31Ah    | PWM4CON                                     | EN                                   | —                 | OUT   | POL           | —                 | —         | —        | —     | 0-00                  | 0-00                       |

| 31Bh    | —                                           |                                      |                   |       | Unimple       | mented            |           |          |       | —                     | —                          |

| 31Ch    | PWM5DCL                                     | 5DCL DC<1:0> — — — — — — —           |                   |       |               |                   |           |          |       |                       | uu                         |

| 31Dh    | PWM5DCH                                     |                                      |                   |       | DC<           | 9:0>              |           |          |       | xxxx xxxx             | uuuu uuuu                  |

| 31Eh    | PWM5CON                                     | EN                                   | —                 | OUT   | POL           | —                 | -         | —        | —     | 0-00                  | 0-00                       |

| 31Fh    | —                                           |                                      |                   |       | Unimple       | mented            |           |          |       | -                     | _                          |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| Address | Name | Bit 7  | Bit 6  | Bit 5   | Bit 4         | Bit 3             | Bit 2       | Bit 1               | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|------|--------|--------|---------|---------------|-------------------|-------------|---------------------|---------|-----------------------|----------------------------|

| Bank 14 |      |        | •      |         |               |                   | •           | •                   |         |                       |                            |

|         |      |        |        | CPU COF | RE REGISTERS; | see Table 4-3 for | r specifics |                     |         |                       |                            |

| 70Ch    | PIR0 | _      | _      | TMR0IF  | IOCIF         | _                 | _           | _                   | INTE    | 000                   | 000                        |

| 70Dh    | PIR1 | OSFIF  | CSWIF  |         |               |                   | _           |                     | ADIF    | 0000                  | 000                        |

| 70Eh    | PIR2 | _      | ZCDIF  | _       | _             | _                 | _           | C2IF <sup>(1)</sup> | C1IF    | -000                  | -000                       |

| 70Fh    | PIR3 | _      | _      | RC1IF   | TX1IF         | _                 | _           | BCL1IF              | SSP1IF  | 0000                  | 000                        |

| 710h    | PIR4 | _      | _      | —       | _             | _                 | _           | TMR2IF              | TMR1IF  | 00                    | 0                          |

| 711h    | PIR5 | CLC4IF | CLC3IF | CLC2IF  | CLC1IF        | _                 | _           | -                   | TMR1GIF | 00000                 | 0000                       |

| 712h    | PIR6 | _      | _      | _       | _             | _                 | _           | CCP2IF              | CCP1IF  | 00                    | 0                          |

| 713h    | PIR7 | _      | —      | NVMIF   | NCO1IF        | —                 | —           | —                   | CWG1IF  | 000                   | 00                         |

| 714h    | _    |        |        |         | Unimple       | mented            |             |                     |         | -                     | —                          |

| 715h    | —    |        |        |         | Unimple       | mented            |             |                     |         | —                     | —                          |

| 716h    | PIE0 | —      | —      | TMR0IE  | IOCIE         | —                 | —           | —                   | INTE    | 000                   | 00                         |

| 717h    | PIE1 | OSFIE  | CSWIE  | —       | —             | —                 | —           | —                   | ADIE    | 0000                  | 0000                       |

| 718h    | PIE2 | —      | ZCDIE  | —       | —             | —                 | —           | C2IE <sup>(1)</sup> | C1IE    | -000                  | -00                        |

| 719h    | PIE3 | —      | _      | RC1IE   | TX1IE         | _                 | _           | BCL1IE              | SSP1IE  | 0000                  | 000                        |

| 71Ah    | PIE4 | _      | _      | _       | _             | _                 | _           | TMR2IE              | TMR1IE  | 00                    | 0                          |

| 71Bh    | PIE5 | CLC4IE | CLC3IE | CLC2IE  | CLC1IE        | _                 | —           | —                   | TMR1GIE | 00000                 | 0000                       |

| 71Ch    | PIE6 | —      | —      | _       | _             | _                 |             | CCP2IE              | CCP1IE  | 00                    | 0                          |

| 71Dh    | PIE7 | _      | —      | NVMIE   | NCO1IE        | —                 | —           | _                   | CWG1IE  | 000                   | 00                         |

| 71Eh    | —    |        |        |         | Unimple       | mented            |             |                     |         | —                     | _                          |

| 71Fh    | —    |        |        |         | Unimple       | mented            |             |                     |         | -                     | _                          |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Present only on PIC16(L)F15323.

| Address           | Name                                            | Bit 7 | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0     Value on:<br>POR, BOR     Value on:<br>MCLR |  |  |  |  |  |  |  | V <u>alue o</u> n:<br>MCLR |

|-------------------|-------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|----------------------------|

| Bank 21-59        | 9                                               |       |                                                                                                                             |  |  |  |  |  |  |  |                            |

|                   | CPU CORE REGISTERS; see Table 4-3 for specifics |       |                                                                                                                             |  |  |  |  |  |  |  |                            |

| x0Ch/<br>x8Ch<br> | <pre>k8Ch Unimplemented</pre>                   |       |                                                                                                                             |  |  |  |  |  |  |  |                            |

| Legend:           |                                                 |       |                                                                                                                             |  |  |  |  |  |  |  |                            |

# PIC16(L)F15313/23

| IRE 4-5:          | ACCI |                  | -                                                                                                            |                                                                                                          |                                                                                                                                                                                                                      |

|-------------------|------|------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   |      |                  |                                                                                                              |                                                                                                          | Rev. 10-000438<br>7/30/2013                                                                                                                                                                                          |

|                   |      |                  |                                                                                                              |                                                                                                          |                                                                                                                                                                                                                      |

|                   |      |                  | 0x0F                                                                                                         |                                                                                                          | ]                                                                                                                                                                                                                    |

|                   |      |                  | 0x0F                                                                                                         |                                                                                                          | -                                                                                                                                                                                                                    |

|                   |      |                  | 0x0L                                                                                                         |                                                                                                          | -                                                                                                                                                                                                                    |

|                   |      |                  | 0x0C                                                                                                         |                                                                                                          | -                                                                                                                                                                                                                    |

|                   |      |                  | 0x0C                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   |      |                  | 0x0A                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   |      |                  | 0x09                                                                                                         |                                                                                                          | This figure shows the stack configuration                                                                                                                                                                            |

|                   |      |                  | 0x08                                                                                                         |                                                                                                          | after the first CALL or a single interrupt.                                                                                                                                                                          |

|                   |      |                  | 0x07                                                                                                         |                                                                                                          | If a RETURN instruction is executed, the return address will be placed in the                                                                                                                                        |

|                   |      |                  | 0x06                                                                                                         |                                                                                                          | Program Counter and the Stack Pointer decremented to the empty state (0x1F).                                                                                                                                         |

|                   |      |                  | 0x05                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   |      |                  | 0x04                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   |      |                  | 0x03                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   |      |                  | 0x02                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   |      | 4                | 0x01                                                                                                         |                                                                                                          |                                                                                                                                                                                                                      |

|                   | TOSL |                  | 0x00                                                                                                         | Return Address                                                                                           | STKPTR = 0x00                                                                                                                                                                                                        |

| тозн:<br>IRE 4-6: | ACCI | ESSING TH        | IE STA                                                                                                       | CK EXAMPLE :                                                                                             | 3                                                                                                                                                                                                                    |

|                   | ACCI | ESSING TH        | IE STA                                                                                                       | CK EXAMPLE :                                                                                             | 3<br>Rev: 10-00043C<br>7/9/2013                                                                                                                                                                                      |

|                   | ACCI | ESSING TH        | IE STA                                                                                                       | CK EXAMPLE :                                                                                             |                                                                                                                                                                                                                      |

|                   | ACCI | ESSING TH        | IE STA                                                                                                       | CK EXAMPLE :                                                                                             |                                                                                                                                                                                                                      |

|                   | ACCI | ESSING TH        |                                                                                                              | CK EXAMPLE :                                                                                             |                                                                                                                                                                                                                      |

|                   | ACCI | ESSING TH        | 0x0F                                                                                                         | CK EXAMPLE :                                                                                             |                                                                                                                                                                                                                      |

|                   | ACCI | ESSING TH        | 0x0F<br>0x0E                                                                                                 | CK EXAMPLE :                                                                                             |                                                                                                                                                                                                                      |

|                   | ACCI | ESSING TH        | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B                                                                         | CK EXAMPLE :                                                                                             | After seven CALLs or six CALLs and an interrupt, the stack looks like the figure on                                                                                                                                  |

|                   | ACCI | ESSING TH        | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A                                                                 | CK EXAMPLE :                                                                                             | After seven CALLs or six CALLs and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into                                        |

|                   | ACCI | ESSING TH        | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x0A                                                         |                                                                                                          | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will                                                                                   |

|                   | ACCI | ESSING TH        | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0B<br>0x0A<br>0x09<br>0x08                                         |                                                                                                          | After seven CALLs or six CALLs and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into                                        |

| IRE 4-6:          |      | ESSING TH        | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07                                         |                                                                                                          | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| IRE 4-6:          | ACCI | ESSING TH        | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07                                 | Return Address                                                                                           | After seven CALLs or six CALLs and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into                                        |

| IRE 4-6:          |      | <u>ESSING TH</u> | 0x0F<br>0x0D<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05                         | Return Address<br>Return Address                                                                         | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| IRE 4-6:          |      | <u>ESSING TH</u> | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0B<br>0x08<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04         | Return Address<br>Return Address<br>Return Address                                                       | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| IRE 4-6:          |      | <u>ESSING T</u>  | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03         | Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address                   | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| IRE 4-6:          |      | <u>ESSING T</u>  | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03<br>0x02 | Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| IRE 4-6:          |      | <u>ESSING T</u>  | 0x0F<br>0x0E<br>0x0D<br>0x0C<br>0x0B<br>0x0A<br>0x09<br>0x08<br>0x07<br>0x06<br>0x05<br>0x04<br>0x03         | Return Address<br>Return Address<br>Return Address<br>Return Address<br>Return Address                   | After seven CALLS or six CALLS and an interrupt, the stack looks like the figure on the left. A series of RETURN instructions will repeatedly place the return addresses into the Program Counter and pop the stack. |

| INPUT SIGNAL | Innut Desister Norma | Default Location | Reset Value   | Remappable to Pins of<br>PORTx |  |  |

|--------------|----------------------|------------------|---------------|--------------------------------|--|--|

| NAME         | Input Register Name  | at POR           | (xxxPPS<4:0>) | PIC16(L)F15313                 |  |  |

|              |                      |                  |               | PORTA                          |  |  |

| INT          | INTPPS               | RA2              | 00010         | •                              |  |  |

| TOCKI        | T0CKIPPS             | RA2              | 00010         | •                              |  |  |

| T1CKI        | T1CKIPSS             | RA5              | 00101         | •                              |  |  |

| T1G          | T1GPPS               | RA4              | 00100         | •                              |  |  |

| T2IN         | T2INPPS              | RA5              | 00101         | •                              |  |  |

| CCP1         | CCP1PPS              | RA5              | 00101         | •                              |  |  |

| CCP2         | CCP2PPS              | RA5              | 00101         | •                              |  |  |

| CWG1IN       | CWG1INPPS            | RA2              | 00010         | •                              |  |  |

| CLCIN0       | CLCIN0PPS            | RA3              | 00011         | •                              |  |  |

| CLCIN1       | CLCIN1PPS            | RA5              | 00101         | •                              |  |  |

| CLCIN2       | CLCIN2PPS            | RA1              | 00001         | •                              |  |  |

| CLCIN3       | CLCIN3PPS            | RA0              | 00000         | •                              |  |  |

| ADACT        | ADACTPPS             | RA5              | 00101         | •                              |  |  |

| SCK1/SCL1    | SSP1CLKPPS           | RA1              | 00001         | •                              |  |  |

| SDI1/SDA1    | SSP1DATPPS           | RA2              | 00010         | •                              |  |  |

| SS1          | SSP1SS1PPS           | RA3              | 00011         | •                              |  |  |

| RX1/DT1      | RX1PPS               | RA1              | 00001         | •                              |  |  |

| CK1          | TX1PPS               | RA0              | 00000         | •                              |  |  |

## TABLE 15-1: PPS INPUT SIGNAL ROUTING OPTIONS (PIC16(L)F15313)

### 15.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- The I<sup>2</sup>C SCLx and SDAx functions can be Note: remapped through PPS. However, only the RB1, RB2, RC3 and RC4 pins have the I<sup>2</sup>C and SMBus specific input buffers implemented (I<sup>2</sup>C mode disables INLVL and sets thresholds that are specific for  $I^2C$ ). If the SCLx or SDAx functions are mapped to some other pin (other than RB1, RB2, RC3 or RC4), the general purpose TTL or ST input buffers (as configured based on INLVL register setting) will be used instead. In most applications, it is therefore recommended only to map the SCLx and SDAx pin functions to the RB1, RB2, RC3 or RC4 pins.

## 15.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 15-1.

#### EXAMPLE 15-1: PPS LOCK/UNLOCK SEQUENCE

| ; | suspend interrupts                     |

|---|----------------------------------------|

|   | BCF INTCON, GIE                        |

| ; | BANKSEL PPSLOCK ; set bank             |

| ; | required sequence, next 5 instructions |

|   | MOVLW 0x55                             |

|   | MOVWF PPSLOCK                          |

|   | MOVLW 0xAA                             |

|   | MOVWF PPSLOCK                          |

| ; | Set PPSLOCKED bit to disable writes or |

| ; | Clear PPSLOCKED bit to enable writes   |

|   | BSF PPSLOCK, PPSLOCKED                 |

| ; | restore interrupts                     |

|   | BSF INTCON, GIE                        |

## 15.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

# 15.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

## 15.7 Effects of a Reset

A device Power-on-Reset (POR) clears all PPS input and output selections to their default values (Permanent Lock Removed). All other Resets leave the selections unchanged. Default input selections are shown in Table 15-1 and Table 15-2.

| Name | Bit 7  | Bit 6   | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on page |

|------|--------|---------|--------|---------|--------|--------|--------|--------|---------------------|

| PMD0 | SYSCMD | FVRMD   | -      | —       | -      | NVMMD  | CLKRMD | IOCMD  | 195                 |

| PMD1 | NCO1MD | —       | _      | _       | _      | TMR2MD | TMR1MD | TMR0MD | 196                 |

| PMD2 | —      | DAC1MD  | ADCMD  | _       | _      | CMP2MD | CMP1MD | ZCDMD  | 197                 |

| PMD3 | —      | —       | PWM6MD | PWM5MD  | PWM4MD | PWM3MD | CCP2MD | CCP1MD | 198                 |

| PMD4 | _      | UART1MD | _      | MSSP1MD | —      | —      | —      | CWG1MD | 199                 |

| PMD5 | —      | —       |        | CLC4MD  | CLC3MD | CLC2MD | CLC1MD |        | 200                 |

TABLE 16-1:

SUMMARY OF REGISTERS ASSOCIATED WITH THE PPS MODULE

Legend: — = unimplemented, read as '0'. Shaded cells are unused by the PPS module.

## 20.4 Register Definitions: ADC Control

## REGISTER 20-1: ADCON0: ADC CONTROL REGISTER 0

| R/W-0/0          | R/W-0/0              | R/W-0/0                                   | R/W-0/0            | R/W-0/0           | R/W-0/0             | R/W-0/0              | R/W-0/0 |

|------------------|----------------------|-------------------------------------------|--------------------|-------------------|---------------------|----------------------|---------|

|                  |                      | CHS<                                      | 5:0>               |                   |                     | GO/DONE              | ADON    |

| bit 7            |                      |                                           |                    |                   |                     |                      | bit (   |

| Legend:          |                      |                                           |                    |                   |                     |                      |         |

| R = Readable     | bit                  | W = Writable bit                          |                    | U = Unimpleme     | nted bit, read as ' | ʻ0'                  |         |

| u = Bit is unch  | anged                | x = Bit is unknow                         | vn                 | -n/n = Value at F | POR and BOR/Va      | alue at all other Re | sets    |

| '1' = Bit is set |                      | '0' = Bit is cleare                       | d                  |                   |                     |                      |         |

|                  |                      |                                           |                    |                   |                     |                      |         |

| bit 7-2          |                      | Analog Channel Sele                       | (-)                |                   |                     |                      |         |

|                  | 111111 =             | FVR Buffer 2 refere                       |                    |                   |                     |                      |         |

|                  | 111110 =<br>111101 = | FVR 1Buffer 1 refer<br>DAC1 output voltag |                    |                   |                     |                      |         |

|                  | 111101 =             | Temperature senso                         | (m)                |                   |                     |                      |         |

|                  | 1110011 =            | AVss (Analog Grou                         |                    |                   |                     |                      |         |

|                  | 010111 =             | Reserved                                  | iu)                |                   |                     |                      |         |

|                  | 010110 =             | Reserved                                  |                    |                   |                     |                      |         |

|                  | 010101 =             | RC5 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010100 =             | RC4 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010011 =             | RC3 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010010 =             | RC2 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010001 =             | RC1 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 010000 =             | RC0 <sup>(4)</sup>                        |                    |                   |                     |                      |         |

|                  | 001111 =             | Reserved                                  |                    |                   |                     |                      |         |

|                  | •                    |                                           |                    |                   |                     |                      |         |

|                  | •                    |                                           |                    |                   |                     |                      |         |

|                  | •                    |                                           |                    |                   |                     |                      |         |

|                  | 000110 =             | Reserved                                  |                    |                   |                     |                      |         |

|                  | 000101 =             | RA5 <sup>(5)</sup>                        |                    |                   |                     |                      |         |

|                  | 000100 =             | RA4 <sup>(5)</sup>                        |                    |                   |                     |                      |         |

|                  | 000011 =<br>000010 = | RA3<br>RA2                                |                    |                   |                     |                      |         |

|                  | 000010 =             | RAZ<br>RA1                                |                    |                   |                     |                      |         |

|                  | 0000001 -            | RA1<br>RA0                                |                    |                   |                     |                      |         |

| bit 1            | GO/DONE: /           | ADC Conversion Stat                       | us bit             |                   |                     |                      |         |

|                  | 1 = ADC cor          | version cycle in prog                     | ress. Setting this | bit starts an ADC | conversion cycle    |                      |         |

|                  | This bit is          | s automatically cleare                    | d by hardware w    | hen the ADC conv  | version has comp    | leted.               |         |

|                  | 0 = ADC cor          | version completed/ne                      | ot in progress     |                   |                     |                      |         |

| bit 0            | ADON: ADC            | Enable bit                                |                    |                   |                     |                      |         |

|                  | 1 = ADC is e         |                                           |                    |                   |                     |                      |         |

|                  | 0 = ADC is d         | lisabled and consume                      | es no operating o  | current           |                     |                      |         |

| Note 1: S        | ee Section 21 0      | "5-Bit Digital-to-Ana                     | alog Converter     | (DAC1) Module" f  | or more informati   | ion                  |         |

|                  |                      | "Fixed Voltage Refe                       | •                  | . ,               |                     |                      |         |

|                  |                      | "Temperature Indic                        | • •                |                   |                     |                      |         |

|                  |                      |                                           |                    |                   |                     |                      |         |

- 4: Present only on the PIC16(L)F15323.

- 5: The analog functionality on the channels RA4 and RA5 is disabled when the system clock source is an external oscillator.

| Name                  | Bit 7 | Bit 6  | Bit 5     | Bit 4                        | Bit 3   | Bit 2   | Bit 1   | Bit 0  | Register<br>on Page |

|-----------------------|-------|--------|-----------|------------------------------|---------|---------|---------|--------|---------------------|

| INTCON                | GIE   | PEIE   | _         | _                            | —       | —       | —       | INTEDG | 121                 |

| PIE1                  | OSFIE | CSWIE  | _         | _                            | —       | —       | —       | ADIE   | 123                 |

| PIR1                  | OSFIF | CSWIF  | _         | _                            | _       | _       | _       | ADIF   | 131                 |

| TRISA                 | _     | _      | TRISA5    | TRISA4                       | —       | TRISA2  | TRISA1  | TRISA0 | 175                 |

| ANSELC <sup>(1)</sup> | _     |        | ANSC5     | ANSC4                        | ANSC3   | ANSC2   | ANSC1   | ANSC0  | 182                 |

| ADCON0                |       |        | CHS<      | 5:0>                         |         |         | GO/DONE | ADON   | 223                 |

| ADCON1                | ADFM  |        | ADCS<2:0> |                              | _       | —       | ADPREF  | 224    |                     |

| ADACT                 | —     | —      | _         |                              |         | ADACT<4 | :0>     |        | 225                 |

| ADRESH                |       |        |           | ADRE                         | SH<7:0> |         |         |        | 226                 |

| ADRESL                |       |        |           | ADRE                         | SL<7:0> |         |         |        | 226                 |

| FVRCON                | FVREN | FVRRDY | TSEN      | TSRNG CDAFVR<1:0> ADFVR<1:0> |         |         |         | 210    |                     |

| DAC1CON1              | _     | —      |           | DAC1R<4:0>                   |         |         | 232     |        |                     |

| OSCSTAT1              | EXTOR | HFOR   | MFOR      | LFOR                         | SOR     | ADOR    |         | PLLR   | 112                 |

#### TABLE 20-3: SUMMARY OF REGISTERS ASSOCIATED WITH ADC

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for the ADC module.

Note 1: Present on PIC16(L)F15323PIC16(L)F15323 only.

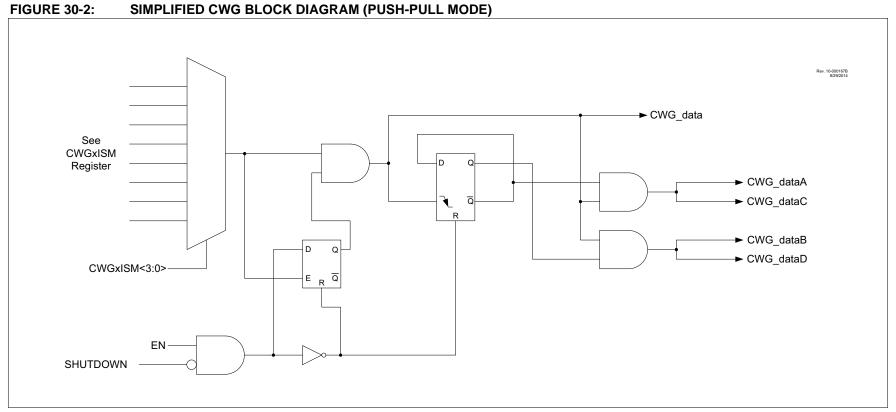

## SIMPLIFIED CWG BLOCK DIAGRAM (PUSH-PULL MODE)

PIC16(L)F15313/23

#### **30.3 Selectable Input Sources**

The CWG generates the output waveforms from the input sources in Table 30-2.

#### TABLE 30-2: SELECTABLE INPUT SOURCES

| Source Peripheral | Signal Name |

|-------------------|-------------|

| CWG input PPS pin | CWG1IN PPS  |

| CCP1              | CCP1_out    |

| CCP2              | CCP2_out    |

| PWM3              | PWM3_out    |

| PWM4              | PWM4_out    |

| PWM5              | PWM5_out    |

| PWM6              | PWM6_out    |

| NCO               | NCO1_out    |

| Comparator C1     | C1OUT_sync  |

| Comparator C2     | C2OUT_sync  |

| CLC1              | LC1_out     |

| CLC2              | LC2_out     |

| CLC3              | LC3_out     |

| CLC4              | LC4_out     |

The input sources are selected using the CWG1ISM register.

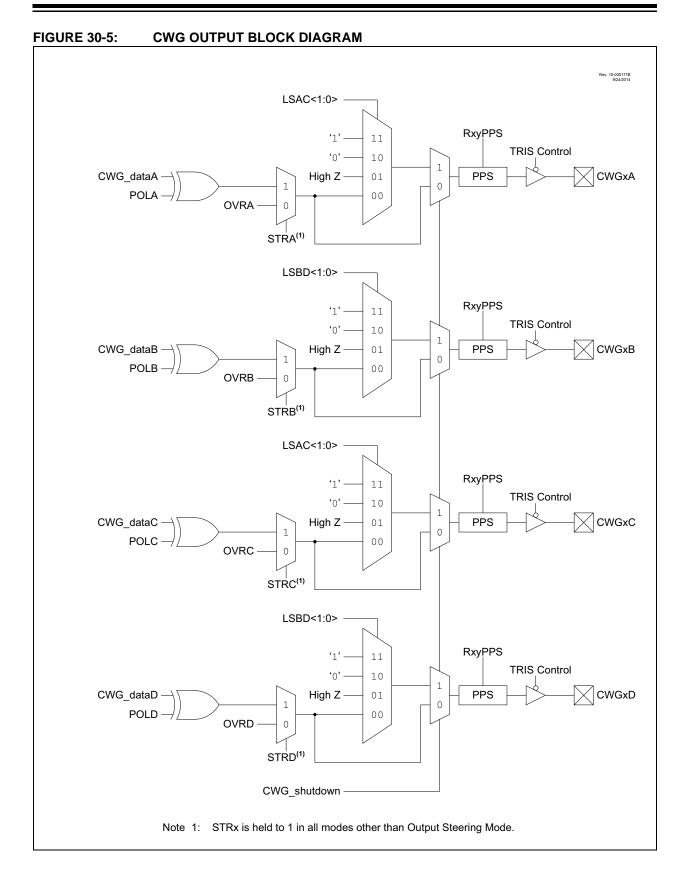

### 30.4 Output Control

#### 30.4.1 POLARITY CONTROL

The polarity of each CWG output can be selected independently. When the output polarity bit is set, the corresponding output is active-high. Clearing the output polarity bit configures the corresponding output as active-low. However, polarity does not affect the override levels. Output polarity is selected with the POLx bits of the CWG1CON1. Auto-shutdown and steering options are unaffected by polarity.

# PIC16(L)F15313/23

#### TABLE 30-3:SUMMARY OF REGISTERS ASSOCIATED WITH CWG

| Name       | Bit 7    | Bit 6 | Bit 5           | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Register<br>on Page |

|------------|----------|-------|-----------------|-------|-------|-------|-------|-------|---------------------|

| CWG1CLKCON | -        | _     | -               | _     | _     | -     | -     | CS    | 341                 |

| CWG1ISM    | _        | _     | _               | _     |       | 341   |       |       |                     |

| CWG1DBR    | _        | _     | DBR<5:0>        |       |       |       |       |       | 337                 |

| CWG1DBF    | _        | _     | DBF<5:0>        |       |       |       |       |       | 337                 |

| CWG1CON0   | EN       | LD    | — — — MODE<2:0> |       |       |       |       | 340   |                     |

| CWG1CON1   | _        | _     | IN              | _     | POLD  | POLC  | POLB  | POLA  | 336                 |

| CWG1AS0    | SHUTDOWN | REN   | LSBD<1:0>       |       | LSAC  | <1:0> | —     | _     | 338                 |

| CWG1AS1    | _        | _     | _               | AS4E  | AS3E  | AS2E  | AS1E  | AS0E  | 339                 |

| CWG1STR    | OVRD     | OVRC  | OVRB            | OVRA  | STRD  | STRC  | STRB  | STRA  | 340                 |

Legend: -= unimplemented locations read as '0'. Shaded cells are not used by CWG.

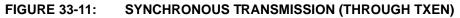

## 33.4 EUSART Synchronous Mode

Synchronous serial communications are typically used in systems with a single master and one or more slaves. The master device contains the necessary circuitry for baud rate generation and supplies the clock for all devices in the system. Slave devices can take advantage of the master clock by eliminating the internal clock generation circuitry.

There are two signal lines in Synchronous mode: a bidirectional data line and a clock line. Slaves use the external clock supplied by the master to shift the serial data into and out of their respective receive and transmit shift registers. Since the data line is bidirectional, synchronous operation is half-duplex only. Half-duplex refers to the fact that master and slave devices can receive and transmit data but not both simultaneously. The EUSART can operate as either a master or slave device.

Start and Stop bits are not used in synchronous transmissions.

#### 33.4.1 SYNCHRONOUS MASTER MODE

The following bits are used to configure the EUSART for synchronous master operation:

- SYNC = 1

- CSRC = 1

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TX1STA register configures the device for synchronous operation. Setting the CSRC bit of the TX1STA register configures the device as a master. Clearing the SREN and CREN bits of the RC1STA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RC1STA register enables the EUSART.

#### 33.4.1.1 Master Clock

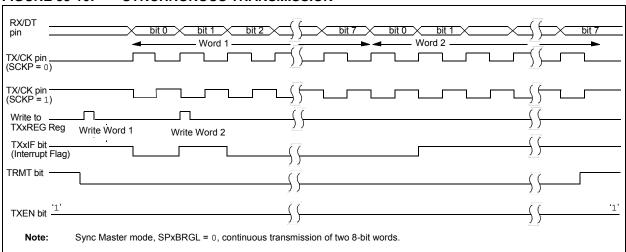

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a master transmits the clock on the TX/CK line. The TX/CK pin output driver is automatically enabled when the EUSART is configured for synchronous transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One clock cycle is generated for each data bit. Only as many clock cycles are generated as there are data bits.

### 33.4.1.2 Clock Polarity

A clock polarity option is provided for Microwire compatibility. Clock polarity is selected with the SCKP bit of the BAUD1CON register. Setting the SCKP bit sets the clock Idle state as high. When the SCKP bit is set, the data changes on the falling edge of each clock. Clearing the SCKP bit sets the Idle state as low. When the SCKP bit is cleared, the data changes on the rising edge of each clock.

#### 33.4.1.3 Synchronous Master Transmission

Data is transferred out of the device on the RX/DT pin. The RX/DT and TX/CK pin output drivers are automatically enabled when the EUSART is configured for synchronous master transmit operation.

A transmission is initiated by writing a character to the TX1REG register. If the TSR still contains all or part of a previous character the new character data is held in the TX1REG until the last bit of the previous character has been transmitted. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TX1REG is immediately transferred to the TSR. The transmission of the character commences immediately following the transfer of the data to the TSR from the TX1REG.

Each data bit changes on the leading edge of the master clock and remains valid until the subsequent leading clock edge.

| Note: | The TSR register is not mapped in data      |

|-------|---------------------------------------------|

|       | memory, so it is not available to the user. |

- 33.4.1.4 Synchronous Master Transmission Set-up:

- Initialize the SP1BRGH, SP1BRGL register pair and the BRGH and BRG16 bits to achieve the desired baud rate (see Section 33.3 "EUSART Baud Rate Generator (BRG)").

- 2. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 3. Disable Receive mode by clearing bits SREN and CREN.

- 4. Enable Transmit mode by setting the TXEN bit.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. If interrupts are desired, set the TX1IE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 7. If 9-bit transmission is selected, the ninth bit should be loaded in the TX9D bit.

- 8. Start transmission by loading data to the TX1REG register.

#### FIGURE 33-10: SYNCHRONOUS TRANSMISSION

#### 33.4.1.5 Synchronous Master Reception

Data is received at the RX/DT pin. The RX/DT pin output driver is automatically disabled when the EUSART is configured for synchronous master receive operation.

In Synchronous mode, reception is enabled by setting either the Single Receive Enable bit (SREN of the RC1STA register) or the Continuous Receive Enable bit (CREN of the RC1STA register).

When SREN is set and CREN is clear, only as many clock cycles are generated as there are data bits in a single character. The SREN bit is automatically cleared at the completion of one character. When CREN is set, clocks are continuously generated until CREN is cleared. If CREN is cleared in the middle of a character the CK clock stops immediately and the partial character is discarded. If SREN and CREN are both set, then SREN is cleared at the completion of the first character and CREN takes precedence. To initiate reception, set either SREN or CREN. Data is sampled at the RX/DT pin on the trailing edge of the TX/CK clock pin and is shifted into the Receive Shift Register (RSR). When a complete character is received into the RSR, the RX1IF bit is set and the character is automatically transferred to the two character receive FIFO. The Least Significant eight bits of the top character in the receive FIFO are available in RC1REG. The RX1IF bit remains set as long as there are unread characters in the receive FIFO.

**Note:** If the RX/DT function is on an analog pin, the corresponding ANSEL bit must be cleared for the receiver to function.

# 38.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Unless otherwise noted, all graphs apply to both the L and LF devices.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum", "Max.", "Minimum" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

Charts and graphs are not available at this time.

#### **39.2 MPLAB XC Compilers**

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

#### 39.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline

assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 39.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 39.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

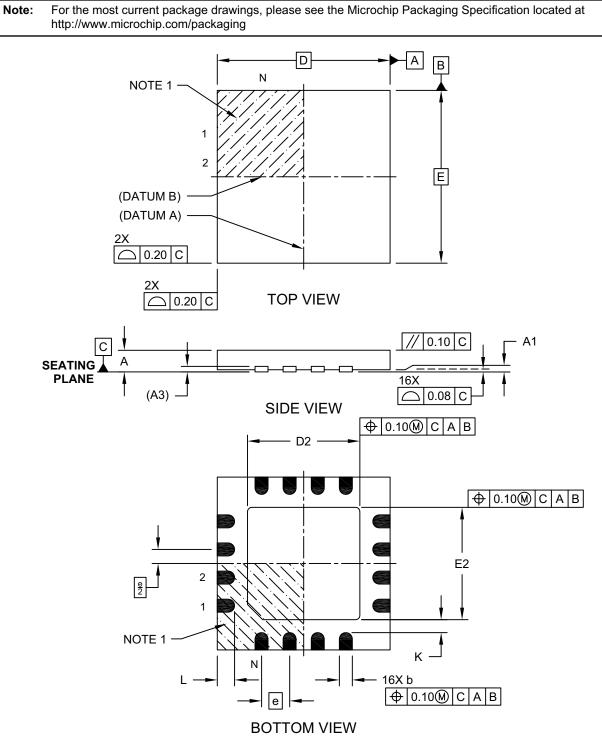

## 16-Lead Ultra Thin Plastic Quad Flat, No Lead Package (JQ) - 4x4x0.5 mm Body [UQFN]

Microchip Technology Drawing C04-257A Sheet 1 of 2

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device                  | ·                                                                                   | Emperature<br>Range                                                                                        | /XX<br>Package   | XXX<br>Pattern |     | amples<br>PIC16<br>Exten |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------|----------------|-----|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Package: <sup>(2)</sup><br>Package: | E = -40°C<br>JQ = 16-lea<br>MF = 8-leaa<br>P = 8-leaa<br>SL = 14-lea<br>SN = 8-leaa | to +125°C (I<br>ad UQFN 4x4x0.<br>I DFN 3x3mm<br>I 14-lead PDIP<br>ad SOIC<br>I SOIC<br>I SOIC<br>ad TSSOP | Extended)<br>5mm |                | Not | e 1:<br>2:               | Tape and Reel identifier only appears in<br>the catalog part number description. This<br>identifier is used for ordering purposes and<br>is not printed on the device package.<br>Check with your Microchip Sales Office<br>for package availability with the Tape and<br>Reel option.<br>Small form-factor packaging options may<br>be available. Check<br>www.microchip.com/packaging for<br>small-form factor package availability, or<br>contact your local Sales Office. |

|                                     |                                                                                     |                                                                                                            |                  |                |     |                          | contact your local sales Office.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                     |                                                                                     |                                                                                                            |                  |                |     |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |