Welcome to **E-XFL.COM**

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                    |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                        |

| Number of I/O              | 6                                                                            |

| Program Memory Size        | 3.5KB (2K x 14)                                                              |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | 224 x 8                                                                      |

| RAM Size                   | 256 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                          |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                                |

| Supplier Device Package    | 8-SOIC                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15313t-i-sn |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | Device Overview                                                           | 1              |

|------|---------------------------------------------------------------------------|----------------|

| 2.0  | Guidelines for Getting Started with PIC16(L)F15313/23 Microcontrollers    | 22             |

| 3.0  | Enhanced Mid-Range CPU                                                    | 2              |

| 4.0  | Memory Organization                                                       | 2 <sup>-</sup> |

| 5.0  | Device Configuration                                                      | 7              |

| 6.0  | Device Information Area                                                   | 80             |

| 7.0  | Device Configuration Information                                          | 88             |

| 8.0  | Resets                                                                    |                |

| 9.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          | 100            |

| 10.0 |                                                                           |                |

| 11.0 | Power-Saving Operation Modes                                              | 139            |

| 12.0 | Windowed Watchdog Timer (WWDT)                                            | 140            |

| 13.0 | Nonvolatile Memory (NVM) Control                                          | 154            |

| 14.0 | I/O Ports                                                                 | 172            |

| 15.0 | Peripheral Pin Select (PPS) Module                                        | 18             |

|      | Peripheral Module Disable                                                 |                |

| 17.0 | Interrupt-On-Change                                                       | 202            |

| 18.0 | · · · · · · · · · · · · · · · · · · ·                                     |                |

|      | Temperature Indicator Module                                              |                |

|      | Analog-to-Digital Converter (ADC) Module                                  |                |

|      | 5-Bit Digital-to-Analog Converter (DAC1) Module                           |                |

|      | Numerically Controlled Oscillator (NCO) Module                            |                |

|      | Comparator Module                                                         |                |

|      | Zero-Cross Detection (ZCD) Module                                         |                |

|      | Timer0 Module                                                             |                |

| 26.0 | Timer1 Module with Gate Control                                           | 260            |

|      | Timer2 Module With Hardware Limit Timer (HLT)                             |                |

|      | Capture/Compare/PWM Modules                                               |                |

|      | Pulse-Width Modulation (PWM)                                              |                |

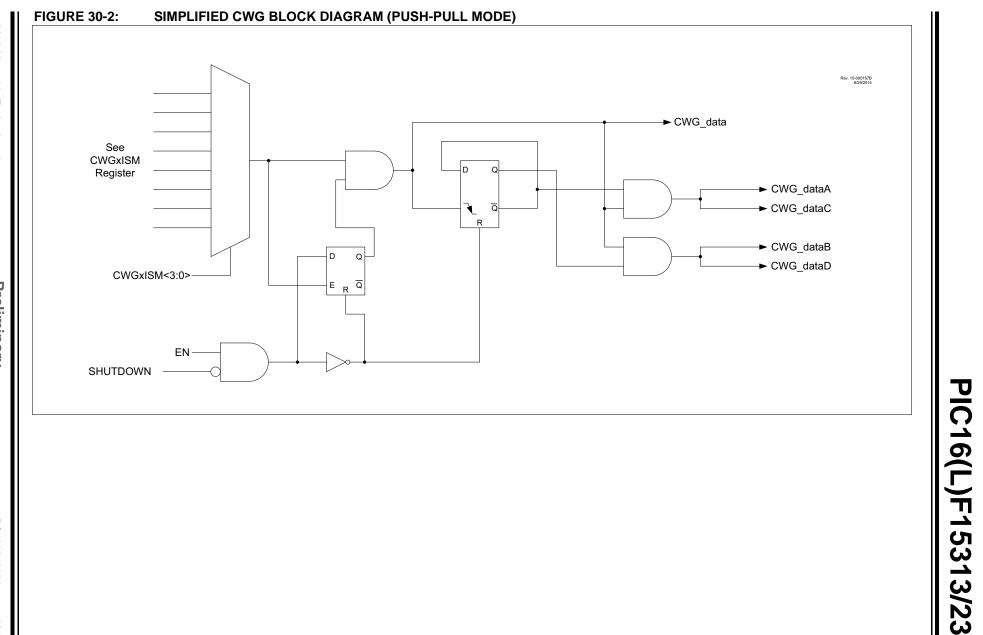

|      | Complementary Waveform Generator (CWG) Module                             |                |

|      | Configurable Logic Cell (CLC)                                             |                |

|      | Master Synchronous Serial Port (MSSP1) Module                             |                |

|      | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |                |

|      | Reference Clock Output Module                                             |                |

|      | In-Circuit Serial Programming™ (ICSP™)                                    |                |

|      | Instruction Set Summary                                                   |                |

|      | Electrical Specifications                                                 |                |

|      | DC and AC Characteristics Graphs and Charts                               |                |

|      | Development Support                                                       |                |

| 40.0 | Packaging Information                                                     | 492            |

## 1.1 Register and Bit Naming Conventions

#### 1.1.1 REGISTER NAMES

When there are multiple instances of the same peripheral in a device, the peripheral control registers will be depicted as the concatenation of a peripheral identifier, peripheral instance, and control identifier. The control registers section will show just one instance of all the register names with an 'x' in the place of the peripheral instance number. This naming convention may also be applied to peripherals when there is only one instance of that peripheral in the device to maintain compatibility with other devices in the family that contain more than one.

#### 1.1.2 BIT NAMES

There are two variants for bit names:

- · Short name: Bit function abbreviation

- · Long name: Peripheral abbreviation + short name

#### 1.1.2.1 Short Bit Names

Short bit names are an abbreviation for the bit function. For example, some peripherals are enabled with the EN bit. The bit names shown in the registers are the short name variant.

Short bit names are useful when accessing bits in C programs. The general format for accessing bits by the short name is RegisterNamebits. ShortName. For example, the enable bit, EN, in the COG1CON0 register can be set in C programs with the instruction COG1CON0bits.EN = 1.

Short names are generally not useful in assembly programs because the same name may be used by different peripherals in different bit positions. When this occurs, during the include file generation, all instances of that short bit name are appended with an underscore plus the name of the register in which the bit resides to avoid naming contentions.

## 1.1.2.2 Long Bit Names

Long bit names are constructed by adding a peripheral abbreviation prefix to the short name. The prefix is unique to the peripheral thereby making every long bit name unique. The long bit name for the COG1 enable bit is the COG1 prefix, G1, appended with the enable bit short name, EN, resulting in the unique bit name G1EN.

Long bit names are useful in both C and assembly programs. For example, in C the COG1CON0 enable bit can be set with the G1EN = 1 instruction. In assembly, this bit can be set with the BSF COG1CON0, G1EN instruction.

#### 1.1.2.3 Bit Fields

Bit fields are two or more adjacent bits in the same register. Bit fields adhere only to the short bit naming convention. For example, the three Least Significant bits of the COG1CON0 register contain the mode control bits. The short name for this field is MD. There is no long bit name variant. Bit field access is only possible in C programs. The following example demonstrates a C program instruction for setting the COG1 to the Push-Pull mode:

```

COG1CON0bits.MD = 0x5;

```

Individual bits in a bit field can also be accessed with long and short bit names. Each bit is the field name appended with the number of the bit position within the field. For example, the Most Significant mode bit has the short bit name MD2 and the long bit name is G1MD2. The following two examples demonstrate assembly program sequences for setting the COG1 to Push-Pull mode:

#### Example 1:

```

MOVLW ~(1<<G1MD1)

ANDWF COG1CON0,F

MOVLW 1<<G1MD2 | 1<<G1MD0

IORWF COG1CON0,F

```

#### Example 2:

| BSF | COG1CON0,G1MD2 |

|-----|----------------|

| BCF | COG1CON0,G1MD1 |

| BSF | COG1CON0,G1MD0 |

# 1.1.3 REGISTER AND BIT NAMING EXCEPTIONS

## 1.1.3.1 Status, Interrupt, and Mirror Bits

Status, interrupt enables, interrupt flags, and mirror bits are contained in registers that span more than one peripheral. In these cases, the bit name shown is unique so there is no prefix or short name variant.

## 1.1.3.2 Legacy Peripherals

There are some peripherals that do not strictly adhere to these naming conventions. Peripherals that have existed for many years and are present in almost every device are the exceptions. These exceptions were necessary to limit the adverse impact of the new conventions on legacy code. Peripherals that do adhere to the new convention will include a table in the registers section indicating the long name prefix for each peripheral instance. Peripherals that fall into the exception category will not have this table. These peripherals include, but are not limited to, the following:

- EUSART

- MSSP

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address           | Name    | Bit 7   | Bit 6 | Bit 5     | Bit 4         | Bit 3             | Bit 2               | Bit 1       | Bit 0     | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|-------------------|---------|---------|-------|-----------|---------------|-------------------|---------------------|-------------|-----------|-----------------------|----------------------------|

| Bank 17           |         |         |       |           |               |                   |                     |             |           |                       |                            |

|                   |         |         |       | CPU COF   | RE REGISTERS; | see Table 4-3 for | specifics           |             |           |                       |                            |

| 88Ch              | CPUDOZE | IDLEN   | DOZEN | ROI       | DOE           | _                 | - DOZE2 DOZE1 DOZE0 |             |           |                       | u000 -000                  |

| 88Dh              | OSCCON1 | _       |       | NOSC<2:0> |               |                   | ND                  | IV<3:0>     |           | -ddd 0000             | -qqq 0000                  |

| 88Eh              | OSCCON2 | _       |       | COSC<2:0> |               | CDIV<3:0>         |                     |             | -ববব বববব | -ddd dddd             |                            |

| 88Fh              | OSCCON3 | CSWHOLD | _     | _         | ORDY          | NOSCR             | _                   | _           | _         | 00 0                  | 00 0                       |

| 890h              | OSCSTAT | EXTOR   | HFOR  | MFOR      | LFOR          | _                 | ADOR                | _           | PLLR      | q000 -q-0             | qqqq -q-q                  |

| 891h              | OSCEN   | EXTOEN  | HFOEN | MFOEN     | LFOEN         | _                 | ADOEN               | _           | _         | 0000 -0               | 0000 -0                    |

| 892h              | OSCTUNE | _       | _     |           |               | HFT               | JN<5:0>             |             |           | 10 0000               | 10 0000                    |

| 893h              | OSCFRQ  | _       | _     | _         | _             | _                 |                     | HFFRQ<2:0   | >         | qqq                   | qqq                        |

| 894h              | _       |         |       |           | Unimpler      | nented            |                     |             |           | _                     | _                          |

| 895h              | CLKRCON | CLKREN  | _     | _         | CLKRD         | C<1:0>            |                     | CLKRDIV<2:0 | )>        | 0x xxxx               | 0u uuuu                    |

| 896h              | CLKRCLK | _       | _     | _         | _             | CLKRCLK<3:0>      |                     |             | 0000      | 0000                  |                            |

| 897h<br>—<br>89Fh | _       |         |       |           | Unimpler      | _                 | _                   |             |           |                       |                            |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                   | Name                   | Bit 7           | Bit 6 | Bit 5   | Bit 4         | Bit 3             | Bit 2     | Bit 1    | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------------------------|------------------------|-----------------|-------|---------|---------------|-------------------|-----------|----------|--------|-----------------------|----------------------------|

| Bank 19                   |                        |                 |       |         |               |                   |           |          |        |                       |                            |

|                           |                        |                 |       | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics |          |        |                       |                            |

| 98Ch                      |                        | - Unimplemented |       |         |               |                   |           |          |        |                       | _                          |

| 98Dh                      | ı                      |                 |       |         | Unimpler      | mented            |           |          |        |                       | _                          |

| 98Eh                      | ı                      |                 |       |         | Unimpler      | mented            |           |          |        |                       | _                          |

| 98Fh                      | CMOUT                  |                 | I     | _       | _             | _                 | 1         | MC2OUT   | MC1OUT | 00                    | 00                         |

| 990h                      | CM1CON0                | EN              | OUT   | _       | POL           | _                 | _         | HYS      | SYNC   | 00-000                | 00-000                     |

| 991h                      | CM1CON1                | _               | _     | _       | _             | _                 | _         | INTP     | INTN   | 00                    | 00                         |

| 992h                      | CM1NCH                 | _               | _     | _       | _             | _                 |           | NCH<2:0> |        | 000                   | 000                        |

| 993h                      | CM1PCH                 | _               | _     | _       | _             | _                 |           | PCH<2:0> |        | 000                   | 000                        |

| 994h                      | CM2CON0 <sup>(1)</sup> | EN              | OUT   | _       | POL           | _                 | _         | HYS      | SYNC   | 00-000                | 00-000                     |

| 995h                      | CM2CON1 <sup>(1)</sup> | _               | _     | _       | _             | _                 | _         | INTP     | INTN   | 00                    | 00                         |

| 996h                      | CM2NCH <sup>(1)</sup>  | _               | _     | _       | _             | _                 |           | NCH<2:0> |        | 000                   | 000                        |

| 997h                      | CM2PCH <sup>(1)</sup>  | _               | _     | _       | _             | _                 |           | PCH<2:0> | 000    | 000                   |                            |

| 994h — Unimplemented 99Fh |                        |                 |       |         |               |                   |           |          | _      | _                     |                            |

**Legend:** x = unknown, u = unchanged, q = depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

Note 1: Present only on PIC16(L)F15323.

TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address | Name                  | Bit 7 | Bit 6         | Bit 5   | Bit 4         | Bit 3             | Bit 2      | Bit 1  | Bit 0  | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

|---------|-----------------------|-------|---------------|---------|---------------|-------------------|------------|--------|--------|-----------------------|----------------------------|

| Bank 62 |                       |       |               |         |               | •                 |            |        |        |                       |                            |

|         |                       |       |               | CPU COF | RE REGISTERS; | see Table 4-3 for | specifics  |        |        |                       |                            |

| 1F0Ch   | _                     |       |               |         | Unimple       | mented            |            |        |        | _                     | _                          |

| 1F0Dh   | _                     |       | Unimplemented |         |               |                   |            |        |        |                       | _                          |

| 1F0Eh   | _                     |       | Unimplemented |         |               |                   |            |        |        | _                     | _                          |

| 1F0Fh   | _                     |       |               |         | Unimple       | mented            |            |        |        | _                     | _                          |

| 1F10h   | RA0PPS                | _     | _             | _       | RA0PPS<4:0>   |                   |            |        |        | 0 0000                | u uuuu                     |

| 1F11h   | RA1PPS                | _     | _             | _       | RA1PPS<4:0>   |                   |            |        |        | 0 0000                | u uuuu                     |

| 1F12h   | RA2PPS                | _     | _             | -       | RA2PPS<4:0>   |                   |            |        |        | 0 0000                | u uuuu                     |

| 1F13h   | RA3PPS                | _     | _             | -       | RA3PPS<4:0>   |                   |            |        |        | 0 0000                | u uuuu                     |

| 1F14h   | RA4PPS                | _     |               | I       |               |                   | RA4PPS<4:0 | >      |        | 0 0000                | u uuuu                     |

| 1F15h   | RA5PPS                | _     |               | I       |               |                   | RA5PPS<4:0 | >      |        | 0 0000                | u uuuu                     |

| 1F16h   |                       |       |               |         | Harman        |                   |            |        |        |                       |                            |

| 1F1Fh   | _                     |       |               |         | Unimple       | mentea            |            |        |        | _                     | _                          |

| 1F20h   | RC0PPS <sup>(1)</sup> | _     | _             | _       |               |                   | RC0PPS<4:0 | >      |        | 0 0000                | u uuuu                     |

| 1F21h   | RC1PPS <sup>(1)</sup> | _     | _             | _       |               | RC1PPS<4:0>       |            |        |        | 0 0000                | u uuuu                     |

| 1F22h   | RC2PPS <sup>(1)</sup> | _     | _             | _       | RC2PPS<4:0>   |                   |            |        | 0 0000 | u uuuu                |                            |

| 1F23h   | RC3PPS <sup>(1)</sup> | _     | _             | _       |               |                   | RC3PPS<4:0 | >      |        | 0 0000                | u uuuu                     |

| 1F24h   | RC4PPS <sup>(1)</sup> | _     | _             | _       |               |                   | 0 0000     | u uuuu |        |                       |                            |

| 1F25h   | RC5PPS <sup>(1)</sup> | _     | _             | _       |               |                   | 0 0000     | u uuuu |        |                       |                            |

**Legend:** x = unknown, u = unchanged, q = depends on condition, -= unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. **Note** 1: Present only in PIC16(L)F15323.

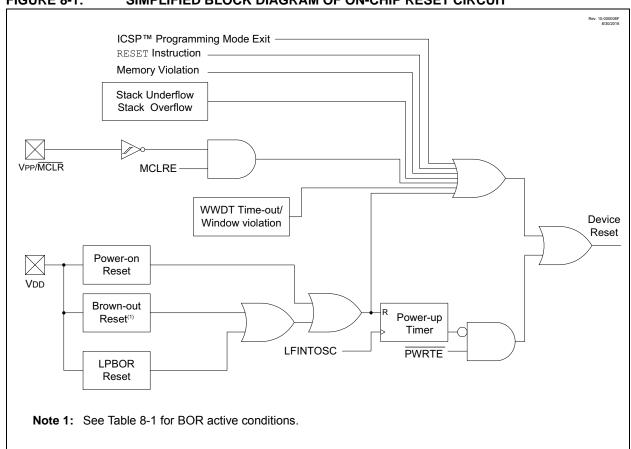

## 8.0 RESETS

There are multiple ways to reset this device:

- Power-on Reset (POR)

- · Brown-out Reset (BOR)

- Low-Power Brown-out Reset (LPBOR)

- MCLR Reset

- WDT Reset

- RESET instruction

- · Stack Overflow

- · Stack Underflow

- · Programming mode exit

- Memory Violation Reset (MEMV)

To allow VDD to stabilize, an optional Power-up Timer can be enabled to extend the Reset time after a BOR or POR event.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 8-1.

## FIGURE 8-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 8.1 Power-on Reset (POR)

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

## 8.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset when VDD reaches a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- · BOR is off when in Sleep

- · BOR is controlled by software

- · BOR is always off

Refer to Table 8-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset. See Figure 8-2 for more information.

TABLE 8-1: BOR OPERATING MODES

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep |

|------------|--------|-------------|----------|---------------------------------------------------------------------|

| 11         | х      | X           | Active   | Wait for release of BOR <sup>(1)</sup> (BORRDY = 1)                 |

| 10         | 77     | Awake       | Active   | Waits for release of BOR (BORRDY = 1)                               |

| 10         | X      | Sleep       | Disabled | Waits for BOR Reset release                                         |

| 0.1        | 1      | X           | Active   | Waits for BOR Reset release (BORRDY = 1)                            |

| 01         | 0      | Х           | Disabled | Pagina immediately (POPPDV =)                                       |

| 0.0        | Х      | Х           | Disabled | Begins immediately (BORRDY = x)                                     |

**Note 1:** In this specific case, "Release of POR" and "Wake-up from Sleep", there is no delay in start-up. The BOR ready flag, (BORRDY = 1), will be set before the CPU is ready to execute instructions because the BOR circuit is forced on by the BOREN<1:0> bits.

## 8.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

## 8.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep. The device wake-up will be delayed until the BOR is ready.

#### 9.2.1.4 4x PLL

The oscillator module contains a PLL that can be used with external clock sources and internal oscillator to provide a system clock source. The input frequency for the PLL must fall within specifications. See the PLL Clock Timing Specifications in Table 37-9.

The PLL may be enabled for use by one of two methods:

- 1. Program the RSTOSC bits in the Configuration Word 1 to enable the EXTOSC with 4x PLL.

- Write the NOSC bits in the OSCCON1 register to enable the EXTOSC with 4x PLL.

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Application Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC® Oscillator Design" (DS00849)

- AN943, "Practical PIC® Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

- TB097, "Interfacing a Micro Crystal MS1V-T1K 32.768 kHz Tuning Fork Crystal to a PIC16F690/SS" (DS91097)

- AN1288, "Design Practices for Low-Power External Oscillators" (DS01288)

#### 9.2.2 INTERNAL CLOCK SOURCES

The device may be configured to use an internal oscillator block as the system clock by performing one of the following actions:

- Program the RSTOSC<2:0> bits in Configuration Words to select the INTOSC clock source, which will be used as the default system clock upon a device Reset.

- Write the NOSC<2:0> bits in the OSCCON1

register to switch the system clock source to the

internal oscillator during run-time. See

Section 9.3 "Clock Switching" for more

information.

In **INTOSC** mode, CLKIN is available for general purpose I/O. CLKOUT is available for general purpose I/O or CLKOUT.

The function of the CLKOUT pin is determined by the CLKOUTEN bit in Configuration Words.

The internal oscillator block has two independent oscillators that can produce two internal system clock sources.

- The HFINTOSC (High-Frequency Internal Oscillator) is factory calibrated and operates up to 32 MHz. The frequency of HFINTOSC can be selected through the OSCFRQ Frequency Selection register, and fine-tuning can be done via the OSCTUNE register.

- The LFINTOSC (Low-Frequency Internal Oscillator) is factory-calibrated and operates at 31 kHz.

#### REGISTER 10-17: PIR7: PERIPHERAL INTERRUPT REQUEST REGISTER 7

| U-0       | U-0 | R/W/HS-0/0 | R/W/HS-0/0 | U-0 | U-0 | U-0 | R/W/HS-0/0 |  |  |

|-----------|-----|------------|------------|-----|-----|-----|------------|--|--|

| _         | _   | NVMIF      | NCO1IF     |     | _   | _   | CWG1IF     |  |  |

| bit 7 bit |     |            |            |     |     |     |            |  |  |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'u = Bit is unchangedx = Bit is unknown-n/n = Value at POR and BOR/Value at all other Resets'1' = Bit is set'0' = Bit is clearedHS = Hardware set

bit 7-6 Unimplemented: Read as '0'

bit 5 **NVMIF:** Nonvolatile Memory (NVM) Interrupt Flag bit 1 = The requested NVM operation has completed

0 = NVM interrupt not asserted

bit 4 NCO1IF: Numerically Controlled Oscillator (NCO) Interrupt Flag bit

1 = The NCO has rolled over

0 = No NCO interrupt event has occurred

bit 3-1 Unimplemented: Read as '0'

bit 0 CWG1IF: CWG1 Interrupt Flag bit

1 = CWG1 has gone into shutdown

0 = CWG1 is operating normally, or interrupt cleared

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the Global Enable bit, GIE, of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# 13.0 NONVOLATILE MEMORY (NVM) CONTROL

NVM consists of the Program Flash Memory (PFM).

NVM is accessible by using both the FSR and INDF registers, or through the NVMREG register interface.

The write time is controlled by an on-chip timer. The write/erase voltages are generated by an on-chip charge pump rated to operate over the operating voltage range of the device.

NVM can be protected in two ways; by either code protection or write protection.

Code protection ( $\overline{\text{CP}}$  bit in Configuration Word 5) disables access, reading and writing, to the PFM via external device programmers. Code protection does not affect the self-write and erase functionality. Code protection can only be Reset by a device programmer performing a Bulk Erase to the device, clearing all nonvolatile memory, Configuration bits, and User IDs.

Write protection prohibits self-write and erase to a portion or all of the PFM, as defined by the WRT<1:0> bits of Configuration Word 4. Write protection does not affect a device programmer's ability to read, write, or erase the device.

## 13.1 Program Flash Memory (PFM)

PFM consists of an array of 14-bit words as user memory, with additional words for User ID information, Configuration words, and interrupt vectors. PFM provides storage locations for:

- · User program instructions

- · User defined data

PFM data can be read and/or written to through:

- CPU instruction fetch (read-only)

- FSR/INDF indirect access (read-only)

(Section 13.2 "FSR and INDF Access")

- NVMREG access (Section 13.3 "NVMREG Access"

- In-Circuit Serial Programming™ (ICSP™)

Read operations return a single word of memory. When write and erase operations are done on a row basis, the row size is defined in Table 13-1. PFM will erase to a logic '1' and program to a logic '0'.

TABLE 13-1: FLASH MEMORY ORGANIZATION BY DEVICE

| Device         | Row<br>Erase<br>(words) | Write<br>Latches<br>(words) | Total<br>Program<br>Flash<br>(words) |

|----------------|-------------------------|-----------------------------|--------------------------------------|

| PIC16(L)F15313 | C16(L)F15313 32 32      |                             | 2048                                 |

| PIC16(L)F15323 | 32                      | 32                          | 2048                                 |

It is important to understand the PFM memory structure for erase and programming operations. PFM is arranged in rows. A row consists of 32 14-bit program memory words. A row is the minimum size that can be erased by user software.

All or a portion of a row can be programmed. Data to be written into the program memory row is written to 14-bit wide data write latches. These latches are not directly accessible, but may be loaded via sequential writes to the NVMDATH:NVMDATL register pair.

Note: To modify only a portion of a previously programmed row, the contents of the entire row must be read. Then, the new data and retained data can be written into the write latches to reprogram the row of PFM. However, any unprogrammed locations can be written without first erasing the row. In this case, it is not necessary to save and rewrite the other previously programmed locations

#### 13.1.1 PROGRAM MEMORY VOLTAGES

The PFM is readable and writable during normal operation over the full VDD range.

#### 13.1.1.1 Programming Externally

The program memory cell and control logic support write and Bulk Erase operations down to the minimum device operating voltage. Special BOR operation is enabled during Bulk Erase (Section 8.2.4 "BOR is always OFF").

#### 13.1.1.2 Self-programming

The program memory cell and control logic will support write and row erase operations across the entire VDD range. Bulk Erase is not available when self-programming.

#### REGISTER 14-14: ODCONC: PORTC OPEN-DRAIN CONTROL REGISTER

| U-0   | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | ODCC5   | ODCC4   | ODCC3   | ODCC2   | ODCC1   | ODCC0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-0 ODCC<5:0>: PORTC Open-Drain Enable bits

For RC<5:0> pins, respectively

1 = Port pin operates as open-drain drive (sink current only)

0 = Port pin operates as standard push-pull drive (source and sink current)

#### REGISTER 14-15: SLRCONC: PORTC SLEW RATE CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | SLRC5   | SLRC4   | SLRC3   | SLRC2   | SLRC1   | SLRC0   |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-0 SLRC<5:0>: PORTC Slew Rate Enable bits

For RC<5:0> pins, respectively 1 = Port pin slew rate is limited 0 = Port pin slews at maximum rate

#### REGISTER 14-16: INLVLC: PORTC INPUT LEVEL CONTROL REGISTER

| U-0   | U-0 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |

|-------|-----|---------|---------|---------|---------|---------|---------|

| _     | _   | INLVLC5 | INLVLC4 | INLVLC3 | INLVLC2 | INLVLC1 | INLVLC0 |

| bit 7 |     |         |         |         |         |         | bit 0   |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

u = Bit is unchanged x = Bit is unknown -n/n = Value at POR and BOR/Value at all other Resets

'1' = Bit is set '0' = Bit is cleared

bit 7-6 **Unimplemented**: Read as '0'

bit 5-0 **INLVLC<5:0>:** PORTC Input Level Select bits

For RC<5:0> pins, respectively

1 = ST input used for PORT reads and interrupt-on-change 0 = TTL input used for PORT reads and interrupt-on-change

#### 23.10 CWG1 Auto-shutdown Source

The output of the comparator module can be used as an auto-shutdown source for the CWG1 module. When the output of the comparator is active and the corresponding ASxE is enabled, the CWG operation will be suspended immediately (see **Section 30.10** "Auto-Shutdown").

## 23.11 Operation in Sleep Mode

The comparator module can operate during Sleep. The comparator clock source is based on the Timer1 clock source. If the Timer1 clock source is either the system clock (Fosc) or the instruction clock (Fosc/4), Timer1 will not operate during Sleep, and synchronized comparator outputs will not operate.

A comparator interrupt will wake the device from Sleep. The CxIE bits of the PIE2 register must be set to enable comparator interrupts.

DS40001897A-page 321

#### 30.10 Auto-Shutdown

Auto-shutdown is a method to immediately override the CWG output levels with specific overrides that allow for safe shutdown of the circuit. The shutdown state can be either cleared automatically or held until cleared by software. The auto-shutdown circuit is illustrated in Figure 30-12.

#### 30.10.1 SHUTDOWN

The shutdown state can be entered by either of the following two methods:

- · Software generated

- · External Input

#### 30.10.1.1 Software Generated Shutdown

Setting the SHUTDOWN bit of the CWG1AS0 register will force the CWG into the shutdown state.

When the auto-restart is disabled, the shutdown state will persist as long as the SHUTDOWN bit is set.

When auto-restart is enabled, the SHUTDOWN bit will clear automatically and resume operation on the next rising edge event.

#### 30.10.2 EXTERNAL INPUT SOURCE

External shutdown inputs provide the fastest way to safely suspend CWG operation in the event of a Fault condition. When any of the selected shutdown inputs goes active, the CWG outputs will immediately go to the selected override levels without software delay. Several input sources can be selected to cause a shutdown condition. All input sources are active-low. The sources are:

- Comparator C1OUT\_sync

- Comparator C2OUT sync

- · Timer2 TMR2\_postscaled

- · CWG1IN input pin

Shutdown inputs are selected using the CWG1AS1 register (Register 30-6).

Note:

Shutdown inputs are level sensitive, not edge sensitive. The shutdown state cannot be cleared, except by disabling auto-shutdown, as long as the shutdown input level persists.

## 30.11 Operation During Sleep

The CWG module operates independently from the system clock and will continue to run during Sleep, provided that the clock and input sources selected remain active.

The HFINTOSC remains active during Sleep when all the following conditions are met:

- · CWG module is enabled

- · Input source is active

- HFINTOSC is selected as the clock source, regardless of the system clock source selected.

In other words, if the HFINTOSC is simultaneously selected as the system clock and the CWG clock source, when the CWG is enabled and the input source is active, then the CPU will go idle during Sleep, but the HFINTOSC will remain active and the CWG will continue to operate. This will have a direct effect on the Sleep mode current.

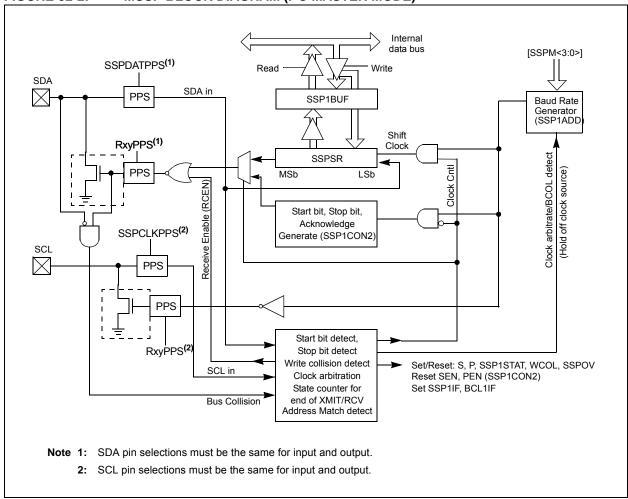

The I<sup>2</sup>C interface supports the following modes and features:

- · Master mode

- · Slave mode

- · Byte NACKing (Slave mode)

- · Limited multi-master support

- · 7-bit and 10-bit addressing

- · Start and Stop interrupts

- Interrupt masking

- · Clock stretching

- · Bus collision detection

- · General call address matching

- · Address masking

- · Selectable SDA hold times

Figure 32-2 is a block diagram of the  $I^2C$  interface module in Master mode. Figure 32-3 is a diagram of the  $I^2C$  interface module in Slave mode.

## FIGURE 32-2: MSSP BLOCK DIAGRAM (I<sup>2</sup>C MASTER MODE)

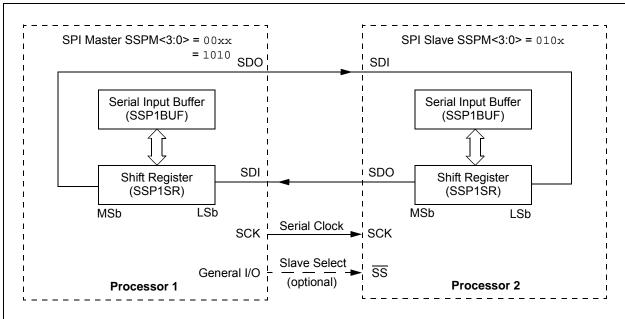

#### 32.2.2 SPI MODE OPERATION

When initializing the SPI, several options need to be specified. This is done by programming the appropriate control bits (SSP1CON1<3:0> and SSP1STAT<7:6>). These control bits allow the following to be specified:

- Master mode (SCK is the clock output)

- · Slave mode (SCK is the clock input)

- Clock Polarity (Idle state of SCK)

- Data Input Sample Phase (middle or end of data output time)

- Clock Edge (output data on rising/falling edge of SCK)

- Clock Rate (Master mode only)

- · Slave Select mode (Slave mode only)

To enable the serial port, SSP Enable bit, SSPEN of the SSP1CON1 register, must be set. To reset or reconfigure SPI mode, clear the SSPEN bit, re-initialize the SSP1CONx registers and then set the SSPEN bit. This configures the SDI, SDO, SCK and SS pins as serial port pins. For the pins to behave as the serial port function, some must have their data direction bits (in the TRISx register) appropriately programmed as follows:

- SDI must have corresponding TRIS bit set

- · SDO must have corresponding TRIS bit cleared

- SCK (Master mode) must have corresponding TRIS bit cleared

- SCK (Slave mode) must have corresponding TRIS bit set

- SS must have corresponding TRIS bit set

Any serial port function that is not desired may be overridden by programming the corresponding data direction (TRIS) register to the opposite value.

The MSSP consists of a transmit/receive shift register (SSP1SR) and a buffer register (SSP1BUF). The SSP1SR shifts the data in and out of the device, MSb first. The SSP1BUF holds the data that was written to the SSP1SR until the received data is ready. Once the eight bits of data have been received, that byte is moved to the SSP1BUF register. Then, the Buffer Full Detect bit, BF of the SSP1STAT register, and the interrupt flag bit, SSP1IF, are set. Any write to the SSP1BUF register during transmission/reception of data will be ignored and the write collision detect bit WCOL of the SSP1CON1 register, will be set. User software must clear the WCOL bit to allow the following write(s) to the SSP1BUF register to complete successfully.

When the application software is expecting to receive valid data, the SSP1BUF should be read before the next byte of data to transfer is written to the SSP1BUF. The Buffer Full bit, BF of the SSP1STAT register, indicates when SSP1BUF has been loaded with the received data (transmission is complete). When the SSP1BUF is read, the BF bit is cleared. This data may be irrelevant if the SPI is only a transmitter. Generally, the MSSP interrupt is used to determine when the transmission/reception has completed. If the interrupt method is not going to be used, then software polling can be done to ensure that a write collision does not occur.

The SSP1SR is not directly readable or writable and can only be accessed by addressing the SSP1BUF register.

FIGURE 32-5: SPI MASTER/SLAVE CONNECTION

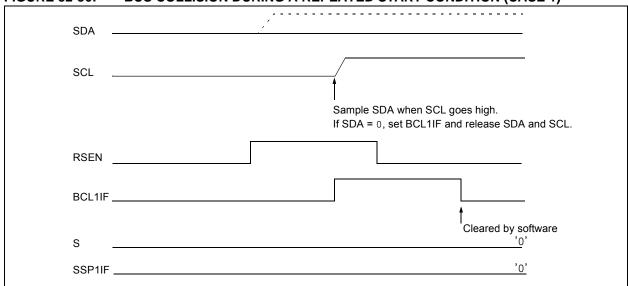

# 32.6.13.2 Bus Collision During a Repeated Start Condition

During a Repeated Start condition, a bus collision occurs if:

- a) A low level is sampled on SDA when SCL goes from low level to high level (Case 1).

- b) SCL goes low before SDA is asserted low, indicating that another master is attempting to transmit a data '1' (Case 2).

When the user releases SDA and the pin is allowed to float high, the BRG is loaded with SSP1ADD and counts down to zero. The SCL pin is then deasserted and when sampled high, the SDA pin is sampled.

If SDA is low, a bus collision has occurred (i.e., another master is attempting to transmit a data '0', Figure 32-36). If SDA is sampled high, the BRG is reloaded and begins

counting. If SDA goes from high-to-low before the BRG times out, no bus collision occurs because no two masters can assert SDA at exactly the same time.

If SCL goes from high-to-low before the BRG times out and SDA has not already been asserted, a bus collision occurs. In this case, another master is attempting to transmit a data '1' during the Repeated Start condition, see Figure 32-37.

If, at the end of the BRG time-out, both SCL and SDA are still high, the SDA pin is driven low and the BRG is reloaded and begins counting. At the end of the count, regardless of the status of the SCL pin, the SCL pin is driven low and the Repeated Start condition is complete.

## FIGURE 32-37: BUS COLLISION DURING REPEATED START CONDITION (CASE 2)

## 36.2 General Format for Instructions

**TABLE 36-3: INSTRUCTION SET**

| Mnemonic,<br>Operands |          | Description:                  | Cualas    | 14-Bit Opcode |      |      |      | Status   | Nieder |

|-----------------------|----------|-------------------------------|-----------|---------------|------|------|------|----------|--------|

|                       |          | Description                   | Cycles    | MSb           |      |      | LSb  | Affected | Notes  |

|                       |          | BYTE-ORIENTED FILE REGIS      | TER OPE   | RATIO         | NS   |      |      |          |        |

| ADDWF                 | f, d     | Add W and f                   | 1         | 00            | 0111 | dfff | ffff | C, DC, Z | 2      |

| ADDWFC                | f, d     | Add with Carry W and f        | 1         | 11            | 1101 | dfff | ffff | C, DC, Z | 2      |

| ANDWF                 | f, d     | AND W with f                  | 1         | 0.0           | 0101 | dfff | ffff | Z        | 2      |

| ASRF                  | f, d     | Arithmetic Right Shift        | 1         | 11            | 0111 | dfff | ffff | C, Z     | 2      |

| LSLF                  | f, d     | Logical Left Shift            | 1         | 11            | 0101 | dfff | ffff | C, Z     | 2      |

| LSRF                  | f, d     | Logical Right Shift           | 1         | 11            | 0110 | dfff | ffff | C, Z     | 2      |

| CLRF                  | f        | Clear f                       | 1         | 00            | 0001 | lfff | ffff | Z        | 2      |

| CLRW                  | _        | Clear W                       | 1         | 00            | 0001 | 0000 | 00xx | Z        |        |

| COMF                  | f, d     | Complement f                  | 1         | 0.0           | 1001 | dfff | ffff | Z        | 2      |

| DECF                  | f, d     | Decrement f                   | 1         | 0.0           | 0011 | dfff | ffff | Z        | 2      |

| INCF                  | f, d     | Increment f                   | 1         | 0.0           | 1010 | dfff | ffff | Z        | 2      |

| IORWF                 | f, d     | Inclusive OR W with f         | 1         | 0.0           | 0100 | dfff | ffff | Z        | 2      |

| MOVF                  | f, d     | Move f                        | 1         | 0.0           | 1000 | dfff | ffff | Z        | 2      |

| MOVWF                 | f        | Move W to f                   | 1         | 0.0           | 0000 | 1fff | ffff |          | 2      |

| RLF                   | f, d     | Rotate Left f through Carry   | 1         | 0.0           | 1101 | dfff | ffff | С        | 2      |

| RRF                   | f, d     | Rotate Right f through Carry  | 1         | 0.0           | 1100 | dfff | ffff | С        | 2      |

| SUBWF                 | f, d     | Subtract W from f             | 1         | 0.0           | 0010 | dfff | ffff | C, DC, Z | 2      |

| SUBWFB                | f, d     | Subtract with Borrow W from f | 1         | 11            | 1011 | dfff | ffff | C, DC, Z | 2      |

| SWAPF                 | f, d     | Swap nibbles in f             | 1         | 0.0           | 1110 | dfff | ffff | -, -,    | 2      |

| XORWF                 | f, d     | Exclusive OR W with f         | 1         | 00            | 0110 | dfff | ffff | Z        | 2      |

|                       |          | BYTE ORIENTED SKIP            | OPERATION | ONS           |      |      |      |          |        |

| DECFSZ                | f, d     | Decrement f, Skip if 0        | 1(2)      | 00            | 1011 | dfff | ffff |          | 1, 2   |

| INCFSZ                | f, d     | Increment f, Skip if 0        | 1(2)      | 00            | 1111 | dfff | ffff |          | 1, 2   |

|                       |          | BIT-ORIENTED FILE REGIS       | ER OPER   | RATION        | NS   | l    | ı    |          | ı      |

| BCF                   | f, b     | Bit Clear f                   | 1         | 01            | 00bb | bfff | ffff |          | 2      |

| BSF                   | f, b     | Bit Set f                     | 1         | 01            | 01bb | bfff | ffff |          | 2      |

|                       | l        | BIT-ORIENTED SKIP O           | PERATIO   | NS            | I    |      |      |          | ı      |

| BTFSC                 | f, b     | Bit Test f, Skip if Clear     | 1 (2)     | 01            | 10bb | bfff | ffff |          | 1, 2   |

| BTFSS                 | f, b     | Bit Test f, Skip if Set       | 1 (2)     | 01            | 11bb | bfff | ffff |          | 1, 2   |

| LITERAL (             | OPERATIO | NS                            |           |               |      |      |      |          |        |

| ADDLW                 | k        | Add literal and W             | 1         | 11            | 1110 | kkkk | kkkk | C, DC, Z |        |

| ANDLW                 | k        | AND literal with W            | 1         | 11            | 1001 | kkkk | kkkk | Z        |        |

| IORLW                 | k        | Inclusive OR literal with W   | 1         | 11            | 1000 | kkkk | kkkk | Z        |        |

| MOVLB                 | k        | Move literal to BSR           | 1         | 00            | 000  | 0k   | kkkk |          |        |

| MOVLP                 | k        | Move literal to PCLATH        | 1         | 11            | 0001 | 1kkk | kkkk |          |        |

| MOVLW                 | k        | Move literal to W             | 1         | 11            | 0000 | kkkk | kkkk |          |        |

| SUBLW                 | k        | Subtract W from literal       | 1         | 11            | 1100 | kkkk | kkkk | C, DC, Z |        |

| XORLW                 | k        | Exclusive OR literal with W   | 1         | 11            | 1010 | kkkk | kkkk | Z        |        |

Note 1: If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

<sup>2:</sup> If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

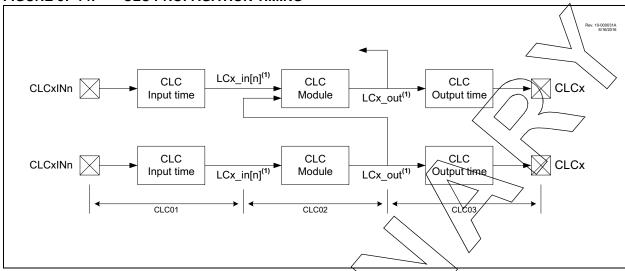

FIGURE 37-14: CLC PROPAGATION TIMING

TABLE 37-20: CONFIGURABLE LOGIC CELL (CLC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +125°C |         |                                             |          |          |      |          |                          |

|----------------------------------------------------------------------------------------------------|---------|---------------------------------------------|----------|----------|------|----------|--------------------------|

| Param.<br>No.                                                                                      | Sym.    | Characteristic                              | Min.     | Typt     | Max. | Units    | Conditions               |

| CLC01*                                                                                             | TCLCIN  | CLC input time                              |          | 7        | 105  | ns       | (Note 1)                 |

| CLC02*                                                                                             | TCLC    | CLC module input to output propagation time | <u> </u> | 24<br>12 |      | ns<br>ns | VDD = 1.8V<br>VDD > 3.6V |

| CLC03*                                                                                             | TCLCOUT | CLC output time Rise Time                   | _        | 107      | _    | _        | (Note 1)                 |

|                                                                                                    |         | Fall Time                                   | _        | IO8      | -    | _        | (Note 1)                 |

| CLC04*                                                                                             | FCLCMAX | CLC maximum switching frequency             | _        | 32       | Fosc | MHz      |                          |

- \* These parameters are characterized but not/tested.

- † Data in "Typ" column is at 3.0% 25 c unless otherwise stated. These parameters are for design guidance only and are not tested.

## 8-Lead Plastic Dual Flat, No Lead Package (MF) - 3x3x0.9mm Body [DFN]

te: For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |           |      |  |  |  |  |

|------------------------|-------------|----------|-----------|------|--|--|--|--|

| Dimension              | Limits      | MIN      | NOM       | MAX  |  |  |  |  |

| Number of Pins         | N           | 8        |           |      |  |  |  |  |

| Pitch                  | е           |          | 0.65 BSC  |      |  |  |  |  |

| Overall Height         | Α           | 0.80     | 0.80 0.90 |      |  |  |  |  |

| Standoff               | A1          | 0.00     | 0.02      | 0.05 |  |  |  |  |

| Contact Thickness      | A3          | 0.20 REF |           |      |  |  |  |  |

| Overall Length         | D           |          | 3.00 BSC  |      |  |  |  |  |

| Exposed Pad Width      | E2          | 1.34     | -         | 1.60 |  |  |  |  |

| Overall Width          | Е           | 3.00 BSC |           |      |  |  |  |  |

| Exposed Pad Length     | D2          | 1.60     | -         | 2.40 |  |  |  |  |

| Contact Width          | b           | 0.25     | 0.30      | 0.35 |  |  |  |  |

| Contact Length         | L           | 0.20     | 0.30      | 0.55 |  |  |  |  |

| Contact-to-Exposed Pad | K           | 0.20     | -         | -    |  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package may have one or more exposed tie bars at ends.

- 3. Package is saw singulated

- 4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing No. C04-062C Sheet 2 of 2