Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15323-e-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0  | Device Overview                                                           |     |

|------|---------------------------------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with PIC16(L)F15313/23 Microcontrollers    |     |

| 3.0  | Enhanced Mid-Range CPU                                                    |     |

| 4.0  | Memory Organization                                                       |     |

| 5.0  | Device Configuration                                                      |     |

| 6.0  | Device Information Area                                                   |     |

| 7.0  | Device Configuration Information                                          |     |

| 8.0  | Resets                                                                    |     |

| 9.0  | Oscillator Module (with Fail-Safe Clock Monitor)                          | 100 |

| 10.0 | Interrupts                                                                |     |

| 11.0 | Power-Saving Operation Modes                                              | 139 |

| 12.0 | Windowed Watchdog Timer (WWDT)                                            | 146 |

| 13.0 | Nonvolatile Memory (NVM) Control                                          | 154 |

| 14.0 | I/O Ports                                                                 | 172 |

| 15.0 | Peripheral Pin Select (PPS) Module                                        | 185 |

| 16.0 | Peripheral Module Disable                                                 | 194 |

| 17.0 | Interrupt-On-Change                                                       | 202 |

| 18.0 | Fixed Voltage Reference (FVR)                                             |     |

| 19.0 | Temperature Indicator Module                                              | 212 |

| 20.0 | Analog-to-Digital Converter (ADC) Module                                  |     |

| 21.0 | 5-Bit Digital-to-Analog Converter (DAC1) Module                           | 229 |

| 22.0 | Numerically Controlled Oscillator (NCO) Module                            |     |

|      | Comparator Module                                                         |     |

|      | Zero-Cross Detection (ZCD) Module                                         |     |

|      | Timer0 Module                                                             |     |

|      | Timer1 Module with Gate Control                                           |     |

| 27.0 | Timer2 Module With Hardware Limit Timer (HLT)                             | 279 |

| 28.0 |                                                                           |     |

|      | Pulse-Width Modulation (PWM)                                              |     |

| 30.0 | Complementary Waveform Generator (CWG) Module                             |     |

| 31.0 |                                                                           |     |

| 32.0 | Master Synchronous Serial Port (MSSP1) Module                             |     |

| 33.0 | Enhanced Universal Synchronous Asynchronous Receiver Transmitter (EUSART) |     |

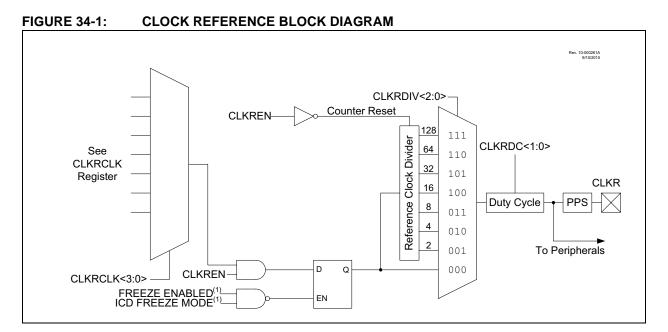

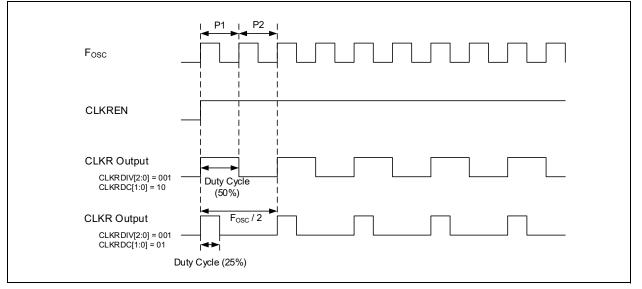

| 34.0 | Reference Clock Output Module                                             |     |

| 35.0 | In-Circuit Serial Programming™ (ICSP™)                                    |     |

| 36.0 | Instruction Set Summary                                                   |     |

| 37.0 |                                                                           |     |

| 38.0 | DC and AC Characteristics Graphs and Charts                               |     |

| 39.0 | Development Support                                                       |     |

| 40.0 | Packaging Information                                                     |     |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Website at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS3000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Website; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our website at www.microchip.com to receive the most current information on all of our products.

# TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address                                         | Name    | Bit 7  | Bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |  |

|-------------------------------------------------|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|-----------------------|----------------------------|--|

| Bank 7                                          | ank 7   |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |       |       |       |       |       |                       |                            |  |

| CPU CORE REGISTERS; see Table 4-3 for specifics |         |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |       |       |       |       |       |                       |                            |  |

| 38Ch                                            | PWM6DCL | DC<1:0 | )>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _     | —     | _     | _     | —     | —     | xx                    | uu                         |  |

| 38Dh                                            | PWM6DCH |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | DC<9  | :0>   |       |       |       | XXXX XXXX             | uuuu uuuu                  |  |

| 38Eh                                            | PWM6CON | EN     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | OUT   | POL   | _     | _     | _     | —     | 0-00                  | 0-00                       |  |

| 38Fh<br><br>39Fh                                | -       |        | Lin         Lin <thlin< th=""> <thlin< th=""> <thlin< th=""></thlin<></thlin<></thlin<> |       |       |       |       |       |       |                       |                            |  |

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

| REGIST  | ER 5-7:                               | REVIS    | SIONID                  | : REVIS | SION ID | REGIS | STER |   |         |          |    |   |   |

|---------|---------------------------------------|----------|-------------------------|---------|---------|-------|------|---|---------|----------|----|---|---|

| R       | R                                     | R        | R                       | R       | R       | R     | R    | R | R       | R        | R  | R | R |

| 1       | 0                                     |          | MJRREV<5:0> MNRREV<5:0> |         |         |       |      |   |         |          |    |   |   |

| bit 13  | 13 bit 0                              |          |                         |         |         |       |      |   |         | bit 0    |    |   |   |

|         |                                       |          |                         |         |         |       |      |   |         |          |    |   |   |

| Legend: |                                       |          |                         |         |         |       |      |   |         |          |    |   |   |

|         | R = Read                              | able bit |                         |         |         |       |      |   |         |          |    |   |   |

|         | '0' = Bit is cleared '1' = Bit is set |          |                         |         |         |       |      |   | x = Bit | is unkno | wn |   |   |

| r       |                                       |          |                         |         |         |       |      |   |         |          |    |   |   |

bit 13-12 **Fixed Value**: Read-only bits These bits are fixed with value '10' for all devices included in this data sheet.

bit 11-6MJRREV<5:0>: Major Revision ID bits<br/>These bits are used to identify a major revision.bit 5-0MNRREV<5:0>: Minor Revision ID bits<br/>These bits are used to identify a minor revision.

© 2017 Microchip Technology Inc.

#### 8.4 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-out Reset (LPBOR) is an important part of the Reset subsystem. Refer to Figure 8-1 to see how the BOR and LPBOR interact with other modules.

The LPBOR is used to monitor the external VDD pin. When too low of a voltage is detected, the device is held in Reset.

# 8.4.1 ENABLING LPBOR

The LPBOR is controlled by the  $\overline{LPBOR}$  bit of the Configuration Word (Register 5-1). When the device is erased, the LPBOR module defaults to disabled.

#### 8.4.2 LPBOR MODULE OUTPUT

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. When this occurs, a register bit (BOR) is changed to indicate that a BOR Reset has occurred. The same bit is set for either the BOR or the LPBOR (refer to Register 8-3). This signal is OR'd with the output of the BOR module to provide the generic BOR signal, which goes to the PCON register and to the power control block. Refer to Figure 8-1 for the OR gate connections of the BOR and LPBOR Reset signals, which eventually generates one common BOR Reset.

# 8.5 MCLR

The  $\overline{\text{MCLR}}$  is an optional external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 8-2).

TABLE 8-2:

MCLR CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| x     | 1   | Enabled  |

# 8.5.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up. Refer to **Section 2.3 "Master Clear (MCLR) Pin"** for recommended MCLR connections.

The device has a noise filter in the MCLR Reset path. The filter will detect and ignore small pulses.

**Note:** A Reset does not drive the MCLR pin low.

# 8.5.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 14.1 "I/O Priorities"** for more information.

# 8.6 Windowed Watchdog Timer (WWDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period and the window is open. The TO and PD bits in the STATUS register and the WDT bit in PCON are changed to indicate a WDT Reset caused by the timer overflowing, and WDTWV bit in the PCON register is changed to indicate a WDT Reset caused by a window violation. See **Section 12.0 "Windowed Watchdog Timer (WWDT)"** for more information.

# 8.7 RESET Instruction

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON register will be set to '0'. See Table 8-4 for default conditions after a RESET instruction has occurred.

# 8.8 Stack Overflow/Underflow Reset

The device can reset when the Stack Overflows or Underflows. The STKOVF or STKUNF bits of the PCON register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 4.5.2** "**Overflow/Underflow Reset**" for more information.

# 8.9 Programming Mode Exit

Upon exit of In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) mode, the device will behave as if a POR had just occurred (the device does not reset upon run time self-programming/erase operations).

# 8.10 Power-up Timer

The Power-up Timer optionally delays device execution after a BOR or POR event. This timer is typically used to allow VDD to stabilize before allowing the device to start running.

The Power-up Timer is controlled by the  $\overrightarrow{\text{PWRTE}}$  bit of the Configuration Words.

The Power-up Timer provides a nominal 64 ms time out on POR or Brown-out Reset. The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in the Configuration Words. The Power-up Timer starts after the release of the POR and BOR. For additional information, refer to Application Note AN607, "*Power-up Trouble Shooting*" (DS00607).

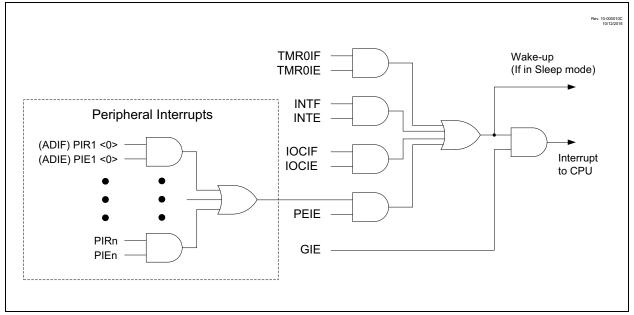

# **10.0 INTERRUPTS**

The interrupt feature allows certain events to preempt normal program flow. Firmware is used to determine the source of the interrupt and act accordingly. Some interrupts can be configured to wake the MCU from Sleep mode.

This chapter contains the following information for Interrupts:

- Operation

- Interrupt Latency

- Interrupts During Sleep

- INT Pin

- · Automatic Context Saving

Many peripherals produce interrupts. Refer to the corresponding chapters for details.

A block diagram of the interrupt logic is shown in Figure 10-1.

#### FIGURE 10-1: INTERRUPT LOGIC

| U-0          | U-0                 | R/W/HS-0/0           | R-0                    | U-0               | U-0                | U-0            | R/W/HS-0/0          |

|--------------|---------------------|----------------------|------------------------|-------------------|--------------------|----------------|---------------------|

| 00           |                     |                      | -                      |                   |                    | 00             | INTF <sup>(1)</sup> |

|              | - <u> </u>          |                      |                        |                   |                    |                |                     |

| bit 7        |                     |                      |                        |                   |                    |                | bit 0               |

| Legend:      |                     |                      |                        |                   |                    |                |                     |

| R = Read     | lable bit           | W = Writable b       | it                     | U = Unimplei      | mented bit, read   | as '0'         |                     |

| u = Bit is   | unchanged           | x = Bit is unkno     | wn                     | -n/n = Value      | at POR and BOF     | R/Value at all | other Resets        |

| '1' = Bit is | s set               | '0' = Bit is clear   | ed                     | HS= Hardwa        | re Set             |                |                     |

|              |                     |                      |                        |                   |                    |                |                     |

| bit 7-6      | Unimpleme           | nted: Read as '0'    |                        |                   |                    |                |                     |

| bit 5        | TMR0IF: Tir         | ner0 Overflow Inte   | errupt Flag            | bit               |                    |                |                     |

|              | 1 = Timer0          | register has over    | flowed (mu             | st be cleared in  | software)          |                |                     |

|              | 0 = Timer0          | ) register did not o | verflow                |                   |                    |                |                     |

| bit 4        | IOCIF: Inter        | rupt-on-Change Ir    | nterrupt Fla           | g bit (read-only) | )(2)               |                |                     |

|              |                     | more of the IOCA     |                        | egister bits are  | currently set, ind | icating an ena | abled edge was      |

|              |                     | ed by the IOC mo     |                        |                   |                    |                |                     |

|              |                     | of the IOCAF-IOC     | 0                      | bits are current  | ly set             |                |                     |

| bit 3-1      | Unimpleme           | nted: Read as '0'    |                        |                   |                    |                |                     |

| bit 0        | INTF: INT E         | xternal Interrupt F  | lag bit <sup>(1)</sup> |                   |                    |                |                     |

|              | 1 = The IN          | T external interru   | ot occurred            | (must be cleare   | ed in software)    |                |                     |

|              | 0 = The IN          | T external interru   | ot did not o           | ccur              |                    |                |                     |

| Note 1:      | The External Inte   | rrupt GPIO pin is    | selected by            | / INTPPS (Regi    | ster 15-1).        |                |                     |

| 2:           | The IOCIF bit is t  | he logical OR of a   | all the IOCA           | F-IOCEF flags.    | Therefore, to cle  | ear the IOCIF  | <sup>-</sup> flag,  |

|              |                     | are must clear all   |                        |                   |                    |                | -                   |

| <b>-</b>     |                     |                      |                        |                   |                    |                |                     |

| Note:        | Interrupt flag bits | are set when an ir   | nterrupt               |                   |                    |                |                     |

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state     |

|       | of its corresponding enable bit or the        |

|       | Global Enable bit, GIE, of the INTCON         |

|       | register. User software should ensure the     |

|       | appropriate interrupt flag bits are clear     |

|       | prior to enabling an interrupt.               |

© 2017 Microchip Technology Inc.

# PIC16(L)F15313/23

| R/W-0/u          | R/W/HC/HS-0/0                                                                                                          | R/W-0/0            | R/W-0/0        | U-0                    | R/W-0/0         | R/W-0/0         | R/W-0/0         |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--------------------|----------------|------------------------|-----------------|-----------------|-----------------|--|--|

| IDLEN            | DOZEN <sup>(1,2)</sup>                                                                                                 | ROI                | DOE            | —                      |                 | DOZE<2:0>       |                 |  |  |

| bit 7            |                                                                                                                        |                    |                |                        |                 |                 | bit 0           |  |  |

| Legend:          |                                                                                                                        |                    |                |                        |                 |                 |                 |  |  |

| R = Readable     | bit                                                                                                                    | W = Writable       | bit            | U = Unimple            | emented bit, re | ead as '0'      |                 |  |  |

| u = Bit is unch  | anged                                                                                                                  | x = Bit is unkn    | iown           | -n/n = Value<br>Resets | e at POR and I  | BOR/Value at a  | all other       |  |  |

| '1' = Bit is set |                                                                                                                        | '0' = Bit is clea  | ared           |                        |                 |                 |                 |  |  |

| bit 7            | <b>IDLEN:</b> Idle Enal<br>1 = A SLEEP ins<br>0 = A SLEEP ins                                                          | struction inhibits |                |                        |                 | ock(s)          |                 |  |  |

| bit 6            | <b>DOZEN:</b> Doze E<br>1 = The CPU ex<br>0 = The CPU ex                                                               | ecutes instruct    |                |                        |                 | ration)         |                 |  |  |

| bit 5            | <ul> <li><b>ROI:</b> Recover-on</li> <li>1 = Entering the operation.</li> <li>0 = Interrupt ent</li> </ul>             | Interrupt Servi    |                | R) makes DO            | ZEN = 0 bit, b  | ringing the CPl | J to full-speed |  |  |

| bit 4            | <b>DOE:</b> Doze on E<br>1 = Executing R<br>0 = RETFIE doe                                                             | ETFIE makes        |                | ringing the C          | PU to reduced   | l speed operati | ion.            |  |  |

| bit 3            | Unimplemented                                                                                                          | I: Read as '0'     |                |                        |                 |                 |                 |  |  |

| bit 2-0          | <b>DOZE&lt;2:0&gt;:</b> Rat<br>111 =1:256<br>110 =1:128<br>101 =1:64<br>100 =1:32<br>011 =1:16<br>010 =1:8<br>001 =1:4 | tio of CPU Insti   | ruction Cycles | to Peripheral          | I Instruction C | ycles           |                 |  |  |

- **Note 1:** When ROI = 1 or DOE = 1, DOZEN is changed by hardware interrupt entry and/or exit.

- 2: Entering ICD overrides DOZEN, returning the CPU to full execution speed; this bit is not affected.

| VALC               | 20                         |

|--------------------|----------------------------|

| Desired Input Pin  | Value to Write to Register |

| RA0                | 0x00                       |

| RA1                | 0x01                       |

| RA2                | 0x02                       |

| RA3                | 0x03                       |

| RA4                | 0x04                       |

| RA5                | 0x05                       |

| RC0 <sup>(1)</sup> | 0x10                       |

| RC1 <sup>(1)</sup> | 0x11                       |

| RC2 <sup>(1)</sup> | 0x12                       |

| RC3 <sup>(1)</sup> | 0x13                       |

| RC4 <sup>(1)</sup> | 0x14                       |

| RC5 <sup>(1)</sup> | 0x15                       |

#### TABLE 15-3: PPS INPUT REGISTER VALUES

Note 1: Present on PIC16(L)F15323 only.

| U-0                                                               | U-0 | R/W/HS-0/0   | R/W/HS-0/0     | R/W/HS-0/0                         | R/W/HS-0/0       | R/W/HS-0/0            | R/W/HS-0/0            |  |  |

|-------------------------------------------------------------------|-----|--------------|----------------|------------------------------------|------------------|-----------------------|-----------------------|--|--|

| —                                                                 | —   | IOCAF5       | IOCAF4         | IOCAF3                             | IOCAF2           | IOCAF1 <sup>(1)</sup> | IOCAF0 <sup>(1)</sup> |  |  |

| bit 7                                                             |     |              |                |                                    |                  |                       | bit 0                 |  |  |

|                                                                   |     |              |                |                                    |                  |                       |                       |  |  |

| Legend:                                                           |     |              |                |                                    |                  |                       |                       |  |  |

| R = Readable b                                                    | bit | W = Writable | bit            | U = Unimplemented bit, read as '0' |                  |                       |                       |  |  |

| u = Bit is unchanged x = Bit is unknown                           |     |              | -n/n = Value a | at POR and BO                      | R/Value at all o | ther Resets           |                       |  |  |

| '1' = Bit is set '0' = Bit is cleared HS - Bit is set in hardware |     |              |                |                                    |                  |                       |                       |  |  |

# REGISTER 17-3: IOCAF: INTERRUPT-ON-CHANGE PORTA FLAG REGISTER

bit 7-6 Unimplemented: read as '0'

bit 5-0 **IOCAF<5:0>:** Interrupt-on-Change PORTA Flag bits

- 1 = An enabled change was detected on the associated pin.

- Set when IOCAPx = 1 and a rising edge was detected on RAx, or when IOCANx = 1 and a falling edge was detected on RAx.

- 0 = No change was detected, or the user cleared the detected change.

**Note 1:** If the debugger is enabled, these bits are not available for use.

# 18.3 Register Definitions: FVR Control

#### REGISTER 18-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0     | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|-------------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAFVR<1:0> |         | ADFV    | R<1:0>  |

| bit 7   |                       |                     |                      |             |         |         | bit 0   |

| Legend:                                                      |                                                                                                                                                                                                                                   |                                                                                                                                                         |                                                                                             |  |  |  |  |

|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--|--|--|--|

| R = Readable bit<br>u = Bit is unchanged<br>'1' = Bit is set |                                                                                                                                                                                                                                   | W = Writable bit                                                                                                                                        | U = Unimplemented bit, read as '0'<br>-n/n = Value at POR and BOR/Value at all other Resets |  |  |  |  |

|                                                              |                                                                                                                                                                                                                                   | x = Bit is unknown                                                                                                                                      |                                                                                             |  |  |  |  |

|                                                              |                                                                                                                                                                                                                                   | '0' = Bit is cleared                                                                                                                                    | q = Value depends on condition                                                              |  |  |  |  |

| bit 7                                                        | 1 = Fixed                                                                                                                                                                                                                         | Fixed Voltage Reference Ena<br>Voltage Reference is enable<br>Voltage Reference is disabl                                                               | ed                                                                                          |  |  |  |  |

| bit 6                                                        | <b>FVRRDY:</b> Fixed Voltage Reference Ready Flag bit <sup>(1)</sup><br>1 = Fixed Voltage Reference output is ready for use<br>0 = Fixed Voltage Reference output is not ready or not enabled                                     |                                                                                                                                                         |                                                                                             |  |  |  |  |

| bit 5                                                        | <b>TSEN:</b> Temperature Indicator Enable bit <sup>(3)</sup><br>1 = Temperature Indicator is enabled<br>0 = Temperature Indicator is disabled                                                                                     |                                                                                                                                                         |                                                                                             |  |  |  |  |

| bit 4                                                        | <b>TSRNG:</b> Temperature Indicator Range Selection bit <sup>(3)</sup><br>1 = Temperature in High Range Vout = 3VT<br>0 = Temperature in Low Range Vout = 2VT                                                                     |                                                                                                                                                         |                                                                                             |  |  |  |  |

| bit 3-2                                                      | 11 = Com<br>10 = Com<br>01 = Com                                                                                                                                                                                                  | <1:0>: Comparator FVR Buff<br>parator FVR Buffer Gain is 4<br>parator FVR Buffer Gain is 2<br>parator FVR Buffer Gain is 1<br>parator FVR Buffer is off | x, (4.096V) <sup>(2)</sup><br>x, (2.048V) <sup>(2)</sup>                                    |  |  |  |  |

| bit 1-0                                                      | ADFVR<1:0>: ADC FVR Buffer Gain Selection bit<br>11 = ADC FVR Buffer Gain is 4x, $(4.096V)^{(2)}$<br>10 = ADC FVR Buffer Gain is 2x, $(2.048V)^{(2)}$<br>01 = ADC FVR Buffer Gain is 1x, $(1.024V)$<br>00 = ADC FVR Buffer is off |                                                                                                                                                         |                                                                                             |  |  |  |  |

| 2: 1                                                         | •                                                                                                                                                                                                                                 | Reference output cannot exc                                                                                                                             | eed VDD.<br>Module" for additional information                                              |  |  |  |  |

3: See Section 19.0 "Temperature Indicator Module" for additional information.

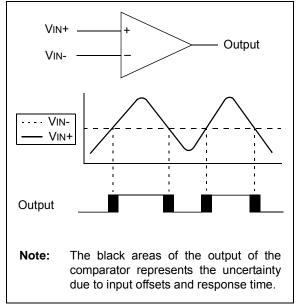

# 23.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- · Programmable input selection

- Selectable voltage reference

- Programmable output polarity

- Rising/falling output edge interrupts

- CWG1 Auto-shutdown source

#### 23.1 Comparator Overview

A single comparator is shown in Figure 23-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available are shown in Table 23-1.

TABLE 23-1:AVAILABLE COMPARATORS

| Device         | C1 | C2 |

|----------------|----|----|

| PIC16(L)F15313 | •  |    |

| PIC16(L)F15323 | •  | •  |

#### FIGURE 23-1:

#### SINGLE COMPARATOR

# 27.4 Timer2 Interrupt

Timer2 can also generate a device interrupt. The interrupt is generated when the postscaler counter matches one of 16 postscale options (from 1:1 through 1:16), which are selected with the postscaler control bits, OUTPS<3:0> of the T2CON register. The interrupt is enabled by setting the TMR2IE interrupt enable bit of the PIE4 register. Interrupt timing is illustrated in Figure 27-3.

#### FIGURE 27-3: TIMER2 PRESCALER, POSTSCALER, AND INTERRUPT TIMING DIAGRAM

|                  | Rev. 10-00205A<br>4/7/2016                               |

|------------------|----------------------------------------------------------|

| CKPS             | 0b010                                                    |

|                  |                                                          |

| PRx              | 1                                                        |

| OUTPS            | 0b0001                                                   |

|                  |                                                          |

| TMRx_clk         |                                                          |

| TMRx             | $\begin{array}{c c c c c c c c c c c c c c c c c c c $   |

| TMRx_postscaled_ |                                                          |

| TMRxIF           | (1) (1)                                                  |

| Note 1:<br>2:    | Synchronization may take as many as 2 instruction cycles |

# 27.5 Operation Examples

Unless otherwise specified, the following notes apply to the following timing diagrams:

- Both the prescaler and postscaler are set to 1:1 (both the CKPS and OUTPS bits in the TxCON register are cleared).

- The diagrams illustrate any clock except Fosc/4 and show clock-sync delays of at least two full cycles for both ON and Timer2\_ers. When using Fosc/4, the clock-sync delay is at least one instruction period for Timer2\_ers; ON applies in the next instruction period.

- The PWM Duty Cycle and PWM output are illustrated assuming that the timer is used for the PWM function of the CCP module as described in **Section 28.0 "Capture/Compare/PWM Modules"**. The signals are not a part of the Timer2 module.

#### 27.5.1 SOFTWARE GATE MODE

This mode corresponds to legacy Timer2 operation. The timer increments with each clock input when ON = 1 and does not increment when ON = 0. When the TMRx count equals the PRx period count the timer resets on the next clock and continues counting from 0. Operation with the ON bit software controlled is illustrated in Figure 27-4. With PRx = 5, the counter advances until TMRx = 5, and goes to zero with the next clock.

| REGISTER 27-4: | T2RST: TIMER2 EXTERNAL RESET SIGNAL SELECTION REGISTER |

|----------------|--------------------------------------------------------|

|----------------|--------------------------------------------------------|

| U-0                                  | U-0                       | U-0               | U-0            | R/W-0/0                                               | R/W-0/0   | R/W-0/0 | R/W-0/0 |  |  |

|--------------------------------------|---------------------------|-------------------|----------------|-------------------------------------------------------|-----------|---------|---------|--|--|

| _                                    |                           |                   | —              | RSEL<3:0>                                             |           |         |         |  |  |

| bit 7                                |                           |                   |                |                                                       |           |         | bit 0   |  |  |

|                                      |                           |                   |                |                                                       |           |         | 1       |  |  |

| Legend:                              |                           |                   |                |                                                       |           |         |         |  |  |

| R = Readable                         | e bit                     | W = Writable      | bit            | U = Unimplemented bit, read as '0'                    |           |         |         |  |  |

| u = Bit is unchanged                 |                           | x = Bit is unkr   | iown           | -n/n = Value at POR and BOR/Value at all other Resets |           |         |         |  |  |

| '1' = Bit is set                     |                           | '0' = Bit is clea | ared           |                                                       |           |         |         |  |  |

|                                      |                           |                   |                |                                                       |           |         |         |  |  |

| bit 7-4                              | Unimplemen                | ted: Read as '    | 0'             |                                                       |           |         |         |  |  |

| bit 3-0                              | RSEL<3:0>:                | Timer2 Externa    | al Reset Signa | I Source Select                                       | tion bits |         |         |  |  |

|                                      | 1111 <b>= Rese</b>        | rved              |                |                                                       |           |         |         |  |  |

|                                      | 1101 <b>= LC4</b> _       |                   |                |                                                       |           |         |         |  |  |

|                                      | 1100 = LC3_               |                   |                |                                                       |           |         |         |  |  |

| 1011 = LC2_out                       |                           |                   |                |                                                       |           |         |         |  |  |

| 1010 = LC1_out<br>1001 = ZCD1_output |                           |                   |                |                                                       |           |         |         |  |  |

|                                      | 1001 = 200<br>1000 = C201 |                   |                |                                                       |           |         |         |  |  |

| $0111 = C1OUT_sync$                  |                           |                   |                |                                                       |           |         |         |  |  |

| 0110 = PWM6 out                      |                           |                   |                |                                                       |           |         |         |  |  |

| 0101 = PWM5 out                      |                           |                   |                |                                                       |           |         |         |  |  |

| $0100 = PWM4_out$                    |                           |                   |                |                                                       |           |         |         |  |  |

|                                      | 0011 = PWM                | 13_out            |                |                                                       |           |         |         |  |  |

| 0010 = CCP2_out                      |                           |                   |                |                                                       |           |         |         |  |  |

|                                      | 0001 = CCP                | -                 |                |                                                       |           |         |         |  |  |

|                                      | 0000 <b>= T2INI</b>       | PPS               |                |                                                       |           |         |         |  |  |

**Note 1:** Present on PIC16(L)F15323 only. Reserved for the PIC16(L)F15313.

| Name     | Bit 7       | Bit 6                                        | Bit 5 | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | Register<br>on Page |

|----------|-------------|----------------------------------------------|-------|-------|------------|-------|--------|--------|---------------------|

| CCP1CON  | EN          | _                                            | OUT   | FMT   |            | MODE  | =<3:0> |        | 306                 |

| CCP2CON  | EN          | _                                            | OUT   | FMT   |            | MODE  | =<3:0> |        | 306                 |

| INTCON   | GIE         | PEIE                                         | _     | —     | —          | —     | —      | INTEDG | 121                 |

| PIE1     | OSFIE       | CSWIE                                        | _     | —     | —          | —     | _      | ADIE   | 123                 |

| PIR1     | OSFIF       | CSWIF                                        | _     |       | —          | —     | _      | ADIF   | 131                 |

| PR2      | Timer2 Modu | Timer2 Module Period Register                |       |       |            |       |        | 280*   |                     |

| TMR2     | Holding Reg | Holding Register for the 8-bit TMR2 Register |       |       |            |       | 280*   |        |                     |

| T2CON    | ON          | CKPS<2:0>                                    |       |       | OUTPS<3:0> |       |        |        | 295                 |

| T2CLKCON | —           |                                              |       | _     | CS<3:0>    |       |        |        | 294                 |

| T2RST    | _           |                                              |       | _     | RSEL<3:0>  |       |        |        | 297                 |

| T2HLT    | PSYNC       | CKPOL CKSYNC                                 |       |       | MODE<4:0>  |       |        |        | 296                 |

#### TABLE 27-2: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER2

Legend: — = unimplemented location, read as '0'. Shaded cells are not used for Timer2 module.

\* Page provides register information.

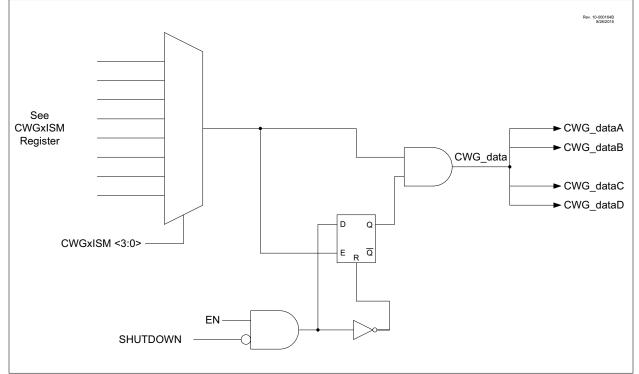

#### 30.1.4 STEERING MODES

In Steering modes, the data input can be steered to any or all of the four CWG output pins. In Synchronous Steering mode, changes to steering selection registers take effect on the next rising input.

In Non-Synchronous mode, steering takes effect on the next instruction cycle. Additional details are provided in **Section 30.9 "CWG Steering Mode"**.

# 30.2 Clock Source

The CWG module allows the following clock sources to be selected:

- Fosc (system clock)

- HFINTOSC (16 MHz only)

The clock sources are selected using the CS bit of the CWG1CLKCON register.

# 33.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 9.2.2.2** "Internal Oscillator Frequency **Adjustment**" for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 33.3.1** "**Auto-Baud Detect**"). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

#### 33.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

| Note: | If the device is configured as a slave and  |

|-------|---------------------------------------------|

|       | the TX/CK function is on an analog pin, the |

|       | corresponding ANSEL bit must be cleared.    |

#### 33.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RC1REG is read to access the FIFO. When this happens the OERR bit of the RC1STA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RC1REG. If the overrun occurred when the CREN bit is set then the error condition is cleared by either clearing the CREN bit of the RC1STA register or by clearing the SPEN bit which resets the EUSART.

#### 33.4.1.8 Receiving 9-bit Characters

The EUSART supports 9-bit character reception. When the RX9 bit of the RC1STA register is set the EUSART will shift nine bits into the RSR for each character received. The RX9D bit of the RC1STA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RC1REG.

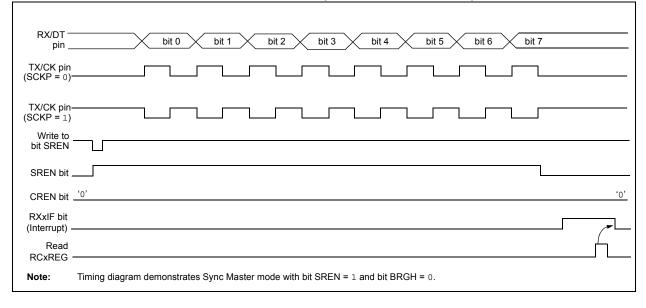

# 33.4.1.9 Synchronous Master Reception Set-up:

- 1. Initialize the SP1BRGH, SP1BRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RX1IE bit of the PIE3 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- Interrupt flag bit RX1IF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RX1IE was set.

- 9. Read the RC1STA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RC1REG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RC1STA register or by clearing the SPEN bit which resets the EUSART.

#### FIGURE 33-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)

# PIC16(L)F15313/23

#### **37.4** AC Characteristics