Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                             |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 224 x 8                                                                     |

| RAM Size                   | 256 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                             |

| Supplier Device Package    | 14-TSSOP                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16lf15323-i-st |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

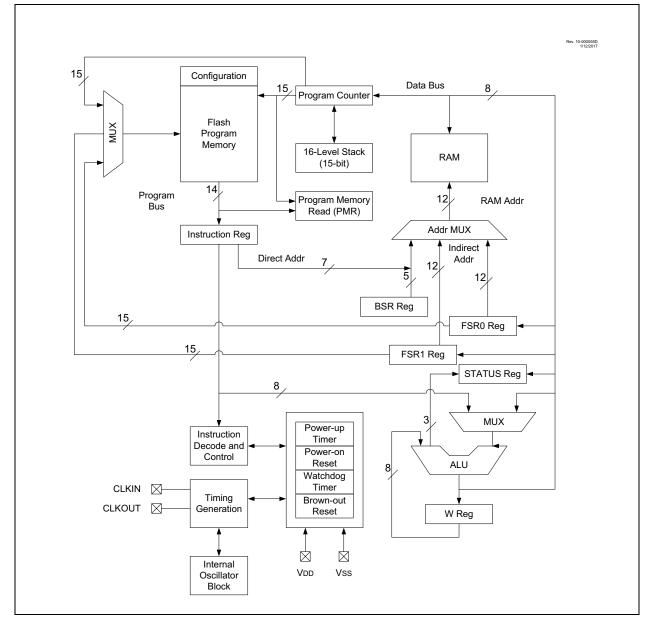

### 3.0 ENHANCED MID-RANGE CPU

This family of devices contains an enhanced mid-range 8-bit CPU core. The CPU has 48 instructions. Interrupt capability includes automatic context saving.

FIGURE 3-1: CORE DATA PATH DIAGRAM

The hardware stack is 16-levels deep and has Overflow and Underflow Reset capability. Direct, Indirect, and Relative Addressing modes are available. Two File Select Registers (FSRs) provide the ability to read program and data memory.

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

| Address           | Name                                            | Bit 7     Bit 6     Bit 5     Bit 4     Bit 3     Bit 2     Bit 1     Bit 0     Value on:<br>POR, BOR     Value on:<br>MCLR |  |  |  |  |  |  |  |  |  |  |  |

|-------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Bank 8-10         | ank 8-10                                        |                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

|                   | CPU CORE REGISTERS; see Table 4-3 for specifics |                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

| x0Ch/<br>x8Ch<br> | /8Ch                                            |                                                                                                                             |  |  |  |  |  |  |  |  |  |  |  |

| IABLE 4                 | -10: SPEC | AL FUNCTION | REGISTER | SUIVIIVIAR I                  | DANKS U-      |                      |           | 1         |         |                       | T.                         |

|-------------------------|-----------|-------------|----------|-------------------------------|---------------|----------------------|-----------|-----------|---------|-----------------------|----------------------------|

| Address                 | Name      | Bit 7       | Bit 6    | Bit 5                         | Bit 4         | Bit 3                | Bit 2     | Bit 1     | Bit 0   | Value on:<br>POR, BOR | V <u>alue o</u> n:<br>MCLR |

| Bank 17                 |           |             |          |                               |               |                      |           |           |         |                       |                            |

|                         |           |             |          | CPU COF                       | RE REGISTERS; | see Table 4-3 for    | specifics |           |         |                       |                            |

| 88Ch                    | CPUDOZE   | IDLEN       | DOZEN    | ROI                           | DOE           | —                    | DOZE2     | DOZE1     | DOZE0   | 0000 -000             | u000 -000                  |

| 88Dh                    | OSCCON1   | _           |          | NOSC<2:0> NDIV<3:0> -qqq 0000 |               |                      | -qqq 0000 | -ddd 0000 |         |                       |                            |

| 88Eh                    | OSCCON2   | —           |          | COSC<2:0>                     |               |                      | CD        | IV<3:0>   |         | -বর্বর বর্ববর         | -বর্বর বর্ববর              |

| 88Fh                    | OSCCON3   | CSWHOLD     | _        | _                             | ORDY          | NOSCR                | —         | —         | —       | 00 0                  | 00 0                       |

| 890h                    | OSCSTAT   | EXTOR       | HFOR     | MFOR                          | LFOR          | —                    | ADOR      | —         | PLLR    | d000 -d-0             | বর্ববুর -ব-ব               |

| 891h                    | OSCEN     | EXTOEN      | HFOEN    | MFOEN                         | LFOEN         | —                    | ADOEN     | —         | —       | 0000 -0               | 0000 -0                    |

| 892h                    | OSCTUNE   | _           | _        |                               | •             | HFT                  | UN<5:0>   |           |         | 10 0000               | 10 0000                    |

| 893h                    | OSCFRQ    | —           | _        | _                             | —             | —                    |           | HFFRQ<2:0 | >       | ddd                   | ddd                        |

| 894h                    | _         |             |          |                               | Unimpler      | mented               |           |           |         | —                     | —                          |

| 895h                    | CLKRCON   | CLKREN      | _        | _                             | CLKRE         | OC<1:0> CLKRDIV<2:0> |           |           | 0x xxxx | 0u uuuu               |                            |

| 896h                    | CLKRCLK   | _           | _        | _                             | —             |                      | CLKR      | CLK<3:0>  |         | 0000                  | 0000                       |

| 897h      Unimplemented |           |             |          |                               |               |                      | -         | _         |         |                       |                            |

### TABLE 4-10: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-63 (CONTINUED)

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

### TABLE 5-1: BOOT BLOCK SIZE BITS

| BBEN | BBSIZE<2:0> | Actual Boot Block Size<br>User Program Memory Size (words) | Last Boot Block<br>Memory Access |

|------|-------------|------------------------------------------------------------|----------------------------------|

| 1    | xxx         | 0                                                          | -                                |

| 0    | 111         | 512                                                        | 01FFh                            |

| 0    | 110-000     | 1024                                                       | 03FFh                            |

**Note:** The maximum boot block size is half the user program memory size. All selections higher than the maximum are set to half size. For example, all BBSIZE = 000 - 100 produce a boot block size of 4kW on a 8kW device.

## PIC16(L)F15313/23

| R-q/q                   | R-q/q                                                                                                                            | R-q/q                                                                                                  | R-q/q                                                                                                         | U-0                                                        | R-q/q              | U-0                | R-q/q    |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------------------|--------------------|----------|

| EXTOR                   | HFOR                                                                                                                             | MFOR                                                                                                   | LFOR                                                                                                          | _                                                          | ADOR               |                    | PLLR     |

| bit 7                   |                                                                                                                                  |                                                                                                        | ·                                                                                                             |                                                            |                    |                    | bit 0    |

| Legend:                 |                                                                                                                                  |                                                                                                        |                                                                                                               |                                                            |                    |                    |          |

| R = Readable b          | oit                                                                                                                              | W = Writable b                                                                                         | it                                                                                                            | U = Unimplem                                               | ented bit, read as | ; '0'              |          |

| u = Bit is uncha        | anged                                                                                                                            | x = Bit is unkno                                                                                       | own                                                                                                           | -n/n = Value at                                            | POR and BOR/V      | /alue at all other | r Resets |

| '1' = Bit is set        |                                                                                                                                  | '0' = Bit is clea                                                                                      | red                                                                                                           |                                                            |                    |                    |          |

| bit 6<br>bit 5<br>bit 4 | 0 = The oscil<br><b>HFOR:</b> HFINT(<br>1 = The oscil<br>0 = The oscil<br><b>MFOR:</b> MFINT<br>1 = The oscill<br>0 = The oscill | DSC Oscillator F<br>llator is ready to<br>llator is not enab<br>OSC Oscillator I<br>ator is ready to I | eled, or is not ye<br>Ready bit<br>be used<br>eled, or is not ye<br>Ready bit<br>be used<br>ed, or is not yet | t ready to be use<br>t ready to be use<br>ready to be used | d.                 |                    |          |

|                         |                                                                                                                                  | llator is ready to<br>lator is not enab                                                                |                                                                                                               | ready to be used                                           | d.                 |                    |          |

| bit 3                   | Unimplemente                                                                                                                     | ed: Read as '0'                                                                                        |                                                                                                               |                                                            |                    |                    |          |

| bit 2                   | 1 = The oscil                                                                                                                    | escillator Ready<br>llator is ready to<br>lator is not enab                                            | be used                                                                                                       | ready to be used                                           | d.                 |                    |          |

| bit 1                   | Unimplemente                                                                                                                     | ed: Read as '0'                                                                                        |                                                                                                               |                                                            |                    |                    |          |

| bit 0                   | PLLR: PLL is F<br>1 = The PLL                                                                                                    | Ready bit<br>is ready to be u                                                                          | sed                                                                                                           |                                                            |                    |                    |          |

0 = The PLL is not enabled, the required input source is not ready, or the PLL is not locked.

| U-0                                 | R/W-0/0                                                                                                    | R/W-0/0                                                                         | R/W/HC-0/0                                                                  | R/W/HC-x/q                                   | R/W-0/0                       | R/S/HC-0/0                              | R/S/HC-0/0         |

|-------------------------------------|------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----------------------------------------------|-------------------------------|-----------------------------------------|--------------------|

| _                                   | NVMREGS                                                                                                    | LWLO                                                                            | FREE                                                                        | WRERR <sup>(1,2,3)</sup>                     | WREN                          | WR <sup>(4,5,6)</sup>                   | RD                 |

| oit 7                               | ·                                                                                                          |                                                                                 |                                                                             |                                              |                               | ÷                                       | bit (              |

|                                     |                                                                                                            |                                                                                 |                                                                             |                                              |                               |                                         |                    |

| Legend:                             |                                                                                                            |                                                                                 |                                                                             |                                              |                               |                                         |                    |

| R = Readable b                      | bit                                                                                                        | W = Writable b                                                                  | it                                                                          | U = Unimpleme                                | nted bit, read as             | s 'O'                                   |                    |

| S = Bit can only                    | / be set                                                                                                   | x = Bit is unkno                                                                | own                                                                         | -n/n = Value at                              | POR and BOR/\                 | /alue at all other I                    | Resets             |

| 1' = Bit is set                     |                                                                                                            | '0' = Bit is clear                                                              | red                                                                         | HC = Bit is clea                             | red by hardware               | •                                       |                    |

|                                     |                                                                                                            |                                                                                 |                                                                             |                                              |                               |                                         |                    |

| bit 7                               | Unimplemente                                                                                               | ed: Read as '0'                                                                 |                                                                             |                                              |                               |                                         |                    |

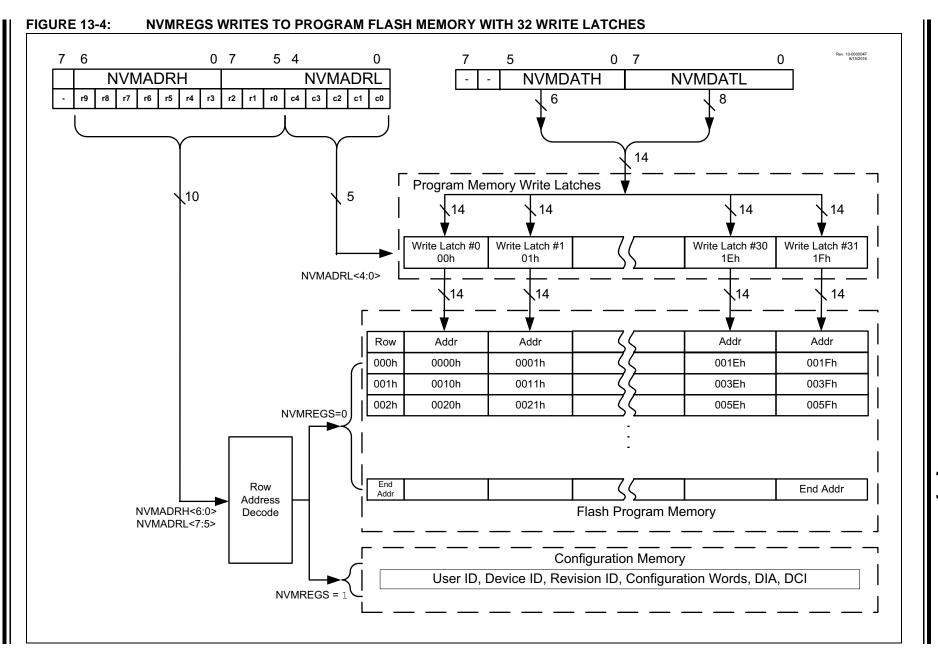

| bit 6                               |                                                                                                            |                                                                                 |                                                                             | and Device ID Re                             | gisters                       |                                         |                    |

| bit 5                               | When FREE =<br>1 = The next \                                                                              | WR command up<br>WR command w                                                   | odates the write                                                            |                                              | d within the row;             | no memory oper                          | ation is initiated |

| bit 4                               | 1 = Performs<br>address is                                                                                 | GS:NVMADR po                                                                    | on with the nex<br>s) to prepare for                                        | t WR command;<br>writing.                    | the 32-word pse               | udo-row containi                        | ng the indicate    |

| bit 3                               | WRERR: Progr<br>This bit is norm<br>1 = A write op<br>NVMADR                                               | ram/Erase Error<br>nally set by hardv                                           | Flag bit <sup>(1,2,3)</sup><br>vare.<br>rrupted by a Re<br>-protected addre | set, interrupted u                           | inlock sequence               | , or WR was writ                        | ten to one whil    |

| bit 2                               | 1 = Allows pro                                                                                             | m/Erase Enable<br>ogram/erase cycl<br>ogramming/eras                            | es                                                                          | -lash                                        |                               |                                         |                    |

| bit 1                               | WR: Write Con<br>When NVMRE<br>1 = Initiates th                                                            |                                                                                 | nts to a PFM loc<br>cated by Table 1                                        | <u>ation</u> :<br>3-4                        |                               |                                         |                    |

| oit O                               | <b>RD:</b> Read Coni<br>1 = Initiates a<br>bit is clear                                                    | trol bit <sup>(7)</sup><br>read at address                                      | = NVMADR1, ar<br>eration is comple                                          | nd loads data to N<br>ete. The bit can o     |                               | akes one instructi<br>leared) in softwa |                    |

| 2: Bit<br>3: Bit<br>4: Thi<br>5: Op | is undefined while<br>must be cleared b<br>may be written to<br>s bit can only be s<br>erations are self-t | by software; hard<br>'1' by software i<br>set by following t<br>imed, and the W | n order to imple<br>he unlock seque<br>R bit is cleared                     | ment test sequen<br>ence of <b>Section</b> 1 | 13.3.2 "NVM Un<br>n complete. | lock Sequence"                          |                    |

### REGISTER 13-5: NVMCON1: NONVOLATILE MEMORY CONTROL 1 REGISTER

6: Once a write operation is initiated, setting this bit to zero will have no effect.

### 15.3 Bidirectional Pins

PPS selections for peripherals with bidirectional signals on a single pin must be made so that the PPS input and PPS output select the same pin. Peripherals that have bidirectional signals include:

- EUSART (synchronous operation)

- MSSP (I<sup>2</sup>C)

- The I<sup>2</sup>C SCLx and SDAx functions can be Note: remapped through PPS. However, only the RB1, RB2, RC3 and RC4 pins have the I<sup>2</sup>C and SMBus specific input buffers implemented (I<sup>2</sup>C mode disables INLVL and sets thresholds that are specific for  $I^2C$ ). If the SCLx or SDAx functions are mapped to some other pin (other than RB1, RB2, RC3 or RC4), the general purpose TTL or ST input buffers (as configured based on INLVL register setting) will be used instead. In most applications, it is therefore recommended only to map the SCLx and SDAx pin functions to the RB1, RB2, RC3 or RC4 pins.

### 15.4 PPS Lock

The PPS includes a mode in which all input and output selections can be locked to prevent inadvertent changes. PPS selections are locked by setting the PPSLOCKED bit of the PPSLOCK register. Setting and clearing this bit requires a special sequence as an extra precaution against inadvertent changes. Examples of setting and clearing the PPSLOCKED bit are shown in Example 15-1.

### EXAMPLE 15-1: PPS LOCK/UNLOCK SEQUENCE

| ; | suspend interrupts                     |

|---|----------------------------------------|

|   | BCF INTCON, GIE                        |

| ; | BANKSEL PPSLOCK ; set bank             |

| ; | required sequence, next 5 instructions |

|   | MOVLW 0x55                             |

|   | MOVWF PPSLOCK                          |

|   | MOVLW 0xAA                             |

|   | MOVWF PPSLOCK                          |

| ; | Set PPSLOCKED bit to disable writes or |

| ; | Clear PPSLOCKED bit to enable writes   |

|   | BSF PPSLOCK, PPSLOCKED                 |

| ; | restore interrupts                     |

|   | BSF INTCON, GIE                        |

### 15.5 PPS Permanent Lock

The PPS can be permanently locked by setting the PPS1WAY Configuration bit. When this bit is set, the PPSLOCKED bit can only be cleared and set one time after a device Reset. This allows for clearing the PPSLOCKED bit so that the input and output selections can be made during initialization. When the PPSLOCKED bit is set after all selections have been made, it will remain set and cannot be cleared until after the next device Reset event.

### 15.6 Operation During Sleep

PPS input and output selections are unaffected by Sleep.

### 15.7 Effects of a Reset

A device Power-on-Reset (POR) clears all PPS input and output selections to their default values (Permanent Lock Removed). All other Resets leave the selections unchanged. Default input selections are shown in Table 15-1 and Table 15-2.

## TABLE 15-4:PPS OUTPUT SIGNAL<br/>ROUTING OPTIONS<br/>(PIC16(L)F15313)

| Output Signal | RxyPPS Register | Remappable to<br>Pins of PORTx |  |

|---------------|-----------------|--------------------------------|--|

| Name          | Value           | PIC16(L)F15313                 |  |

|               |                 | PORTA                          |  |

| CLKR          | 0x1B            | •                              |  |

| NCO10UT       | 0x1A            | •                              |  |

| TMR0          | 0x19            | •                              |  |

| SDO1/SDA1     | 0x16            | •                              |  |

| SCK1/SCL1     | 0x15            | •                              |  |

| C1OUT         | 0x13            | •                              |  |

| DT1           | 0x10            | •                              |  |

| TX1/CK1       | 0x0F            | •                              |  |

| PWM6OUT       | 0x0E            | •                              |  |

| PWM5OUT       | 0x0D            | •                              |  |

| PWM4OUT       | 0x0C            | •                              |  |

| PWM3OUT       | 0x0B            | •                              |  |

| CCP2          | 0x0A            | •                              |  |

| CCP1          | 0x09            | •                              |  |

| CWG1D         | 0x08            | •                              |  |

| CWG1C         | 0x07            | •                              |  |

| CWG1B         | 0x06            | •                              |  |

| CWG1A         | 0x05            | •                              |  |

| CLC4OUT       | 0x04            | •                              |  |

| CLC3OUT       | 0x03            | •                              |  |

| CLC2OUT       | 0x02            | •                              |  |

| CLC10UT       | 0x01            | •                              |  |

# TABLE 15-5:PPS OUTPUT SIGNAL<br/>ROUTING OPTIONS<br/>(PIC16(L)F15323)

| Output      | RxyPPS<br>Register |                | le to Pins of<br>RTx |  |

|-------------|--------------------|----------------|----------------------|--|

| Signal Name | Value              | PIC16(L)F15323 |                      |  |

|             |                    | PORTA          | PORTC                |  |

| CLKR        | 0x1B               | •              | •                    |  |

| NCO10UT     | 0x1A               | •              | •                    |  |

| TMR0        | 0x19               | •              | •                    |  |

| SDO1/SDA1   | 0x16               | •              | •                    |  |

| SCK1/SCL1   | 0x15               | •              | •                    |  |

| C2OUT       | 0x14               | •              | •                    |  |

| C10UT       | 0x13               | •              | •                    |  |

| DT1         | 0x10               | •              | •                    |  |

| TX1/CK1     | 0x0F               | •              | •                    |  |

| PWM6OUT     | 0x0E               | •              | •                    |  |

| PWM5OUT     | 0x0D               | •              | •                    |  |

| PWM4OUT     | 0x0C               | •              | •                    |  |

| PWM3OUT     | 0x0B               | •              | •                    |  |

| CCP2        | 0x0A               | •              | •                    |  |

| CCP1        | 0x09               | •              | •                    |  |

| CWG1D       | 0x08               | •              | •                    |  |

| CWG1C       | 0x07               | •              | •                    |  |

| CWG1B       | 0x06               | •              | •                    |  |

| CWG1A       | 0x05               | •              | •                    |  |

| CLC4OUT     | 0x04               | •              | •                    |  |

| CLC3OUT     | 0x03               | •              | •                    |  |

| CLC2OUT     | 0x02               | •              | •                    |  |

| CLC10UT     | 0x01               | •              | •                    |  |

### 18.3 Register Definitions: FVR Control

### REGISTER 18-1: FVRCON: FIXED VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0/0 | R-q/q                 | R/W-0/0             | R/W-0/0              | R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 |

|---------|-----------------------|---------------------|----------------------|---------|---------|---------|---------|

| FVREN   | FVRRDY <sup>(1)</sup> | TSEN <sup>(3)</sup> | TSRNG <sup>(3)</sup> | CDAF\   | /R<1:0> | ADFV    | R<1:0>  |

| bit 7   |                       |                     |                      |         |         |         | bit 0   |

| Legend:          |                                  |                                                                                                                                                           |                                                          |

|------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| R = Readable bit |                                  | W = Writable bit                                                                                                                                          | U = Unimplemented bit, read as '0'                       |

| u = Bit is un    | nchanged                         | x = Bit is unknown                                                                                                                                        | -n/n = Value at POR and BOR/Value at all other Resets    |

| '1' = Bit is s   | et                               | '0' = Bit is cleared                                                                                                                                      | q = Value depends on condition                           |

| bit 7            | 1 = Fixed                        | Fixed Voltage Reference Ena<br>Voltage Reference is enable<br>Voltage Reference is disabl                                                                 | ed                                                       |

| bit 6            | 1 = Fixed                        | Fixed Voltage Reference Re<br>Voltage Reference output is<br>Voltage Reference output is                                                                  | ready for use                                            |

| bit 5            | 1 = Temp                         | mperature Indicator Enable I<br>erature Indicator is enabled<br>erature Indicator is disabled                                                             | bit <sup>(3)</sup>                                       |

| bit 4            | 1 = Temp                         | Femperature Indicator Range<br>erature in High Range Vo∪⊤<br>erature in Low Range Vo∪⊤                                                                    | = 3VT                                                    |

| bit 3-2          | 11 = Com<br>10 = Com<br>01 = Com | <1:0>: Comparator FVR Buff<br>parator FVR Buffer Gain is 4<br>parator FVR Buffer Gain is 2<br>parator FVR Buffer Gain is 1<br>parator FVR Buffer is off   | x, (4.096V) <sup>(2)</sup><br>x, (2.048V) <sup>(2)</sup> |

| bit 1-0          | 11 = ADC<br>10 = ADC<br>01 = ADC | <b>:0&gt;:</b> ADC FVR Buffer Gain S<br>FVR Buffer Gain is 4x, (4.09<br>FVR Buffer Gain is 2x, (2.04<br>FVR Buffer Gain is 1x, (1.02<br>FVR Buffer is off | 96V)(2)<br>48V) <sup>(2)</sup>                           |

| <b>2:</b> F      | •                                | Reference output cannot exc                                                                                                                               | eed VDD.<br>Module" for additional information           |

3: See Section 19.0 "Temperature Indicator Module" for additional information.

### PIC16(L)F15313/23

### REGISTER 28-4: CCPRxH REGISTER: CCPx REGISTER HIGH BYTE

| R/W-x/x |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | CCPRx   | <15:8>  |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| Legend:              |                      |                                                      |

|----------------------|----------------------|------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                   |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Reset |

| '1' = Bit is set     | '0' = Bit is cleared |                                                      |

| CCPxMODE = Capture mode                              |

|------------------------------------------------------|

| CCPRxH<7:0>: Captured value of TMR1H                 |

| <u>CCPxMODE = Compare mode</u>                       |

| CCPRxH<7:0>: MS Byte compared to TMR1H               |

| <u>CCPxMODE = PWM modes when CCPxFMT = 0</u> :       |

| CCPRxH<7:2>: Not used                                |

| CCPRxH<1:0>: Pulse-width Most Significant two bits   |

| CCPxMODE = PWM modes when CCPxFMT = 1:               |

| CCPRxH<7:0>: Pulse-width Most Significant eight bits |

|                                                      |

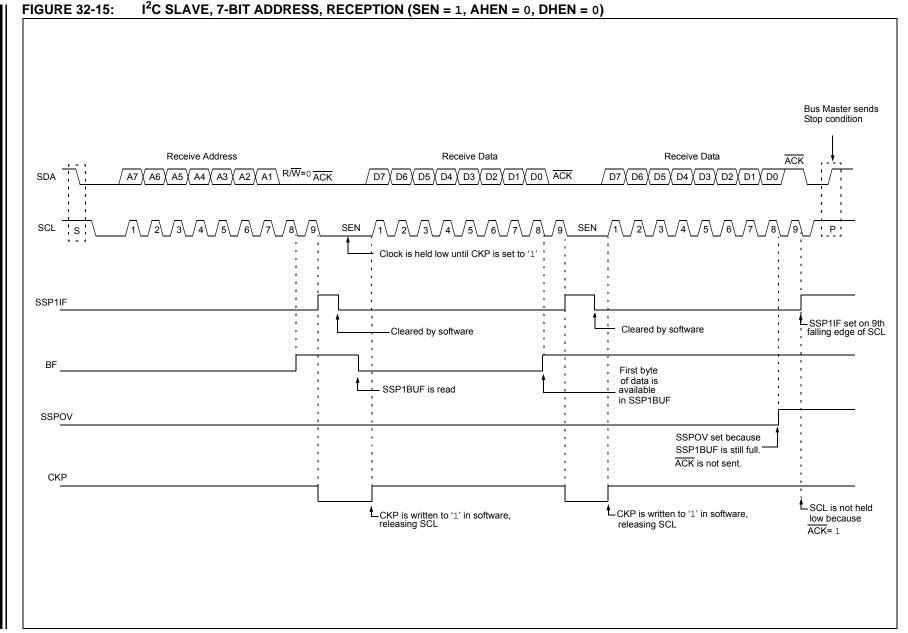

### 32.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

### 32.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

### 32.4 I<sup>2</sup>C MODE OPERATION

All MSSP I<sup>2</sup>C communication is byte oriented and shifted out MSb first. Six SFR registers and two interrupt flags interface the module with the  $PIC^{$ <sup>®</sup>} microcontroller and user software. Two pins, SDA and SCL, are exercised by the module to communicate with other external I<sup>2</sup>C devices.

### 32.4.1 BYTE FORMAT

All communication in  $I^2C$  is done in 9-bit segments. A byte is sent from a master to a slave or vice-versa, followed by an Acknowledge bit sent back. After the eighth falling edge of the SCL line, the device outputting data on the SDA changes that pin to an input and reads in an acknowledge value on the next clock pulse.

The clock signal, SCL, is provided by the master. Data is valid to change while the SCL signal is low, and sampled on the rising edge of the clock. Changes on the SDA line while the SCL line is high define special conditions on the bus, explained below.

### 32.4.2 DEFINITION OF I<sup>2</sup>C TERMINOLOGY

There is language and terminology in the description of  $I^2C$  communication that have definitions specific to  $I^2C$ . That word usage is defined below and may be used in the rest of this document without explanation. This table was adapted from the Philips  $I^2C$  specification.

### 32.4.3 SDA AND SCL PINS

Selection of any I<sup>2</sup>C mode with the SSPEN bit set, forces the SCL and SDA pins to be open-drain. These pins should be set by the user to inputs by setting the appropriate TRIS bits.

| Note 1: | Any device pin can be selected for SDA        |

|---------|-----------------------------------------------|

|         | and SCL functions with the PPS periph-        |

|         | eral. These functions are bidirectional.      |

|         | The SDA input is selected with the            |

|         | SSPDATPPS registers. The SCL input is         |

|         | selected with the SSPCLKPPS registers.        |

|         | Outputs are selected with the RxyPPS          |

|         | registers. It is the user's responsibility to |

|         | make the selections so that both the input    |

|         | and the output for each function is on the    |

|         | same pin.                                     |

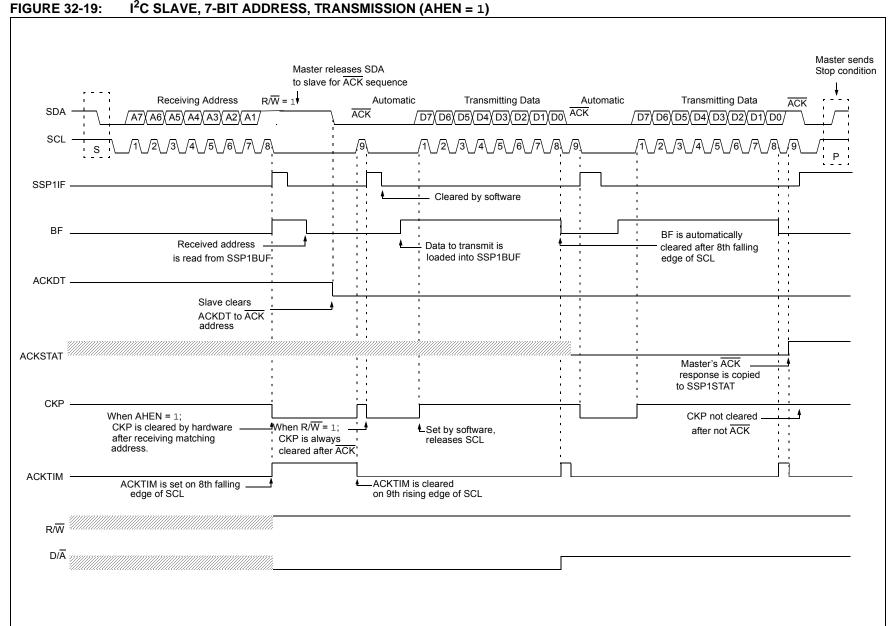

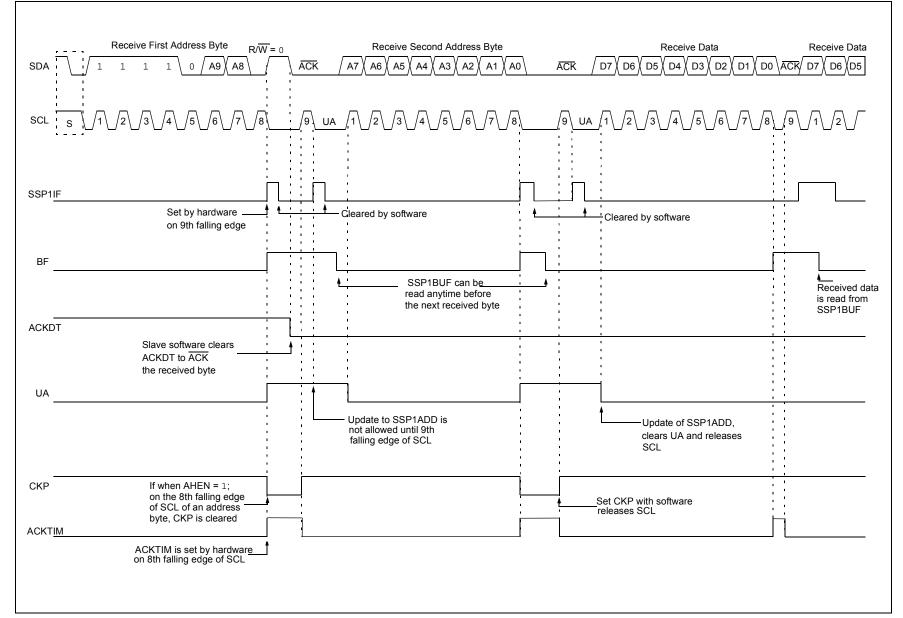

### **FIGURE 32-15:**

### I<sup>2</sup>C SLAVE, 7-BIT ADDRESS, TRANSMISSION (AHEN = 1)

### FIGURE 32-21: I<sup>2</sup>C SLAVE, 10-BIT ADDRESS, RECEPTION (SEN = 0, AHEN = 1, DHEN = 0)

Preliminary

### 32.8 Register Definitions: MSSP1 Control

| R/W-0/0          | R/W-0/0                                                                                                                                                                                         | R/HS/HC-0                                                                                   | R/HS/HC-0          | R/HS/HC-0         | R/HS/HC-0              | R/HS/HC-0           | R/HS/HC-0         |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------|-------------------|------------------------|---------------------|-------------------|

| SMP              | CKE <sup>(1)</sup>                                                                                                                                                                              | D/A                                                                                         | P <sup>(2)</sup>   | S <sup>(2)</sup>  | R/W                    | UA                  | BF                |

| bit 7            |                                                                                                                                                                                                 |                                                                                             |                    | 1                 |                        |                     | bit C             |

| Legend:          |                                                                                                                                                                                                 |                                                                                             |                    |                   |                        |                     |                   |

| R = Readable b   | bit                                                                                                                                                                                             | W = Writable bit                                                                            |                    | II = I Inimpleme  | nted bit, read as '0   | ,                   |                   |

|                  |                                                                                                                                                                                                 |                                                                                             |                    | •                 | POR and BOR/Val        |                     | oto               |

| u = Bit is uncha | ingeu                                                                                                                                                                                           | x = Bit is unknow                                                                           |                    |                   |                        |                     | els               |

| '1' = Bit is set |                                                                                                                                                                                                 | '0' = Bit is cleare                                                                         | ea                 | HS/HC = Hardw     | /are set/clear         |                     |                   |

| bit 7            | <u>SPI Master mo</u><br>1 = Input data                                                                                                                                                          | a Input Sample bit<br><u>ode:</u><br>sampled at end of<br>sampled at middle                 | •                  | ne                |                        |                     |                   |

|                  | In I <sup>2</sup> C Master of<br>1 = Slew rate                                                                                                                                                  | control disabled for                                                                        | r Standard Speed   | d mode (100 kHz a | and 1 MHz)             |                     |                   |

|                  |                                                                                                                                                                                                 | control enabled for                                                                         | • •                | . ,               |                        |                     |                   |

| bit 6            | <u>In SPI Master</u><br>1 = Transmit o<br>0 = Transmit o                                                                                                                                        | ck Edge Select bit (<br>or Slave mode:<br>ccurs on transition<br>ccurs on transition        | from active to Id  | e clock state     |                        |                     |                   |

|                  |                                                                                                                                                                                                 | <u>nly:</u><br>ut logic so that thre<br>/Bus specific input:                                |                    | liant with SMBus  | specification          |                     |                   |

| bit 5            | _                                                                                                                                                                                               | Iress bit (I <sup>2</sup> C mode                                                            |                    |                   |                        |                     |                   |

|                  | 1 = Indicates t                                                                                                                                                                                 | hat the last byte red<br>hat the last byte red                                              | ceived or transmi  |                   |                        |                     |                   |

| bit 4            | P: Stop bit <sup>(2)</sup>                                                                                                                                                                      |                                                                                             |                    |                   |                        |                     |                   |

|                  | 1 = Indicates t                                                                                                                                                                                 | y. This bit is cleared hat a Stop bit has b as not detected last                            | een detected las   |                   |                        | red.)               |                   |

| bit 3            | 1 = Indicates t                                                                                                                                                                                 | y. This bit is cleared<br>hat a Start bit has b<br>as not detected last                     | een detected las   |                   |                        | red.)               |                   |

| bit 2            | This bit holds t                                                                                                                                                                                | ite bit information (<br>he R/W bit info <u>rmai</u><br>Stop bit, or not ACK<br><u>ode:</u> | tion following the | last address mate | ch. This bit is only v | valid from the addı | ress match to the |

|                  | In I <sup>2</sup> C Master I<br>1 = Transmit<br>0 = Transmit                                                                                                                                    | <u>mode:</u><br>is in progress<br>is not in progress<br>his bit with SEN, R                 | SEN. PEN. RCE      | N or ACKEN will i | ndicate if the MSS     | P is in IDLE mode   |                   |

| bit 1            | <b>UA:</b> Update Address bit (10-bit I <sup>2</sup> C mode only)<br>1 = Indicates that the user needs to update the address in the SSP1ADD register<br>0 = Address does not need to be updated |                                                                                             |                    |                   |                        |                     |                   |

| bit 0            | 0 = Receive no                                                                                                                                                                                  | and I <sup>2</sup> C modes):<br>omplete, SSPBUF i<br>ot complete, SSPBI                     |                    |                   |                        |                     |                   |

|                  |                                                                                                                                                                                                 | <u>mode only):</u><br>mit in progress (doo<br>mit complete (does                            |                    |                   |                        |                     |                   |

|                  |                                                                                                                                                                                                 | e is set by the CKP                                                                         |                    |                   |                        |                     |                   |

### REGISTER 32-1: SSP1STAT: SSP1 STATUS REGISTER

2: This bit is cleared on Reset and when SSPEN is cleared.

### 36.2 General Format for Instructions

| Mnemonic, |         | Description                   |               | 14-Bit Opcode |      |      |          | Status   | Notes |

|-----------|---------|-------------------------------|---------------|---------------|------|------|----------|----------|-------|

| Oper      | ands    | Description                   |               | MSb           | LSb  |      | Affected | Notes    |       |

|           |         | BYTE-ORIENTED FILE            | REGISTER OPE  | RATIC         | ONS  |      |          |          |       |

| ADDWF     | f, d    | Add W and f                   | 1             | 00            | 0111 | dfff | ffff     | C, DC, Z | 2     |

| ADDWFC    | f, d    | Add with Carry W and f        | 1             | 11            | 1101 | dfff | ffff     | C, DC, Z | 2     |

| ANDWF     | f, d    | AND W with f                  | 1             | 00            | 0101 | dfff | ffff     | Z        | 2     |

| ASRF      | f, d    | Arithmetic Right Shift        | 1             | 11            | 0111 | dfff | ffff     | C, Z     | 2     |

| LSLF      | f, d    | Logical Left Shift            | 1             | 11            | 0101 | dfff | ffff     | C, Z     | 2     |

| LSRF      | f, d    | Logical Right Shift           | 1             | 11            | 0110 | dfff | ffff     | C, Z     | 2     |

| CLRF      | f       | Clear f                       | 1             | 00            | 0001 | lfff | ffff     | Z        | 2     |

| CLRW      | -       | Clear W                       | 1             | 00            | 0001 | 0000 | 00xx     | Z        |       |

| COMF      | f, d    | Complement f                  | 1             | 00            | 1001 | dfff | ffff     | Z        | 2     |

| DECF      | f, d    | Decrement f                   | 1             | 00            | 0011 | dfff | ffff     | Z        | 2     |

| INCF      | f, d    | Increment f                   | 1             | 00            | 1010 | dfff | ffff     | Z        | 2     |

| IORWF     | f, d    | Inclusive OR W with f         | 1             | 00            | 0100 | dfff | ffff     | Z        | 2     |

| MOVF      | f, d    | Move f                        | 1             | 00            | 1000 | dfff | ffff     | Z        | 2     |

| MOVWF     | f       | Move W to f                   | 1             | 00            | 0000 | 1fff | ffff     |          | 2     |

| RLF       | f, d    | Rotate Left f through Carry   | 1             | 00            | 1101 | dfff | ffff     | С        | 2     |

| RRF       | f, d    | Rotate Right f through Carry  | 1             | 00            | 1100 | dfff | ffff     | С        | 2     |

| SUBWF     | f, d    | Subtract W from f             | 1             | 00            | 0010 | dfff | ffff     | C, DC, Z | 2     |

| SUBWFB    | f, d    | Subtract with Borrow W from f | 1             | 11            | 1011 | dfff | ffff     | C, DC, Z | 2     |

| SWAPF     | f, d    | Swap nibbles in f             | 1             | 00            | 1110 | dfff | ffff     |          | 2     |

| XORWF     | f, d    | Exclusive OR W with f         | 1             | 00            | 0110 | dfff | ffff     | Z        | 2     |

|           |         | BYTE ORIENTED                 | SKIP OPERATIO | ONS           |      |      |          |          |       |

| DECFSZ    | f, d    | Decrement f, Skip if 0        | 1(2)          | 00            | 1011 | dfff | ffff     |          | 1, 2  |

| INCFSZ    | f, d    | Increment f, Skip if 0        | 1(2)          | 00            | 1111 | dfff | ffff     |          | 1, 2  |

|           | 1       | BIT-ORIENTED FILE             |               |               | vs   |      |          |          |       |

| BCF       | f, b    | Bit Clear f                   | 1             | 01            | 00bb | bfff | ffff     |          | 2     |

| BSF       | f, b    | Bit Set f                     | 1             | 01            | 01bb | bfff | ffff     |          | 2     |

|           |         | BIT-ORIENTED                  | SKIP OPERATIO | NS            |      |      |          |          |       |

| BTFSC     | f, b    | Bit Test f, Skip if Clear     | 1 (2)         | 01            | 10bb | bfff | ffff     |          | 1, 2  |

| BTFSS     | f, b    | Bit Test f, Skip if Set       | 1 (2)         | 01            | 11bb | bfff | ffff     |          | 1, 2  |

| LITERAL ( | OPERATI |                               |               |               |      |      |          |          |       |

| ADDLW     | k       | Add literal and W             | 1             | 11            | 1110 | kkkk | kkkk     | C, DC, Z |       |

| ANDLW     | k       | AND literal with W            | 1             | 11            | 1001 | kkkk | kkkk     | Z        |       |

| IORLW     | k       | Inclusive OR literal with W   | 1             | 11            | 1000 | kkkk | kkkk     | Z        |       |

| MOVLB     | k       | Move literal to BSR           | 1             | 00            | 000  | 0k   | kkkk     |          |       |

| MOVLP     | k       | Move literal to PCLATH        | 1             | 11            | 0001 | 1kkk | kkkk     |          |       |

| MOVLW     | k       | Move literal to W             | 1             | 11            | 0000 | kkkk | kkkk     |          |       |

| SUBLW     | k       | Subtract W from literal       | 1             | 11            | 1100 | kkkk | kkkk     | C, DC, Z |       |

| XORLW     | k       | Exclusive OR literal with W   | 1             | 11            | 1010 | kkkk | kkkk     | Z        | 1     |

### TABLE 36-3: INSTRUCTION SET

**Note 1:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

2: If this instruction addresses an INDF register and the MSb of the corresponding FSR is set, this instruction will require one additional instruction cycle.

| TABLE 37-18: | TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS |

|--------------|-----------------------------------------------|

|--------------|-----------------------------------------------|

|               | ng Temperatur |                           | nless otherwis<br>≤ +125°C | e stateu)      |                            |           | -                        |       | $\sum_{i=1}^{n} \sum_{j=1}^{n} \sum_{i=1}^{n} \sum_{j=1}^{n} \sum_{i$ |

|---------------|---------------|---------------------------|----------------------------|----------------|----------------------------|-----------|--------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. | Sym.          |                           | Characteristic             | c              | Min.                       | Тур†      | Max.                     | Units | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 40*           | T⊤0H          | T0CKI High I              | Pulse Width                | No Prescaler   | 0.5 Tcy + 20               | 1         | —                        | ns    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |               |                           |                            | With Prescaler | 10                         | _         | —                        | / ns  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 41*           | TT0L          | T0CKI Low F               | ulse Width                 | No Prescaler   | 0.5 TCY + 20               | _         | _/                       | /ns / |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               |               |                           |                            | With Prescaler | 10                         | _         |                          | NS    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |