#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                 |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | AVR                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | USI                                                                      |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 16                                                                       |

| Program Memory Size        | 2KB (1K x 16)                                                            |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 128 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                              |

| Data Converters            | A/D 11x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 32-VFQFN Exposed Pad                                                     |

| Supplier Device Package    | 32-VQFN (5x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny261-20mu |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# ATtiny261/461/861

#### 5.5.2 EEARL – EEPROM Address Register

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x1E (0x3E)   | EEAR7 | EEAR6 | EEAR5 | EEAR4 | EEAR3 | EEAR2 | EEAR1 | EEAR0 | EEARL |

| Read/Write    | R/W   |       |

| Initial Value | X/0   | Х     | Х     | Х     | Х     | Х     | Х     | Х     |       |

#### • Bit 7 – EEAR7: EEPROM Address

This is the most significant EEPROM address bit of ATtiny461. In devices with less EEPROM, i.e. ATtiny261, this bit is reserved and will always read zero. The initial value of the EEPROM Address Register (EEAR) is undefined and a proper value must therefore be written before the EEPROM is accessed.

#### • Bits 6:0 – EEAR6:0: EEPROM Address

These are the (low) bits of the EEPROM Address Register. The EEPROM data bytes are addressed linearly in the range 0...128/256/512. The initial value of EEAR is undefined and a proper value must be therefore be written before the EEPROM may be accessed.

#### 5.5.3 EEDR – EEPROM Data Register

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _    |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| 0x1D (0x3D)   | EEDR7 | EEDR6 | EEDR5 | EEDR4 | EEDR3 | EEDR2 | EEDR1 | EEDR0 | EEDR |

| Read/Write    | R/W   | -    |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |      |

#### • Bits 7:0 – EEDR7:0: EEPROM Data

For the EEPROM write operation the EEDR Register contains the data to be written to the EEPROM in the address given by the EEAR Register. For the EEPROM read operation, the EEDR contains the data read out from the EEPROM at the address given by EEAR.

#### 5.5.4 EECR – EEPROM Control Register

| Bit           | 7 | 6 | 5     | 4     | 3     | 2     | 1    | 0    | _    |

|---------------|---|---|-------|-------|-------|-------|------|------|------|

| 0x1C (0x3C)   | - | - | EEPM1 | EEPM0 | EERIE | EEMPE | EEPE | EERE | EECR |

| Read/Write    | R | R | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | -    |

| Initial Value | 0 | 0 | Х     | Х     | 0     | 0     | Х    | 0    |      |

#### • Bit 7 - Res: Reserved Bit

This bit is reserved for future use and will always read as 0 in ATtiny261/461/861. For compatibility with future AVR devices, always write this bit to zero. After reading, mask out this bit.

#### • Bit 6 - Res: Reserved Bit

This bit is reserved in the ATtiny261/461/861 and will always read as zero.

#### • Bits 5, 4 – EEPM1 and EEPM0: EEPROM Programming Mode Bits

The EEPROM Programming mode bits setting defines which programming action that will be triggered when writing EEPE. It is possible to program data in one atomic operation (erase the

old value and program the new value) or to split the Erase and Write operations in two different operations. The Programming times for the different modes are shown in Table 5-1.

Table 5-1. EEPROM Mode Bits

| EEPM1 | EEPM0 | Programming<br>Time | Operation                                           |

|-------|-------|---------------------|-----------------------------------------------------|

| 0     | 0     | 3.4 ms              | Erase and Write in one operation (Atomic Operation) |

| 0     | 1     | 1.8 ms              | Erase Only                                          |

| 1     | 0     | 1.8 ms              | Write Only                                          |

| 1     | 1     | _                   | Reserved for future use                             |

When EEPE is set, any write to EEPMn will be ignored. During reset, the EEPMn bits will be reset to 0b00 unless the EEPROM is busy programming.

#### • Bit 3 – EERIE: EEPROM Ready Interrupt Enable

Writing EERIE to one enables the EEPROM Ready Interrupt if the I-bit in SREG is set. Writing EERIE to zero disables the interrupt. The EEPROM Ready Interrupt generates a constant interrupt when Non-volatile memory is ready for programming.

#### • Bit 2 – EEMPE: EEPROM Master Program Enable

The EEMPE bit determines whether writing EEPE to one will have effect or not.

When EEMPE is set, setting EEPE within four clock cycles will program the EEPROM at the selected address. If EEMPE is zero, setting EEPE will have no effect. When EEMPE has been written to one by software, hardware clears the bit to zero after four clock cycles.

#### • Bit 1 – EEPE: EEPROM Program Enable

The EEPROM Program Enable Signal EEPE is the programming enable signal to the EEPROM. When EEPE is written, the EEPROM will be programmed according to the EEPMn bits setting. The EEMPE bit must be written to one before a logical one is written to EEPE, otherwise no EEPROM write takes place. When the write access time has elapsed, the EEPE bit is cleared by hardware. When EEPE has been set, the CPU is halted for two cycles before the next instruction is executed.

#### Bit 0 – EERE: EEPROM Read Enable

The EEPROM Read Enable Signal – EERE – is the read strobe to the EEPROM. When the correct address is set up in the EEAR Register, the EERE bit must be written to one to trigger the EEPROM read. The EEPROM read access takes one instruction, and the requested data is available immediately. When the EEPROM is read, the CPU is halted for four cycles before the next instruction is executed. The user should poll the EEPE bit before starting the read operation. If a write operation is in progress, it is neither possible to read the EEPROM, nor to change the EEAR Register.

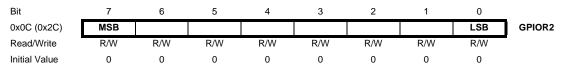

#### 5.5.5 GPIOR2 – General Purpose I/O Register 2

## <sup>22</sup> ATtiny261/461/861

mencing normal operation. The watchdog oscillator is used for timing this real-time part of the start-up time. The number of WD oscillator cycles used for each time-out is shown in Table 6-2.

Table 6-2.

Number of Watchdog Oscillator Cycles

| Typ Time-out | Number of Cycles |

|--------------|------------------|

| 4 ms         | 512              |

| 64 ms        | 8K (8,192)       |

#### 6.2.1 External Clock

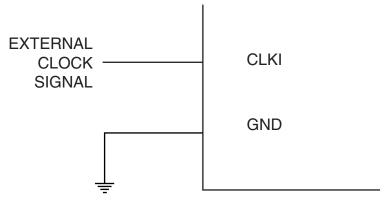

To drive the device from an external clock source, CLKI should be driven as shown in Figure 6-2. To run the device on an external clock, the CKSEL Fuses must be programmed to "0000".

Figure 6-2. External Clock Drive Configuration

When this clock source is selected, start-up times are determined by the SUT Fuses as shown in Table 6-3.

| Table 6-3.         Start-up Times for the External Clock S |

|------------------------------------------------------------|

|------------------------------------------------------------|

| SUT1:0 | Start-up Time from Power-<br>down and Power-save | Additional Delay from<br>Reset | Recommended Usage   |  |  |

|--------|--------------------------------------------------|--------------------------------|---------------------|--|--|

| 00     | 6 CK                                             | 14CK                           | BOD enabled         |  |  |

| 01     | 6 CK                                             | 14CK + 4 ms                    | Fast rising power   |  |  |

| 10     | 6 CK                                             | 14CK + 64 ms                   | Slowly rising power |  |  |

| 11     | Reserved                                         |                                |                     |  |  |

When applying an external clock, it is required to avoid sudden changes in the applied clock frequency to ensure stable operation of the MCU. A variation in frequency of more than 2% from one clock cycle to the next can lead to unpredictable behavior. It is required to ensure that the MCU is kept in Reset during such changes in the clock frequency.

Note that the system clock prescaler can be used to implement run-time changes of the internal clock frequency. See "System Clock Prescaler" on page 31 for details.

#### 6.2.2 High-Frequency PLL Clock

The internal PLL generates a clock signal with a frequency eight times higher than the source input. The PLL uses the output of the internal 8 MHz oscillator as source and the default setting generates a fast peripheral clock signal of 64 MHz.

From the time the CLKPS values are written, it takes between T1 + T2 and T1 +  $2^{T2}$  before the new clock frequency is active. In this interval, two active clock edges are produced. Here, T1 is the previous clock period, and T2 is the period corresponding to the new prescaler setting.

#### 6.4 Clock Output Buffer

The device can output the system clock on the CLKO pin (when not used as XTAL2 pin). To enable the output, the CKOUT Fuse has to be programmed. This mode is suitable when the chip clock is used to drive other circuits on the system. Note that the clock will not be output during reset and the normal operation of I/O pin will be overridden when the fuse is programmed. Internal RC Oscillator, WDT Oscillator, PLL, and external clock (CLKI) can be selected when the clock is output on CLKO. Crystal oscillators (XTAL1, XTAL2) can not be used for clock output on CLKO. If the System Clock Prescaler is used, it is the divided system clock that is output.

#### 6.5 Register Description

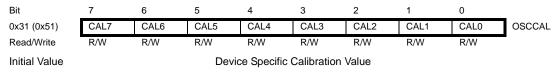

#### 6.5.1 OSCCAL – Oscillator Calibration Register

#### • Bits 7:0 – CAL7:0: Oscillator Calibration Value

The Oscillator Calibration Register is used to trim the Calibrated Internal RC Oscillator to remove process variations from the oscillator frequency. A pre-programmed calibration value is automatically written to this register during chip reset, giving the Factory calibrated frequency as specified in Table 19-2 on page 189. The application software can write this register to change the oscillator frequency. The oscillator can be calibrated to frequencies as specified in Table 19-2 on page 189. The application software development of the specified in Table 19-2 on page 189. The application software can write this register to change the oscillator frequency. The oscillator can be calibrated to frequencies as specified in Table 19-2 on page 189. Calibration outside that range is not guaranteed.

Note that this oscillator is used to time EEPROM and Flash write accesses, and these write times will be affected accordingly. If the EEPROM or Flash are written, do not calibrate to more than 8.8 MHz. Otherwise, the EEPROM or Flash write may fail.

The CAL7 bit determines the range of operation for the oscillator. Setting this bit to 0 gives the lowest frequency range, setting this bit to 1 gives the highest frequency range. The two frequency ranges are overlapping, in other words a setting of OSCCAL = 0x7F gives a higher frequency than OSCCAL = 0x80.

The CAL6:0 bits are used to tune the frequency within the selected range. A setting of 0x00 gives the lowest frequency in that range, and a setting of 0x7F gives the highest frequency in the range.

#### 6.5.2 CLKPR – Clock Prescale Register

| Bit           | 7      | 6 | 5 | 4 | 3          | 2         | 1      | 0      | _     |

|---------------|--------|---|---|---|------------|-----------|--------|--------|-------|

| 0x28 (0x48)   | CLKPCE | - | - | - | CLKPS3     | CLKPS2    | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write    | R/W    | R | R | R | R/W        | R/W       | R/W    | R/W    |       |

| Initial Value | 0      | 0 | 0 | 0 | See Bit De | scription |        |        |       |

#### • Bit 7 – CLKPCE: Clock Prescaler Change Enable

The CLKPCE bit must be written to logic one to enable change of the CLKPS bits. The CLKPCE bit is only updated when the other bits in CLKPR are simultaniosly written to zero. CLKPCE is

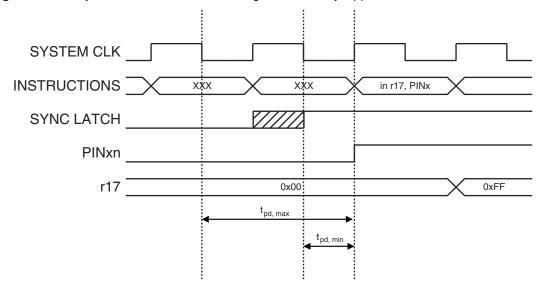

Figure 10-3. Synchronization when Reading an Externally Applied Pin value

Consider the clock period starting shortly after the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the "SYNC LATCH" signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indicated by the two arrows tpd,max and tpd,min, a single signal transition on the pin will be delayed between ½ and 1½ system clock period depending upon the time of assertion.

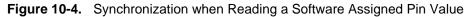

When reading back a software assigned pin value, a nop instruction must be inserted as indicated in Figure 10-4. The out instruction sets the "SYNC LATCH" signal at the positive edge of the clock. In this case, the delay tpd through the synchronizer is one system clock period.

#### • Port A, Bit 5 – ADC4/AIN2/PCINT5

- ADC4: Analog to Digital Converter, Channel 4.

- AIN2: Analog Comparator Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

- PCINT5: Pin Change Interrupt source 5.

#### • Port A, Bit 4 – ADC3/ICP0/PCINT4

- ADC3: Analog to Digital Converter, Channel 3.

- ICP0: Timer/Counter0 Input Capture Pin.

- PCINT4: Pin Change Interrupt source 4.

#### • Port A, Bit 3 – AREF/PCINT3

- AREF: External analog reference for ADC. Pullup and output driver are disabled on PA3 when the pin is used as an external reference or internal voltage reference with external capacitor at the AREF pin.

- PCINT3: Pin Change Interrupt source 3.

#### • Port A, Bit 2 – ADC2/INT1/USCK/SCL/PCINT2

- ADC2: Analog to Digital Converter, Channel 2.

- INT1: The PA2 pin can serve as an External Interrupt source 1.

- USCK: Three-wire mode Universal Serial Interface Clock.

- SCL: Two-wire mode Serial Clock for USI Two-wire mode.

- PCINT2: Pin Change Interrupt source 2.

#### • Port A, Bit 1 – ADC1/DO/PCINT1

- ADC1: Analog to Digital Converter, Channel 1.

- DO: Three-wire mode Universal Serial Interface Data output. Three-wire mode Data output overrides PORTA1 value and it is driven to the port when data direction bit DDA1 is set. PORTA1 still enables the pull-up, if the direction is input and PORTA1 is set.

- PCINT1: Pin Change Interrupt source 1.

#### Port A, Bit 0 – ADC0/DI/SDA/PCINT0

- ADC0: Analog to Digital Converter, Channel 0.

- DI: Data Input in USI Three-wire mode. USI Three-wire mode does not override normal port functions, so pin must be configure as an input for DI function.

- SDA: Two-wire mode Serial Interface Data.

- PCINT0: Pin Change Interrupt source 0.

#### • Port B, Bit 1 - MISO/ DO/ OC1A/ PCINT9

- DO: Three-wire mode Universal Serial Interface Data output. Three-wire mode Data output overrides PORTB1 value and it is driven to the port when data direction bit DDB1 is set (one). PORTB1 still enables the pull-up, if the direction is input and PORTB1 is set (one).

- OC1A: Output Compare Match output: The PB1 pin can serve as an external output for the Timer/Counter1 Compare Match B when configured as an output (DDB1 set). The OC1A pin is also the output pin for the PWM mode timer function.

- PCINT9: Pin Change Interrupt source 9.

#### • Port B, Bit 0 – MOSI/ DI/ SDA/ OC1A/ PCINT8

- DI: Data Input in USI Three-wire mode. USI Three-wire mode does not override normal port functions, so pin must be configure as an input for DI function.

- SDA: Two-wire mode Serial Interface Data.

- OC1A: Inverted Output Compare Match output: The PB0 pin can serve as an external output for the Timer/Counter1 Compare Match B when configured as an output (DDB0 set). The OC1A pin is also the inverted output pin for the PWM mode timer function.

- PCINT8: Pin Change Interrupt source 8.

Table 10-7 and Table 10-8 relate the alternate functions of Port B to the overriding signals shown in Figure 10-5 on page 61.

| Signal<br>Name | PB7/RESET/<br>dW/ADC10/<br>PCINT15               | PB6/ADC9/T0/<br>INT0/PCINT14          | PB5/XTAL2/CLKO/<br>OC1D/ADC8/<br>PCINT13 <sup>(1)</sup> | PB4/XTAL1/<br>OC1D/ADC7/<br>PCINT12 <sup>(1)</sup> |

|----------------|--------------------------------------------------|---------------------------------------|---------------------------------------------------------|----------------------------------------------------|

| PUOE           | RSTDISBL <sup>(1)</sup> •<br>DWEN <sup>(1)</sup> | 0                                     | INTRC • EXTCLK                                          | INTRC                                              |

| PUOV           | 1                                                | 0                                     | 0                                                       | 0                                                  |

| DDOE           | RSTDISBL <sup>(1)</sup> •<br>DWEN <sup>(1)</sup> | 0                                     | INTRC • EXTCLK                                          | INTRC                                              |

| DDOV           | debugWire Transmit                               | 0                                     | 0                                                       | 0                                                  |

| PVOE           | 0                                                | 0                                     | OC1D Enable                                             | OC1D Enable                                        |

| PVOV           | 0                                                | 0                                     | OC1D                                                    | OC1D                                               |

| PTOE           | 0                                                | 0                                     | 0                                                       | 0                                                  |

| DIEOE          | 0                                                | RSTDISBL + (PCINT5<br>• PCIE + ADC9D) | INTRC • EXTCLK +<br>PCINT4 • PCIE +<br>ADC8D            | INTRC + PCINT12 •<br>PCIE + ADC7D                  |

| DIEOV          | ADC10D                                           | ADC9D                                 | (INTRC • EXTCLK) +<br>ADC8D                             | INTRC • ADC7D                                      |

| DI             | PCINT15                                          | T0/INT0/PCINT14                       | PCINT13                                                 | PCINT12                                            |

| AIO            | RESET / ADC10                                    | ADC9                                  | XTAL2, ADC8                                             | XTAL1, ADC7                                        |

Table 10-7.

Overriding Signals for Alternate Functions in PB7:PB4

Note: 1. "1" when the Fuse is "0" (Programmed).

#### • Bit 1 – TOV0: Timer/Counter0 Overflow Flag

The bit TOV0 is set when an overflow occurs in Timer/Counter0. TOV0 is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, TOV0 is cleared by writing a logic one to the flag. When the SREG I-bit, TOIE0 (Timer/Counter0 Overflow Interrupt Enable), and TOV0 are set, the Timer/Counter0 Overflow interrupt is executed.

#### • Bit 0 – ICF0: Timer/Counter0, Input Capture Flag

This flag is set when a capture event occurs on the ICP0 pin. When the Input Capture Register (ICR0) is set to be used as the TOP value, the ICF0 flag is set when the counter reaches the TOP value.

ICF0 is automatically cleared when the Input Capture Interrupt Vector is executed. Alternatively, ICF0 can be cleared by writing a logic one to its bit location.

#### 12.4.1 Counter Initialization for Asynchronous Mode

To set Timer/Counter1 to asynchronous mode follow the procedure below:

- 1. Enable PLL.

- 2. Wait 100 µs for PLL to stabilize.

- 3. Poll the PLOCK bit until it is set.

- 4. Set the PCKE bit in the PLLCSR register which enables the asynchronous mode.

#### 12.5 Output Compare Unit

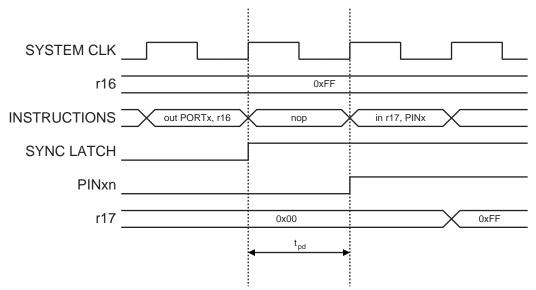

The comparator continuously compares TCNT1 with the Output Compare Registers (OCR1A, OCR1B, OCR1C and OCR1D). Whenever TCNT1 equals to the Output Compare Register, the comparator signals a match. A match will set the Output Compare Flag (OCF1A, OCF1B or OCF1D) at the next timer clock cycle. If the corresponding interrupt is enabled, the Output Compare Flag generates an Output Compare interrupt. The Output Compare Flag is automatically cleared when the interrupt is executed. Alternatively, the flag can be cleared by software by writing a logical one to its I/O bit location. The Waveform Generator uses the match signal to generate an output according to operating mode set by bits PWM1A, PWM1B, WGM11:10 and COM1x1:0. The top and bottom signals are used by the Waveform Generator for handling the special cases of the extreme values in some modes of operation (See "Modes of Operation" on page 99.). Figure 12-5 shows a block diagram of the Output Compare unit.

Figure 12-5. Output Compare Unit, Block Diagram

The OCR1x Registers are double buffered when using any of the Pulse Width Modulation (PWM) modes. For the normal mode of operation, the double buffering is disabled. The double buffering synchronizes the update of the OCR1x Compare Registers to either top or bottom of the counting sequence. The synchronization prevents the occurrence of odd-length, non-sym-

#### 12.6 Dead Time Generator

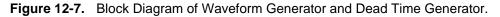

The Dead Time Generator is provided for the Timer/Counter1 PWM output pairs to allow driving external power control switches safely. The Dead Time Generator is a separate block that can be used to insert dead times (non-overlapping times) for the Timer/Counter1 complementary output pairs OC1x and OC1x when the PWM mode is enabled and the COM1x1:0 bits are set to "01". See Figure 12-7 below.

The tasks are shared as follows: the Waveform Generator generates the output (OCW1x) and the Dead Time Generator generates the non-overlapping PWM output pair from the output. Three Dead Time Generators are provided, one for each PWM output. The non-overlap time is adjustable and the PWM output and it's complementary output are adjusted separately, and independently for both PWM outputs.

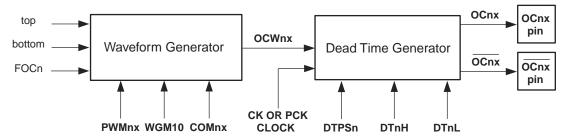

The Dead Time Generation is based on 4-bit down counters that count the dead time, as shown in Figure 12-8.

Figure 12-8. Dead Time Generator

There is a dedicated prescaler in front of the Dead Time Generator that can divide the Timer/Counter1 clock (PCK or CK) by 1, 2, 4 or 8. This provides for large range of dead times that can be generated. The prescaler is controlled by two control bits DTPS11:10. The block has also a rising and falling edge detector that is used to start the dead time counting period. Depending on the edge, one of the transitions on the rising edges, OC1x or  $\overline{OC1x}$  is delayed until the counter has counted to zero. The comparator is used to compare the counter with zero and stop the dead time insertion when zero has been reached. The counter is loaded with a 4-bit DT1H or DT1L value from DT1 I/O register, depending on the edge of the Waveform Output (OCW1x) when the dead time insertion is started. The Output Compare Output are delayed by one timer clock cycle at minimum from the Waveform Output when the Dead Time is adjusted to

OCnx

OCnx

| Table 12-1. Comparation of Output Compare 1 ms OCTD and OCTD in 1 White Mode |   |                |                |  |  |  |  |

|------------------------------------------------------------------------------|---|----------------|----------------|--|--|--|--|

| COM1D1 COM1D0                                                                |   | OC1D Pin (PB4) | OC1D Pin (PB5) |  |  |  |  |

| 0                                                                            | 0 | Disconnected   | Disconnected   |  |  |  |  |

| 0                                                                            | 1 | OC1A • OC1OE4  | OC1A • OC1OE5  |  |  |  |  |

| 1                                                                            | 0 | OC1A • OC1OE4  | OC1A • OC1OE5  |  |  |  |  |

| 1                                                                            | 1 | OC1A • OC1OE4  | OC1A • OC1OE5  |  |  |  |  |

Table 12-7.

Configuration of Output Compare Pins OC1D and OC1D in PWM6 Mode

### 12.9 Timer/Counter Timing Diagrams

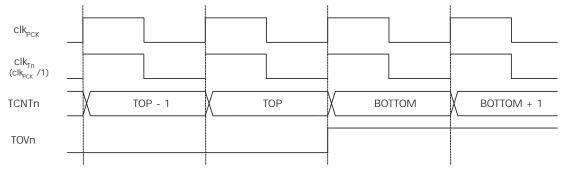

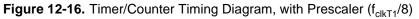

The Timer/Counter is a synchronous design and the timer clock  $(clk_{T1})$  is therefore shown as a clock enable signal in the following figures. The figures include information on when Interrupt Flags are set.

Figure 12-15 contains timing data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value in all modes other than Phase and Frequency Correct PWM Mode.

Figure 12-16 shows the same timing data, but with the prescaler enabled, in all modes other than Phase and Frequency Correct PWM Mode.

Figure 12-17 shows the setting of OCF1A, OCF1B and OCF1D in all modes.

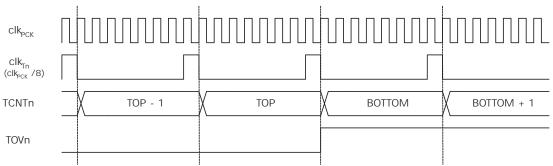

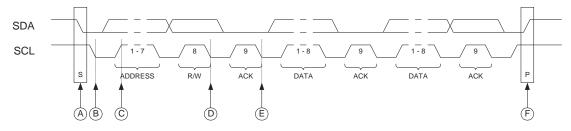

Figure 13-4. Two-wire Mode Operation, Simplified Diagram

The data direction is not given by the physical layer. A protocol, like the one used by the TWIbus, must be implemented to control the data flow.

#### Figure 13-5. Two-wire Mode, Typical Timing Diagram

Referring to the timing diagram (Figure 13-5), a bus transfer involves the following steps:

- The start condition is generated by the master by forcing the SDA low line while keeping the SCL line high (A). SDA can be forced low either by writing a zero to bit 7 of the USI Data Register, or by setting the corresponding bit in the PORTA register to zero. Note that the Data Direction Register bit must be set to one for the output to be enabled. The start detector logic of the slave device (see Figure 13-6 on page 131) detects the start condition and sets the USISIF Flag. The flag can generate an interrupt if necessary.

- 2. In addition, the start detector will hold the SCL line low after the master has forced a negative edge on this line (B). This allows the slave to wake up from sleep or complete other tasks before setting up the USI Data Register to receive the address. This is done by clearing the start condition flag and resetting the counter.

| ADTS2 | ADTS1 | ADTS0 | Trigger Source                 |

|-------|-------|-------|--------------------------------|

| 1     | 0     | 1     | Timer/Counter0 Compare Match B |

| 1     | 1     | 0     | Timer/Counter1 Overflow        |

| 1     | 1     | 1     | Watchdog Interrupt Request     |

Table 15-6.

ADC Auto Trigger Source Selections

#### 15.13.5 DIDR0 – Digital Input Disable Register 0

| Bit           | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | _     |

|---------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x01 (0x21)   | ADC6D | ADC5D | ADC4D | ADC3D | AREFD | ADC2D | ADC1D | ADC0D | DIDR0 |

| Read/Write    | R/W   | -     |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |       |

#### • Bits 7:4,2:0 - ADC6D:ADC0D: ADC6:0 Digital Input Disable

When this bit is written logic one, the digital input buffer on the corresponding ADC pin is disabled. The corresponding PIN register bit will always read as zero when this bit is set. When an analog signal is applied to the ADC7:0 pin and the digital input from this pin is not needed, this bit should be written logic one to reduce power consumption in the digital input buffer.

#### • Bit 3 – AREFD: AREF Digital Input Disable

When this bit is written logic one, the digital input buffer on the AREF pin is disabled. The corresponding PIN register bit will always read as zero when this bit is set. When an analog signal is applied to the AREF pin and the digital input from this pin is not needed, this bit should be written logic one to reduce power consumption in the digital input buffer.

#### 15.13.6 DIDR1 – Digital Input Disable Register 1

| Bit           | 7      | 6     | 5     | 4     | 3 | 2 | 1 | 0 |       |

|---------------|--------|-------|-------|-------|---|---|---|---|-------|

| 0x02 (0x22)   | ADC10D | ADC9D | ADC8D | ADC7D | - |   |   |   | DIDR1 |

| Read/Write    | R/W    | R/W   | R/W   | R/W   | R | R | R | R |       |

| Initial Value | 0      | 0     | 0     | 0     | 0 | 0 | 0 | 0 |       |

#### • Bits 7:4 – ADC10D:ADC7D: ADC10:7 Digital Input Disable

When this bit is written logic one, the digital input buffer on the corresponding ADC pin is disabled. The corresponding PIN register bit will always read as zero when this bit is set. When an analog signal is applied to the ADC10:7 pin and the digital input from this pin is not needed, this bit should be written logic one to reduce power consumption in the digital input buffer.

#### 17.9 Register Description

#### 17.9.1 SPMCSR – Store Program Memory Control and Status Register

The Store Program Memory Control and Status Register contains the control bits needed to control the Program memory operations.

| Bit           | 7 | 6 | 5 | 4    | 3    | 2     | 1     | 0     | _      |

|---------------|---|---|---|------|------|-------|-------|-------|--------|

| 0x37 (0x57)   | - | - | - | СТРВ | RFLB | PGWRT | PGERS | SPMEN | SPMCSR |

| Read/Write    | R | R | R | R/W  | R/W  | R/W   | R/W   | R/W   | -      |

| Initial Value | 0 | 0 | 0 | 0    | 0    | 0     | 0     | 0     |        |

#### • Bits 7:5 - Res: Reserved Bits

These bits are reserved and always read as zero.

#### • Bit 4 – CTPB: Clear Temporary Page Buffer

If the CTPB bit is written while filling the temporary page buffer, the temporary page buffer will be cleared and the data will be lost.

#### Bit 3 – RFLB: Read Fuse and Lock Bits

An LPM instruction within three cycles after RFLB and SPMEN are set in the SPMCSR Register, will read either the Lock bits or the Fuse bits (depending on Z0 in the Z-pointer) into the destination register. See "EEPROM Write Prevents Writing to SPMCSR" on page 167 for details.

#### • Bit 2 – PGWRT: Page Write

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles executes Page Write, with the data stored in the temporary buffer. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGWRT bit will auto-clear upon completion of a Page Write, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

#### • Bit 1 – PGERS: Page Erase

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles executes Page Erase. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGERS bit will auto-clear upon completion of a Page Erase, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

#### • Bit 0 – SPMEN: Store Program Memory Enable

This bit enables the SPM instruction for the next four clock cycles. If written to one together with either CTPB, RFLB, PGWRT, or PGERS, the following SPM instruction will have a special meaning, see description above. If only SPMEN is written, the following SPM instruction will store the value in R1:R0 in the temporary page buffer addressed by the Z-pointer. The LSB of the Z-pointer is ignored. The SPMEN bit will auto-clear upon completion of an SPM instruction, or if no SPM instruction is executed within four clock cycles. During Page Erase and Page Write, the SPMEN bit remains high until the operation is completed.

Writing any other combination than "10001", "01001", "00101", "00011" or "00001" in the lower five bits will have no effect.

# ATtiny261/461/861

Figure 19-8. Parallel Programming Timing, Reading Sequence (within the Same Page) with Timing Requirements

Note: The timing requirements shown in Figure 19-6 (i.e.,  $t_{DVXH}$ ,  $t_{XHXL}$ , and  $t_{XLDX}$ ) also apply to reading operation.

| Symbol               | Parameter                                            | Min  | Тур | Max  | Units |

|----------------------|------------------------------------------------------|------|-----|------|-------|

| V <sub>PP</sub>      | Programming Enable Voltage                           | 11.5 |     | 12.5 | V     |

| I <sub>PP</sub>      | Programming Enable Current                           |      |     | 250  | μA    |

| t <sub>DVXH</sub>    | Data and Control Valid before XTAL1 High             | 67   |     |      | ns    |

| t <sub>XLXH</sub>    | XTAL1 Low to XTAL1 High                              | 200  |     |      | ns    |

| t <sub>XHXL</sub>    | XTAL1 Pulse Width High                               | 150  |     |      | ns    |

| t <sub>XLDX</sub>    | Data and Control Hold after XTAL1 Low                | 67   |     |      | ns    |

| t <sub>XLWL</sub>    | XTAL1 Low to WR Low                                  | 0    |     |      | ns    |

| t <sub>BVPH</sub>    | BS1 Valid before PAGEL High                          | 67   |     |      | ns    |

| t <sub>PHPL</sub>    | PAGEL Pulse Width High                               | 150  |     |      | ns    |

| t <sub>PLBX</sub>    | BS1 Hold after PAGEL Low                             | 67   |     |      | ns    |

| t <sub>WLBX</sub>    | BS2/1 Hold after WR Low                              | 67   |     |      | ns    |

| t <sub>PLWL</sub>    | PAGEL Low to WR Low                                  | 67   |     |      | ns    |

| t <sub>BVWL</sub>    | BS1 Valid to WR Low                                  | 67   |     |      | ns    |

| t <sub>WLWH</sub>    | WR Pulse Width Low                                   | 150  |     |      | ns    |

| t <sub>WLRL</sub>    | WR Low to RDY/BSY Low                                | 0    |     | 1    | μs    |

| t <sub>WLRH</sub>    | WR Low to RDY/BSY High <sup>(1)</sup>                | 3.7  |     | 4.5  | ms    |

| t <sub>WLRH_CE</sub> | WR Low to RDY/BSY High for Chip Erase <sup>(2)</sup> | 7.5  |     | 9    | ms    |

| t <sub>XLOL</sub>    | XTAL1 Low to OE Low                                  | 0    |     |      | ns    |

**Table 19-9.** Parallel Programming Characteristics,  $V_{CC} = 5V \pm 10\%$

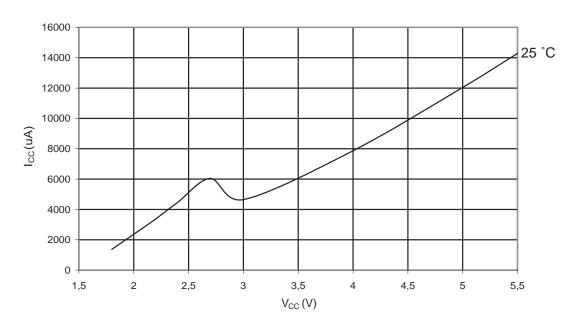

30 85 °C 25 °C 25 -40 °C 20 I<sub>cc</sub>(uA) 15 10 5 0 1,5 2 2,5 3 3,5 4 4,5 5 5,5  $V_{CC}(V)$

Figure 20-44Brownout Detector Current vs.  $V_{CC}$  BROWNOUT DETECTOR CURRENT vs.  $V_{CC}$

Figure 20-45Programming Current vs.  $V_{CC}$ PROGRAMMING CURRENT vs.  $V_{CC}$

# Atmel Enabling Unlimited Possibilities®

Atmel Corporation 1600 Technology Drive San Jose, CA 95110 USA Tel: (+1) (408) 441-0311 Fax: (+1) (408) 487-2600 www.atmel.com Atmel Asia Limited Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Roa Kwun Tong, Kowloon HONG KONG Tel: (+852) 2245-6100 Fax: (+852) 2722-1369 Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY **Tel:** (+49) 89-31970-0 **Fax:** (+49) 89-3194621 Atmel Japan G.K. 16F Shin-Osaki Kangyo Bldg 1-6-4 Osaki, Shinagawa-ku Tokyo 141-0032 JAPAN Tel: (+81) (3) 6417-0300 Fax: (+81) (3) 6417-0370

© 2013 Atmel Corporation. All rights reserved. / Rev.: 2588F–AVR–06/2013

Atmel<sup>®</sup>, Atmel logo and combinations thereof, Enabling Unlimited Possibilities<sup>®</sup>, AVR<sup>®</sup> and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.