Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | AVR                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 20MHz                                                     |

| Connectivity               | USI                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                     |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (1K x 16)                                             |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | 128 x 8                                                   |

| RAM Size                   | 128 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                               |

| Data Converters            | A/D 11x10b                                                |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                         |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | 20-SOIC                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/atmel/attiny261-20su |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 4.4 General Purpose Register File

The Register File is optimized for the AVR Enhanced RISC instruction set. In order to achieve the required performance and flexibility, the following input/output schemes are supported by the Register File:

- One 8-bit output operand and one 8-bit result input

- Two 8-bit output operands and one 8-bit result input

- Two 8-bit output operands and one 16-bit result input

- One 16-bit output operand and one 16-bit result input

Figure 4-2 below shows the structure of the 32 general purpose working registers in the CPU.

Figure 4-2. AVR CPU General Purpose Working Registers

|           | 7   | 0 | Addr. |                      |

|-----------|-----|---|-------|----------------------|

|           | R0  |   | 0x00  |                      |

|           | R1  |   | 0x01  |                      |

|           | R2  |   | 0x02  |                      |

|           |     |   |       |                      |

|           | R13 |   | 0x0D  |                      |

| General   | R14 |   | 0x0E  |                      |

| Purpose   | R15 |   | 0x0F  |                      |

| Working   | R16 |   | 0x10  |                      |

| Registers | R17 |   | 0x11  |                      |

|           |     |   |       |                      |

|           | R26 |   | 0x1A  | X-register Low Byte  |

|           | R27 |   | 0x1B  | X-register High Byte |

|           | R28 |   | 0x1C  | Y-register Low Byte  |

|           | R29 |   | 0x1D  | Y-register High Byte |

|           | R30 |   | 0x1E  | Z-register Low Byte  |

|           | R31 |   | 0x1F  | Z-register High Byte |

Most of the instructions operating on the Register File have direct access to all registers, and most of them are single cycle instructions.

As shown in Figure 4-2, each register is also assigned a Data memory address, mapping them directly into the first 32 locations of the user Data Space. Although not being physically implemented as SRAM locations, this memory organization provides great flexibility in access of the registers, as the X-, Y- and Z-pointer registers can be set to index any register in the file.

### 4.4.1 The X-register, Y-register, and Z-register

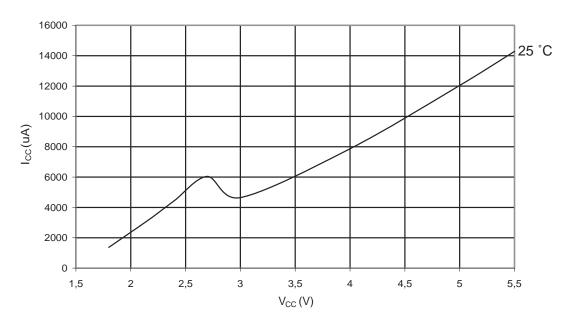

The registers R26:R31 have some added functions to their general purpose usage. These registers are 16-bit address pointers for indirect addressing of the data space. The three indirect address registers X, Y, and Z are defined as described in Figure 4-3.

Figure 4-3. The X-, Y-, and Z-registers

# <sup>10</sup> ATtiny261/461/861

When the PLL output is selected as clock source, the start-up times are determined by SUT fuse bits as shown in Table 6-5.

| SUT1:0 | Start-up Time from<br>Power Down | Additional Delay from<br>Power-On-Reset (V <sub>CC</sub> = 5.0V) | Recommended<br>usage |

|--------|----------------------------------|------------------------------------------------------------------|----------------------|

| 00     | 14CK + 1K (1024) + 4 ms          | 4 ms                                                             | BOD enabled          |

| 01     | 14CK + 16K (16384) + 4 ms        | 4 ms                                                             | Fast rising power    |

| 10     | 14CK + 1K (1024) + 64 ms         | 4 ms                                                             | Slowly rising power  |

| 11     | 14CK + 16K (16384) + 64 ms       | 4 ms                                                             | Slowly rising power  |

Table 6-5.Start-up Times for the PLLCK

### 6.2.3 Calibrated Internal 8 MHz Oscillator

By default, the Internal Oscillator provides an approximately 8 MHz clock signal. Though voltage and temperature dependent, this clock can be very accurately calibrated by the user. See Table 19-2 on page 189 and "Internal Oscillator Speed" on page 216 for more details. The device is shipped with the CKDIV8 Fuse programmed. See "System Clock Prescaler" on page 31 for more details.

This clock may be selected as the system clock by programming the CKSEL Fuses as shown in Table 6-6. If selected, it will operate with no external components. During reset, hardware loads the pre-programmed calibration value into the OSCCAL Register and thereby automatically calibrates the RC Oscillator. The accuracy of this calibration is shown as Factory calibration in Table 19-2 on page 189.

### **Table 6-6.**Internal Calibrated RC Oscillator Operating Modes

| CKSEL3:0            | Nominal Frequency      |

|---------------------|------------------------|

| 0010 <sup>(1)</sup> | 8.0 MHz <sup>(2)</sup> |

Notes: 1. The device is shipped with this option selected.

2. If the oscillator frequency exceeds the specification of the device (depends on  $V_{CC}$ ), the CKDIV8 Fuse can be programmed to divide the internal frequency by 8.

When this oscillator is selected, start-up times are determined by SUT fuses as shown in Table 6-7.

| SUT1:0            | Start-up Time<br>from Power-down | Additional Delay from<br>Reset (V <sub>CC</sub> = 5.0V) | Recommended<br>Usage |

|-------------------|----------------------------------|---------------------------------------------------------|----------------------|

| 00                | 6 CK                             | 14CK <sup>(1)</sup>                                     | BOD enabled          |

| 01                | 6 CK                             | 14CK + 4 ms                                             | Fast rising power    |

| 10 <sup>(2)</sup> | 6 CK                             | 14CK + 64 ms                                            | Slowly rising power  |

| 11                |                                  | Reserved                                                |                      |

Table 6-7.

Start-up Times for the Internal Calibrated RC Oscillator Clock Selection

Note: 1. If the RSTDISBL fuse is programmed, this start-up time will be increased to 14CK + 4 ms to ensure programming mode can be entered.

2. The device is shipped with this option selected.

## • Bit 2 – PRTIM0: Power Reduction Timer/Counter0

Writing a logic one to this bit shuts down the Timer/Counter0 module. When the Timer/Counter0 is enabled, operation will continue like before the shutdown.

## • Bit 1 – PRUSI: Power Reduction USI

Writing a logic one to this bit shuts down the USI by stopping the clock to the module. When waking up the USI again, the USI should be re initialized to ensure proper operation.

## • Bit 0 – PRADC: Power Reduction ADC

Writing a logic one to this bit shuts down the ADC. The ADC must be disabled before shut down. Also analog comparator needs this clock.

- 1. In the same operation, write a logical one to WDCE and WDE. Even though the WDE always is set, the WDE must be written to one to start the timed sequence.

- 2. Within the next four clock cycles, in the same operation, write the WDP bits as desired, but with the WDCE bit cleared. The value written to the WDE bit is irrelevant.

### 8.3.2 Code Examples

The following code example shows one assembly and one C function for turning off the WDT. The example assumes that interrupts are controlled (e.g., by disabling interrupts globally) so that no interrupts will occur during execution of these functions.

```

Assembly Code Example

WDT off:

wdr

; Clear WDRF in MCUSR

ldi r16, (0<<WDRF)

out MCUSR, r16

; Write logical one to WDCE and WDE

; Keep old prescaler setting to prevent unintentional Watchdog Reset

in r16, WDTCSR

ori r16, (1<<WDCE) | (1<<WDE)

out WDTCSR, r16

; Turn off WDT

ldi r16, (0<<WDE)

out WDTCSR, r16

ret

C Code Example

void WDT_off(void)

{

WDR();

/* Clear WDRF in MCUSR */

MCUSR = 0x00

/* Write logical one to WDCE and WDE */

WDTCSR |= (1<<WDCE) | (1<<WDE);

/* Turn off WDT */

WDTCSR = 0 \times 00;

}

```

Note: See "Code Examples" on page 6.

- ADC10: ADC input Channel 10. Note that ADC input channel 10 uses analog power.

- PCINT15: Pin Change Interrupt source 15.

### Port B, Bit 6 – ADC9/ T0/ INT0/ PCINT14

- ADC9: ADC input Channel 9. Note that ADC input channel 9 uses analog power.

- T0: Timer/Counter0 counter source.

- INT0: The PB6 pin can serve as an External Interrupt source 0.

- PCINT14: Pin Change Interrupt source 14.

### Port B, Bit 5 – XTAL2/ CLKO/ ADC8/ PCINT13

- XTAL2: Chip clock Oscillator pin 2. Used as clock pin for crystal Oscillator or Low-frequency crystal Oscillator. When used as a clock pin, the pin can not be used as an I/O pin.

- CLKO: The divided system clock can be output on the PB5 pin, if the CKOUT Fuse is programmed, regardless of the PORTB5 and DDB5 settings. It will also be output during reset.

- OC1D Output Compare Match output: The PB5 pin can serve as an external output for the Timer/Counter1 Compare Match D when configured as an output (DDA1 set). The OC1D pin is also the output pin for the PWM mode timer function.

- ADC8: ADC input Channel 8. Note that ADC input channel 8 uses analog power.

- PCINT13: Pin Change Interrupt source 13.

### Port B, Bit 4 – XTAL1/ CLKI/ OC1B/ ADC7/ PCINT12

- XTAL1/CLKI: Chip clock Oscillator pin 1. Used for all chip clock sources except internal calibrated RC Oscillator. When used as a clock pin, the pin can not be used as an I/O pin.

- OC1D: Inverted Output Compare Match output: The PB4 pin can serve as an external output for the Timer/Counter1 Compare Match D when configured as an output (DDA0 set). The OC1D pin is also the inverted output pin for the PWM mode timer function.

- ADC7: ADC input Channel 7. Note that ADC input channel 7 uses analog power.

- PCINT12: Pin Change Interrupt source 12.

### • Port B, Bit 3 - OC1B/ PCINT11

- OC1B, Output Compare Match output: The PB3 pin can serve as an external output for the Timer/Counter1 Compare Match B. The PB3 pin has to be configured as an output (DDB3 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function.

- PCINT11: Pin Change Interrupt source 11.

## Port B, Bit 2 – SCK/ USCK/ SCL/ OC1B/ PCINT10

- USCK: Three-wire mode Universal Serial Interface Clock.

- SCL: Two-wire mode Serial Clock for USI Two-wire mode.

- OC1B: Inverted Output Compare Match output: The PB2 pin can serve as an external output for the Timer/Counter1 Compare Match B when configured as an output (DDB2 set). The OC1B pin is also the inverted output pin for the PWM mode timer function.

- PCINT10: Pin Change Interrupt source 10.

if a Compare Match in Timer/Counter0 occurs, i.e., when the OCF0A bit is set in the Timer/Counter 0 Interrupt Flag Register – TIFR0.

### • Bit 3 – OCIE0B: Timer/Counter Output Compare Match B Interrupt Enable

When the OCIE0B bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter Compare Match B interrupt is enabled. The corresponding interrupt is executed if a Compare Match in Timer/Counter occurs, i.e., when the OCF0B bit is set in the Timer/Counter Interrupt Flag Register – TIFR0.

### • Bit 1 – TOIE0: Timer/Counter0 Overflow Interrupt Enable

When the TOIE0 bit is written to one, and the I-bit in the Status Register is set, the Timer/Counter0 Overflow interrupt is enabled. The corresponding interrupt is executed if an overflow in Timer/Counter0 occurs, i.e., when the TOV0 bit is set in the Timer/Counter 0 Interrupt Flag Register – TIFR0.

### • Bit 0 – TICIE0: Timer/Counter0, Input Capture Interrupt Enable

When this bit is written to one, and the I-flag in the Status Register is set (interrupts globally enabled), the Timer/Counter1 Input Capture interrupt is enabled. The corresponding Interrupt Vector (See "Interrupts" on page 50.) is executed when the ICF0 flag, located in TIFR, is set.

### 11.10.8 TIFR – Timer/Counter0 Interrupt Flag Register

| Bit           | 7     | 6     | 5     | 4     | 3     | 2    | 1    | 0    |      |

|---------------|-------|-------|-------|-------|-------|------|------|------|------|

| 0x38 (0x58)   | OCF1D | OCF1A | OCF1B | OCF0A | OCF0B | TOV1 | TOV0 | ICF0 | TIFR |

| Read/Write    | R/W   | R/W   | R/W   | R/W   | R/W   | R/W  | R/W  | R    |      |

| Initial Value | 0     | 0     | 0     | 0     | 0     | 0    | 0    | 0    |      |

## • Bit 4 – OCF0A: Output Compare Flag 0 A

The OCF0A bit is set when a Compare Match occurs between the Timer/Counter0 and the data in OCR0A – Output Compare Register0. OCF0A is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0A is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0A (Timer/Counter0 Compare Match Interrupt Enable), and OCF0A are set, the Timer/Counter0 Compare Match Interrupt is executed.

The OCF0A is also set in 16-bit mode when a Compare Match occurs between the Timer/Counter and 16-bit data in OCR0B/A. The OCF0A is not set in Input Capture mode when the Output Compare Register OCR0A is used as an Input Capture Register.

## • Bit 3 – OCF0B: Output Compare Flag 0 B

The OCF0B bit is set when a Compare Match occurs between the Timer/Counter and the data in OCR0B – Output Compare Register0 B. OCF0B is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, OCF0B is cleared by writing a logic one to the flag. When the I-bit in SREG, OCIE0B (Timer/Counter Compare B Match Interrupt Enable), and OCF0B are set, the Timer/Counter Compare Match Interrupt is executed.

The OCF0B is not set in 16-bit Output Compare mode when the Output Compare Register OCR0B is used as the high byte of the 16-bit Output Compare Register or in 16-bit Input Capture mode when the Output Compare Register OCR0B is used as the high byte of the Input Capture Register.

2588F-AVR-06/2013

The counter value (TCNT1) that is shown as a histogram in Figure 12-11 is incremented until the counter value matches the TOP value. The counter is then cleared at the following clock cycle The diagram includes the Waveform Output (OCW1x) in toggle Compare Mode. The small horizontal line marks on the TCNT1 slopes represent Compare Matches between OCR1x and TCNT1.

The Timer/Counter Overflow Flag (TOV1) is set in the same clock cycle as the TCNT1 becomes zero. The TOV1 Flag in this case behaves like a 11th bit, except that it is only set, not cleared. However, combined with the timer overflow interrupt, that automatically clears the TOV1 Flag, the timer resolution can be increased by software. There are no special cases to consider in the Normal mode, a new counter value can be written anytime.

The Output Compare Unit can be used to generate interrupts at some given time. Using the Output Compare to generate waveforms in Normal mode is not recommended, since this will occupy too much of the CPU time. For generating a waveform, the OCW1x output can be set to toggle its logical level on each Compare Match by setting the Compare Output mode bits to toggle mode (COM1x1:0 = 1). The OC1x value will not be visible on the port pin unless the data direction for the pin is set to output. The waveform generated will have a maximum frequency of  $f_{OC1x} = f_{clkT1}/4$  when OCR1C is set to zero. The waveform frequency is defined by the following equation:

$$f_{OC1x} = \frac{f_{clkT1}}{2 \cdot (1 + OCR1C)}$$

Resolution, R<sub>PWM</sub>, shows how many bit is required to express the value in the OCR1C register and it can be calculated using the following equation:

$$R_{PWM} = \log_2(OCR1C + 1)$$

The Output Compare Pin configurations in Normal Mode are described in Table 12-2.

| COM1x1 | COM1x0 | OC1x Pin     | OC1x Pin     |

|--------|--------|--------------|--------------|

| 0      | 0      | Disconnected | Disconnected |

| 0      | 1      | Disconnected | OC1x         |

| 1      | 0      | Disconnected | OC1x         |

| 1      | 1      | Disconnected | OC1x         |

Table 12-2.

Output Compare Pin Configurations in Normal Mode

### 12.8.2 Fast PWM Mode

The fast Pulse Width Modulation or fast PWM mode (PWM1A/PWM1B = 1 and WGM11:10 = 00) provides a high frequency PWM waveform generation option. The fast PWM differs from the other PWM option by its single-slope operation. The counter counts from BOTTOM to TOP (defined as OCR1C) then restarts from BOTTOM. In non-inverting Compare Output mode the Waveform Output (OCW1x) is cleared on the Compare Match between TCNT1 and OCR1x and set at BOTTOM. In inverting Compare Output mode, the Waveform Output is set on Compare Match and cleared at BOTTOM. In complementary Compare Output mode the Waveform Output is cleared on the Compare Output mode the Waveform Output is set on Compare Match and cleared at BOTTOM. In complementary Compare Output mode the Waveform Output is cleared on the Compare Match and set at BOTTOM.

Due to the single-slope operation, the operating frequency of the fast PWM mode can be twice as high as the Phase and Frequency Correct PWM mode that use dual-slope operation. This high frequency makes the fast PWM mode well suited for power regulation, rectification, and

| COM1D1 | COM1D0 | OC1D Pin (PB4) | OC1D Pin (PB5) |

|--------|--------|----------------|----------------|

| 0      | 0      | Disconnected   | Disconnected   |

| 0      | 1      | OC1A • OC1OE4  | OC1A • OC1OE5  |

| 1      | 0      | OC1A • OC1OE4  | OC1A • OC1OE5  |

| 1      | 1      | OC1A • OC1OE4  | OC1A • OC1OE5  |

Table 12-7.

Configuration of Output Compare Pins OC1D and OC1D in PWM6 Mode

## 12.9 Timer/Counter Timing Diagrams

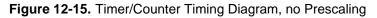

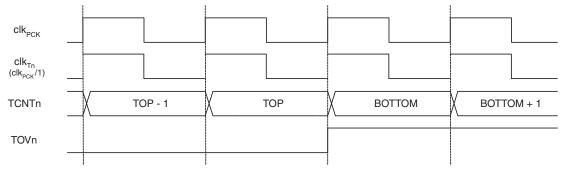

The Timer/Counter is a synchronous design and the timer clock  $(clk_{T1})$  is therefore shown as a clock enable signal in the following figures. The figures include information on when Interrupt Flags are set.

Figure 12-15 contains timing data for basic Timer/Counter operation. The figure shows the count sequence close to the MAX value in all modes other than Phase and Frequency Correct PWM Mode.

Figure 12-16 shows the same timing data, but with the prescaler enabled, in all modes other than Phase and Frequency Correct PWM Mode.

Figure 12-17 shows the setting of OCF1A, OCF1B and OCF1D in all modes.

## 12.12 Register Description

|               |        | 0      |        |        |       |       |       |       |        |

|---------------|--------|--------|--------|--------|-------|-------|-------|-------|--------|

| Bit           | 7      | 6      | 5      | 4      | 3     | 2     | 1     | 0     |        |

| 0x30 (0x50)   | COM1A1 | COM1A0 | COM1B1 | COM1B0 | FOC1A | FOC1B | PWM1A | PWM1B | TCCR1A |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | W     | W     | R/W   | R/W   |        |

| Initial value | 0      | 0      | 0      | 0      | 0     | 0     | 0     | 0     |        |

## 12.12.1 TCCR1A – Timer/Counter1 Control Register A

### • Bits 7,6 – COM1A1, COM1A0: Comparator A Output Mode, Bits 1 and 0

These bits control the behaviour of the Waveform Output (OCW1A) and the connection of the Output Compare pin (OC1A). If one or both of the COM1A1:0 bits are set, the OC1A output overrides the normal port functionality of the I/O pin it is connected to. The complementary OC1B output is connected only in PWM modes when the COM1A1:0 bits are set to "01". Note that the Data Direction Register (DDR) bit corresponding to the OC1A and OC1A pins must be set in order to enable the output driver.

The function of the COM1A1:0 bits depends on the PWM1A, WGM10 and WGM11 bit settings. Table 12-8 shows the COM1A1:0 bit functionality when the PWM1A bit is set to Normal Mode (non-PWM).

| COM1A1:0 | OCW1A Behaviour          | OC1A Pin     | OC1A Pin     |

|----------|--------------------------|--------------|--------------|

| 00       | Normal port operation.   | Disconnected | Disconnected |

| 01       | Toggle on Compare Match. | Connected    | Disconnected |

| 10       | Clear on Compare Match.  | Connected    | Disconnected |

| 11       | Set on Compare Match.    | Connected    | Disconnected |

Table 12-8.

Compare Output Mode, Normal Mode (non-PWM)

Table 12-9 shows the COM1A1:0 bit functionality when the PWM1A, WGM10 and WGM11 bits are set to fast PWM mode.

| COM1A1:0 | OCW1A Behaviour                                      | OC1A         | OC1A         |

|----------|------------------------------------------------------|--------------|--------------|

| 00       | Normal port operation.                               | Disconnected | Disconnected |

| 01       | Cleared on Compare Match.<br>Set when TCNT1 = 0x000. | Connected    | Connected    |

| 10       | Cleared on Compare Match.<br>Set when TCNT1 = 0x000. | Connected    | Disconnected |

| 11       | Set on Compare Match.<br>Cleared when TCNT1 = 0x000. | Connected    | Disconnected |

**Table 12-9.**Compare Output Mode, Fast PWM Mode

## 13. USI – Universal Serial Interface

## 13.1 Features

- Two-wire Synchronous Data Transfer (Master or Slave)

- Three-wire Synchronous Data Transfer (Master or Slave)

- Data Received Interrupt

- Wakeup from Idle Mode

- In Two-wire Mode: Wake-up from All Sleep Modes, Including Power-down Mode

- Two-wire Start Condition Detector with Interrupt Capability

## 13.2 Overview

The Universal Serial Interface, or USI, provides the basic hardware resources needed for serial communication. Combined with a minimum of control software, the USI allows significantly higher transfer rates and uses less code space than solutions based on software only. Interrupts are included to minimize the processor load.

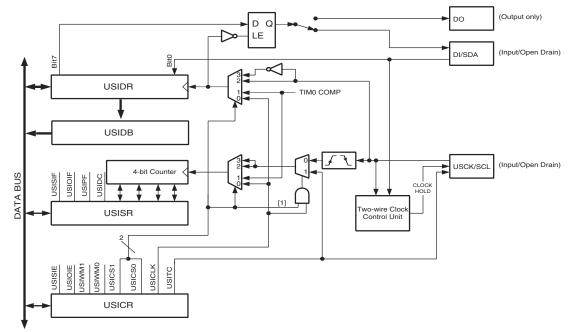

A simplified block diagram of the USI is shown in Figure 13-1 For actual placement of I/O pins refer to "Pinout ATtiny261/461/861 and ATtiny261V/461V/861V" on page 2. Device-specific I/O Register and bit locations are listed in the "Register Descriptions" on page 132.

Figure 13-1. Universal Serial Interface, Block Diagram

The 8-bit USI Data Register (USIDR) is directly accessible via the data bus and contains the incoming and outgoing data. The register has no buffering so the data must be read as quickly as possible to ensure that no data is lost. The data register is a serial shift register where the most significant bit is connected to one of two output pins depending of the wire mode configuration. A transparent latch between the output of the data register and the output pin delays the change of data output to the opposite clock edge of the data input sampling. The serial input is always sampled from the Data Input (DI) pin, regardless of the configuration.

The 4-bit counter increments by one for each clock generated either by the external clock edge detector, by a Timer/Counter0 Compare Match, or by software using USICLK or USITC strobe bits. The clock source depends of the setting of the USICS1:0 bits. For external clock operation a special feature is added that allows the clock to be generated by writing to the USITC strobe bit. This feature is enabled by write a one to the USICLK bit while setting an external clock source (USICS1 = 1).

Note that even when no wire mode is selected (USIWM1:0 = 0) the external clock input (USCK/SCL) are can still be used by the counter.

### 13.5.4 USICR – USI Control Register

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0     |       |

|---------------|--------|--------|--------|--------|--------|--------|--------|-------|-------|

| 0x0D (0x2D)   | USISIE | USIOIE | USIWM1 | USIWM0 | USICS1 | USICS0 | USICLK | USITC | USICR |

| Read/Write    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | W      | W     | -     |

| Initial Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0     |       |

The Control Register includes interrupt enable control, wire mode setting, Clock Select setting, and clock strobe.

### • Bit 7 – USISIE: Start Condition Interrupt Enable

Setting this bit to one enables the Start Condition detector interrupt. If there is a pending interrupt when the USISIE and the Global Interrupt Enable Flag is set to one, this will immediately be executed. Refer to the USISIF bit description on page 133 for further details.

### • Bit 6 – USIOIE: Counter Overflow Interrupt Enable

Setting this bit to one enables the Counter Overflow interrupt. If there is a pending interrupt when the USIOIE and the Global Interrupt Enable Flag is set to one, this will immediately be executed. Refer to the USIOIF bit description on page 133 for further details.

### • Bits 5:4 – USIWM1:0: Wire Mode

These bits set the type of wire mode to be used, as shown in Table 13-1 on page 134.

Basically, only the function of the outputs are affected by these bits. Data and clock inputs are not affected by the mode selected and will always have the same function. The counter and USI Data Register can therefore be clocked externally, and data input sampled, even when outputs are disabled.

| USIWM1 | USIWM0                                                                                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

|--------|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0      | 0 0 Outputs, clock hold, and start detector disabled.<br>Port pins operate as normal. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| 0      | 1                                                                                     | Three-wire mode. Uses DO, DI, and USCK pins.<br>The <i>Data Output</i> (DO) pin overrides the corresponding bit in the PORTA register. However, the corresponding DDRA bit still controls the data direction.<br>When the port pin is set as input the pin pull-up is controlled by the PORTA bit.<br>The <i>Data Input</i> (DI) and <i>Serial Clock</i> (USCK) pins do not affect the normal port operation. When operating as master, clock pulses are software generated by toggling the PORTA register, while the data direction is set to output. The USITC bit in the USICR Register can be used for this purpose. |  |  |  |  |

| Table 13-1. | Relationship betwe | en USIWM1:0 and U | SI Operation |

|-------------|--------------------|-------------------|--------------|

|-------------|--------------------|-------------------|--------------|

# ATtiny261/461/861

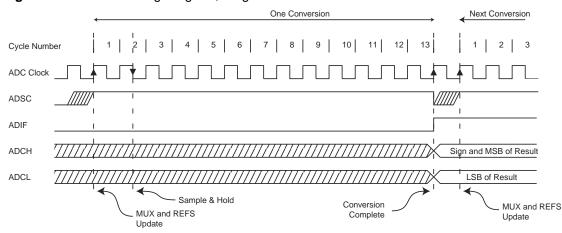

Figure 15-5. ADC Timing Diagram, Single Conversion

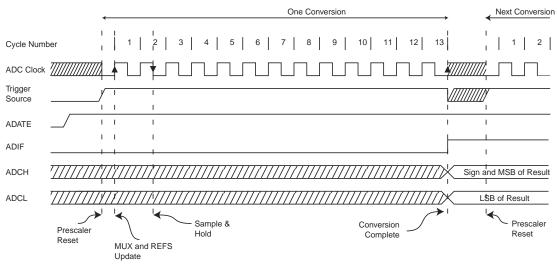

When Auto Triggering is used, the prescaler is reset when the trigger event occurs. See Figure 15-6. This assures a fixed delay from the trigger event to the start of conversion. In this mode, the sample-and-hold takes place two ADC clock cycles after the rising edge on the trigger source signal. Three additional CPU clock cycles are used for synchronization logic.

Figure 15-6. ADC Timing Diagram, Auto Triggered Conversion

In Free Running mode (see Figure 15-7), a new conversion will be started immediately after the conversion completes, while ADSC remains high.

Atmel

If these bits are changed during a conversion, the change will not go into effect until this conversion is complete (ADIF in ADCSRA is set).

15.13.2 ADCSRA – ADC Control and Status Register A

| Bit           | 7    | 6    | 5     | 4    | 3    | 2     | 1     | 0     | _      |

|---------------|------|------|-------|------|------|-------|-------|-------|--------|

| 0x06 (0x26)   | ADEN | ADSC | ADATE | ADIF | ADIE | ADPS2 | ADPS1 | ADPS0 | ADCSRA |

| Read/Write    | R/W  | R/W  | R/W   | R/W  | R/W  | R/W   | R/W   | R/W   | •      |

| Initial Value | 0    | 0    | 0     | 0    | 0    | 0     | 0     | 0     |        |

### • Bit 7 – ADEN: ADC Enable

Writing this bit to one enables the ADC. By writing it to zero, the ADC is turned off. Turning the ADC off while a conversion is in progress, will terminate this conversion.

### Bit 6 – ADSC: ADC Start Conversion

In Single Conversion mode, write this bit to one to start each conversion. In Free Running mode, write this bit to one to start the first conversion. The first conversion after ADSC has been written after the ADC has been enabled, or if ADSC is written at the same time as the ADC is enabled, will take 25 ADC clock cycles instead of the normal 13. This first conversion performs initialization of the ADC.

ADSC will read as one as long as a conversion is in progress. When the conversion is complete, it returns to zero. Writing zero to this bit has no effect.

### • Bit 5 – ADATE: ADC Auto Trigger Enable

When this bit is written to one, Auto Triggering of the ADC is enabled. The ADC will start a conversion on a positive edge of the selected trigger signal. The trigger source is selected by setting the ADC Trigger Select bits, ADTS in ADCSRB.

### Bit 4 – ADIF: ADC Interrupt Flag

This bit is set when an ADC conversion completes and the data registers are updated. The ADC Conversion Complete Interrupt is executed if the ADIE bit and the I-bit in SREG are set. ADIF is cleared by hardware when executing the corresponding interrupt handling vector. Alternatively, ADIF is cleared by writing a logical one to the flag. Beware that if doing a Read-Modify-Write on ADCSRA, a pending interrupt can be disabled. This also applies if the SBI and CBI instructions are used.

### • Bit 3 – ADIE: ADC Interrupt Enable

When this bit is written to one and the I-bit in SREG is set, the ADC Conversion Complete Interrupt is activated.

### Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits

These bits determine the division factor between the system clock frequency and the input clock to the ADC.

| ADPS2 | ADPS1 | ADPS0 | Division Factor |

|-------|-------|-------|-----------------|

| 0     | 0     | 0     | 2               |

| 0     | 0     | 1     | 2               |

| 0     | 1     | 0     | 4               |

Table 15-5. ADC Prescaler Selections

## 17.9 Register Description

### 17.9.1 SPMCSR – Store Program Memory Control and Status Register

The Store Program Memory Control and Status Register contains the control bits needed to control the Program memory operations.

| Bit           | 7 | 6 | 5 | 4    | 3    | 2     | 1     | 0     | _      |

|---------------|---|---|---|------|------|-------|-------|-------|--------|

| 0x37 (0x57)   | - | - | - | СТРВ | RFLB | PGWRT | PGERS | SPMEN | SPMCSR |

| Read/Write    | R | R | R | R/W  | R/W  | R/W   | R/W   | R/W   | -      |

| Initial Value | 0 | 0 | 0 | 0    | 0    | 0     | 0     | 0     |        |

### • Bits 7:5 - Res: Reserved Bits

These bits are reserved and always read as zero.

## • Bit 4 – CTPB: Clear Temporary Page Buffer

If the CTPB bit is written while filling the temporary page buffer, the temporary page buffer will be cleared and the data will be lost.

### Bit 3 – RFLB: Read Fuse and Lock Bits

An LPM instruction within three cycles after RFLB and SPMEN are set in the SPMCSR Register, will read either the Lock bits or the Fuse bits (depending on Z0 in the Z-pointer) into the destination register. See "EEPROM Write Prevents Writing to SPMCSR" on page 167 for details.

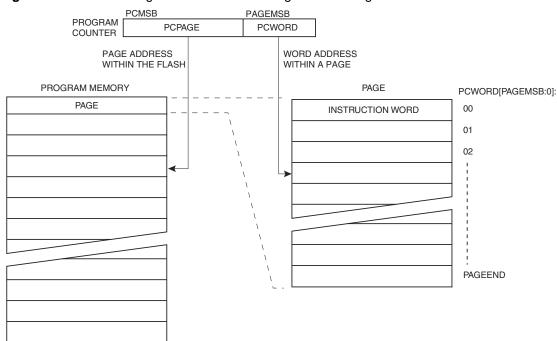

## • Bit 2 – PGWRT: Page Write

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles executes Page Write, with the data stored in the temporary buffer. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGWRT bit will auto-clear upon completion of a Page Write, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

## • Bit 1 – PGERS: Page Erase

If this bit is written to one at the same time as SPMEN, the next SPM instruction within four clock cycles executes Page Erase. The page address is taken from the high part of the Z-pointer. The data in R1 and R0 are ignored. The PGERS bit will auto-clear upon completion of a Page Erase, or if no SPM instruction is executed within four clock cycles. The CPU is halted during the entire Page Write operation.

### • Bit 0 – SPMEN: Store Program Memory Enable

This bit enables the SPM instruction for the next four clock cycles. If written to one together with either CTPB, RFLB, PGWRT, or PGERS, the following SPM instruction will have a special meaning, see description above. If only SPMEN is written, the following SPM instruction will store the value in R1:R0 in the temporary page buffer addressed by the Z-pointer. The LSB of the Z-pointer is ignored. The SPMEN bit will auto-clear upon completion of an SPM instruction, or if no SPM instruction is executed within four clock cycles. During Page Erase and Page Write, the SPMEN bit remains high until the operation is completed.

Writing any other combination than "10001", "01001", "00101", "00011" or "00001" in the lower five bits will have no effect.

**Figure 18-4.** Addressing the Flash Which is Organized in Pages

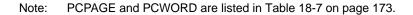

In the figure below, "XX" means don't care. The numbers in the figure refer to the programming description above.

WR

### 18.7.6 Programming the EEPROM

The EEPROM is organized in pages, see Table 18-8 on page 173. When programming the EEPROM, the program data is latched into a page buffer. This allows one page of data to be

# 182 ATtiny261/461/861

| Symbol          | Parameter                           | Condition                       | Min | <b>Typ</b> <sup>(1)</sup> | Мах | Units |

|-----------------|-------------------------------------|---------------------------------|-----|---------------------------|-----|-------|

| I <sub>CC</sub> | Power Supply Current <sup>(7)</sup> | Active 1MHz, $V_{CC} = 2V$      |     | 0.4                       | 0.6 | mA    |

|                 |                                     | Active 4MHz, $V_{CC} = 3V$      |     | 2                         | 3   | mA    |

|                 |                                     | Active 8MHz, $V_{CC} = 5V$      |     | 6                         | 9   | mA    |

|                 |                                     | Idle 1MHz, V <sub>CC</sub> = 2V |     | 0.1                       | 0.3 | mA    |

|                 |                                     | Idle 4MHz, V <sub>CC</sub> = 3V |     | 0.4                       | 1   | mA    |

|                 |                                     | Idle 8MHz, V <sub>CC</sub> = 5V |     | 1.5                       | 3   | mA    |

|                 | Power-down mode <sup>(8)</sup>      | WDT enabled, $V_{CC} = 3V$      |     | 4                         | 10  | μA    |

|                 |                                     | WDT disabled, $V_{CC} = 3V$     |     | 0.15                      | 2   | μA    |

## **Table 19-1.** DC Characteristics. $T_A = -40^{\circ}$ C to $+85^{\circ}$ C, $V_{CC} = 1.8$ V to 5.5V (unless otherwise noted).

Notes: 1. Typical values at +25°C.

- 2. "Min" means the lowest value where the pin is guaranteed to be read as high.

- 3. "Max" means the highest value where the pin is guaranteed to be read as low.

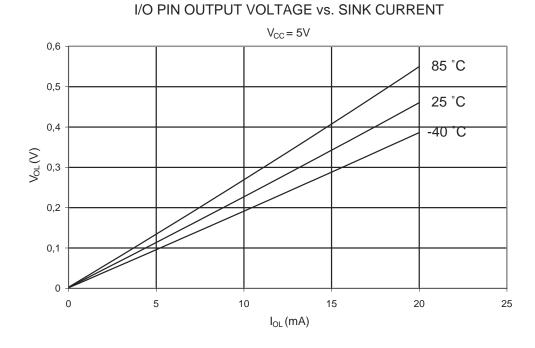

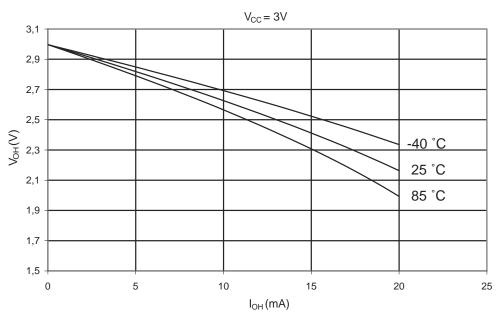

- 4. Although each I/O port can sink more than the test conditions (10 mA at V<sub>CC</sub> = 5V, 5 mA at V<sub>CC</sub> = 3V) under steady state conditions (non-transient), the sum of all I<sub>OL</sub> (for all ports) should not exceed 60 mA. If I<sub>OL</sub> exceeds the test conditions, V<sub>OL</sub> may exceed the related specification. Pins are not guaranteed to sink current greater than the listed test condition.

- 5. Although each I/O port can source more than the test conditions (10 mA at  $V_{CC} = 5V$ , 5 mA at  $V_{CC} = 3V$ ) under steady state conditions (non-transient), the sum of all I<sub>OH</sub> (for all ports) should not exceed 60 mA. If I<sub>OH</sub> exceeds the test condition,  $V_{OH}$  may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition.

- The RESET pin must tolerate high voltages when entering and operating in programming modes and, as a consequence, has a weak drive strength as compared to regular I/O pins. See Figure 20-23, Figure 20-24, Figure 20-25, and Figure 20-26 (starting on page 209).

- 7. Values are with external clock using methods described in "Minimizing Power Consumption" on page 37. Power Reduction is enabled (PRR = 0xFF) and there is no I/O drive.

- 8. BOD Disabled.

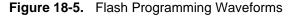

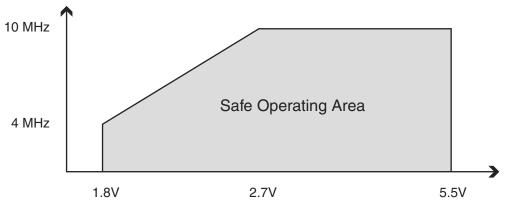

## 19.3 Speed

The maximum operating frequency of the device depends on V<sub>CC</sub>. As shown in Figure 19-1 and Figure 19-2, the maximum frequency vs. V<sub>CC</sub> relationship is linear between  $1.8V < V_{CC} < 2.7V$  and between  $2.7V < V_{CC} < 4.5V$ .

| PRR bit | Additional Current consumption<br>compared to Active with external<br>clock (see Figure 20-1 on page<br>198 and Figure 20-2 on page 199) | Additional Current consumption<br>compared to Idle with external<br>clock (see Figure 20-6 on page<br>201 and Figure 20-7 on page 201) |  |  |  |

|---------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| PRTIM1  | 26.9 %                                                                                                                                   | 103.7 %                                                                                                                                |  |  |  |

| PRTIM0  | 2.6 %                                                                                                                                    | 10.0 %                                                                                                                                 |  |  |  |

| PRUSI   | 1.7 %                                                                                                                                    | 6.5 %                                                                                                                                  |  |  |  |

| PRADC   | 7.1 %                                                                                                                                    | 27.3 %                                                                                                                                 |  |  |  |

It is possible to calculate the typical current consumption based on the numbers from Table 20-1 for other  $V_{CC}$  and frequency settings than listed in Table 20-2.

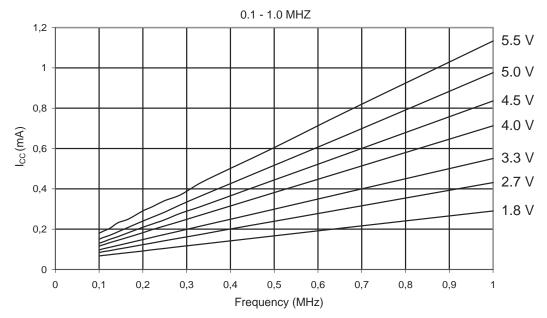

#### 20.1.0.1 Example

Calculate the expected current consumption in idle mode with TIMER0, ADC, and USI enabled at  $V_{CC}$  = 2.0V and F = 1MHz. From Table 20-2, third column, we see that we need to add 10% for the TIMER0, 27.3 % for the ADC, and 6.5 % for the USI module. Reading from Figure 20-6 on page 201, we find that the idle current consumption is ~0,085 mA at  $V_{CC}$  = 2.0V and F=1MHz. The total current consumption in idle mode with TIMER0, ADC, and USI enabled, gives:

$ICC_{total} \approx 0.085 mA \bullet (1 + 0.10 + 0.273 + 0.065) \approx 0.122 mA$

## 20.2 Active Supply Current

### Figure 20-1. Active Supply Current vs. Low Frequency (0.1 - 1.0 MHz)

# 198 ATtiny261/461/861

Figure 20-20. I/O Pin Output Voltage vs. Sink Current ( $V_{CC} = 5V$ )

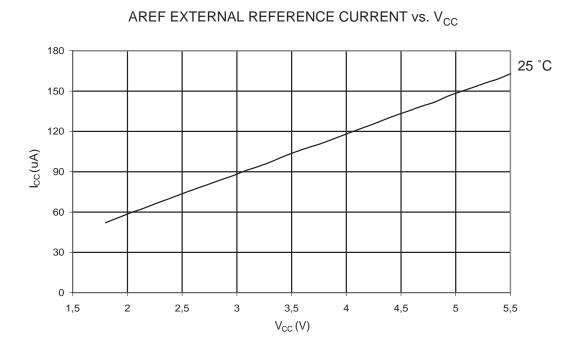

Figure 20-42. AREF External Reference Current vs. V<sub>CC</sub>

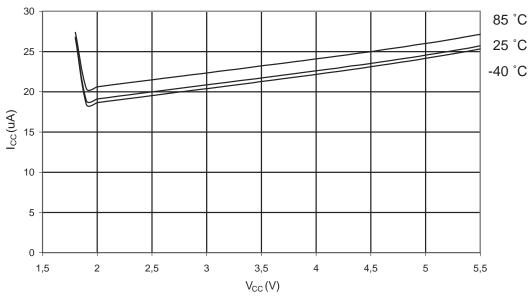

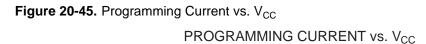

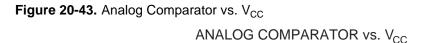

Figure 20-44. Brownout Detector Current vs.  $V_{CC}$ BROWNOUT DETECTOR CURRENT vs.  $V_{CC}$