## Microchip Technology - ATTINY861V-10SU Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | AVR                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 10MHz                                                                     |

| Connectivity               | USI                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 16                                                                        |

| Program Memory Size        | 8KB (4K x 16)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 512 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b                                                                |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                                            |

| Supplier Device Package    | 20-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/attiny861v-10su |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The calibrated Oscillator is used to time the EEPROM accesses. Make sure the Oscillator frequency is within the requirements described in "OSCCAL – Oscillator Calibration Register" on page 32.

#### 5.3.6 Program Examples

The following code examples show one assembly and one C function for erase, write, or atomic write of the EEPROM. The examples assume that interrupts are controlled (e.g., by disabling interrupts globally) so that no interrupts will occur during execution of these functions.

Assembly Code Example

```

EEPROM write:

; Wait for completion of previous write

sbic EECR, EEPE

rjmp EEPROM_write

; Set Programming mode

ldi r16, (0<<EEPM1) | (0<<EEPM0)

out EECR, r16

; Set up address (r18:r17) in address register

out EEARH, r18

out EEARL, r17

; Write data (r19) to data register

out EEDR, r19

; Write logical one to EEMPE

sbi EECR, EEMPE

; Start eeprom write by setting EEPE

sbi EECR, EEPE

ret

```

C Code Example

```

void EEPROM_write(unsigned char ucAddress, unsigned char ucData)

{

/* Wait for completion of previous write */

while(EECR & (1<<EPE))

;

/* Set Programming mode */

EECR = (0<<EEPM1) | (0<<EEPM0);

/* Set up address and data registers */

EEAR = ucAddress;

EEDR = ucData;

/* Write logical one to EEMPE */

EECR |= (1<<EEMPE);

/* Start eeprom write by setting EEPE */

EECR |= (1<<EEPE);

}</pre>

```

#### Note: See "Code Examples" on page 6.

ATtiny261/461/861

#### 6.1.3 Flash Clock – clk<sub>FLASH</sub>

The Flash clock controls operation of the Flash interface. The Flash clock is usually active simultaneously with the CPU clock.

## 6.1.4 ADC Clock – clk<sub>ADC</sub>

The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks in order to reduce noise generated by digital circuitry. This gives more accurate ADC conversion results.

#### 6.1.5 Fast Peripheral Clock – clk<sub>PCK</sub>

Selected peripherals can be clocked at a frequency higher than the CPU core. The fast peripheral clock is generated by an on-chip PLL circuit.

#### 6.1.6 PLL System Clock – clk<sub>ADC</sub>

The PLL can also be used to generate a system clock. The clock signal can be prescaled to avoid overclocking the CPU.

#### 6.2 Clock Sources

The device has the following clock source options, selectable by Flash Fuse bits as shown below. The clock from the selected source is input to the AVR clock generator, and routed to the appropriate modules.

| Device Clocking Option                                             | CKSEL3:0     | PB4   | PB5   |

|--------------------------------------------------------------------|--------------|-------|-------|

| External Clock (see page 26)                                       | 0000         | XTAL1 | I/O   |

| High-Frequency PLL Clock (see page 26)                             | 0001         | I/O   | I/O   |

| Calibrated Internal 8 MHz Oscillator (see page 28)                 | 0010         | I/O   | I/O   |

| Internal 128 kHz Oscillator (see page 29)                          | 0011         | I/O   | I/O   |

| Low-Frequency Crystal Oscillator (see page 29)                     | 01xx         | XTAL1 | XTAL2 |

| Crystal Oscillator / Ceramic Resonator<br>0.40.9 MHz (see page 30) | 1000<br>1001 | XTAL1 | XTAL2 |

| Crystal Oscillator / Ceramic Resonator<br>0.93.0 MHz (see page 30) | 1010<br>1011 | XTAL1 | XTAL2 |

| Crystal Oscillator / Ceramic Resonator<br>38 MHz (see page 30)     | 1100<br>1101 | XTAL1 | XTAL2 |

| Crystal Oscillator / Ceramic Resonator<br>820 MHz (see page 30)    | 1110<br>1111 | XTAL1 | XTAL2 |

Table 6-1.

Device Clocking Options Select<sup>(1)</sup> vs. PB4 and PB5 Functionality

Note: 1. For all fuses "1" means unprogrammed and "0" means programmed.

The various choices for each clocking option is given in the following sections. When the CPU wakes up from Power-down or Power-save, the selected clock source is used to time the startup, ensuring stable oscillator operation before instruction execution starts. When the CPU starts from reset, there is an additional delay allowing the power to reach a stable level before com-

From the time the CLKPS values are written, it takes between T1 + T2 and T1 +  $2^{T2}$  before the new clock frequency is active. In this interval, two active clock edges are produced. Here, T1 is the previous clock period, and T2 is the period corresponding to the new prescaler setting.

### 6.4 Clock Output Buffer

The device can output the system clock on the CLKO pin (when not used as XTAL2 pin). To enable the output, the CKOUT Fuse has to be programmed. This mode is suitable when the chip clock is used to drive other circuits on the system. Note that the clock will not be output during reset and the normal operation of I/O pin will be overridden when the fuse is programmed. Internal RC Oscillator, WDT Oscillator, PLL, and external clock (CLKI) can be selected when the clock is output on CLKO. Crystal oscillators (XTAL1, XTAL2) can not be used for clock output on CLKO. If the System Clock Prescaler is used, it is the divided system clock that is output.

### 6.5 Register Description

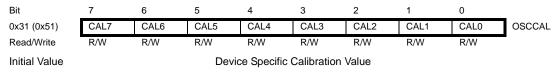

### 6.5.1 OSCCAL – Oscillator Calibration Register

#### • Bits 7:0 – CAL7:0: Oscillator Calibration Value

The Oscillator Calibration Register is used to trim the Calibrated Internal RC Oscillator to remove process variations from the oscillator frequency. A pre-programmed calibration value is automatically written to this register during chip reset, giving the Factory calibrated frequency as specified in Table 19-2 on page 189. The application software can write this register to change the oscillator frequency. The oscillator can be calibrated to frequencies as specified in Table 19-2 on page 189. The application software development of the specified in Table 19-2 on page 189. The application software can write this register to change the oscillator frequency. The oscillator can be calibrated to frequencies as specified in Table 19-2 on page 189. Calibration outside that range is not guaranteed.

Note that this oscillator is used to time EEPROM and Flash write accesses, and these write times will be affected accordingly. If the EEPROM or Flash are written, do not calibrate to more than 8.8 MHz. Otherwise, the EEPROM or Flash write may fail.

The CAL7 bit determines the range of operation for the oscillator. Setting this bit to 0 gives the lowest frequency range, setting this bit to 1 gives the highest frequency range. The two frequency ranges are overlapping, in other words a setting of OSCCAL = 0x7F gives a higher frequency than OSCCAL = 0x80.

The CAL6:0 bits are used to tune the frequency within the selected range. A setting of 0x00 gives the lowest frequency in that range, and a setting of 0x7F gives the highest frequency in the range.

#### 6.5.2 CLKPR – Clock Prescale Register

| Bit           | 7      | 6 | 5 | 4 | 3          | 2         | 1      | 0      | _     |

|---------------|--------|---|---|---|------------|-----------|--------|--------|-------|

| 0x28 (0x48)   | CLKPCE | - | - | - | CLKPS3     | CLKPS2    | CLKPS1 | CLKPS0 | CLKPR |

| Read/Write    | R/W    | R | R | R | R/W        | R/W       | R/W    | R/W    |       |

| Initial Value | 0      | 0 | 0 | 0 | See Bit De | scription |        |        |       |

#### • Bit 7 – CLKPCE: Clock Prescaler Change Enable

The CLKPCE bit must be written to logic one to enable change of the CLKPS bits. The CLKPCE bit is only updated when the other bits in CLKPR are simultaniosly written to zero. CLKPCE is

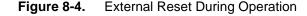

#### 8.1.2 External Reset

An External Reset is generated by a low level on the  $\overline{\text{RESET}}$  pin if enabled. Reset pulses longer than the minimum pulse width (see "System and Reset Characteristics" on page 190) will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset. When the applied signal reaches the Reset Threshold Voltage –  $V_{RST}$  – on its positive edge, the delay counter starts the MCU after the Time-out period –  $t_{TOUT}$  – has expired.

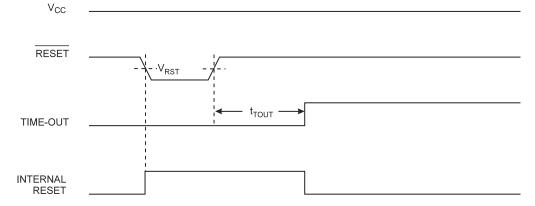

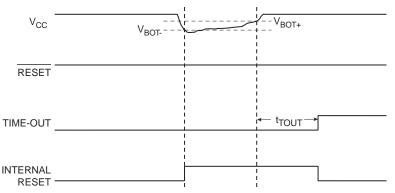

#### 8.1.3 Brown-out Detection

ATtiny261/461/861 has an On-chip Brown-out Detection (BOD) circuit for monitoring the V<sub>CC</sub> level during operation by comparing it to a fixed trigger level. The trigger level for the BOD can be selected by the BODLEVEL Fuses. The trigger level has a hysteresis to ensure spike free Brown-out Detection. The hysteresis on the detection level should be interpreted as V<sub>BOT+</sub> = V<sub>BOT</sub> + V<sub>HYST</sub>/2 and V<sub>BOT-</sub> = V<sub>BOT</sub> - V<sub>HYST</sub>/2.

When the BOD is enabled, and V<sub>CC</sub> decreases to a value below the trigger level (V<sub>BOT</sub> in Figure 8-5), the Brown-out Reset is immediately activated. When V<sub>CC</sub> increases above the trigger level (V<sub>BOT</sub> in Figure 8-5), the delay counter starts the MCU after the Time-out period  $t_{TOUT}$  has expired.

The BOD circuit will only detect a drop in  $V_{CC}$  if the voltage stays below the trigger level for longer than  $t_{BOD}$  given in "System and Reset Characteristics" on page 190.

Atmel

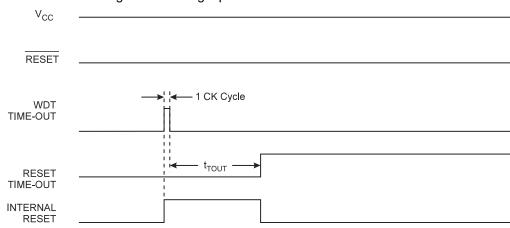

#### 8.1.4 Watchdog Reset

When the Watchdog times out, it will generate a short reset pulse of one CK cycle duration. On the falling edge of this pulse, the delay timer starts counting the Time-out period  $t_{TOUT}$ . Refer to "Watchdog Timer" on page 44 for details on operation of the Watchdog Timer.

Figure 8-6. Watchdog Reset During Operation

#### 8.2 Internal Voltage Reference

ATtiny261/461/861 features an internal bandgap reference. This reference is used for Brown-out Detection, and it can be used as an input to the Analog Comparator or the ADC. The bandgap voltage varies with supply voltage and temperature, as can be seen in Figure 20-36 on page 216.

#### 8.2.1 Voltage Reference Enable Signals and Start-up Time

The voltage reference has a start-up time that may influence the way it should be used. The start-up time is given in "System and Reset Characteristics" on page 190. To save power, the reference is not always turned on. The reference is on during the following situations:

- 1. When the BOD is enabled (by programming the BODLEVEL [2:0] Fuse bits).

- 2. When the bandgap reference is connected to the Analog Comparator (by setting the ACBG bit in ACSR).

- 3. When the ADC is enabled.

Thus, when the BOD is not enabled, after setting the ACBG bit or enabling the ADC, the user must always allow the reference to start up before the output from the Analog Comparator or ADC is used. To reduce power consumption in Power-down mode, the user can avoid the three conditions above to ensure that the reference is turned off before entering Power-down mode.

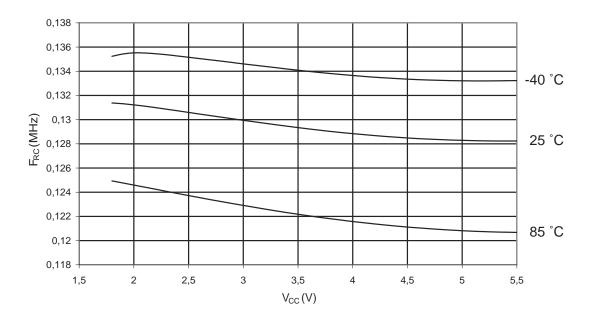

### 8.3 Watchdog Timer

The Watchdog Timer is clocked from an on-chip oscillator, which runs at 128 kHz. By controlling the Watchdog Timer prescaler, the Watchdog Reset interval can be adjusted as shown in Table 8-3 on page 49. The WDR – Watchdog Reset – instruction resets the Watchdog Timer. The Watchdog Timer is also reset when it is disabled and when a device reset occurs. Ten different clock cycle periods can be selected to determine the reset period. If the reset period expires without another Watchdog Reset, the ATtiny261/461/861 resets and executes from the Reset Vector. For timing details on the Watchdog Reset, refer to Table 8-3 on page 49.

# 44 ATtiny261/461/861

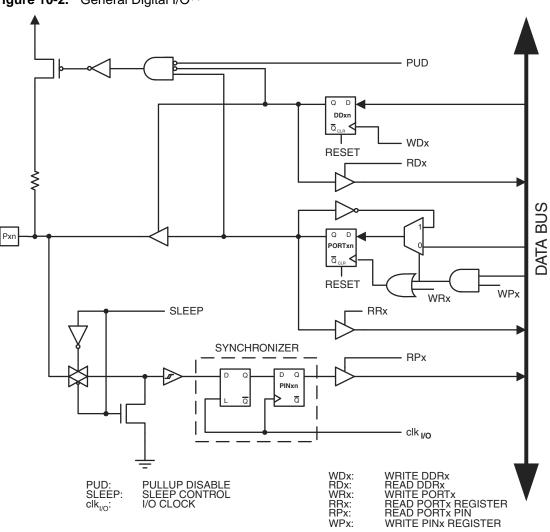

## 10.1 Ports as General Digital I/O

The ports are bi-directional I/O ports with optional internal pull-ups. Figure 10-2 shows a functional description of one I/O-port pin, here generically called Pxn.

Figure 10-2. General Digital I/O<sup>(1)</sup>

#### 10.1.1 Configuring the Pin

Each port pin consists of three register bits: DDxn, PORTxn, and PINxn. As shown in "Register Description" on page 69, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the PORTx I/O address, and the PINxn bits at the PINx I/O address.

The DDxn bit in the DDRx Register selects the direction of this pin. If DDxn is written logic one, Pxn is configured as an output pin. If DDxn is written logic zero, Pxn is configured as an input pin.

If PORTxn is written logic one when the pin is configured as an input pin, the pull-up resistor is activated. To switch the pull-up resistor off, PORTxn has to be written logic zero or the pin has to

# 56 ATtiny261/461/861

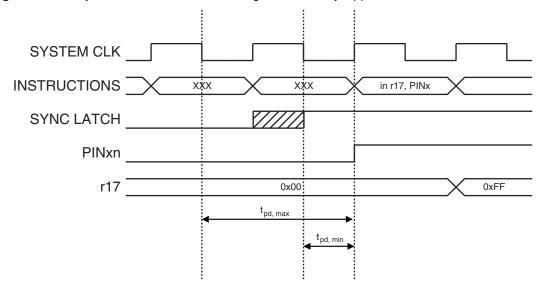

Figure 10-3. Synchronization when Reading an Externally Applied Pin value

Consider the clock period starting shortly after the first falling edge of the system clock. The latch is closed when the clock is low, and goes transparent when the clock is high, as indicated by the shaded region of the "SYNC LATCH" signal. The signal value is latched when the system clock goes low. It is clocked into the PINxn Register at the succeeding positive clock edge. As indicated by the two arrows tpd,max and tpd,min, a single signal transition on the pin will be delayed between ½ and 1½ system clock period depending upon the time of assertion.

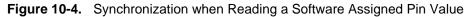

When reading back a software assigned pin value, a nop instruction must be inserted as indicated in Figure 10-4. The out instruction sets the "SYNC LATCH" signal at the positive edge of the clock. In this case, the delay tpd through the synchronizer is one system clock period.

### • Port A, Bit 5 – ADC4/AIN2/PCINT5

- ADC4: Analog to Digital Converter, Channel 4.

- AIN2: Analog Comparator Input. Configure the port pin as input with the internal pull-up switched off to avoid the digital port function from interfering with the function of the Analog Comparator.

- PCINT5: Pin Change Interrupt source 5.

#### • Port A, Bit 4 – ADC3/ICP0/PCINT4

- ADC3: Analog to Digital Converter, Channel 3.

- ICP0: Timer/Counter0 Input Capture Pin.

- PCINT4: Pin Change Interrupt source 4.

#### • Port A, Bit 3 – AREF/PCINT3

- AREF: External analog reference for ADC. Pullup and output driver are disabled on PA3 when the pin is used as an external reference or internal voltage reference with external capacitor at the AREF pin.

- PCINT3: Pin Change Interrupt source 3.

#### • Port A, Bit 2 – ADC2/INT1/USCK/SCL/PCINT2

- ADC2: Analog to Digital Converter, Channel 2.

- INT1: The PA2 pin can serve as an External Interrupt source 1.

- USCK: Three-wire mode Universal Serial Interface Clock.

- SCL: Two-wire mode Serial Clock for USI Two-wire mode.

- PCINT2: Pin Change Interrupt source 2.

#### • Port A, Bit 1 – ADC1/DO/PCINT1

- ADC1: Analog to Digital Converter, Channel 1.

- DO: Three-wire mode Universal Serial Interface Data output. Three-wire mode Data output overrides PORTA1 value and it is driven to the port when data direction bit DDA1 is set. PORTA1 still enables the pull-up, if the direction is input and PORTA1 is set.

- PCINT1: Pin Change Interrupt source 1.

#### Port A, Bit 0 – ADC0/DI/SDA/PCINT0

- ADC0: Analog to Digital Converter, Channel 0.

- DI: Data Input in USI Three-wire mode. USI Three-wire mode does not override normal port functions, so pin must be configure as an input for DI function.

- SDA: Two-wire mode Serial Interface Data.

- PCINT0: Pin Change Interrupt source 0.

counter value and so on. The definitions in Table 12-1 are used extensively throughout the document.

| Table 12-1. | Definitions |

|-------------|-------------|

|-------------|-------------|

| Constant | Description                                                                                                                                                                                                                                             |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BOTTOM   | The counter reaches BOTTOM when it becomes 0x00                                                                                                                                                                                                         |

| MAX      | The counter reaches its MAXimum when it becomes 0xFF (decimal 255)                                                                                                                                                                                      |

| ТОР      | The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR0A Register. The assignment depends on the mode of operation |

### 12.3 Clock Sources

The Timer/Counter is clocked internally, either from CK or PCK. See bits CSxx in Table 12-17 on page 116 and bit PCKE in "PLLCSR – PLL Control and Status Register" on page 120.

#### 12.3.1 Prescaler

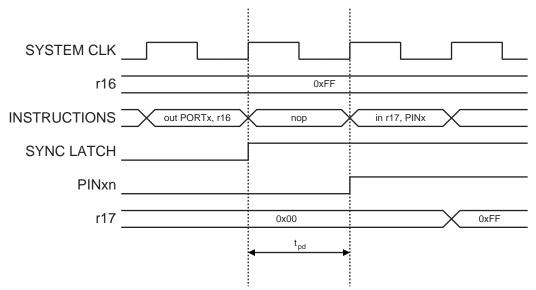

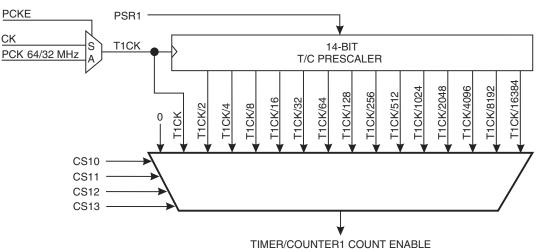

Figure 12-3 shows the Timer/Counter1 prescaler that supports two clocking modes, a synchronous clocking mode and an asynchronous clocking mode. The synchronous clocking mode uses the system clock (CK) as a clock timebase and asynchronous mode uses the fast peripheral clock (PCK) as a clock time base. The PCKE bit from the PLLCSR register enables the asynchronous mode when it is set ('1').

In the asynchronous clocking mode the clock selections are from PCK to PCK/16384 and stop, and in the synchronous clocking mode the clock selections are from CK to CK/16384 and stop. The clock options are illustrated in Figure 12-3 and desribed in "TCCR1B – Timer/Counter1 Control Register B" on page 115.

The frequency of the fast peripheral clock is 64 MHz or 32 MHz in Low Speed mode (the LSM bit in PLLCSR register is set to one). The Low Speed Mode is recommended to use when the supply voltage below 2.7 volts are used.

actual value from the port register will be visible on the port pin. The configurations of the Output Compare Pins are described in Table 12-4.

| COM1x1 | COM1x0 | OC1x Pin     | OC1x Pin     |  |

|--------|--------|--------------|--------------|--|

| 0      | 0      | Disconnected | Disconnected |  |

| 0      | 1      | OC1x         | OC1x         |  |

| 1      | 0      | Disconnected | OC1x         |  |

| 1      | 1      | Disconnected | OC1x         |  |

Table 12-4.

Output Compare pin configurations in Phase and Frequency Correct PWM Mode

#### 12.8.4 PWM6 Mode

The PWM6 Mode (PWM1A = 1, WGM11:10 = 1X) provide PWM waveform generation option e.g. for controlling Brushless DC (BLDC) motors. In the PWM6 Mode the OCR1A Register controls all six Output Compare waveforms as the same Waveform Output (OCW1A) from the Waform Generator is used for generating all waveforms. The PWM6 Mode also provides an Output Compare Override Enable Register (OC1OE) that can be used with an instant response for disabling or enabling the Output Compare pins. If the Output Compare Override Enable bit is cleared, the actual value from the port register will be visible on the port pin.

The PWM6 Mode provides two counter operation modes, a single-slope operation and a dualslope operation. If the single-slope operation is selected (the WGM10 bit is set to 0), the counter counts from BOTTOM to TOP (defined as OCR1C) then restart from BOTTOM like in Fast PWM Mode. The PWM waveform is generated by setting (or clearing) the Waveforn Output (OCW1A) at the Compare Match between OCR1A and TCNT1, and clearing (or setting) the Waveform Output at the timer clock cycle the counter is cleared (changes from TOP to BOTTOM). The Timer/Counter Overflow Flag (TOV1) is set each time the counter reaches the TOP and, if the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

Whereas, if the dual-slope operation is selected (the WGM10 bit is set to 1), the counter counts repeatedly from BOTTOM to TOP (defined as OCR1C) and then from TOP to BOTTOM like in Phase and Frequency Correct PWM Mode. The PWM waveform is generated by setting (or clearing) the Waveforn Output (OCW1A) at the Compare Match between OCR1A and TCNT1 when the counter increments, and clearing (or setting) the Waveform Output at the he Compare Match between OCR1A and TCNT1 when the counter decrements. The Timer/Counter Overflow Flag (TOV1) is set each time the counter reaches the BOTTOM and, if the interrupt is enabled, the interrupt handler routine can be used for updating the compare value.

The timing diagram for the PWM6 Mode in single-slope operation when the COM1A1:0 bits are set to "10" is shown in Figure 12-14. The counter is incremented until the counter value matches the TOP value. The counter is then cleared at the following timer clock cycle. The TCNT1 value is in the timing diagram shown as a histogram for illustrating the single-slope operation. The timing diagram includes Output Compare pins OC1A and OC1A, and the corresponding Output Compare Override Enable bits (OC1OE1:OC1OE0).

# ATtiny261/461/861

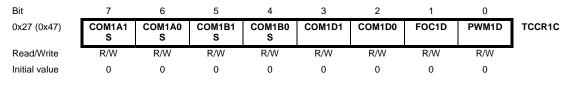

### 12.12.3 TCCR1C – Timer/Counter1 Control Register C

• Bits 7,6 – COM1A1S, COM1A0S: Comparator A Output Mode, Shadow Bits 1 and 0 These are shadow bits of COM1A1 and COM1A0 in TCCR1A. Writing to bits COM1A1S and COM1A0S will also change bits COM1A1 and COM1A0 in TCCR1A. Similary, changes written to bits COM1A1 and COM1A0 in TCCR1A will show here.

See "TCCR1A – Timer/Counter1 Control Register A" on page 112 for information on bit usage.

#### • Bits 5,4 – COM1B1S, COM1B0S: Comparator B Output Mode, Shadow Bits 1 and 0

These are shadow bits of COM1B1 and COM1B0 in TCCR1A. Writing to bits COM1B1S and COM1B0S will also change bits COM1B1 and COM1B0 in TCCR1A. Similary, changes written to bits COM1B1 and COM1B0 in TCCR1A will show here.

See "TCCR1A – Timer/Counter1 Control Register A" on page 112 for information on bit usage.

#### • Bits 3,2 - COM1D1, COM1D0: Comparator D Output Mode, Bits 1 and 0

These bits control the behaviour of the Waveform Output (OCW1D) and the connection of the Output Compare pin (OC1D). If one or both of the COM1D1:0 bits are set, the OC1D output overrides the normal port functionality of the I/O pin it is connected to. The complementary OC1D output is connected only in PWM modes when the COM1D1:0 bits are set to "01". Note that the Data Direction Register (DDR) bit corresponding to the OC1D pin must be set in order to enable the output driver.

The function of the COM1D1:0 bits depends on the PWM1D and WGM11:10 bit settings. Table 12-18 shows the COM1D1:0 bit functionality when the PWM1D bit is set to a Normal Mode (non-PWM).

| COM1D1:0 | OCW1D Behaviour          | OC1D Pin     | OC1D Pin     |

|----------|--------------------------|--------------|--------------|

| 00       | Normal port operation.   | Disconnected | Disconnected |

| 01       | Toggle on Compare Match. | Connected    | Disconnected |

| 10       | Clear on Compare Match.  | Connected    | Disconnected |

| 11       | Set on Compare Match.    | Connected    | Disconnected |

Table 12-18. Compare Output Mode, Normal Mode (non-PWM)

Table 12-19 shows the COM1D1:0 bit functionality when the PWM1D and WGM11:10 bits are set to Fast PWM Mode.

| COM1D1:0 | OCW1D Behaviour                                 | OC1D Pin     | OC1D Pin     |

|----------|-------------------------------------------------|--------------|--------------|

| 00       | Normal port operation.                          | Disconnected | Disconnected |

| 01       | Cleared on Compare Match. Set when TCNT1=0x000. | Connected    | Connected    |

| 10       | Cleared on Compare Match. Set when TCNT1=0x000. | Connected    | Disconnected |

| 11       | Set on Compare Match. Cleared when TCNT1=0x000. | Connected    | Disconnected |

Table 12-19. Compare Output Mode, Fast PWM Mode

### 13.4 Alternative USI Usage

The flexible design of the USI allows it to be used for other tasks when serial communication is not needed. Below are some examples.

#### 13.4.1 Half-Duplex Asynchronous Data Transfer

Using the USI Data Register in three-wire mode it is possible to implement a more compact and higher performance UART than by software, only.

#### 13.4.2 4-Bit Counter

The 4-bit counter can be used as a stand-alone counter with overflow interrupt. Note that if the counter is clocked externally, both clock edges will increment the counter value.

#### 13.4.3 12-Bit Timer/Counter

Combining the 4-bit USI counter with one of the 8-bit timer/counters creates a 12-bit counter.

#### 13.4.4 Edge Triggered External Interrupt

By setting the counter to maximum value (F) it can function as an additional external interrupt. The Overflow Flag and Interrupt Enable bit are then used for the external interrupt. This feature is selected by the USICS1 bit.

#### 13.4.5 Software Interrupt

The counter overflow interrupt can be used as a software interrupt triggered by a clock strobe.

### 13.5 Register Descriptions

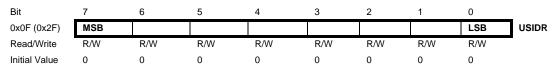

### 13.5.1 USIDR – USI Data Register

The USI Data Register can be accessed directly.

Depending on the USICS1:0 bits of the USI Control Register a (left) shift operation may be performed. The shift operation can be synchronised to an external clock edge, to a Timer/Counter0 Compare Match, or directly to software via the USICLK bit. If a serial clock occurs at the same cycle the register is written, the register will contain the value written and no shift is performed.

Note that even when no wire mode is selected (USIWM1:0 = 0) both the external data input (DI/SDA) and the external clock input (USCK/SCL) can still be used by the USI Data Register.

The output pin (DO or SDA, depending on the wire mode) is connected via the output latch to the most significant bit (bit 7) of the USI Data Register. The output latch ensures that data input is sampled and data output is changed on opposite clock edges. The latch is open (transparent) during the first half of a serial clock cycle when an external clock source is selected (USICS1 = 1) and constantly open when an internal clock source is used (USICS1 = 0). The output will be changed immediately when a new MSB is written as long as the latch is open.

Note that the Data Direction Register bit corresponding to the output pin must be set to one in order to enable data output from the USI Data Register.

| USIWM1 | USIWM0 | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | 0      | Two-wire mode. Uses SDA (DI) and SCL (USCK) pins <sup>(1)</sup> .<br>The <i>Serial Data</i> (SDA) and the <i>Serial Clock</i> (SCL) pins are bi-directional and<br>use open-collector output drives. The output drivers are enabled by setting the<br>corresponding bit for SDA and SCL in the DDRA register.<br>When the output driver is enabled for the SDA pin, the output driver will force<br>the line SDA low if the output of the USI Data Register or the corresponding<br>bit in the PORTA register is zero. Otherwise, the SDA line will not be driven (i.e.,<br>it is released). When the SCL pin output driver is enabled the SCL line will be<br>forced low if the corresponding bit in the PORTA register is zero, or by the start<br>detector. Otherwise the SCL line will not be driven.<br>The SCL line is held low when a start detector detects a start condition and the<br>output is enabled. Clearing the Start Condition Flag (USISIF) releases the line.<br>The SDA and SCL pin inputs is not affected by enabling this mode. Pull-ups on<br>the SDA and SCL port pin are disabled in Two-wire mode. |

| 1      | 1      | Two-wire mode. Uses SDA and SCL pins.<br>Same operation as in two-wire mode above, except that the SCL line is also<br>held low when a counter overflow occurs, and until the Counter Overflow Flag<br>(USIOIF) is cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 13-1.

Relationship between USIWM1:0 and USI Operation (Continued)

Note: 1. The DI and USCK pins are renamed to *Serial Data* (SDA) and *Serial Clock* (SCL) respectively to avoid confusion between the modes of operation.

#### • Bits 3:2 – USICS1:0: Clock Source Select

These bits set the clock source for the USI Data Registerr and counter. The data output latch ensures that the output is changed at the opposite edge of the sampling of the data input (DI/SDA) when using external clock source (USCK/SCL). When software strobe or Timer/Counter0 Compare Match clock option is selected, the output latch is transparent and therefore the output is changed immediately. Clearing the USICS1:0 bits enables software strobe option. When using this option, writing a one to the USICLK bit clocks both the USI Data Register and the counter. For external clock source (USICS1 = 1), the USICLK bit is no longer used as a strobe, but selects between external clocking and software clocking by the USITC strobe bit.

Table 13-2 on page 135 shows the relationship between the USICS1:0 and USICLK setting and clock source used for the USI Data Register and the 4-bit counter.

| USICS1 | USICS0 | USICLK | USI Data Register Clock<br>Source | 4-bit Counter Clock Source        |

|--------|--------|--------|-----------------------------------|-----------------------------------|

| 0      | 0      | 0      | No Clock                          | No Clock                          |

| 0      | 0      | 1      | Software clock strobe<br>(USICLK) | Software clock strobe<br>(USICLK) |

| 0      | 1      | Х      | Timer/Counter0 Compare<br>Match   | Timer/Counter0 Compare<br>Match   |

| 1      | 0      | 0      | External, positive edge           | External, both edges              |

Table 13-2. Relations between the USICS1:0 and USICLK Setting

| ADPS2 | ADPS1 | ADPS0 | Division Factor |

|-------|-------|-------|-----------------|

| 0     | 1     | 1     | 8               |

| 1     | 0     | 0     | 16              |

| 1     | 0     | 1     | 32              |

| 1     | 1     | 0     | 64              |

| 1     | 1     | 1     | 128             |

Table 15-5.

ADC Prescaler Selections (Continued)

### 15.13.3 ADCL and ADCH – The ADC Data Register

#### 15.13.3.1 ADLAR = 0

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    |      |

|---------------|------|------|------|------|------|------|------|------|------|

| 0x05 (0x25)   | -    | -    | -    | -    | -    | -    | ADC9 | ADC8 | ADCH |

| 0x04 (0x24)   | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADC1 | ADC0 | ADCL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | -    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |      |

|               | R    | R    | R    | R    | R    | R    | R    | R    |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

#### 15.13.3.2 ADLAR = 1

| Bit           | 15   | 14   | 13   | 12   | 11   | 10   | 9    | 8    | _    |

|---------------|------|------|------|------|------|------|------|------|------|

| 0x05 (0x25)   | ADC9 | ADC8 | ADC7 | ADC6 | ADC5 | ADC4 | ADC3 | ADC2 | ADCH |

| 0x04 (0x24)   | ADC1 | ADC0 | -    | -    | -    | -    | -    | -    | ADCL |

|               | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    | -    |

| Read/Write    | R    | R    | R    | R    | R    | R    | R    | R    |      |

|               | R    | R    | R    | R    | R    | R    | R    | R    |      |

| Initial Value | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

|               | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |      |

When an ADC conversion is complete, the result is found in these two registers.

When ADCL is read, the ADC Data Register is not updated until ADCH is read. Consequently, if the result is left adjusted and no more than 8-bit precision is required, it is sufficient to read ADCH. Otherwise, ADCL must be read first, then ADCH.

The ADLAR bit in ADMUX, and the MUXn bits in ADMUX affect the way the result is read from the registers. If ADLAR is set, the result is left adjusted. If ADLAR is cleared (default), the result is right adjusted.

#### • ADC9:0: ADC Conversion Result

These bits represent the result from the conversion, as detailed in "ADC Conversion Result" on page 153.

If the EEPROM is written in the middle of an SPM Page Load operation, all data loaded will be lost.

## 17.3 Performing a Page Write

To execute Page Write, set up the address in the Z-pointer, write "00000101" to SPMCSR and execute SPM within four clock cycles after writing SPMCSR. The data in R1 and R0 is ignored. The page address must be written to PCPAGE. Other bits in the Z-pointer must be written to zero during this operation.

Note: The CPU is halted during the Page Write operation.

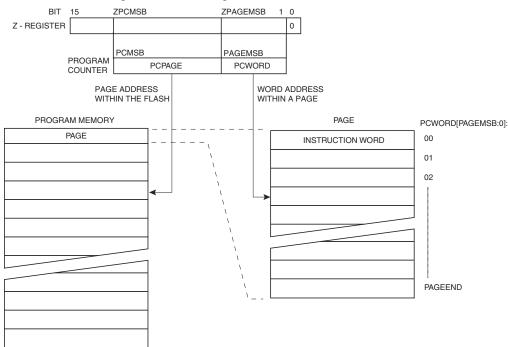

## 17.4 Addressing the Flash During Self-Programming

The Z-pointer is used to address the SPM commands.

| Bit      | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 8  |

|----------|-----|-----|-----|-----|-----|-----|----|----|

| ZH (R31) | Z15 | Z14 | Z13 | Z12 | Z11 | Z10 | Z9 | Z8 |

| ZL (R30) | Z7  | Z6  | Z5  | Z4  | Z3  | Z2  | Z1 | Z0 |

| -        | 7   | 6   | 5   | 4   | 3   | 2   | 1  | 0  |

Since the Flash is organized in pages (see Table 18-7 on page 173), the Program Counter can be treated as having two different sections. One section, consisting of the least significant bits, is addressing the words within a page, while the most significant bits are addressing the pages. This is shown in Figure 17-1. Note that the Page Erase and Page Write operations are addressed independently. Therefore it is of major importance that the software addresses the same page in both the Page Erase and Page Write operation.

The LPM instruction uses the Z-pointer to store the address. Since this instruction addresses the Flash byte-by-byte, also the LSB (bit Z0) of the Z-pointer is used.

#### Figure 17-1. Addressing the Flash During SPM

Note: The different variables used in Figure 17-1 are listed in Table 18-7 on page 173.

After **RESET** is set low, the Programming Enable instruction needs to be executed first before program/erase operations can be executed.

| Symbol | Pins | I/O            | Description     |

|--------|------|----------------|-----------------|

| MOSI   | PB0  | I              | Serial Data in  |

| MISO   | PB1  | 0              | Serial Data out |

| SCK    | PB2  | I Serial Clock |                 |

Table 18-9.

Pin Mapping Serial Programming

Note: In Table 18-9, above, the pin mapping for SPI programming is listed. Not all parts use the SPI pins dedicated for the internal SPI interface.

When programming the EEPROM, an auto-erase cycle is built into the self-timed programming operation (in the Serial mode ONLY) and there is no need to first execute the Chip Erase instruction. The Chip Erase operation turns the content of every memory location in both the Program and EEPROM arrays into 0xFF.

Depending on CKSEL Fuses, a valid clock must be present. The minimum low and high periods for the serial clock (SCK) input are defined as follows:

- Low:> 2 CPU clock cycles for  $f_{ck}$  < 12 MHz, 3 CPU clock cycles for  $f_{ck}$  >= 12 MHz

- High:> 2 CPU clock cycles for  $f_{ck}$  < 12 MHz, 3 CPU clock cycles for  $f_{ck}$  >= 12 MHz

#### 18.6.1 Serial Programming Algorithm

When writing serial data to the ATtiny261/461/861, data is clocked on the rising edge of SCK. When reading, data is clocked on the falling edge of SCK. See Figure 19-4 and Figure 19-5 for timing details.

To program and verify the ATtiny261/461/861 in the Serial Programming mode, the following sequence is recommended (see four byte instruction formats in Table 18-11):

1. Power-up sequence:

Apply power between V<sub>CC</sub> and GND while RESET and SCK are set to "0". In some systems, the programmer can not guarantee that SCK is held low during power-up. In this case, RESET must be given a positive pulse after SCK has been set to '0'. The duration of the pulse must be at least  $t_{RST}$  (the minimum pulse width on RESET pin, see Table 19-4 on page 190) plus two CPU clock cycles.

- 2. Wait for at least 20 ms and enable serial programming by sending the Programming Enable serial instruction to pin MOSI.

- 3. The serial programming instructions will not work if the communication is out of synchronization. When in sync. the second byte (0x53), will echo back when issuing the third byte of the Programming Enable instruction. Whether the echo is correct or not, all four bytes of the instruction must be transmitted. If the 0x53 did not echo back, give RESET a positive pulse and issue a new Programming Enable command.

- 4. The Flash is programmed one page at a time. The memory page is loaded one byte at a time by supplying the 5 LSB of the address and data together with the Load Program memory Page instruction. To ensure correct loading of the page, the data low byte must be loaded before data high byte is applied for a given address. The Program memory Page is stored by loading the Write Program memory Page instruction with the 6 MSB of the address. If polling (RDY/BSY) is not used, the user must wait at least t<sub>WD\_FLASH</sub> before issuing the next page. (See Table 18-10.) Accessing the serial programming

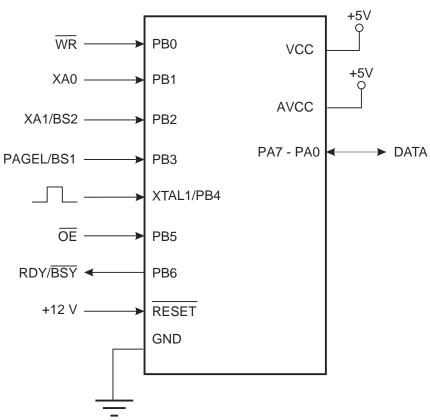

Figure 18-3. Parallel Programming.

Table 18-12. Pin Name Mapping

| Signal Name in<br>Programming Mode | Pin<br>Name | I/O | Function                                                                                                  |

|------------------------------------|-------------|-----|-----------------------------------------------------------------------------------------------------------|

| WR                                 | PB0         | I   | Write Pulse (Active low).                                                                                 |

| XA0                                | PB1         | I   | XTAL Action Bit 0                                                                                         |

| XA1/BS2                            | PB2         | I   | XTAL Action Bit 1. Byte Select 2 ("0" selects low byte, "1" selects 2'nd high byte).                      |

| PAGEL/BS1                          | PB3         | I   | Byte Select 1 ("0" selects low byte, "1" selects high byte).<br>Program Memory and EEPROM Data Page Load. |

| OE                                 | PB5         | I   | Output Enable (Active low).                                                                               |

| RDY/BSY                            | PB6         | 0   | 0: Device is busy programming, 1: Device is ready for new command.                                        |

| DATA I/O                           | PA7-PA0     | I/O | Bi-directional Data bus (Output when OE is low).                                                          |

| Symbol            | Parameter                  | Min | Тур | Max | Units |

|-------------------|----------------------------|-----|-----|-----|-------|

| t <sub>BVDV</sub> | BS1 Valid to DATA valid    | 0   |     | 250 | ns    |

| t <sub>OLDV</sub> | OE Low to DATA Valid       |     |     | 250 | ns    |

| t <sub>OHDZ</sub> | OE High to DATA Tri-stated |     |     | 250 | ns    |

**Table 19-9.** Parallel Programming Characteristics,  $V_{CC} = 5V \pm 10\%$  (Continued)

Notes: 1. t<sub>WLRH</sub> is valid for the Write Flash, Write EEPROM, Write Fuse bits and Write Lock bits commands.

2.  $t_{WLRH_CE}$  is valid for the Chip Erase command.

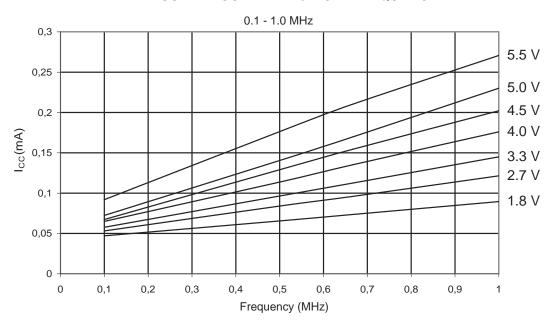

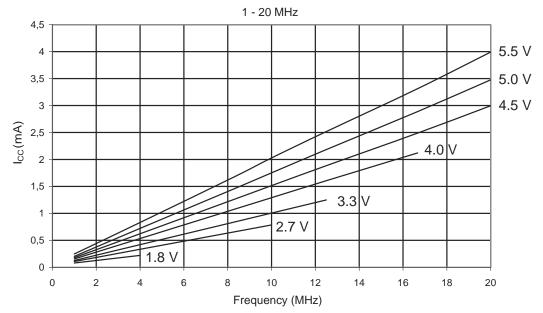

## 20.3 Idle Supply Current

Figure 20-6. Idle Supply Current vs. Low Frequency (0.1 - 1.0 MHz) IDLE SUPPLY CURRENT vs. LOW FREQUENCY

Figure 20-36. Bandgap Voltage vs. Supply Voltage (V<sub>CC</sub>).

## 20.9 Internal Oscillator Speed

# 216 ATtiny261/461/861