Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 128KB (64K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega128a3u-an |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

addressing. The most significant bits in the address (E2PAGE) give the page number and the least significant address bits (E2BYTE) give the byte in the page.

| Devices       | EEPROM | Page Size | E2BYTE    | E2PAGE     | No of Pages |  |

|---------------|--------|-----------|-----------|------------|-------------|--|

|               | Size   | bytes     |           |            |             |  |

| ATxmega64A3U  | 2K     | 32        | ADDR[4:0] | ADDR[10:5] | 64          |  |

| ATxmega128A3U | 2K     | 32        | ADDR[4:0] | ADDR[10:5] | 64          |  |

| ATxmega192A3U | 2K     | 32        | ADDR[4:0] | ADDR[10:5] | 64          |  |

| ATxmega256A3U | 4K     | 32        | ADDR[4:0] | ADDR[11:5] | 128         |  |

# 9. Event System

# 9.1 Features

- System for direct peripheral-to-peripheral communication and signaling

- Peripherals can directly send, receive, and react to peripheral events

- CPU and DMA controller independent operation

- 100% predictable signal timing

- Short and guaranteed response time

- Eight event channels for up to eight different and parallel signal routing configurations

- Events can be sent and/or used by most peripherals, clock system, and software

- Additional functions include

- Quadrature decoders

- Digital filtering of I/O pin state

- Works in active mode and idle sleep mode

# 9.2 Overview

The event system enables direct peripheral-to-peripheral communication and signaling. It allows a change in one peripheral's state to automatically trigger actions in other peripherals. It is designed to provide a predictable system for short and predictable response times between peripherals. It allows for autonomous peripheral control and interaction without the use of interrupts, CPU, or DMA controller resources, and is thus a powerful tool for reducing the complexity, size and execution time of application code. It also allows for synchronized timing of actions in several peripheral modules.

A change in a peripheral's state is referred to as an event, and usually corresponds to the peripheral's interrupt conditions. Events can be directly passed to other peripherals using a dedicated routing network called the event routing network. How events are routed and used by the peripherals is configured in software.

Figure 9-1 on page 21 shows a basic diagram of all connected peripherals. The event system can directly connect together analog and digital converters, analog comparators, I/O port pins, the real-time counter, timer/counters, IR communication module (IRCOM), and USB interface. It can also be used to trigger DMA transactions (DMA controller). Events can also be generated from software and the peripheral clock.

Atmel

# 12. System Control and Reset

# 12.1 Features

- Reset the microcontroller and set it to initial state when a reset source goes active

- Multiple reset sources that cover different situations

- Power-on reset

- External reset

- Watchdog reset

- Brownout reset

- PDI reset

- Software reset

- Asynchronous operation

- No running system clock in the device is required for reset

- Reset status register for reading the reset source from the application code

# 12.2 Overview

The reset system issues a microcontroller reset and sets the device to its initial state. This is for situations where operation should not start or continue, such as when the microcontroller operates below its power supply rating. If a reset source goes active, the device enters and is kept in reset until all reset sources have released their reset. The I/O pins are immediately tri-stated. The program counter is set to the reset vector location, and all I/O registers are set to their initial values. The SRAM content is kept. However, if the device accesses the SRAM when a reset occurs, the content of the accessed location can not be guaranteed.

After reset is released from all reset sources, the default oscillator is started and calibrated before the device starts running from the reset vector address. By default, this is the lowest program memory address, 0, but it is possible to move the reset vector to the lowest address in the boot section.

The reset functionality is asynchronous, and so no running system clock is required to reset the device. The software reset feature makes it possible to issue a controlled system reset from the user software.

The reset status register has individual status flags for each reset source. It is cleared at power-on reset, and shows which sources have issued a reset since the last power-on.

# 12.3 Reset Sequence

A reset request from any reset source will immediately reset the device and keep it in reset as long as the request is active. When all reset requests are released, the device will go through three stages before the device starts running again:

- Reset counter delay

- Oscillator startup

- Oscillator calibration

If another reset requests occurs during this process, the reset sequence will start over again.

# 12.4 Reset Sources

## 12.4.1 Power-on Reset

A power-on reset (POR) is generated by an on-chip detection circuit. The POR is activated when the  $V_{CC}$  rises and reaches the POR threshold voltage ( $V_{POT}$ ), and this will start the reset sequence.

The POR is also activated to power down the device properly when the  $V_{CC}$  falls and drops below the  $V_{POT}$  level. The  $V_{POT}$  level is higher for falling  $V_{CC}$  than for rising  $V_{CC}$ . Consult the datasheet for POR characteristics data.

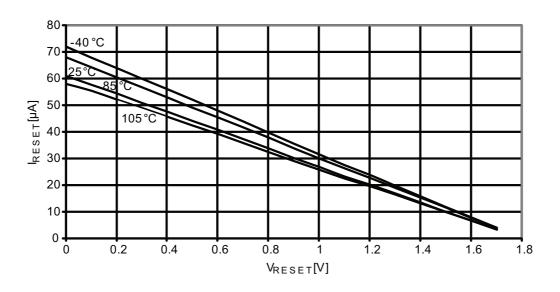

Both internal and external reference voltages can be used. An integrated temperature sensor is available for use with the ADC. The output from the DAC,  $AV_{CC}/10$  and the bandgap voltage can also be measured by the ADC.

The ADC has a compare function for accurate monitoring of user defined thresholds with minimum software intervention required.

### Figure 28-1. ADC overview.

Two inputs can be sampled simultaneously as both the ADC and the gain stage include sample and hold circuits, and the gain stage has 1x gain setting. Four inputs can be sampled within 1.5µs without any intervention by the application.

The ADC may be configured for 8- or 12-bit result, reducing the minimum conversion time (propagation delay) from 3.5µs for 12-bit to 2.5µs for 8-bit result.

ADC conversion results are provided left- or right adjusted with optional '1' or '0' padding. This eases calculation when the result is represented as a signed integer (signed 16-bit number).

PORTA and PORTB each has one ADC. Notation of these peripherals are ADCA and ADCB, respectively.

# 32. Pinout and Pin Functions

The device pinout is shown in "Pinout/Block Diagram" on page 5. In addition to general purpose I/O functionality, each pin can have several alternate functions. This will depend on which peripheral is enabled and connected to the actual pin. Only one of the pin functions can be used at time.

# 32.1 Alternate Pin Function Description

The tables below show the notation for all pin functions available and describe its function.

## 32.1.1 Operation/Power Supply

| V <sub>CC</sub>  | Digital supply voltage |

|------------------|------------------------|

| AV <sub>CC</sub> | Analog supply voltage  |

| GND              | Ground                 |

### 32.1.2 Port Interrupt functions

| SYNC  | Port pin with full synchronous and limited asynchronous interrupt function |

|-------|----------------------------------------------------------------------------|

| ASYNC | Port pin with full synchronous and full asynchronous interrupt function    |

### 32.1.3 Analog functions

| ACn              | Analog Comparator input pin n            |

|------------------|------------------------------------------|

| ACnOUT           | Analog Comparator n Output               |

| ADCn             | Analog to Digital Converter input pin n  |

| DACn             | Digital to Analog Converter output pin n |

| A <sub>REF</sub> | Analog Reference input pin               |

## 32.1.4 Timer/Counter and AWEX functions

| OCnxLS | Output Compare Channel x Low Side for Timer/Counter n  |

|--------|--------------------------------------------------------|

| OCnxHS | Output Compare Channel x High Side for Timer/Counter n |

# 32.1.5 Communication functions

| SCL    | Serial Clock for TWI                                               |

|--------|--------------------------------------------------------------------|

| SDA    | Serial Data for TWI                                                |

| SCLIN  | Serial Clock In for TWI when external driver interface is enabled  |

| SCLOUT | Serial Clock Out for TWI when external driver interface is enabled |

| SDAIN  | Serial Data In for TWI when external driver interface is enabled   |

| SDAOUT | Serial Data Out for TWI when external driver interface is enabled  |

| XCKn   | Transfer Clock for USART n                                         |

| RXDn   | Receiver Data for USART n                                          |

### Table 32-5. Port E - alternate functions.

| PORTE | PIN # | INTERRUPT  | TCE0 | TCE1 | USART<br>E0 | USART<br>E1 | SPIE | TWIE | TWIE<br>w/ext<br>driver | тоѕс  | CLOCKOUT           | EVENTOUT |

|-------|-------|------------|------|------|-------------|-------------|------|------|-------------------------|-------|--------------------|----------|

| PE0   | 36    | SYNC       | OC0A |      |             |             |      | SDA  | SDAIN                   |       |                    |          |

| PE1   | 37    | SYNC       | OC0B |      | XCK0        |             |      | SCL  | SCLIN                   |       |                    |          |

| PE2   | 38    | SYNC/ASYNC | OC0C |      | RXD0        |             |      |      | SDAOUT                  |       |                    |          |

| PE3   | 39    | SYNC       | OC0D |      | TXD0        |             |      |      | SCLOUT                  |       |                    |          |

| PE4   | 40    | SYNC       |      | OC1A |             |             | SS   |      |                         |       |                    |          |

| PE5   | 41    | SYNC       |      | OC1B |             | XCK1        | MOSI |      |                         |       |                    |          |

| PE6   | 42    | SYNC       |      |      |             | RXD1        | MISO |      |                         | TOSC2 |                    |          |

| PE7   | 43    | SYNC       |      |      |             | TXD1        | SCK  |      |                         | TOSC1 | clk <sub>PER</sub> | EVOUT    |

| GND   | 44    |            |      |      |             |             |      |      |                         |       |                    |          |

| vcc   | 45    |            |      |      |             |             |      |      |                         |       |                    |          |

Notes: 1. Pin mapping of all TC0 can optionally be moved to high nibble of port.

2. If TC0 is configured as TC2 all eight pins can be used for PWM output.

- 3. Pin mapping of all USART0 can optionally be moved to high nibble of port.

- 4. Pins MOSI and SCK for all SPI can optionally be swapped.

- 5. CLKOUT can optionally be moved between port C, D and E and be on pin 4 or 7.

- 6. EVOUT can optionally be moved between port C, D and E and be on pin 4 or 7.

### Table 32-6. Port F - alternate functions.

| PORTF | PIN# | INTERRUPT  | TCF0 | USARTF0 |

|-------|------|------------|------|---------|

| PF0   | 46   | SYNC       | OC0A |         |

| PF1   | 47   | SYNC       | OC0B | ХСКО    |

| PF2   | 48   | SYNC/ASYNC | 0000 | RXD0    |

| PF3   | 49   | SYNC       | OC0D | TXD0    |

| PF4   | 50   | SYNC       |      |         |

| PF5   | 51   | SYNC       |      |         |

| GND   | 52   |            |      |         |

| vcc   | 53   |            |      |         |

| PF6   | 54   | SYNC       |      |         |

| PF7   | 55   | SYNC       |      |         |

### Table 32-7. Port R - alternate functions.

| PORTR | PIN# | INTERRUPT | PDI       | XTAL  |

|-------|------|-----------|-----------|-------|

| PDI   | 56   |           | PDI_DATA  |       |

| RESET | 57   |           | PDI_CLOCK |       |

| PR0   | 58   | SYNC      |           | XTAL2 |

| PR1   | 59   | SYNC      |           | XTAL1 |

| Mnemonics | Operands | Description                     | Operation                       | Flags | #Clocks |

|-----------|----------|---------------------------------|---------------------------------|-------|---------|

| SEV       |          | Set Two's Complement Overflow   | V ← 1                           | V     | 1       |

| CLV       |          | Clear Two's Complement Overflow | $V \leftarrow 0$                | V     | 1       |

| SET       |          | Set T in SREG                   | T ← 1                           | Т     | 1       |

| CLT       |          | Clear T in SREG                 | $T \leftarrow 0$                | Т     | 1       |

| SEH       |          | Set Half Carry Flag in SREG     | H ← 1                           | н     | 1       |

| CLH       |          | Clear Half Carry Flag in SREG   | H ← 0                           | н     | 1       |

|           |          | MCU d                           | control instructions            |       |         |

| BREAK     |          | Break                           | (See specific descr. for BREAK) | None  | 1       |

| NOP       |          | No Operation                    |                                 | None  | 1       |

| SLEEP     |          | Sleep                           | (see specific descr. for Sleep) | None  | 1       |

| WDR       |          | Watchdog Reset                  | (see specific descr. for WDR)   | None  | 1       |

Notes: 1. Cycle times for Data memory accesses assume internal memory accesses, and are not valid for accesses via the external RAM interface.

2. One extra cycle must be added when accessing Internal SRAM.

# **Atmel**

Table 36-5. Current consumption for modules and peripherals.

| Symbol          | Parameter                 | Condition <sup>(1)</sup>                |                                    | Min. | Тур. | Max. | Units |

|-----------------|---------------------------|-----------------------------------------|------------------------------------|------|------|------|-------|

|                 | ULP oscillator            |                                         |                                    |      | 1.0  |      | μA    |

|                 | 32.768kHz int. oscillator |                                         |                                    |      | 26   |      | μA    |

|                 | 2MHz int. oscillator      |                                         |                                    |      | 85   |      |       |

|                 |                           | DFLL enabled with                       | n 32.768kHz int. osc. as reference |      | 115  |      | μA    |

|                 | 32MHz int. oscillator     |                                         |                                    |      | 270  |      | μA    |

|                 |                           | DFLL enabled with                       | n 32.768kHz int. osc. as reference |      | 460  |      | μΑ    |

|                 | PLL                       | 20x multiplication<br>32MHz int. osc. D |                                    |      | 220  |      | μA    |

|                 | Watchdog Timer            |                                         |                                    |      | 1    |      | μA    |

|                 | BOD                       | Continuous mode                         | Continuous mode                    |      | 138  |      |       |

|                 | вор                       | Sampled mode, includes ULP oscillator   |                                    |      | 1.2  |      | μA    |

|                 | Internal 1.0V reference   |                                         |                                    |      | 100  |      | μA    |

| I <sub>CC</sub> | Temperature sensor        |                                         |                                    |      | 95   |      | μA    |

|                 |                           |                                         |                                    |      | 3.0  |      |       |

|                 | ADC                       | 250ksps                                 | CURRLIMIT = LOW                    |      | 2.6  |      | mA    |

|                 | ADC                       | V <sub>REF</sub> = Ext ref              | CURRLIMIT = MEDIUM                 |      | 2.1  |      |       |

|                 |                           |                                         | CURRLIMIT = HIGH                   |      | 1.6  |      |       |

|                 | DAC                       | 250ksps                                 | Normal mode                        |      | 1.9  |      | mA    |

|                 | DAC                       | V <sub>REF</sub> = Ext ref<br>No load   | Low Power mode                     |      | 1.1  |      | mA    |

|                 | 10                        | High Speed Mode                         |                                    |      | 330  |      |       |

|                 | AC                        | Low Power Mode                          |                                    |      | 130  |      | μA    |

|                 | DMA                       | 615KBps between                         | I/O registers and SRAM             |      | 115  |      | μA    |

|                 | Timer/Counter             |                                         |                                    |      | 16   |      | μA    |

|                 | USART                     | Rx and Tx enable                        | d, 9600 BAUD                       |      | 2.5  |      | μA    |

|                 | Flash memory and EEPRO    | OM programming                          |                                    |      | 4    |      | mA    |

Note:

All parameters measured as the difference in current consumption between module enabled and disabled. All data at V<sub>CC</sub> = 3.0V, Clk<sub>SYS</sub> = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

| Symbol             | Parameter               | Condition                 |                                    | Min. | Тур. | Max. | Units |

|--------------------|-------------------------|---------------------------|------------------------------------|------|------|------|-------|

|                    |                         | mode = HS                 | V <sub>CC</sub> = 3.0V,<br>T= 85°C |      | 60   | 90   |       |

| t <sub>delay</sub> | Propagation delay       |                           | V <sub>CC</sub> = 1.6V - 3.6V      |      | 30   |      | ns    |

|                    |                         | mode = LP                 | v <sub>CC</sub> - 1.0v - 3.0v      |      | 160  |      |       |

|                    | 64-Level Voltage Scaler | Integral non-linearity (I | NL)                                |      | 0.3  | 0.5  | lsb   |

# 36.1.9 Bandgap and Internal 1.0V Reference Characteristics

### Table 36-16. Bandgap and Internal 1.0V reference characteristics.

| Symbol | Parameter                              | Condition                            | Min. | Тур.                     | Max. | Units |

|--------|----------------------------------------|--------------------------------------|------|--------------------------|------|-------|

|        | Startup time                           | As reference for ADC or DAC          |      | Clk <sub>PER</sub> + 2.5 | ōμs  |       |

|        | Startup time                           | As input voltage to ADC and AC       | 1.5  |                          |      | μs    |

|        | Bandgap voltage                        |                                      |      | 1.1                      |      | V     |

| INT1V  | Internal 1.00V reference               | T= 85°C, after calibration           | 0.99 | 1                        | 1.01 | V     |

|        | Variation over voltage and temperature | Relative to T= 85°C, $V_{CC}$ = 3.0V |      | ±1.0                     |      | %     |

# 36.1.10 Brownout Detection Characteristics

## Table 36-17. Brownout detection characteristics.

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|

|                   | BOD level 0 falling V <sub>CC</sub> |                 | 1.60 | 1.62 | 1.72 |       |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.8  |      | -     |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      | -     |

| V                 | BOD level 3 falling $V_{CC}$        |                 |      | 2.2  |      | v     |

| V <sub>BOT</sub>  | BOD level 4 falling $V_{CC}$        |                 |      | 2.4  |      | V     |

|                   | BOD level 5 falling $V_{CC}$        |                 |      | 2.6  |      | _     |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      | _     |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      | _     |

| +                 | Detection time                      | Continuous mode |      | 0.4  |      |       |

| t <sub>BOD</sub>  |                                     | Sampled mode    |      | 1000 |      | μs    |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.6  |      | %     |

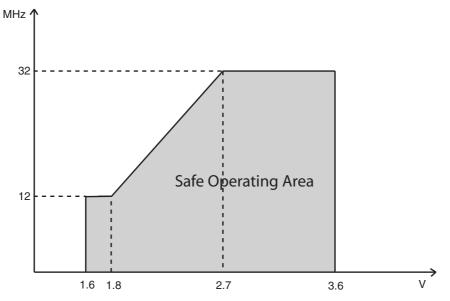

The maximum CPU clock frequency depends on V<sub>CC</sub>. As shown in Figure 36-1 the Frequency vs. V<sub>CC</sub> curve is linear between 1.8V < V<sub>CC</sub> < 2.7V.

| Symbol             | Parameter               | Condition              |                                 | Min. | Тур. | Max. | Units |

|--------------------|-------------------------|------------------------|---------------------------------|------|------|------|-------|

|                    |                         | mode = HS              | V <sub>CC</sub> = 3.0V, T= 85°C |      | 90   | 100  |       |

| t <sub>delay</sub> | Propagation delay       | mode – HS              | VCC = 1.6V - 3.6V               |      | 95   |      | ns    |

|                    |                         | mode = LP              | VCC - 1.0V - 3.0V               |      | 200  | 500  |       |

|                    | 64-Level Voltage Scaler | Integral non-linearity | (INL)                           |      | 0.5  | 1.0  | lsb   |

# 36.2.9 Bandgap and Internal 1.0V Reference Characteristics

| Table 36-48. | Bandgap and Internal 1.0V reference characteristics. |

|--------------|------------------------------------------------------|

|--------------|------------------------------------------------------|

| Symbol | Parameter                              | Condition                            | Min. | Тур.                    | Max. | Units |

|--------|----------------------------------------|--------------------------------------|------|-------------------------|------|-------|

|        | Startup time                           | As reference for ADC or DAC          | 1 (  | Clk <sub>PER</sub> + 2. | ōμs  |       |

|        | Startup time                           | As input voltage to ADC and AC       | 1.5  |                         |      | μs    |

|        | Bandgap voltage                        |                                      |      | 1.1                     |      | V     |

| INT1V  | Internal 1.00V reference               | T= 85°C, after calibration           | 0.99 | 1                       | 1.01 |       |

|        | Variation over voltage and temperature | Relative to T= 85°C, $V_{CC}$ = 3.0V |      | ±1.0                    |      | %     |

# 36.2.10 Brownout Detection Characteristics

## Table 36-49. Brownout detection characteristics.

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|

|                   | BOD level 0 falling V <sub>CC</sub> |                 | 1.60 | 1.62 | 1.72 |       |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.8  |      | -     |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      | V     |

| V                 | BOD level 3 falling V <sub>CC</sub> |                 |      | 2.2  |      |       |

| V <sub>BOT</sub>  | BOD level 4 falling V <sub>CC</sub> |                 |      | 2.4  |      |       |

|                   | BOD level 5 falling $V_{CC}$        |                 |      | 2.6  |      |       |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      | _     |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      | _     |

| +                 | Detection time                      | Continuous mode |      | 0.4  |      | ue    |

| t <sub>BOD</sub>  |                                     | Sampled mode    |      | 1000 |      | μs    |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.6  |      | %     |

### 36.3.6 ADC characteristics

| Table 36-72. | Power supply, reference and input range. |

|--------------|------------------------------------------|

|--------------|------------------------------------------|

| Symbol              | Parameter                   | Condition                        | Min.                  | Тур. | Max.                   | Units |

|---------------------|-----------------------------|----------------------------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>    | Analog supply voltage       |                                  | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  | V     |

| V <sub>REF</sub>    | Reference voltage           |                                  | 1                     |      | AV <sub>CC</sub> - 0.6 | V     |

| R <sub>in</sub>     | Input resistance            | Switched                         |                       | 4.0  |                        | kΩ    |

| C <sub>sample</sub> | Input capacitance           | Switched                         |                       | 4.4  |                        | pF    |

| R <sub>AREF</sub>   | Reference input resistance  | (leakage only)                   |                       | >10  |                        | MΩ    |

| C <sub>AREF</sub>   | Reference input capacitance | Static load                      |                       | 7    |                        | pF    |

| V <sub>IN</sub>     | Input range                 |                                  | -0.1                  |      | AV <sub>CC</sub> +0.1  | V     |

|                     | Conversion range            | Differential mode, Vinp - Vinn   | -V <sub>REF</sub>     |      | V <sub>REF</sub>       | V     |

| V <sub>IN</sub>     | Conversion range            | Single ended unsigned mode, Vinp | -ΔV                   |      | $V_{REF} \Delta V$     | V     |

| ΔV                  | Fixed offset voltage        |                                  |                       | 190  |                        | LSB   |

# Table 36-73. Clock and timing.

| Symbol             | Parameter                 | Condition                                          | Min. | Тур. | Max. | Units                        |

|--------------------|---------------------------|----------------------------------------------------|------|------|------|------------------------------|

| Clk <sub>ADC</sub> | ADC Clock frequency       | Maximum is 1/4 of Peripheral clock<br>frequency    | 100  |      | 2000 | kHz                          |

|                    |                           | Measuring internal signals                         | 100  |      | 125  |                              |

|                    | Sample rate               | Current limitation (CURRLIMIT) off                 | 100  |      | 2000 |                              |

| 4                  |                           | CURRLIMIT = LOW                                    | 100  |      | 1500 | liene                        |

| f <sub>ADC</sub>   |                           | CURRLIMIT = MEDIUM                                 | 100  |      | 1000 | ksps                         |

|                    |                           | CURRLIMIT = HIGH                                   | 100  |      | 500  | -                            |

|                    | Sampling Time             | 1/2 Clk <sub>ADC</sub> cycle                       | 0.25 |      | 5    | μs                           |

|                    | Conversion time (latency) | (RES+2)/2+(GAIN !=0)<br>RES (Resolution) = 8 or 12 | 5    |      | 8    | Clk <sub>ADC</sub><br>cycles |

|                    | Start-up time             | ADC clock cycles                                   |      | 12   | 24   | Clk <sub>ADC</sub><br>cycles |

|                    | ADC settling time         | After changing reference or input mode             |      | 7    | 7    | Clk <sub>ADC</sub>           |

|                    |                           | After ADC flush                                    |      | 1    | 1    | cycles                       |

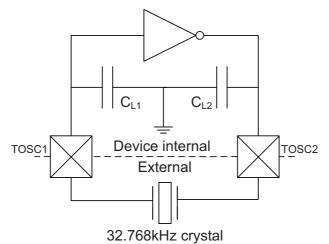

### 36.3.14.8 External 32.768kHz crystal oscillator and TOSC characteristics

### Table 36-94. External 32.768kHz crystal oscillator and TOSC characteristics.

| Symbol             | Parameter                       | Condition                                            | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------|------------------------------------------------------|------|------|------|-------|

| ESR/R1             | Recommended crystal equivalent  | Crystal load capacitance 6.5pF                       |      |      | 60   | kΩ    |

| ESR/RI             | orion registered (ESD)          | Crystal load capacitance 9.0pF                       |      |      | 35   | K22   |

| C <sub>TOSC1</sub> | Parasitic capacitance TOSC1 pin |                                                      |      | 4.2  |      | pF    |

| C <sub>TOSC2</sub> | Parasitic capacitance TOSC2 pin |                                                      |      | 4.3  |      | pF    |

|                    | Recommended safety factor       | capacitance load matched to<br>crystal specification | 3    |      |      |       |

Note: 1. See Figure 36-4 for definition.

### Figure 36-18. TOSC input capacitance.

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

# 36.4.3 Current consumption

| Symbol          | Parameter                                   | Condition                                                 |                        | Min. | Тур. | Max. | Units |

|-----------------|---------------------------------------------|-----------------------------------------------------------|------------------------|------|------|------|-------|

|                 | Active Power<br>consumption <sup>(1)</sup>  |                                                           | V <sub>CC</sub> = 1.8V |      | 60   |      | μΑ    |

|                 |                                             | 32kHz, Ext. Clk                                           | V <sub>CC</sub> = 3.0V |      | 140  |      |       |

|                 |                                             |                                                           | V <sub>CC</sub> = 1.8V |      | 280  |      |       |

|                 |                                             | 1MHz, Ext. Clk                                            | V <sub>CC</sub> = 3.0V |      | 600  |      |       |

|                 |                                             | 2MHz, Ext. Clk                                            | V <sub>CC</sub> = 1.8V |      | 510  | 500  |       |

|                 |                                             |                                                           | V - 2 0V               |      | 1.1  | 1.5  | mA    |

|                 |                                             | 32MHz, Ext. Clk                                           | V <sub>CC</sub> = 3.0V |      | 10.6 | 15   |       |

|                 | Idle Power<br>consumption <sup>(1)</sup>    | 32kHz, Ext. Clk                                           | V <sub>CC</sub> = 1.8V |      | 4.3  |      | μΑ    |

|                 |                                             |                                                           | V <sub>CC</sub> = 3.0V |      | 4.8  |      |       |

|                 |                                             |                                                           | V <sub>CC</sub> = 1.8V |      | 78   |      |       |

| I <sub>CC</sub> |                                             | 1MHz, Ext. Clk                                            | V <sub>CC</sub> = 3.0V |      | 150  |      |       |

|                 |                                             | 2MHz, Ext. Clk                                            | V <sub>CC</sub> = 1.8V |      | 150  | 350  |       |

|                 |                                             |                                                           |                        |      | 290  | 600  |       |

|                 |                                             | 32MHz, Ext. Clk                                           | V <sub>CC</sub> = 3.0V |      | 4.7  | 7.0  | mA    |

|                 | Power-down power consumption                | T = 25°C                                                  |                        |      | 0.1  | 1.0  |       |

|                 |                                             | T = 85°C                                                  | V <sub>CC</sub> = 3.0V |      | 1.8  | 5.0  | μΑ    |

|                 |                                             | T = 105°C                                                 | _                      |      | 6.5  | 17   |       |

|                 |                                             | WDT and Sampled BOD enabled,<br>T = $25^{\circ}$ C        |                        |      | 1.3  | 3.0  |       |

|                 |                                             | WDT and Sampled BOD enabled,<br>T = 85°C                  | V <sub>CC</sub> = 3.0V |      | 3.1  | 7.0  |       |

|                 |                                             | WDT and Sampled BOD enabled,<br>T = 105°C                 |                        |      | 7.3  | 20   |       |

|                 | Power-save power consumption <sup>(2)</sup> | RTC from ULP clock, WDT and sampled BOD enabled, T = 25°C | V <sub>CC</sub> = 1.8V |      | 1.2  |      |       |

|                 |                                             |                                                           | V <sub>CC</sub> = 3.0V |      | 1.3  |      | μΑ    |

|                 |                                             | RTC from 1.024kHz low power<br>32.768kHz TOSC, T = 25°C   | V <sub>CC</sub> = 1.8V |      | 0.6  | 2    |       |

|                 |                                             |                                                           | V <sub>CC</sub> = 3.0V |      | 0.7  | 2    |       |

|                 |                                             | RTC from low power 32.768kHz                              | V <sub>CC</sub> = 1.8V |      | 0.8  | 3    |       |

|                 |                                             | TOSC, T = 25°C                                            | V <sub>CC</sub> = 3.0V |      | 1.0  | 3    |       |

|                 | Reset power consumption                     | Current through RESET pin substracted                     | V <sub>CC</sub> = 3.0V |      | 250  |      | μΑ    |

Table 36-100. Current consumption for active mode and sleep modes.

Notes: 1. All Power Reduction Registers set.

2. Maximum limits are based on characterization, and not tested in production.

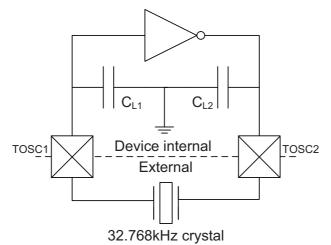

### 36.4.14.8 External 32.768kHz crystal oscillator and TOSC characteristics

### Table 36-126. External 32.768kHz crystal oscillator and TOSC characteristics.

| Symbol             | Parameter                       | Condition                                         | Min. | Тур. | Max. | Units |

|--------------------|---------------------------------|---------------------------------------------------|------|------|------|-------|

| ESR/R1             | Recommended crystal equivalent  | Crystal load capacitance 6.5pF                    |      |      | 60   | kΩ    |

|                    | series resistance (ESR)         | Crystal load capacitance 9.0pF                    |      |      | 35   |       |

| C <sub>TOSC1</sub> | Parasitic capacitance TOSC1 pin |                                                   |      | 4.2  |      | pF    |

| C <sub>TOSC2</sub> | Parasitic capacitance TOSC2 pin |                                                   |      | 4.3  |      | pF    |

|                    | Recommended safety factor       | capacitance load matched to crystal specification | 3    |      |      |       |

Note: 1. See Figure 36-4 for definition.

### Figure 36-25. TOSC input capacitance.

The parasitic capacitance between the TOSC pins is  $C_{L1} + C_{L2}$  in series as seen from the crystal when oscillating without external capacitors.

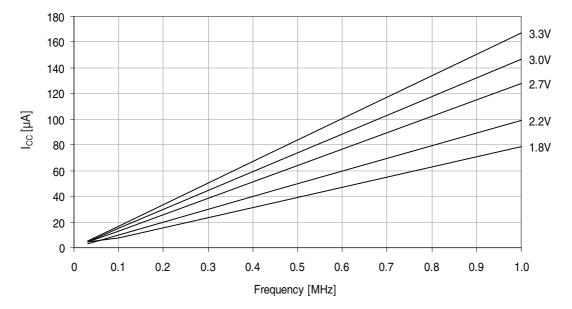

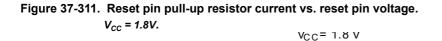

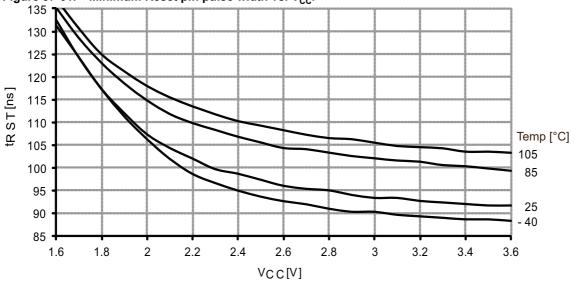

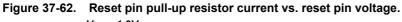

### 37.1.8 External Reset Characteristics

# **37.1.10 Oscillator Characteristics**

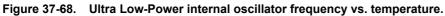

37.1.10.1 Ultra Low-Power internal oscillator

<sup>37.1.10.2 32.768</sup>kHz Internal Oscillator

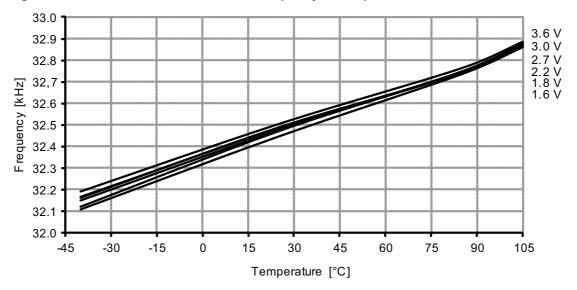

Figure 37-69. 32.768kHz internal oscillator frequency vs. temperature.

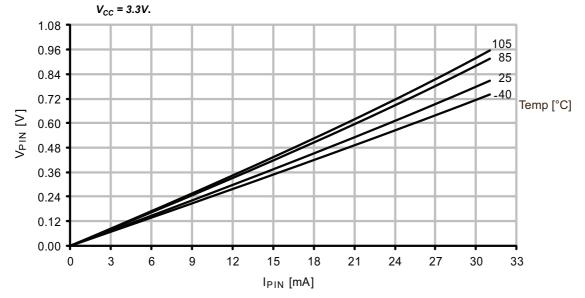

Figure 37-112. I/O pin output voltage vs. sink current.

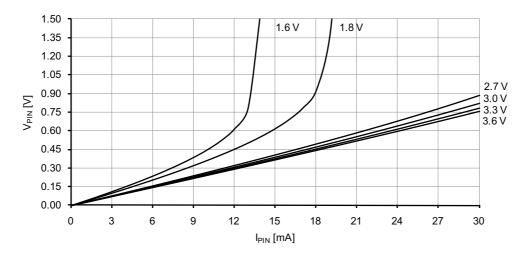

Figure 37-113. I/O pin output voltage vs. sink current.

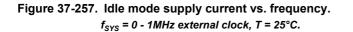

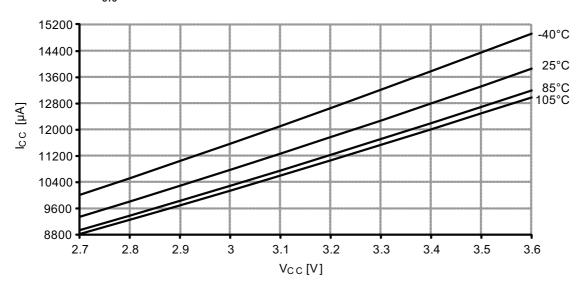

### 37.4.1.2 Idle mode supply current