Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 192KB (96K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-TQFP                                                                    |

| Supplier Device Package    | 64-TQFP (14x14)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega192a3u-an |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

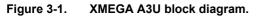

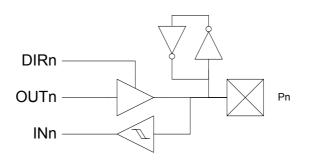

## 3.1 Block Diagram

**Atmel**

# 10. System Clock and Clock options

## 10.1 Features

- Fast start-up time

- Safe run-time clock switching

- Internal oscillators:

- 32MHz run-time calibrated and tuneable oscillator

- 2MHz run-time calibrated oscillator

- 32.768kHz calibrated oscillator

- 32kHz ultra low power (ULP) oscillator with 1kHz output

- External clock options

- 0.4MHz 16MHz crystal oscillator

- 32.768kHz crystal oscillator

- External clock

- PLL with 20MHz 128MHz output frequency

- Internal and external clock options and 1x to 31x multiplication

- Lock detector

- Clock prescalers with 1x to 2048x division

- Fast peripheral clocks running at two and four times the CPU clock

- Automatic run-time calibration of internal oscillators

- External oscillator and PLL lock failure detection with optional non-maskable interrupt

### 10.2 Overview

Atmel AVR XMEGA A3U devices have a flexible clock system supporting a large number of clock sources. It incorporates both accurate internal oscillators and external crystal oscillator and resonator support. A high-frequency phase locked loop (PLL) and clock prescalers can be used to generate a wide range of clock frequencies. A calibration feature (DFLL) is available, and can be used for automatic run-time calibration of the internal oscillators to remove frequency drift over voltage and temperature. An oscillator failure monitor can be enabled to issue a non-maskable interrupt and switch to the internal oscillator if the external oscillator or PLL fails.

When a reset occurs, all clock sources except the 32kHz ultra low power oscillator are disabled. After reset, the device will always start up running from the 2MHz internal oscillator. During normal operation, the system clock source and prescalers can be changed from software at any time.

Figure 10-1 on page 23 presents the principal clock system in the XMEGA A3U family of devices. Not all of the clocks need to be active at a given time. The clocks for the CPU and peripherals can be stopped using sleep modes and power reduction registers, as described in "Power Management and Sleep Modes" on page 25.

### 12.4.2 Brownout Detection

The on-chip brownout detection (BOD) circuit monitors the  $V_{CC}$  level during operation by comparing it to a fixed, programmable level that is selected by the BODLEVEL fuses. If disabled, BOD is forced on at the lowest level during chip erase and when the PDI is enabled.

### 12.4.3 External Reset

The external reset circuit is connected to the external  $\overrightarrow{\text{RESET}}$  pin. The external reset will trigger when the  $\overrightarrow{\text{RESET}}$  pin is driven below the  $\overrightarrow{\text{RESET}}$  pin threshold voltage,  $V_{RST}$ , for longer than the minimum pulse period,  $t_{EXT}$ . The reset will be held as long as the pin is kept low. The  $\overrightarrow{\text{RESET}}$  pin includes an internal pull-up resistor.

### 12.4.4 Watchdog Reset

The watchdog timer (WDT) is a system function for monitoring correct program operation. If the WDT is not reset from the software within a programmable timeout period, a watchdog reset will be given. The watchdog reset is active for one to two clock cycles of the 2MHz internal oscillator. For more details see "WDT – Watchdog Timer" on page 29.

### 12.4.5 Software Reset

The software reset makes it possible to issue a system reset from software by writing to the software reset bit in the reset control register. The reset will be issued within two CPU clock cycles after writing the bit. It is not possible to execute any instruction from when a software reset is requested until it is issued.

### 12.4.6 Program and Debug Interface Reset

The program and debug interface reset contains a separate reset source that is used to reset the device during external programming and debugging. This reset source is accessible only from external debuggers and programmers.

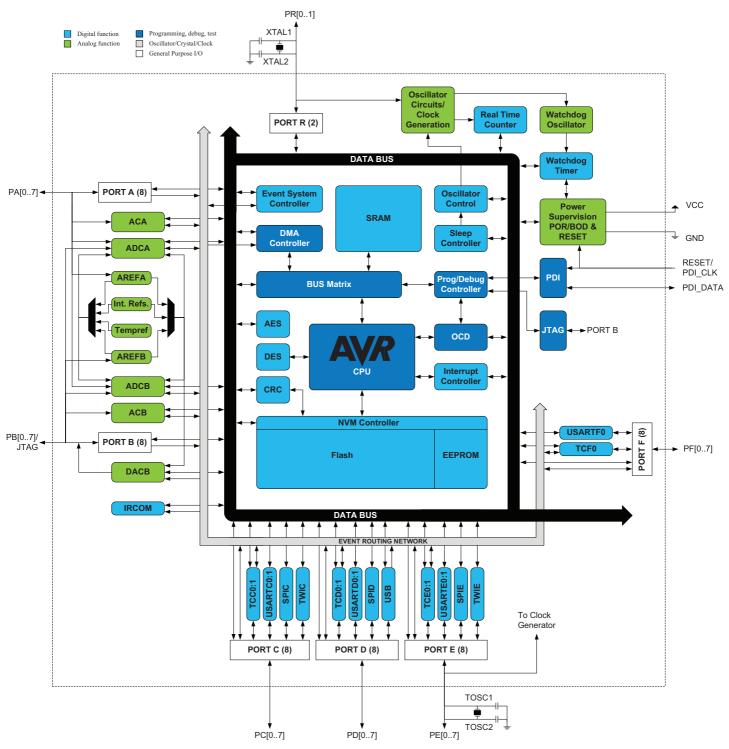

#### 15.3.4 Bus-keeper

The bus-keeper's weak output produces the same logical level as the last output level. It acts as a pull-up if the last level was '1', and pull-down if the last level was '0'.

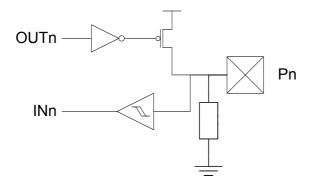

### Figure 15-4. I/O configuration - Totem-pole with bus-keeper.

#### 15.3.5 Others

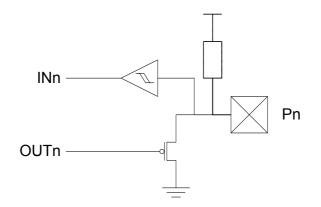

Figure 15-5. Output configuration - Wired-OR with optional pull-down.

Figure 15-6. I/O configuration - Wired-AND with optional pull-up.

# 24. USART

### 24.1 Features

- Seven identical USART peripherals

- Full-duplex operation

- Asynchronous or synchronous operation

- Synchronous clock rates up to 1/2 of the device clock frequency

- Asynchronous clock rates up to 1/8 of the device clock frequency

- Supports serial frames with 5, 6, 7, 8, or 9 data bits and 1 or 2 stop bits

- Fractional baud rate generator

- Can generate desired baud rate from any system clock frequency

- No need for external oscillator with certain frequencies

- Built-in error detection and correction schemes

- Odd or even parity generation and parity check

- Data overrun and framing error detection

- Noise filtering includes false start bit detection and digital low-pass filter

- Separate interrupts for

- Transmit complete

- Transmit data register empty

- Receive complete

- Multiprocessor communication mode

- Addressing scheme to address a specific devices on a multidevice bus

- Enable unaddressed devices to automatically ignore all frames

- Master SPI mode

- Double buffered operation

- Operation up to 1/2 of the peripheral clock frequency

- IRCOM module for IrDA compliant pulse modulation/demodulation

### 24.2 Overview

The universal synchronous and asynchronous serial receiver and transmitter (USART) is a fast and flexible serial communication module. The USART supports full-duplex communication and asynchronous and synchronous operation. The USART can be configured to operate in SPI master mode and used for SPI communication.

Communication is frame based, and the frame format can be customized to support a wide range of standards. The USART is buffered in both directions, enabling continued data transmission without any delay between frames. Separate interrupts for receive and transmit complete enable fully interrupt driven communication. Frame error and buffer overflow are detected in hardware and indicated with separate status flags. Even or odd parity generation and parity check can also be enabled.

The clock generator includes a fractional baud rate generator that is able to generate a wide range of USART baud rates from any system clock frequencies. This removes the need to use an external crystal oscillator with a specific frequency to achieve a required baud rate. It also supports external clock input in synchronous slave operation.

When the USART is set in master SPI mode, all USART-specific logic is disabled, leaving the transmit and receive buffers, shift registers, and baud rate generator enabled. Pin control and interrupt generation are identical in both modes. The registers are used in both modes, but their functionality differs for some control settings.

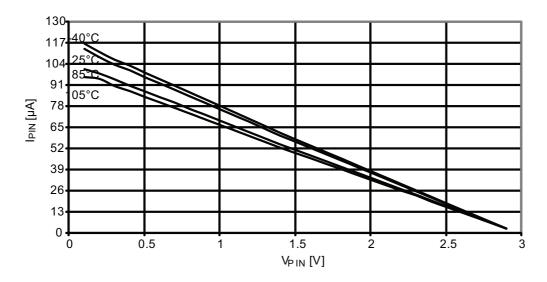

### 36.2.5 I/O Pin Characteristics

The I/O pins comply with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

| Table 36-39. | I/O pin characteristics. |

|--------------|--------------------------|

|--------------|--------------------------|

| Symbol                                                             | Parameter                                | Con                          | dition                 | Min.                | Тур.                 | Max.                 | Units |

|--------------------------------------------------------------------|------------------------------------------|------------------------------|------------------------|---------------------|----------------------|----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current              |                              |                        | -20                 |                      | 20                   | mA    |

|                                                                    | V <sub>CC</sub> = 2.7 - 3.6V             |                              | 2                      |                     | V <sub>CC</sub> +0.3 |                      |       |

| V <sub>IH</sub>                                                    | High Level Input Voltage                 | V <sub>CC</sub> = 2.0 - 2.7V |                        | 0.7*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 | V     |

|                                                                    |                                          | V <sub>CC</sub> = 1.6 - 2.0V |                        | 0.8*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 |       |

|                                                                    |                                          | V <sub>CC</sub> = 2.7- 3.6V  |                        | -0.3                |                      | 0.8                  |       |

| V <sub>IL</sub>                                                    | Low Level Input Voltage                  | V <sub>CC</sub> = 2.0 - 2.7V |                        | -0.3                |                      | 0.2*V <sub>CC</sub>  | V     |

|                                                                    |                                          | V <sub>CC</sub> = 1.6 - 2.0V |                        | -0.3                |                      | 0.2*V <sub>CC</sub>  |       |

|                                                                    |                                          | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OH</sub> = -2mA | 2.4                 | 0.19                 |                      |       |

| M                                                                  | High Level Output Voltage                | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OH</sub> = -1mA | 2.0                 | 2.44                 |                      | V     |

|                                                                    |                                          |                              | I <sub>OH</sub> = -2mA | 1.7                 | 2.37                 |                      |       |

| V <sub>OH</sub>                                                    |                                          | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -8mA | 2.6                 | 2.9                  |                      |       |

|                                                                    |                                          | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -6mA | 2.1                 | 2.6                  |                      |       |

|                                                                    |                                          | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -2mA | 1.4                 | 1.6                  |                      |       |

|                                                                    |                                          | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OL</sub> = 2mA  |                     | 0.05                 | 0.4                  |       |

|                                                                    |                                          |                              | I <sub>OL</sub> = 1mA  |                     | 0.03                 | 0.4                  |       |

| V                                                                  | Low Level Output Voltage                 | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OL</sub> = 2mA  |                     | 0.05                 | 0.7                  | V     |

| V <sub>OL</sub>                                                    | Low Level Output voltage                 | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 15mA |                     | 0.4                  | 0.76                 | V     |

|                                                                    |                                          | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 10mA |                     | 0.3                  | 0.64                 |       |

|                                                                    |                                          | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 5mA  |                     | 0.2                  | 0.46                 |       |

| I <sub>IN</sub>                                                    | Input Leakage Current                    | T = 25°C                     |                        |                     | <0.01                | 0.1                  | μA    |

| R <sub>P</sub>                                                     | Pull/Buss keeper Resistor                |                              |                        |                     | 27                   |                      | kΩ    |

| t <sub>r</sub>                                                     | Rise time                                | No load                      |                        |                     | 4                    |                      | ns    |

| L,                                                                 | The sum of all Law for PORTA and PORTB m |                              | slew rate limitation   |                     | 7                    |                      | 113   |

Notes:

1. The sum of all I<sub>OH</sub> for PORTA and PORTB must not exceed 100mA. The sum of all I<sub>OH</sub> for PORTC, PORTD, PORTE must for each port not exceed 200mA. The sum of all I<sub>OH</sub> for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all I<sub>OL</sub> for pins PF[6-7] on PORTF, PORTR and PDI must not exceed 100mA.

2. The sum of all  $I_{OL}$  for PORTA and PORTB must not exceed 100mA. The sum of all  $I_{OL}$  for PORTC, PORTD, PORTE must for each port not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[6-7] on PORTF, PORTR and PDI must not exceed 100mA.

### 36.3.5 I/O Pin Characteristics

The I/O pins comply with the JEDEC LVTTL and LVCMOS specification and the high- and low level input and output voltage limits reflect or exceed this specification.

| Table 36-71. | I/O pin characteristics. |

|--------------|--------------------------|

|--------------|--------------------------|

| Symbol                                                             | Parameter                   | Con                          | dition                 | Min.                | Тур.                 | Max.                 | Units |

|--------------------------------------------------------------------|-----------------------------|------------------------------|------------------------|---------------------|----------------------|----------------------|-------|

| I <sub>OH</sub> <sup>(1)</sup> /<br>I <sub>OL</sub> <sup>(2)</sup> | I/O pin source/sink current |                              |                        | -20                 |                      | 20                   | mA    |

|                                                                    |                             | V <sub>CC</sub> = 2.7 - 3.6V |                        | 2                   |                      | V <sub>CC</sub> +0.3 |       |

| V <sub>IH</sub>                                                    | High Level Input Voltage    | V <sub>CC</sub> = 2.0 - 2.7V |                        | 0.7*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 | V     |

|                                                                    |                             | V <sub>CC</sub> = 1.6 - 2.0V |                        | 0.8*V <sub>CC</sub> |                      | V <sub>CC</sub> +0.3 |       |

|                                                                    |                             | V <sub>CC</sub> = 2.7- 3.6V  |                        | -0.3                |                      | 0.8                  |       |

| V <sub>IL</sub>                                                    | Low Level Input Voltage     | V <sub>CC</sub> = 2.0 - 2.7V |                        | -0.3                |                      | 0.3*V <sub>CC</sub>  | V     |

|                                                                    |                             | V <sub>CC</sub> = 1.6 - 2.0V |                        | -0.3                |                      | 0.2*V <sub>CC</sub>  |       |

|                                                                    | High Level Output Voltage   | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OH</sub> = -2mA | 2.4                 | 0.94*V <sub>CC</sub> |                      |       |

| V <sub>OH</sub>                                                    |                             | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OH</sub> = -1mA | 2.0                 | 0.96*V <sub>CC</sub> |                      | V     |

|                                                                    |                             |                              | I <sub>OH</sub> = -2mA | 1.7                 | 0.92*V <sub>CC</sub> |                      |       |

|                                                                    |                             | V <sub>CC</sub> = 3.3V       | I <sub>OH</sub> = -8mA | 2.6                 | 2.9                  |                      |       |

|                                                                    |                             | V <sub>CC</sub> = 3.0V       | I <sub>OH</sub> = -6mA | 2.1                 | 2.6                  |                      |       |

|                                                                    |                             | V <sub>CC</sub> = 1.8V       | I <sub>OH</sub> = -2mA | 1.4                 | 1.6                  |                      |       |

|                                                                    |                             | V <sub>CC</sub> = 3.0 - 3.6V | I <sub>OL</sub> = 2mA  |                     | 0.05*V <sub>CC</sub> | 0.4                  |       |

|                                                                    |                             |                              | I <sub>OL</sub> = 1mA  |                     | 0.03*V <sub>CC</sub> | 0.4                  |       |

| V                                                                  | Low Level Output Voltage    | V <sub>CC</sub> = 2.3 - 2.7V | I <sub>OL</sub> = 2mA  |                     | 0.06*V <sub>CC</sub> | 0.7                  | V     |

| V <sub>OL</sub>                                                    | Low Level Output voltage    | V <sub>CC</sub> = 3.3V       | I <sub>OL</sub> = 15mA |                     | 0.4                  | 0.76                 | v     |

|                                                                    |                             | V <sub>CC</sub> = 3.0V       | I <sub>OL</sub> = 10mA |                     | 0.3                  | 0.64                 |       |

|                                                                    |                             | V <sub>CC</sub> = 1.8V       | I <sub>OL</sub> = 5mA  |                     | 0.3                  | 0.46                 |       |

| I <sub>IN</sub>                                                    | Input Leakage Current       | T = 25°C                     |                        |                     | <0.001               | 0.1                  | μA    |

| R <sub>P</sub>                                                     | Pull/Buss keeper Resistor   |                              |                        |                     | 27                   |                      | kΩ    |

| t <sub>r</sub>                                                     | Rise time                   | No load                      |                        |                     | 4                    |                      | ns    |

| ۲.                                                                 |                             |                              | slew rate limitation   |                     | 7                    |                      | 113   |

Notes:

1. The sum of all I<sub>OH</sub> for PORTA and PORTB must not exceed 100mA. The sum of all I<sub>OH</sub> for PORTC, PORTD, PORTE must for each port not exceed 200mA. The sum of all I<sub>OH</sub> for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all I<sub>OL</sub> for pins PF[6-7] on PORTF, PORTR and PDI must not exceed 100mA.

2. The sum of all  $I_{OL}$  for PORTA and PORTB must not exceed 100mA. The sum of all  $I_{OL}$  for PORTC, PORTD, PORTE must for each port not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[0-5] on PORTF must not exceed 200mA. The sum of all  $I_{OL}$  for pins PF[6-7] on PORTF, PORTR and PDI must not exceed 100mA.

#### Table 36-78. Accuracy characteristics.

| Symbol             | Parameter                    | Condit                             | tion                   | Min.                   | Тур.                   | Max. | Units |     |  |

|--------------------|------------------------------|------------------------------------|------------------------|------------------------|------------------------|------|-------|-----|--|

| RES                | Input Resolution             |                                    |                        |                        |                        | 12   | Bits  |     |  |

|                    |                              | V <sub>REF</sub> = Ext 1.0V        | V <sub>CC</sub> = 1.6V |                        | ±2.0                   | ±3   |       |     |  |

| INL <sup>(1)</sup> |                              |                                    | V <sub>CC</sub> = 3.6V |                        | ±1.5                   | ±2.5 |       |     |  |

|                    | Integral per linearity       |                                    | V <sub>CC</sub> = 1.6V |                        | ±2.0                   | ±4   | lah   |     |  |

|                    | Integral non-linearity       | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 3.6V |                        | ±1.5                   | ±4   | lsb   |     |  |

|                    |                              |                                    | V <sub>CC</sub> = 1.6V |                        | ±5.0                   |      |       |     |  |

|                    |                              | V <sub>REF</sub> =INT1V            | V <sub>CC</sub> = 3.6V |                        | ±5.0                   |      |       |     |  |

|                    | Differential non-linearity   | V <sub>REF</sub> =Ext 1.0V         | V <sub>CC</sub> = 1.6V |                        | ±1.5                   | 3    |       |     |  |

|                    |                              |                                    | V <sub>CC</sub> = 3.6V |                        | ±0.6                   | 1.5  |       |     |  |

| DNL <sup>(1)</sup> |                              |                                    |                        | V <sub>CC</sub> = 1.6V |                        | ±1.0 | 3.5   | lah |  |

| DNL ()             |                              | V <sub>REF</sub> =AV <sub>CC</sub> | V <sub>CC</sub> = 3.6V |                        | ±0.6                   | 1.5  | lsb   |     |  |

|                    |                              | V <sub>REF</sub> =INT1V            |                        |                        | V <sub>CC</sub> = 1.6V |      | ±4.5  |     |  |

|                    |                              |                                    | V <sub>CC</sub> = 3.6V |                        | ±4.5                   |      |       |     |  |

|                    | Gain error                   | After calibration                  |                        |                        | <4                     |      | lsb   |     |  |

|                    | Gain calibration step size   |                                    |                        |                        | 4                      |      | lsb   |     |  |

|                    | Gain calibration drift       | V <sub>REF</sub> = Ext 1.0V        |                        |                        | <0.2                   |      | mV/K  |     |  |

|                    | Offset error                 | After calibration                  |                        |                        | <1                     |      | lsb   |     |  |

|                    | Offset calibration step size |                                    |                        |                        | 1                      |      |       |     |  |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% output voltage range.

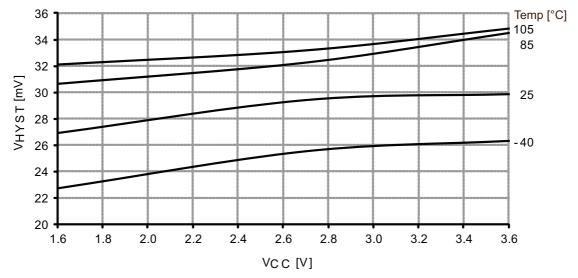

### 36.3.8 Analog Comparator Characteristics

#### Table 36-79. Analog Comparator characteristics.

| Symbol            | Parameter             | Condition              | Min. | Тур. | Max.             | Units  |

|-------------------|-----------------------|------------------------|------|------|------------------|--------|

| V <sub>off</sub>  | Input Offset Voltage  |                        |      | <±10 |                  | mV     |

| I <sub>lk</sub>   | Input Leakage Current |                        |      | <1   |                  | nA     |

|                   | Input voltage range   |                        | -0.1 |      | AV <sub>CC</sub> | V      |

|                   | AC startup time       |                        |      | 100  |                  | μs     |

| V <sub>hys1</sub> | Hysteresis, None      |                        |      | 0    |                  | mV     |

| V                 | Hysteresis, Small     | mode = High Speed (HS) |      | 13   |                  | mV     |

| V <sub>hys2</sub> |                       | mode = Low Power (LP)  |      | 30   |                  | - 11IV |

| V                 | Hysteresis, Large     | mode = HS              |      | 30   |                  | m\/    |

| V <sub>hys3</sub> |                       | mode = LP              |      | 60   |                  | mV     |

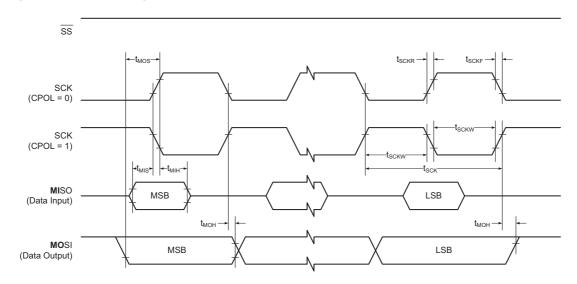

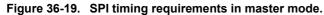

#### 36.3.15 SPI Characteristics

### Table 36-117. Programming time.

| Symbol | Parameter         | Condition                                         | Min. | <b>Typ.</b> <sup>(1)</sup> | Max. | Units |

|--------|-------------------|---------------------------------------------------|------|----------------------------|------|-------|

|        | Chip Erase        | 256KB Flash, EEPROM <sup>(2)</sup> and SRAM Erase |      | 105                        |      | ms    |

|        | Application Erase | Section erase                                     |      | 6                          |      | ms    |

|        |                   | Page Erase                                        |      | 4                          |      |       |

|        | Flash             | Page Write                                        |      | 4                          |      | ms    |

|        |                   | Atomic Page Erase and Write                       |      | 8                          |      |       |

|        |                   | Page Erase                                        |      | 4                          |      |       |

|        | EEPROM            | Page Write                                        |      | 4                          |      | ms    |

|        |                   | Atomic Page Erase and Write                       |      | 8                          |      |       |

Notes: 1. Programming is timed from the 2MHz internal oscillator.

2. EEPROM is not erased if the EESAVE fuse is programmed.

### 36.4.14 Clock and Oscillator Characteristics

#### 36.4.14.1 Calibrated 32.768kHz Internal Oscillator characteristics

#### Table 36-118. 32.768kHz internal oscillator characteristics.

| Symbol | Parameter                    | Condition                        | Min. | Тур.   | Max. | Units |

|--------|------------------------------|----------------------------------|------|--------|------|-------|

|        | Frequency                    |                                  |      | 32.768 |      | kHz   |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V | -0.5 |        | 0.5  | %     |

|        | User calibration accuracy    |                                  | -0.5 |        | 0.5  | ms    |

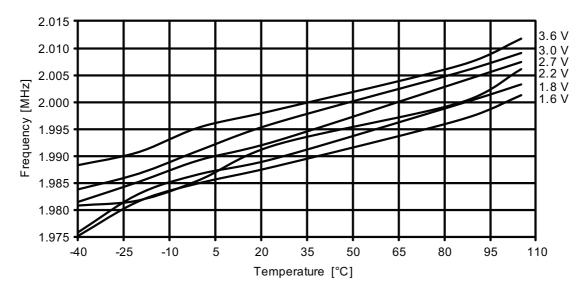

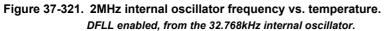

#### 36.4.14.2 Calibrated 2MHz RC Internal Oscillator characteristics

#### Table 36-119. 2MHz internal oscillator characteristics.

| Symbol | Parameter                    | Condition                                                    | Min. | Тур. | Max. | Units |

|--------|------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Frequency range              | DFLL can tune to this frequency over voltage and temperature | 1.8  |      | 2.2  | MHz   |

|        | Factory calibrated frequency |                                                              |      | 2.0  |      | MHz   |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V                             | -1.5 |      | 1.5  | %     |

|        | User calibration accuracy    |                                                              | -0.2 |      | 0.2  | %     |

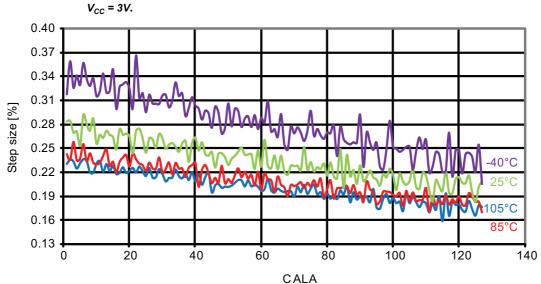

|        | DFLL calibration stepsize    |                                                              |      | 0.22 |      | %     |

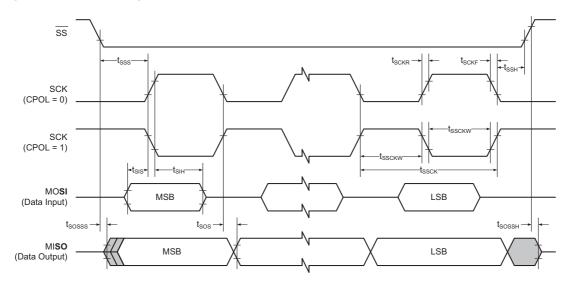

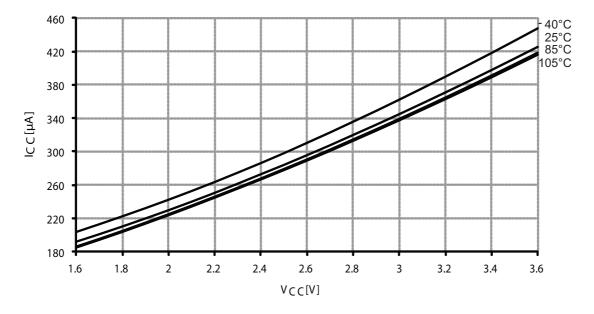

Figure 37-11. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 1MHz \text{ external clock.}$

### 37.1.5 Analog Comparator Characteristics

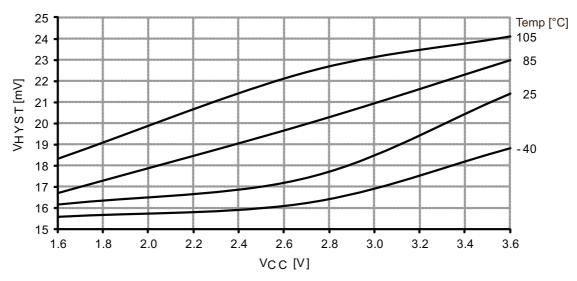

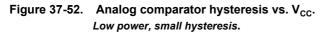

Figure 37-51. Analog comparator hysteresis vs. V<sub>CC</sub> High-speed, small hysteresis.

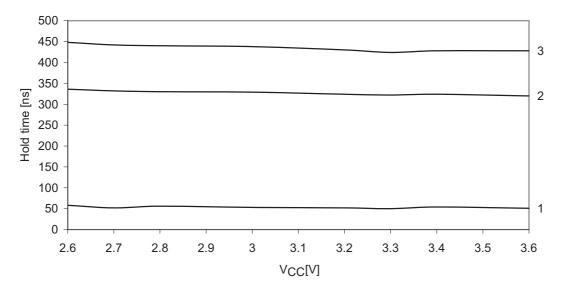

Figure 37-82. SDA hold time vs. supply voltage.

#### 37.1.12 PDI characteristics

22 18

14 10 1.6

1.8

2

2.2

2.4

2.6

VCC[V]

2.8

3

3.2

3.4

3.6

-40

25

85 105

Temp [°C]

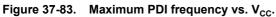

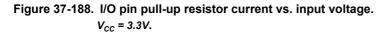

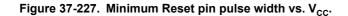

Figure 37-108. I/O pin output voltage vs. source current.

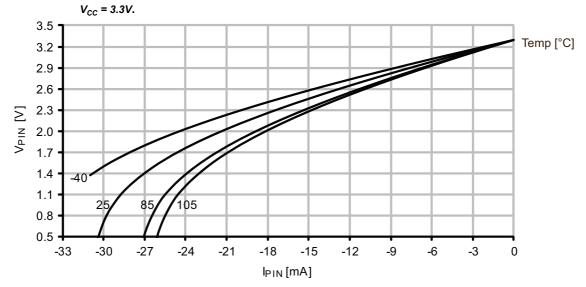

Figure 37-109. I/O pin output voltage vs. source current.

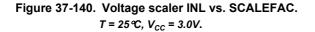

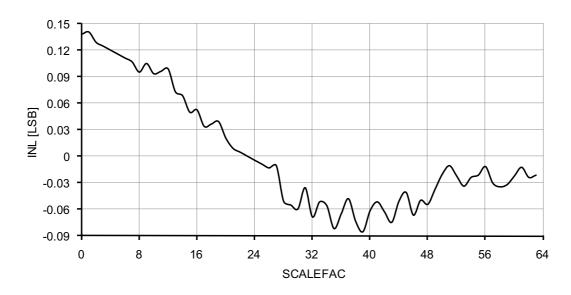

Figure 37-141. ADC/DAC Internal 1.0V reference vs. temperature.

## 37.3 ATxmega192A3U

### 37.3.1 Current consumption

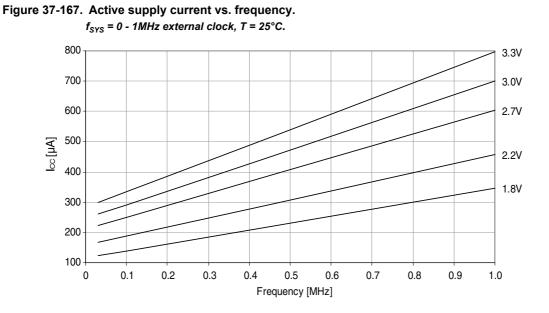

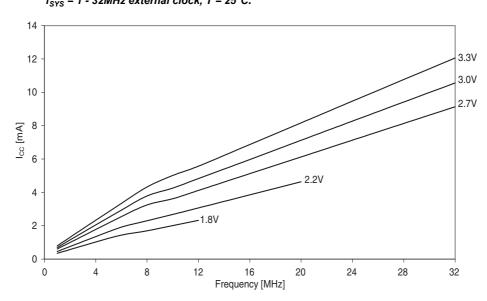

#### 37.3.1.1 Active mode supply current

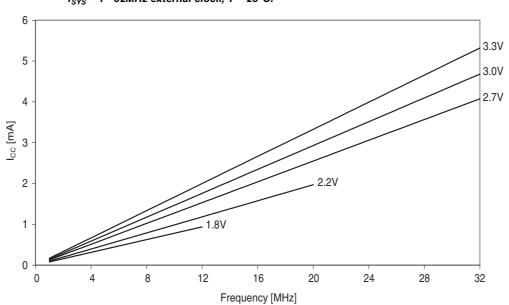

Figure 37-168. Active supply current vs. frequency.  $f_{SYS} = 1 - 32MHz \text{ external clock, } T = 25^{\circ}C.$

**Atmel**

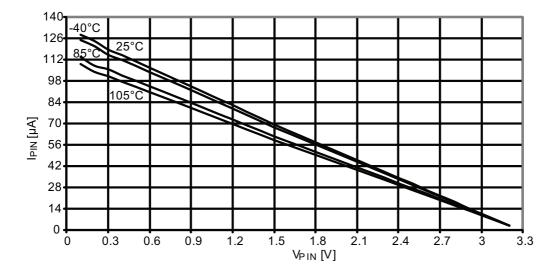

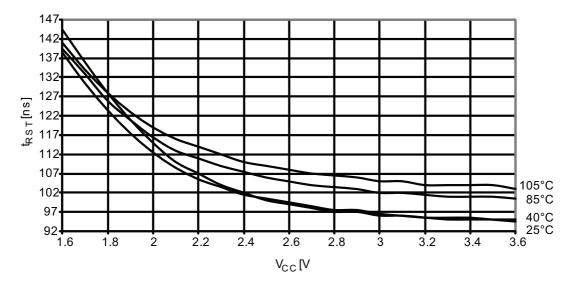

#### 37.3.8 External Reset Characteristics

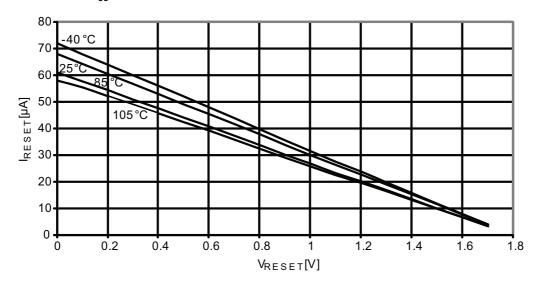

Figure 37-228. Reset pin pull-up resistor current vs. reset pin voltage.  $V_{cc} = 1.8V$ .