#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                     |

|----------------------------|----------------------------------------------------------------------------|

| Core Processor             | AVR                                                                        |

| Core Size                  | 8/16-Bit                                                                   |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O              | 50                                                                         |

| Program Memory Size        | 192KB (96K x 16)                                                           |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 16K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                      |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 64-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 64-QFN (9×9)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega192a3u-m7 |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

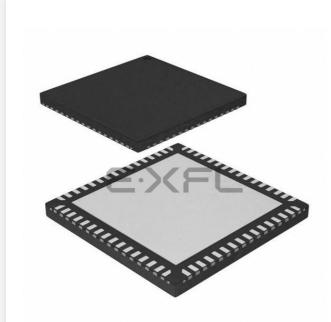

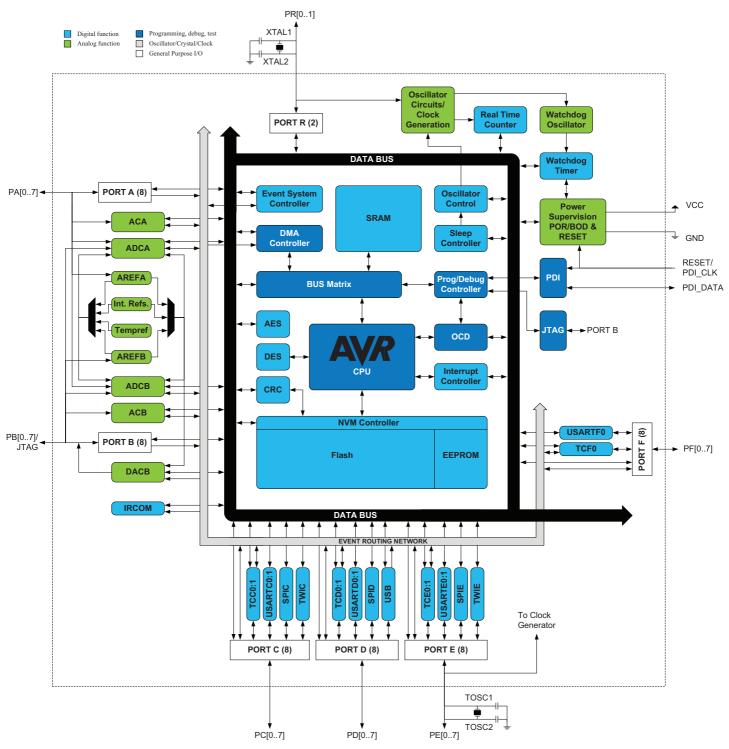

# 3.1 Block Diagram

Atmel

# 6.4 ALU - Arithmetic Logic Unit

The arithmetic logic unit (ALU) supports arithmetic and logic operations between registers or between a constant and a register. Single-register operations can also be executed. The ALU operates in direct connection with all 32 general purpose registers. In a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed and the result is stored in the register file. After an arithmetic or logic operation, the status register is updated to reflect information about the result of the operation.

ALU operations are divided into three main categories – arithmetic, logical, and bit functions. Both 8- and 16-bit arithmetic is supported, and the instruction set allows for efficient implementation of 32-bit aritmetic. The hardware multiplier supports signed and unsigned multiplication and fractional format.

# 6.4.1 Hardware Multiplier

The multiplier is capable of multiplying two 8-bit numbers into a 16-bit result. The hardware multiplier supports different variations of signed and unsigned integer and fractional numbers:

- Multiplication of unsigned integers

- Multiplication of signed integers

- Multiplication of a signed integer with an unsigned integer

- Multiplication of unsigned fractional numbers

- Multiplication of signed fractional numbers

- Multiplication of a signed fractional number with an unsigned one

A multiplication takes two CPU clock cycles.

# 6.5 Program Flow

After reset, the CPU starts to execute instructions from the lowest address in the flash programmemory '0.' The program counter (PC) addresses the next instruction to be fetched.

Program flow is provided by conditional and unconditional jump and call instructions capable of addressing the whole address space directly. Most AVR instructions use a 16-bit word format, while a limited number use a 32-bit format.

During interrupts and subroutine calls, the return address PC is stored on the stack. The stack is allocated in the general data SRAM, and consequently the stack size is only limited by the total SRAM size and the usage of the SRAM. After reset, the stack pointer (SP) points to the highest address in the internal SRAM. The SP is read/write accessible in the I/O memory space, enabling easy implementation of multiple stacks or stack areas. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR CPU.

# 6.6 Status Register

The status register (SREG) contains information about the result of the most recently executed arithmetic or logic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the status register is updated after all ALU operations, as specified in the instruction set reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The status register is not automatically stored when entering an interrupt routine nor restored when returning from an interrupt. This must be handled by software.

The status register is accessible in the I/O memory space.

# 18. AWeX – Advanced Waveform Extension

# 18.1 Features

- Waveform output with complementary output from each compare channel

- Four dead-time insertion (DTI) units

- 8-bit resolution

- Separate high and low side dead-time setting

- Double buffered dead time

- Optionally halts timer during dead-time insertion

- Pattern generation unit creating synchronised bit pattern across the port pins

- Double buffered pattern generation

- Optional distribution of one compare channel output across the port pins

- Event controlled fault protection for instant and predictable fault triggering

# 18.2 Overview

The advanced waveform extension (AWeX) provides extra functions to the timer/counter in waveform generation (WG) modes. It is primarily intended for use with different types of motor control and other power control applications. It enables low- and high side output with dead-time insertion and fault protection for disabling and shutting down external drivers. It can also generate a synchronized bit pattern across the port pins.

Each of the waveform generator outputs from the timer/counter 0 are split into a complimentary pair of outputs when any AWeX features are enabled. These output pairs go through a dead-time insertion (DTI) unit that generates the non-inverted low side (LS) and inverted high side (HS) of the WG output with dead-time insertion between LS and HS switching. The DTI output will override the normal port value according to the port override setting.

The pattern generation unit can be used to generate a synchronized bit pattern on the port it is connected to. In addition, the WG output from compare channel A can be distributed to and override all the port pins. When the pattern generator unit is enabled, the DTI unit is bypassed.

The fault protection unit is connected to the event system, enabling any event to trigger a fault condition that will disable the AWeX output. The event system ensures predictable and instant fault reaction, and gives flexibility in the selection of fault triggers.

The AWeX is available for TCC0. The notation of this is AWEXC.

Atmel

| Mnemonics | Operands | Description                  | Oper                  | ation                                                                 |                                   | Flags     | #Clocks |

|-----------|----------|------------------------------|-----------------------|-----------------------------------------------------------------------|-----------------------------------|-----------|---------|

| IN        | Rd, A    | In From I/O Location         | Rd                    | ←                                                                     | I/O(A)                            | None      | 1       |

| OUT       | A, Rr    | Out To I/O Location          | I/O(A)                | ~                                                                     | Rr                                | None      | 1       |

| PUSH      | Rr       | Push Register on Stack       | STACK                 | ~                                                                     | Rr                                | None      | 1 (1)   |

| POP       | Rd       | Pop Register from Stack      | Rd                    | ~                                                                     | STACK                             | None      | 2 (1)   |

| ХСН       | Z, Rd    | Exchange RAM location        | Temp<br>Rd<br>(Z)     | $\begin{array}{c} \downarrow \\ \downarrow \\ \downarrow \end{array}$ | Rd,<br>(Z),<br>Temp               | None      | 2       |

| LAS       | Z, Rd    | Load and Set RAM location    | Temp<br>Rd<br>(Z)     | $\downarrow \downarrow \downarrow \downarrow$                         | Rd,<br>(Z),<br>Temp v (Z)         | None      | 2       |

| LAC       | Z, Rd    | Load and Clear RAM location  | Temp<br>Rd<br>(Z)     | $\begin{array}{c} \downarrow \\ \downarrow \\ \downarrow \end{array}$ | Rd,<br>(Z),<br>(\$FFh – Rd) ● (Z) | None      | 2       |

| LAT       | Z, Rd    | Load and Toggle RAM location | Temp<br>Rd<br>(Z)     | $\stackrel{\leftarrow}{\leftarrow}$                                   | Rd,<br>(Z),<br>Temp ⊕ (Z)         | None      | 2       |

|           |          | Bit and                      | bit-test instructions |                                                                       |                                   |           |         |

| LSL       | Rd       | Logical Shift Left           | Rd(n+1)<br>Rd(0)<br>C | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$ | Rd(n),<br>0,<br>Rd(7)             | Z,C,N,V,H | 1       |

| LSR       | Rd       | Logical Shift Right          | Rd(n)<br>Rd(7)<br>C   | $\begin{array}{c} \downarrow \\ \downarrow \\ \downarrow \end{array}$ | Rd(n+1),<br>0,<br>Rd(0)           | Z,C,N,V   | 1       |

| ROL       | Rd       | Rotate Left Through Carry    | Rd(0)<br>Rd(n+1)<br>C | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$ | C,<br>Rd(n),<br>Rd(7)             | Z,C,N,V,H | 1       |

| ROR       | Rd       | Rotate Right Through Carry   | Rd(7)<br>Rd(n)<br>C   | $\begin{array}{c} \downarrow \\ \downarrow \\ \downarrow \end{array}$ | C,<br>Rd(n+1),<br>Rd(0)           | Z,C,N,V   | 1       |

| ASR       | Rd       | Arithmetic Shift Right       | Rd(n)                 | ←                                                                     | Rd(n+1), n=06                     | Z,C,N,V   | 1       |

| SWAP      | Rd       | Swap Nibbles                 | Rd(30)                | $\leftrightarrow$                                                     | Rd(74)                            | None      | 1       |

| BSET      | S        | Flag Set                     | SREG(s)               | ←                                                                     | 1                                 | SREG(s)   | 1       |

| BCLR      | S        | Flag Clear                   | SREG(s)               | ←                                                                     | 0                                 | SREG(s)   | 1       |

| SBI       | A, b     | Set Bit in I/O Register      | I/O(A, b)             | ←                                                                     | 1                                 | None      | 1       |

| CBI       | A, b     | Clear Bit in I/O Register    | I/O(A, b)             | ←                                                                     | 0                                 | None      | 1       |

| BST       | Rr, b    | Bit Store from Register to T | Т                     | ←                                                                     | Rr(b)                             | Т         | 1       |

| BLD       | Rd, b    | Bit load from T to Register  | Rd(b)                 | ←                                                                     | т                                 | None      | 1       |

| SEC       |          | Set Carry                    | C                     | ←                                                                     | 1                                 | С         | 1       |

| CLC       |          | Clear Carry                  | C                     | ←                                                                     | 0                                 | С         | 1       |

| SEN       |          | Set Negative Flag            | N                     | ←                                                                     | 1                                 | N         | 1       |

| CLN       |          | Clear Negative Flag          | Ν                     | ←                                                                     | 0                                 | N         | 1       |

| SEZ       |          | Set Zero Flag                | Z                     | ←                                                                     | 1                                 | Z         | 1       |

| CLZ       |          | Clear Zero Flag              | Z                     | ←                                                                     | 0                                 | Z         | 1       |

| SEI       |          | Global Interrupt Enable      | I                     | ←                                                                     | 1                                 | I         | 1       |

| CLI       |          | Global Interrupt Disable     | I                     | ←                                                                     | 0                                 | I         | 1       |

| SES       |          | Set Signed Test Flag         | S                     | ←                                                                     | 1                                 | S         | 1       |

| CLS       |          | Clear Signed Test Flag       | S                     | ←                                                                     | 0                                 | S         | 1       |

| Symbol        | Parameter                       | Condition             | Min.                                            | Тур. | Max. | Units |           |

|---------------|---------------------------------|-----------------------|-------------------------------------------------|------|------|-------|-----------|

| Offset Error, |                                 | 1x gain, normal mode  |                                                 |      | -2   |       |           |

|               | Offset Error,<br>input referred | 8x gain, normal mode  |                                                 |      | -5   |       | mV        |

|               |                                 | 64x gain, normal mode |                                                 |      | -4   |       |           |

|               |                                 | 1x gain, normal mode  | V <sub>CC</sub> = 3.6V<br>Ext. V <sub>REF</sub> |      | 0.5  |       |           |

|               | Noise                           | 8x gain, normal mode  |                                                 |      | 1.5  |       | mV<br>rms |

|               |                                 | 64x gain, normal mode |                                                 |      | 11   |       |           |

Note: 1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

## 36.1.7 DAC Characteristics

# Table 36-12. Power supply, reference and output range.

| Symbol               | Parameter                   | Condition                               | Min.                  | Тур. | Max.                   | Units |

|----------------------|-----------------------------|-----------------------------------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>     | Analog supply voltage       |                                         | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  |       |

| AV <sub>REF</sub>    | External reference voltage  |                                         | 1.0                   |      | V <sub>CC</sub> - 0.6  | V     |

| R <sub>channel</sub> | DC output impedance         |                                         |                       |      | 50                     | Ω     |

|                      | Linear output voltage range |                                         | 0.15                  |      | AV <sub>CC</sub> -0.15 | V     |

| R <sub>AREF</sub>    | Reference input resistance  |                                         |                       | >10  |                        | MΩ    |

| CAREF                | Reference input capacitance | Static load                             |                       | 7    |                        | pF    |

|                      | Minimum Resistance load     |                                         | 1                     |      |                        | kΩ    |

|                      | Maximum capacitance load    |                                         |                       |      | 100                    | pF    |

|                      | Maximum capacitance load    | 1000 $\Omega$ serial resistance         |                       |      | 1                      | nF    |

|                      | Output sink/source          | Operating within accuracy specification |                       |      | AV <sub>CC</sub> /1000 | mA    |

|                      |                             | Safe operation                          |                       |      | 10                     |       |

### Table 36-13.Clock and timing.

| Symbol                           | Parameter         | Condition                 |             | Min. | Тур. | Max. | Units |

|----------------------------------|-------------------|---------------------------|-------------|------|------|------|-------|

| f                                | Conversion rate   | C <sub>load</sub> =100pF, | Normal mode | 0    |      | 1000 | kana  |

| f <sub>DAC</sub> Conversion rate | maximum step size | Low power mode            | 0           |      | 500  | ksps |       |

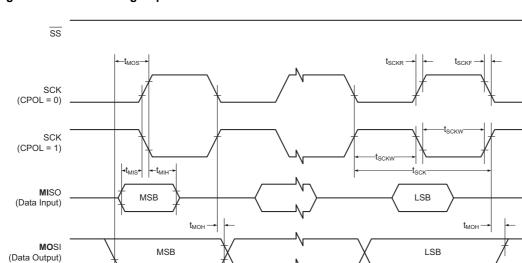

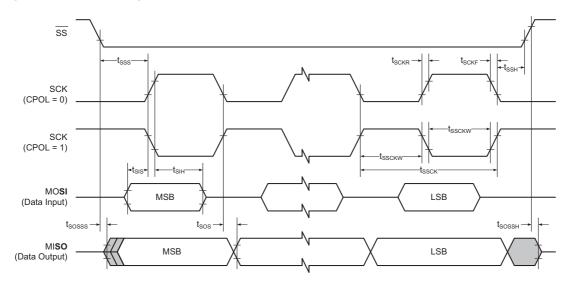

## 36.2.15 SPI Characteristics

Table 36-63.

SPI timing characteristics and requirements.

| Symbol             | Parameter                            | Condition | Min.                    | Тур.                                   | Max. | Units |

|--------------------|--------------------------------------|-----------|-------------------------|----------------------------------------|------|-------|

| t <sub>scк</sub>   | SCK Period                           | Master    |                         | (See Table 21-4 in<br>XMEGA AU Manual) |      |       |

| t <sub>scкw</sub>  | SCK high/low width                   | Master    |                         | 0.5*SCK                                |      |       |

| t <sub>SCKR</sub>  | SCK Rise time                        | Master    |                         | 2.7                                    |      |       |

| t <sub>SCKF</sub>  | SCK Fall time                        | Master    |                         | 2.7                                    |      |       |

| t <sub>MIS</sub>   | MISO setup to SCK                    | Master    |                         | 11                                     |      |       |

| t <sub>MIH</sub>   | MISO hold after SCK                  | Master    |                         | 0                                      |      |       |

| t <sub>MOS</sub>   | MOSI setup SCK                       | Master    |                         | 0.5*t <sub>SCK</sub>                   |      |       |

| t <sub>MOH</sub>   | MOSI hold after SCK                  | Master    |                         | 1                                      |      |       |

| t <sub>sscк</sub>  | Slave SCK Period                     | Slave     | >4*t Clk <sub>PER</sub> |                                        |      |       |

| t <sub>sscкw</sub> | SCK high/low width                   | Slave     | >2*t Clk <sub>PER</sub> |                                        |      | ns    |

| t <sub>SSCKR</sub> | SCK Rise time                        | Slave     |                         |                                        | 1600 |       |

| t <sub>SSCKF</sub> | SCK Fall time                        | Slave     |                         |                                        | 1600 |       |

| t <sub>SIS</sub>   | MOSI setup to SCK                    | Slave     | 3                       |                                        |      |       |

| t <sub>SIH</sub>   | MOSI hold after SCK                  | Slave     | t <sub>SCK</sub>        |                                        |      |       |

| t <sub>SSS</sub>   | SS setup to SCK                      | Slave     | 20                      |                                        |      |       |

| t <sub>SSH</sub>   | SS hold after SCK                    | Slave     | 20                      |                                        |      |       |

| t <sub>sos</sub>   | MISO setup SCK                       | Slave     |                         | 8                                      |      |       |

| t <sub>SOH</sub>   | MISO hold after SCK                  | Slave     |                         | 13                                     |      |       |

| t <sub>soss</sub>  | MISO setup after SS low              | Slave     |                         | 11                                     |      |       |

| t <sub>SOSH</sub>  | MISO hold after $\overline{SS}$ high | Slave     |                         | 8                                      |      |       |

| Symbol             | Parameter                             | Condition                            |                                      | Min. | Тур. | Max.                    | Units |

|--------------------|---------------------------------------|--------------------------------------|--------------------------------------|------|------|-------------------------|-------|

|                    |                                       | XOSCPWR=0,<br>FRQRANGE=0             |                                      | 2.4k |      |                         |       |

|                    |                                       |                                      | 1MHz crystal, CL=20pF                | 8.7k |      |                         |       |

|                    |                                       |                                      | 2MHz crystal, CL=20pF                | 2.1k |      |                         |       |

|                    |                                       |                                      | 4.2k                                 |      |      |                         |       |

|                    |                                       |                                      | 8MHz crystal                         | 250  |      |                         |       |

|                    |                                       | CL=20pF                              | 9MHz crystal                         | 195  |      |                         | -     |

|                    |                                       | XOSCPWR=0,                           | 8MHz crystal                         | 360  |      |                         |       |

|                    |                                       | FRQRANGE=2,                          | 9MHz crystal                         | 285  |      |                         |       |

|                    |                                       | CL=20pF                              | 12MHz crystal                        | 155  |      |                         | -     |

|                    |                                       | XOSCPWR=0,                           | 9MHz crystal                         | 365  |      |                         |       |

| R <sub>Q</sub>     | Negative impedance                    | FRQRANGE=3,<br>CL=20pF               | 12MHz crystal                        | 200  |      |                         | Ω     |

| ··Q                |                                       |                                      | 16MHz crystal                        | 105  |      |                         |       |

|                    |                                       | XOSCPWR=1,<br>FRQRANGE=0,<br>CL=20pF | 9MHz crystal                         | 435  |      |                         | -     |

|                    |                                       |                                      | 12MHz crystal                        | 235  |      |                         |       |

|                    |                                       |                                      | 16MHz crystal                        | 125  |      |                         |       |

|                    |                                       | XOSCPWR=1,<br>FRQRANGE=1,<br>CL=20pF | 9MHz crystal                         | 495  |      |                         |       |

|                    |                                       |                                      | 12MHz crystal                        | 270  |      |                         |       |

|                    |                                       |                                      | 16MHz crystal                        | 145  |      |                         |       |

|                    |                                       | XOSCPWR=1,<br>FRQRANGE=2,<br>CL=20pF | 12MHz crystal                        | 305  |      |                         |       |

|                    |                                       |                                      | 16MHz crystal                        | 160  |      |                         |       |

|                    |                                       | XOSCPWR=1,                           | 12MHz crystal                        | 380  |      |                         | -     |

|                    |                                       | FRQRANGE=3,<br>CL=20pF               | 16MHz crystal                        | 205  |      |                         |       |

|                    | ESR                                   | SF = Safety factor                   |                                      |      |      | min(R <sub>Q</sub> )/SF | kΩ    |

| C <sub>XTAL1</sub> | Parasitic<br>capacitance XTAL1<br>pin |                                      |                                      |      | 5.2  |                         | pF    |

| C <sub>XTAL2</sub> | Parasitic<br>capacitance XTAL2<br>pin |                                      |                                      |      | 6.8  |                         | pF    |

| C <sub>LOAD</sub>  | Parasitic<br>capacitance load         |                                      | but augranteed from decign and chara |      | 2.95 |                         | pF    |

Note: 1. Numbers for negative impedance are not tested in production but guaranteed from design and characterization.

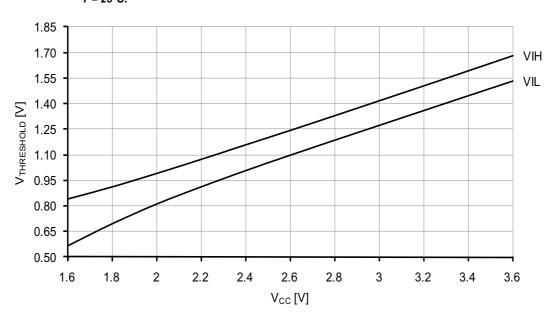

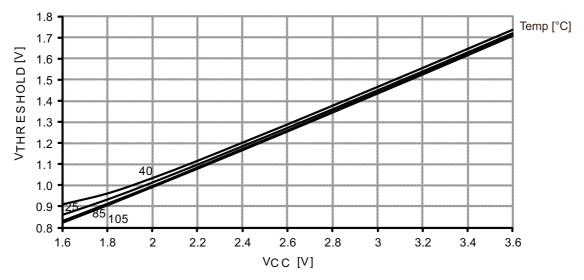

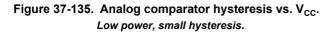

### 37.1.2.3 Thresholds and Hysteresis

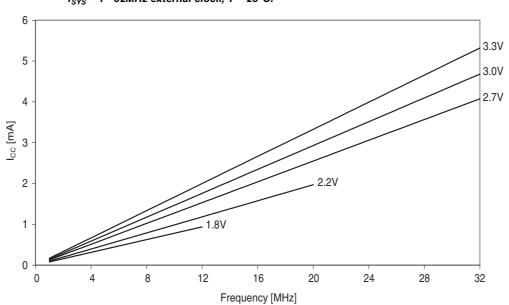

#### 37.1.10.4 32MHz Internal Oscillator

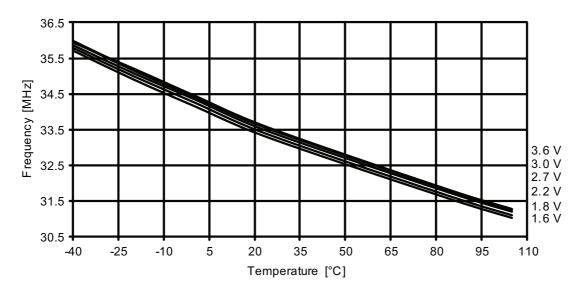

Figure 37-74. 32MHz internal oscillator frequency vs. temperature.

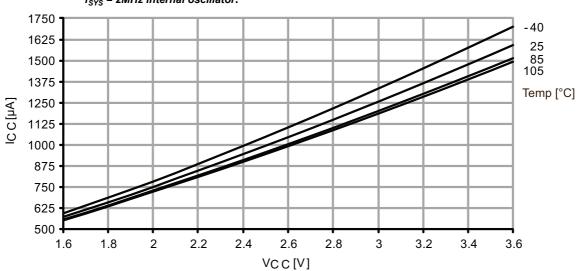

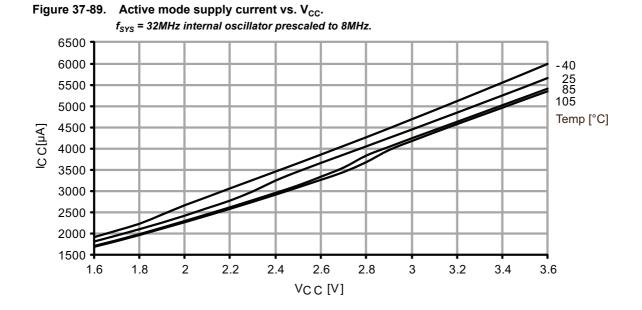

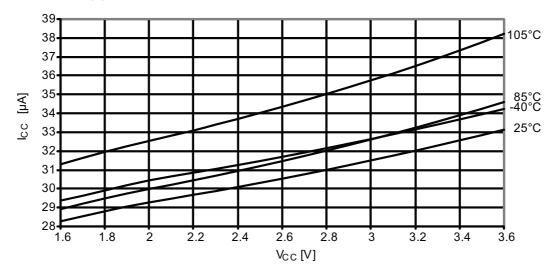

Figure 37-88. Active mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 2MHz$  internal oscillator.

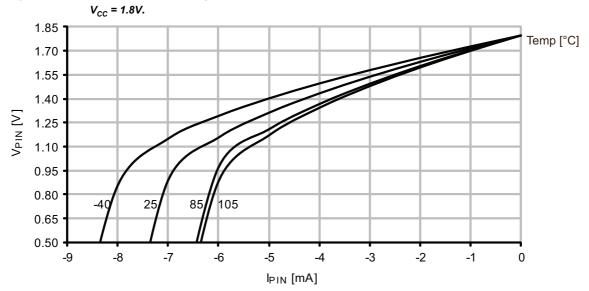

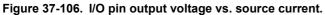

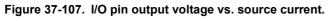

### 37.2.2.2 Output Voltage vs. Sink/Source Current

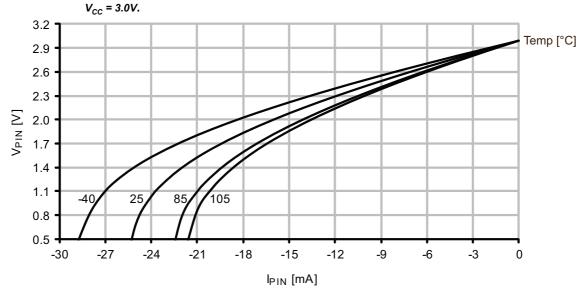

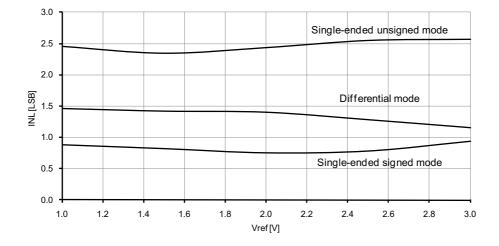

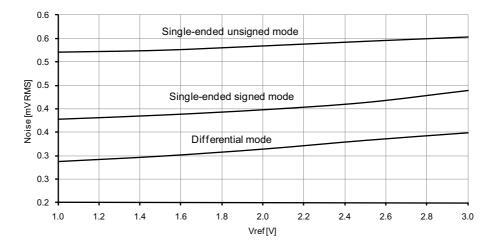

## 37.2.3 ADC Characteristics

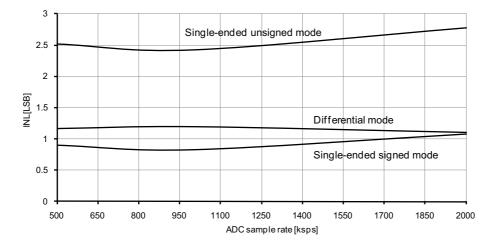

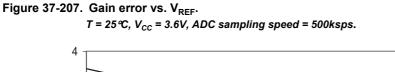

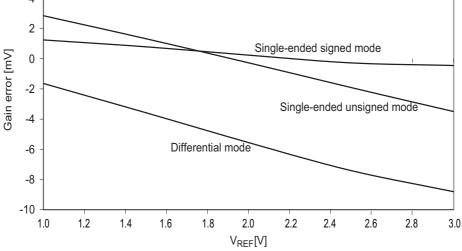

Figure 37-118. INL error vs. external  $V_{REF}$ .  $T = 25 \,$ C,  $V_{CC} = 3.6V$ , external reference.

# 37.2.5 Analog Comparator Characteristics

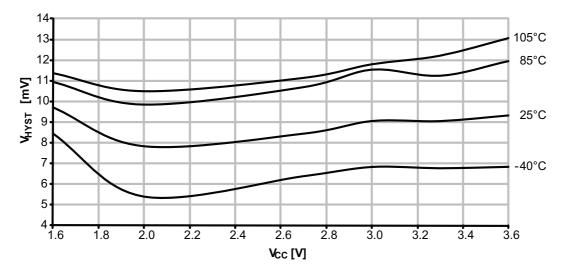

Figure 37-134. Analog comparator hysteresis vs. V<sub>CC</sub>. *High-speed, small hysteresis.*

Atmel

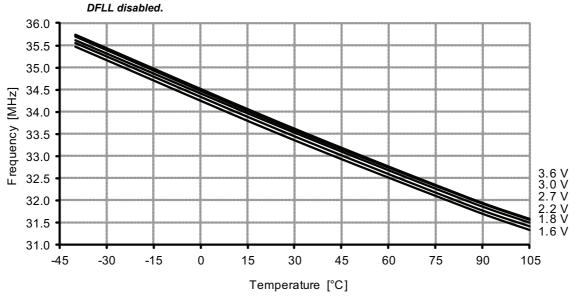

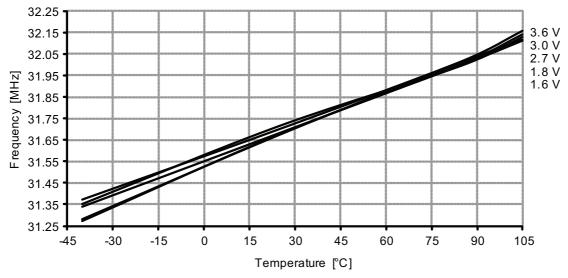

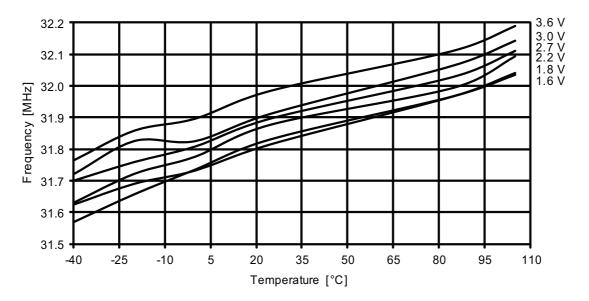

#### 37.3.10.4 32MHz Internal Oscillator

Figure 37-240. 32MHz internal oscillator frequency vs. temperature. *DFLL disabled*.

Figure 37-241. 32MHz internal oscillator frequency vs. temperature. DFLL enabled, from the 32.768kHz internal oscillator.

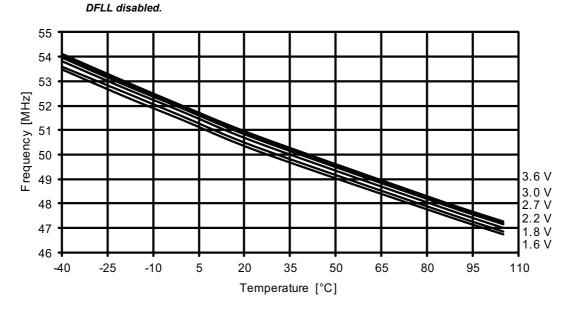

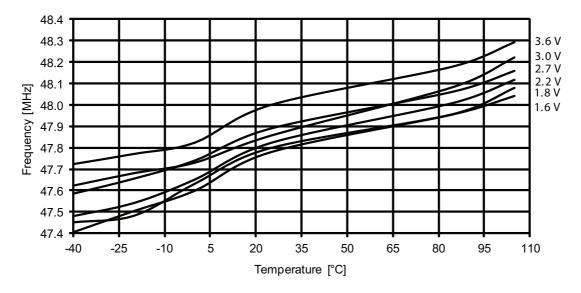

### 37.3.10.5 32MHz internal oscillator calibrated to 48MHz

Figure 37-244. 48MHz internal oscillator frequency vs. temperature.

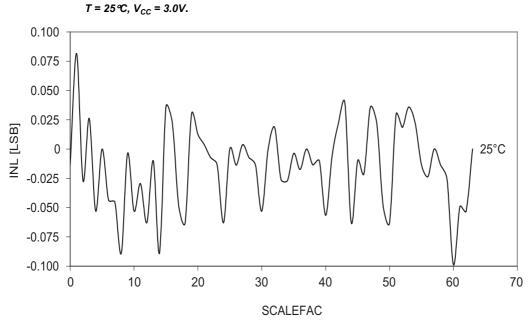

Figure 37-306. Voltage scaler INL vs. SCALEFAC.

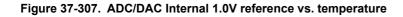

# 37.4.6 Internal 1.0V reference Characteristics