Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | AVR                                                                         |

| Core Size                  | 8/16-Bit                                                                    |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                  |

| Number of I/O              | 50                                                                          |

| Program Memory Size        | 192KB (96K x 16)                                                            |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 2K x 8                                                                      |

| RAM Size                   | 16K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                 |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                       |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 64-VFQFN Exposed Pad                                                        |

| Supplier Device Package    | 64-QFN (9x9)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega192a3u-mhr |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 6.4 ALU - Arithmetic Logic Unit

The arithmetic logic unit (ALU) supports arithmetic and logic operations between registers or between a constant and a register. Single-register operations can also be executed. The ALU operates in direct connection with all 32 general purpose registers. In a single clock cycle, arithmetic operations between general purpose registers or between a register and an immediate are executed and the result is stored in the register file. After an arithmetic or logic operation, the status register is updated to reflect information about the result of the operation.

ALU operations are divided into three main categories – arithmetic, logical, and bit functions. Both 8- and 16-bit arithmetic is supported, and the instruction set allows for efficient implementation of 32-bit aritmetic. The hardware multiplier supports signed and unsigned multiplication and fractional format.

### 6.4.1 Hardware Multiplier

The multiplier is capable of multiplying two 8-bit numbers into a 16-bit result. The hardware multiplier supports different variations of signed and unsigned integer and fractional numbers:

- Multiplication of unsigned integers

- Multiplication of signed integers

- Multiplication of a signed integer with an unsigned integer

- Multiplication of unsigned fractional numbers

- Multiplication of signed fractional numbers

- Multiplication of a signed fractional number with an unsigned one

A multiplication takes two CPU clock cycles.

### 6.5 Program Flow

After reset, the CPU starts to execute instructions from the lowest address in the flash programmemory '0.' The program counter (PC) addresses the next instruction to be fetched.

Program flow is provided by conditional and unconditional jump and call instructions capable of addressing the whole address space directly. Most AVR instructions use a 16-bit word format, while a limited number use a 32-bit format.

During interrupts and subroutine calls, the return address PC is stored on the stack. The stack is allocated in the general data SRAM, and consequently the stack size is only limited by the total SRAM size and the usage of the SRAM. After reset, the stack pointer (SP) points to the highest address in the internal SRAM. The SP is read/write accessible in the I/O memory space, enabling easy implementation of multiple stacks or stack areas. The data SRAM can easily be accessed through the five different addressing modes supported in the AVR CPU.

### 6.6 Status Register

The status register (SREG) contains information about the result of the most recently executed arithmetic or logic instruction. This information can be used for altering program flow in order to perform conditional operations. Note that the status register is updated after all ALU operations, as specified in the instruction set reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code.

The status register is not automatically stored when entering an interrupt routine nor restored when returning from an interrupt. This must be handled by software.

The status register is accessible in the I/O memory space.

## 12. System Control and Reset

#### 12.1 Features

- Reset the microcontroller and set it to initial state when a reset source goes active

- Multiple reset sources that cover different situations

- Power-on reset

- External reset

- Watchdog reset

- Brownout reset

- PDI reset

- Software reset

- Asynchronous operation

- No running system clock in the device is required for reset

- Reset status register for reading the reset source from the application code

#### 12.2 Overview

The reset system issues a microcontroller reset and sets the device to its initial state. This is for situations where operation should not start or continue, such as when the microcontroller operates below its power supply rating. If a reset source goes active, the device enters and is kept in reset until all reset sources have released their reset. The I/O pins are immediately tri-stated. The program counter is set to the reset vector location, and all I/O registers are set to their initial values. The SRAM content is kept. However, if the device accesses the SRAM when a reset occurs, the content of the accessed location can not be guaranteed.

After reset is released from all reset sources, the default oscillator is started and calibrated before the device starts running from the reset vector address. By default, this is the lowest program memory address, 0, but it is possible to move the reset vector to the lowest address in the boot section.

The reset functionality is asynchronous, and so no running system clock is required to reset the device. The software reset feature makes it possible to issue a controlled system reset from the user software.

The reset status register has individual status flags for each reset source. It is cleared at power-on reset, and shows which sources have issued a reset since the last power-on.

### 12.3 Reset Sequence

A reset request from any reset source will immediately reset the device and keep it in reset as long as the request is active. When all reset requests are released, the device will go through three stages before the device starts running again:

- Reset counter delay

- Oscillator startup

- Oscillator calibration

If another reset requests occurs during this process, the reset sequence will start over again.

### 12.4 Reset Sources

#### 12.4.1 Power-on Reset

A power-on reset (POR) is generated by an on-chip detection circuit. The POR is activated when the  $V_{CC}$  rises and reaches the POR threshold voltage ( $V_{POT}$ ), and this will start the reset sequence.

The POR is also activated to power down the device properly when the  $V_{CC}$  falls and drops below the  $V_{POT}$  level.

The  $V_{POT}$  level is higher for falling  $V_{CC}$  than for rising  $V_{CC}$ . Consult the datasheet for POR characteristics data.

### 15. I/O Ports

### 15.1 Features

- 50 general purpose input and output pins with individual configuration

- Output driver with configurable driver and pull settings:

- Totem-pole

- Wired-AND

- Wired-OR

- Bus-keeper

- Inverted I/O

- Input with synchronous and/or asynchronous sensing with interrupts and events

- Sense both edges

- Sense rising edges

- Sense falling edges

- Sense low level

- Optional pull-up and pull-down resistor on input and Wired-OR/AND configurations

- Optional slew rate control

- Asynchronous pin change sensing that can wake the device from all sleep modes

- Two port interrupts with pin masking per I/O port

- Efficient and safe access to port pins

- Hardware read-modify-write through dedicated toggle/clear/set registers

- Configuration of multiple pins in a single operation

- Mapping of port registers into bit-accessible I/O memory space

- Peripheral clocks output on port pin

- Real-time counter clock output to port pin

- Event channels can be output on port pin

- Remapping of digital peripheral pin functions

- Selectable USART, SPI, and timer/counter input/output pin locations

#### 15.2 Overview

One port consists of up to eight port pins: pin 0 to 7. Each port pin can be configured as input or output with configurable driver and pull settings. They also implement synchronous and asynchronous input sensing with interrupts and events for selectable pin change conditions. Asynchronous pin-change sensing means that a pin change can wake the device from all sleep modes, included the modes where no clocks are running.

All functions are individual and configurable per pin, but several pins can be configured in a single operation. The pins have hardware read-modify-write (RMW) functionality for safe and correct change of drive value and/or pull resistor configuration. The direction of one port pin can be changed without unintentionally changing the direction of any other pin.

The port pin configuration also controls input and output selection of other device functions. It is possible to have both the peripheral clock and the real-time clock output to a port pin, and available for external use. The same applies to events from the event system that can be used to synchronize and control external functions. Other digital peripherals, such as USART, SPI, and timer/counters, can be remapped to selectable pin locations in order to optimize pin-out versus application needs.

The notation of the ports are PORTA, PORTB, PORTC, PORTD, PORTE, PORTF and PORTR.

#### **Output Driver** 15.3

All port pins (Pn) have programmable output configuration. The port pins also have configurable slew rate limitation to reduce electromagnetic emission.

### 15.3.1 Push-pull

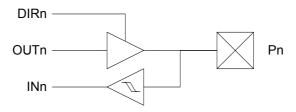

Figure 15-1. I/O configuration - Totem-pole.

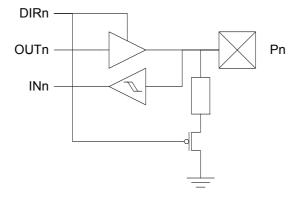

#### 15.3.2 Pull-down

I/O configuration - Totem-pole with pull-down (on input).

#### 15.3.3 Pull-up

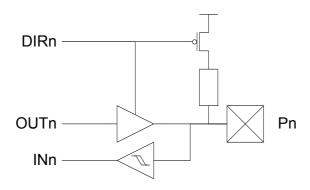

Figure 15-3. I/O configuration - Totem-pole with pull-up (on input).

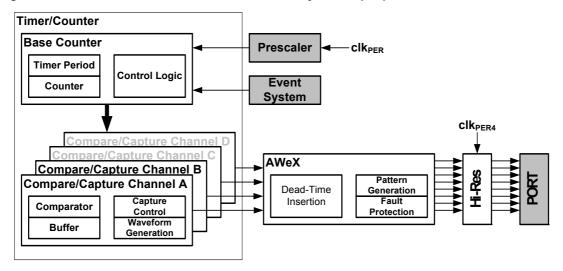

A timer/counter can be clocked and timed from the peripheral clock with optional prescaling or from the event system. The event system can also be used for direction control and capture trigger or to synchronize operations.

There are two differences between timer/counter type 0 and type 1. Timer/counter 0 has four CC channels, and timer/counter 1 has two CC channels. All information related to CC channels 3 and 4 is valid only for timer/counter 0. Only Timer/Counter 0 has the split mode feature that split it into two 8-bit Timer/Counters with four compare channels each.

Some timer/counters have extensions to enable more specialized waveform and frequency generation. The advanced waveform extension (AWeX) is intended for motor control and other power control applications. It enables low- and high-side output with dead-time insertion, as well as fault protection for disabling and shutting down external drivers. It can also generate a synchronized bit pattern across the port pins.

The advanced waveform extension can be enabled to provide extra and more advanced features for the Timer/Counter. This are only available for Timer/Counter 0. See "AWeX – Advanced Waveform Extension" on page 39 for more details.

The high-resolution (hi-res) extension can be used to increase the waveform output resolution by four or eight times by using an internal clock source running up to four times faster than the peripheral clock. See "Hi-Res – High Resolution Extension" on page 40 for more details.

Figure 16-1. Overview of a Timer/Counter and closely related peripherals.

PORTC, PORTD and PORTE each has one Timer/Counter 0 and one Timer/Counter1. PORTF has one Timer/Counter 0. Notation of these are TCC0 (Time/Counter C0), TCC1, TCD0, TCD1, TCE0, TCE1 and TCF0, respectively.

# 30. AC - Analog Comparator

#### 30.1 Features

- Four Analog Comparators (AC)

- Selectable propagation delay versus current consumption

- Selectable hysteresis

- No

- Small

- Large

- Analog comparator output available on pin

- Flexible input selection

- All pins on the port

- Output from the DAC

- Bandgap reference voltage

- A 64-level programmable voltage scaler of the internal AV<sub>CC</sub> voltage

- Interrupt and event generation on:

- Rising edge

- Falling edge

- Toggle

- Window function interrupt and event generation on:

- Signal above window

- Signal inside window

- Signal below window

- Constant current source with configurable output pin selection

#### 30.2 Overview

The analog comparator (AC) compares the voltage levels on two inputs and gives a digital output based on this comparison. The analog comparator may be configured to generate interrupt requests and/or events upon several different combinations of input change.

Two important properties of the analog comparator's dynamic behavior are: hysteresis and propagation delay. Both of these parameters may be adjusted in order to achieve the optimal operation for each application.

The input selection includes analog port pins, several internal signals, and a 64-level programmable voltage scaler. The analog comparator output state can also be output on a pin for use by external devices.

A constant current source can be enabled and output on a selectable pin. This can be used to replace, for example, external resistors used to charge capacitors in capacitive touch sensing applications.

The analog comparators are always grouped in pairs on each port. These are called analog comparator 0 (AC0) and analog comparator 1 (AC1). They have identical behavior, but separate control registers. Used as pair, they can be set in window mode to compare a signal to a voltage range instead of a voltage level.

PORTA and PORTB each has one AC pair. Notations are ACA and ACB, respectively.

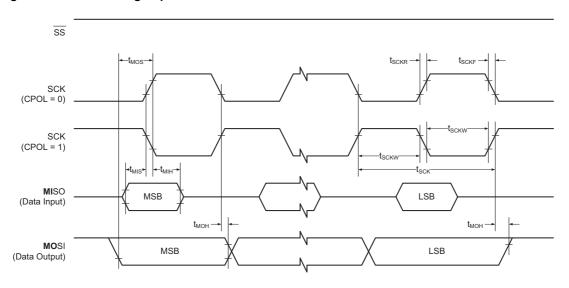

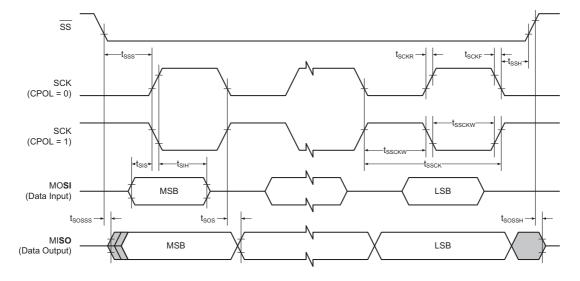

### 36.1.15 SPI Characteristics

Figure 36-5. SPI timing requirements in master mode.

Figure 36-6. SPI timing requirements in slave mode.

Table 36-60. External clock with prescaler <sup>(1)</sup>for system clock.

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units   |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|---------|

| 1 /4              | Clock Frequency (2)                               | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 90   | MHz     |

| 1/t <sub>CK</sub> | Clock Frequency C                                 | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 142  | IVII IZ |

| 4                 | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 11   |      |      | ns      |

| t <sub>CK</sub>   | CIOCK PERIOU                                      | V <sub>CC</sub> = 2.7 - 3.6V | 7    |      |      | 113     |

| 4                 | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 4.5  |      |      | ns      |

| t <sub>CH</sub>   | Clock High Time                                   | V <sub>CC</sub> = 2.7 - 3.6V | 2.4  |      |      | 115     |

|                   | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 4.5  |      |      | ns      |

| t <sub>CL</sub>   | Clock Low Time                                    | V <sub>CC</sub> = 2.7 - 3.6V | 2.4  |      |      |         |

| 4                 | Disa Tima (for maximum fraguancy)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  | ne      |

| t <sub>CR</sub>   | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  | – ns    |

| +                 | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  | ns      |

| t <sub>CF</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  | 115     |

| Δt <sub>CK</sub>  | Change in period from one clock cycle to the next |                              |      |      | 10   | %       |

Notes:

### 36.2.14.7 External 16MHz crystal oscillator and XOSC characteristics

Table 36-61. External 16MHz crystal oscillator and XOSC characteristics.

| Symbol | Parameter             | Condition  |                     | Min.       | Тур.   | Max. | Units |  |

|--------|-----------------------|------------|---------------------|------------|--------|------|-------|--|

|        | Cycle to cycle jitter | XOSCPWR=0  | FRQRANGE=0          |            | <10    |      |       |  |

|        |                       | AUSCHWR-U  | FRQRANGE=1, 2, or 3 |            | <1     |      | ns    |  |

|        |                       | XOSCPWR=1  |                     |            | <1     |      |       |  |

|        |                       | XOSCPWR=0  | FRQRANGE=0          |            | <6     |      |       |  |

|        | Long term jitter      | XUSCPVVR=U | FRQRANGE=1, 2, or 3 |            | <0.5   |      | ns    |  |

|        |                       | XOSCPWR=1  |                     |            | <0.5   |      |       |  |

|        | Frequency error       | XOSCPWR=0  |                     | FRQRANGE=0 |        | <0.1 |       |  |

|        |                       |            | FRQRANGE=1          |            | <0.05  |      | %     |  |

|        |                       |            | FRQRANGE=2 or 3     |            | <0.005 |      |       |  |

|        |                       | XOSCPWR=1  |                     |            | <0.005 |      |       |  |

|        |                       |            | FRQRANGE=0          |            | 40     |      |       |  |

|        | Duty cycle            | XOSCPWR=0  | FRQRANGE=1          |            | 42     |      | %     |  |

|        |                       |            | FRQRANGE=2 or 3     |            | 45     |      | 70    |  |

|        |                       | XOSCPWR=1  |                     |            | 48     |      |       |  |

<sup>1.</sup> System Clock Prescalers must be set so that maximum CPU clock frequency for device is not exceeded.

<sup>2.</sup> The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

## 36.4.3 Current consumption

Table 36-100. Current consumption for active mode and sleep modes.

| Symbol          | Parameter                    | Condition                                      |                        | Min. | Тур. | Max. | Units |

|-----------------|------------------------------|------------------------------------------------|------------------------|------|------|------|-------|

|                 |                              | 20kH= Evt Olk                                  | V <sub>CC</sub> = 1.8V |      | 60   |      |       |

|                 |                              | 32kHz, Ext. Clk                                | V <sub>CC</sub> = 3.0V |      | 140  |      |       |

|                 | Active Power consumption (1) | AMUL For Olle                                  | V <sub>CC</sub> = 1.8V |      | 280  |      | μА    |

|                 |                              | 1MHz, Ext. Clk                                 | V <sub>CC</sub> = 3.0V |      | 600  |      |       |

|                 |                              | OMILE For Oils                                 | V <sub>CC</sub> = 1.8V |      | 510  | 500  | _     |

|                 |                              | 2MHz, Ext. Clk                                 | \/ - 2 0\/             |      | 1.1  | 1.5  | m A   |

|                 |                              | 32MHz, Ext. Clk                                | V <sub>CC</sub> = 3.0V |      | 10.6 | 15   | mA    |

|                 |                              | 2011 - 5.4 011                                 | V <sub>CC</sub> = 1.8V |      | 4.3  |      |       |

|                 |                              | 32kHz, Ext. Clk                                | V <sub>CC</sub> = 3.0V |      | 4.8  |      | _     |

|                 |                              | ANNIE Trat Olle                                | V <sub>CC</sub> = 1.8V |      | 78   |      |       |

|                 | Idle Power consumption (1)   | 1MHz, Ext. Clk                                 | V <sub>CC</sub> = 3.0V |      | 150  |      | μΑ    |

|                 |                              | 2MHz, Ext. Clk                                 | V <sub>CC</sub> = 1.8V |      | 150  | 350  |       |

|                 |                              |                                                | \/ - 2.0\/             |      | 290  | 600  |       |

|                 |                              | 32MHz, Ext. Clk                                | V <sub>CC</sub> = 3.0V |      | 4.7  | 7.0  | mA    |

| I <sub>CC</sub> | Power-down power consumption | T = 25°C                                       |                        |      | 0.1  | 1.0  |       |

|                 |                              | T = 85°C                                       | V <sub>CC</sub> = 3.0V |      | 1.8  | 5.0  |       |

|                 |                              | T = 105°C                                      |                        |      | 6.5  | 17   |       |

|                 |                              | WDT and Sampled BOD enabled,<br>T = 25°C       | V <sub>CC</sub> = 3.0V |      | 1.3  | 3.0  | μА    |

|                 |                              | WDT and Sampled BOD enabled,<br>T = 85°C       |                        |      | 3.1  | 7.0  |       |

|                 |                              | WDT and Sampled BOD enabled,<br>T = 105°C      |                        |      | 7.3  | 20   |       |

|                 |                              | RTC from ULP clock, WDT and                    | V <sub>CC</sub> = 1.8V |      | 1.2  |      |       |

|                 |                              | sampled BOD enabled, T = 25°C                  | V <sub>CC</sub> = 3.0V |      | 1.3  |      |       |

|                 | Power-save power             | RTC from 1.024kHz low power                    | V <sub>CC</sub> = 1.8V |      | 0.6  | 2    |       |

|                 | consumption (2)              | 32.768kHz TOSC, T = 25°C                       | V <sub>CC</sub> = 3.0V |      | 0.7  | 2    | μΑ    |

|                 |                              | RTC from low power 32.768kHz<br>TOSC, T = 25°C | V <sub>CC</sub> = 1.8V |      | 0.8  | 3    |       |

|                 |                              |                                                | V <sub>CC</sub> = 3.0V |      | 1.0  | 3    |       |

|                 | Reset power consumption      | Current through RESET pin substracted          | V <sub>CC</sub> = 3.0V |      | 250  |      | μA    |

Notes:

<sup>2.</sup> Maximum limits are based on characterization, and not tested in production.

<sup>1.</sup> All Power Reduction Registers set.

### 36.4.14.3 Calibrated and tunable 32MHz internal oscillator characteristics

Table 36-120. 32MHz internal oscillator characteristics.

| Symbol | Parameter                    | Condition                                                    | Min. | Тур. | Max. | Units |

|--------|------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Frequency range              | DFLL can tune to this frequency over voltage and temperature | 30   |      | 55   | MHz   |

|        | Factory calibrated frequency |                                                              |      | 32   |      | MHz   |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V                             | -1.5 |      | 1.5  | %     |

|        | User calibration accuracy    |                                                              | -0.2 |      | 0.2  | %     |

|        | DFLL calibration step size   |                                                              |      | 0.23 |      | %     |

#### 36.4.14.4 32kHz Internal ULP Oscillator characteristics

Table 36-121. 32kHz internal ULP oscillator characteristics.

| Symbol | Parameter        | Condition | Min. | Тур. | Max. | Units |

|--------|------------------|-----------|------|------|------|-------|

|        | Output frequency |           |      | 32   |      | kHz   |

|        | Accuracy         |           | -30  |      | 30   | %     |

### 36.4.14.5 Internal Phase Locked Loop (PLL) characteristics

Table 36-122. Internal PLL characteristics.

| Symbo<br>I      | Parameter                             | Condition                                        | Min. | Тур. | Max. | Units  |

|-----------------|---------------------------------------|--------------------------------------------------|------|------|------|--------|

| f <sub>IN</sub> | Input Frequency                       | Output frequency must be within f <sub>OUT</sub> | 0.4  |      | 64   | MHz    |

| f Outo          | Output frequency (1)                  | V <sub>CC</sub> = 1.6 - 1.8V                     | 20   |      | 48   | MHz    |

| OUT             | f <sub>OUT</sub> Output frequency (1) | V <sub>CC</sub> = 2.7 - 3.6V                     | 20   |      | 128  | IVIIIZ |

|                 | Start-up time                         |                                                  |      | 25   |      | μs     |

|                 | Re-lock time                          |                                                  |      | 25   |      | μs     |

Note: 1. The maximum output frequency vs. supply voltage is linear between 1.8V and 2.7V, and can never be higher than four times the maximum CPU frequency.

| Symbol             | Parameter                       | Condition              |                                   | Min.          | Тур. | Max.                    | Units |

|--------------------|---------------------------------|------------------------|-----------------------------------|---------------|------|-------------------------|-------|

|                    |                                 | XOSCPWR=0,             | 0.4MHz resonator,<br>CL=100pF     | 2.4k          |      |                         |       |

|                    |                                 | FRQRANGE=0             | 1MHz crystal, CL=20pF             | 8.7k          |      |                         |       |

|                    |                                 |                        | 2MHz crystal, CL=20pF             | 2.1k          |      |                         |       |

|                    |                                 | XOSCPWR=0,             | 2MHz crystal                      | 4.2k          |      |                         |       |

|                    |                                 | FRQRANGE=1,            | 8MHz crystal                      | 250           |      |                         |       |

|                    |                                 | CL=20pF                | 9MHz crystal                      | 195           |      |                         |       |

|                    |                                 | XOSCPWR=0,             | 8MHz crystal                      | 360           |      |                         |       |

|                    |                                 | FRQRANGE=2,            | 9MHz crystal                      | 285           |      |                         |       |

|                    |                                 | CL=20pF                | 12MHz crystal                     | 155           |      |                         |       |

|                    |                                 | XOSCPWR=0,             | 9MHz crystal                      | 365           |      |                         |       |

|                    | Negative impedance              | FRQRANGE=3,            | 12MHz crystal                     | 200           |      |                         | Ω     |

| ·u                 | (1)                             | CL=20pF                | 16MHz crystal                     | 105           |      |                         | 32    |

|                    |                                 | XOSCPWR=1,             | 9MHz crystal                      | 435           |      |                         |       |

|                    |                                 | FRQRANGE=0,            | 12MHz crystal                     | 235           |      |                         |       |

|                    |                                 | CL=20pF                | 16MHz crystal                     | 125           |      |                         |       |

|                    |                                 | XOSCPWR=1,             | 9MHz crystal                      | 495           |      |                         |       |

|                    |                                 | FRQRANGE=1,            | FRQRANGE=1,                       | 12MHz crystal | 270  |                         |       |

|                    |                                 | CL=20pF                | 16MHz crystal                     | 145           |      |                         |       |

|                    |                                 | XOSCPWR=1,             | 12MHz crystal                     | 305           |      |                         |       |

|                    |                                 | FRQRANGE=2,<br>CL=20pF | 16MHz crystal                     | 160           |      |                         |       |

|                    |                                 | XOSCPWR=1,             | 12MHz crystal                     | 380           |      |                         |       |

|                    | FRQRANGE=3,<br>CL=20pF          | 16MHz crystal          | 205                               |               |      |                         |       |

|                    | ESR                             | SF = Safety factor     |                                   |               |      | min(R <sub>Q</sub> )/SF | kΩ    |

| C <sub>XTAL1</sub> | Parasitic capacitance XTAL1 pin |                        |                                   |               | 5.2  |                         | pF    |

| S <sub>XTAL2</sub> | Parasitic capacitance XTAL2 pin |                        |                                   |               | 6.8  |                         | pF    |

| C <sub>LOAD</sub>  | Parasitic capacitance load      |                        | ut quaranteed from design and cha |               | 2.95 |                         | pF    |

Note: 1. Numbers for negative impedance are not tested in production but guaranteed from design and characterization.

| Symbol              | Parameter                          | Condition                 | Min. | Тур. | Max. | Units |

|---------------------|------------------------------------|---------------------------|------|------|------|-------|

| 4                   | Set-up time for a repeated START   | $f_{SCL} \le 100 kHz$     | 4.7  |      |      |       |

| T <sub>SU;STA</sub> | condition                          | f <sub>SCL</sub> > 100kHz | 0.6  |      |      | μs    |

| 4                   | Data hold time                     | $f_{SCL} \le 100 kHz$     | 0    |      | 3.45 | LIC.  |

| <sup>t</sup> HD;DAT | t <sub>HD;DAT</sub> Data hold time | f <sub>SCL</sub> > 100kHz | 0    |      | 0.9  | μs    |

|                     | Data setup time                    | $f_{SCL} \le 100 kHz$     | 250  |      |      | ns    |

| t <sub>SU;DAT</sub> |                                    | f <sub>SCL</sub> > 100kHz | 100  |      |      |       |

| t                   | Setup time for STOP condition      | $f_{SCL} \le 100 kHz$     | 4.0  |      |      | μs    |

| t <sub>su;sto</sub> | Setup time for STOP condition      | f <sub>SCL</sub> > 100kHz | 0.6  |      |      | μο    |

| t <sub>BUF</sub>    | Bus free time between a STOP and   | $f_{SCL} \le 100 kHz$     | 4.7  |      |      | 116   |

|                     | START condition                    | f <sub>SCL</sub> > 100kHz | 1.3  |      |      | μs    |

Notes:

- Required only for f<sub>SCL</sub> > 100kHz.

C<sub>b</sub> = Capacitance of one bus line in pF.

f<sub>PER</sub> = Peripheral clock frequency.

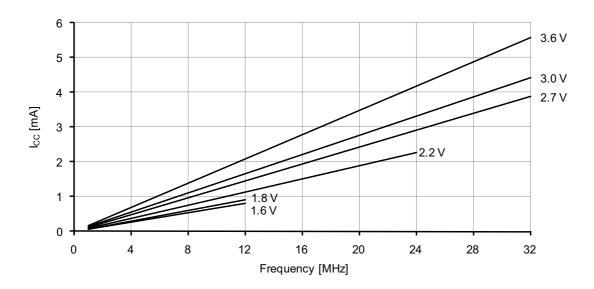

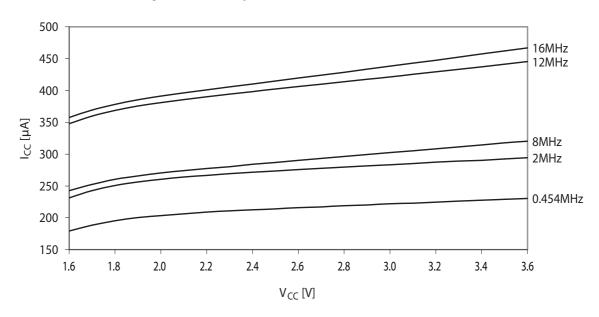

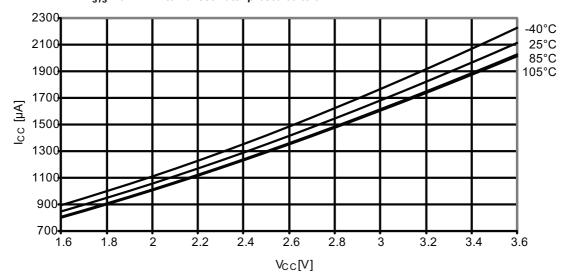

Figure 37-92. Idle mode supply current vs. frequency.  $f_{SYS} = 1 - 32MHz$  external clock, T = 25°C.

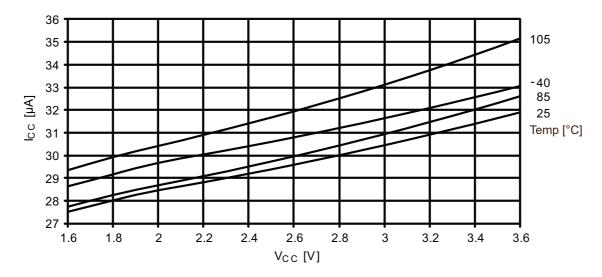

Figure 37-93. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 32.768kHz$  internal oscillator.

Figure 37-102. Standby supply current vs. V<sub>CC</sub>. 25°C, running from different crystal oscillators.

### 37.2.2 I/O Pin Characteristics

### 37.2.2.1 Pull-up

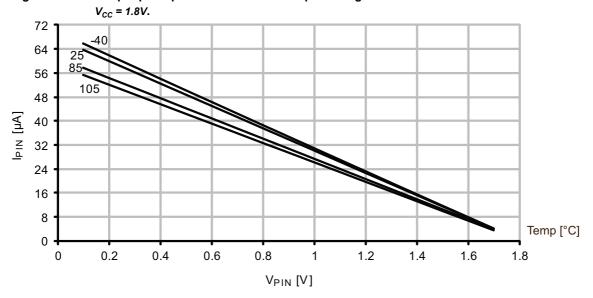

Figure 37-103. I/O pin pull-up resistor current vs. input voltage.

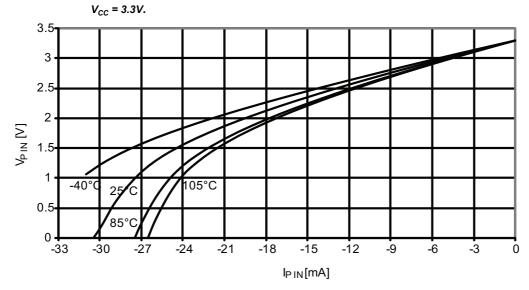

Figure 37-191. I/O pin output voltage vs. source current.

Figure 37-192. I/O pin output voltage vs. source current.

### 37.3.10 Oscillator Characteristics

### 37.3.10.1 Ultra Low-Power internal oscillator

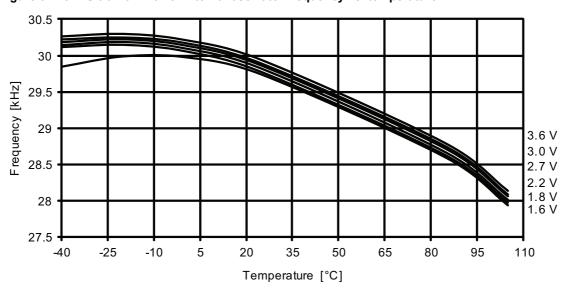

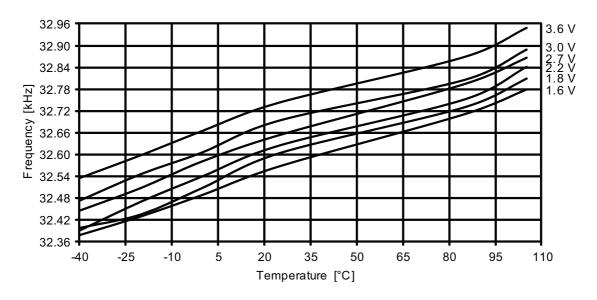

Figure 37-234. Ultra Low-Power internal oscillator frequency vs. temperature.

#### 37.3.10.2 32.768kHz Internal Oscillator

Figure 37-235. 32.768kHz internal oscillator frequency vs. temperature.

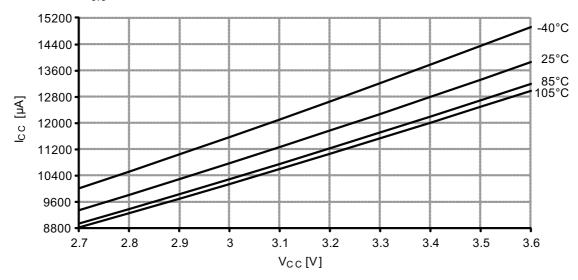

Figure 37-262. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 32MHz$  internal oscillator prescaled to 8MHz.

Figure 37-263. Idle mode current vs.  $V_{CC}$ .  $f_{SYS} = 32MHz$  internal oscillator.

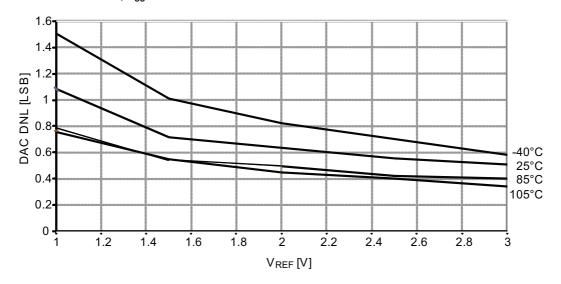

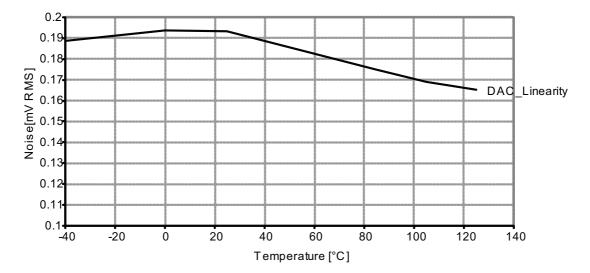

Figure 37-299. DAC noise vs. temperature.

$$V_{CC} = 3.0V$$

,  $V_{REF} = 2.4V$ .

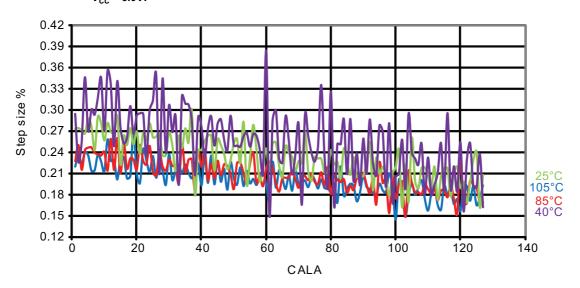

Figure 37-329. 48MHz internal oscillator CALA calibration step size.  $V_{\rm CC}$  = 3.0V.

### 37.4.11 Two-Wire Interface characteristics

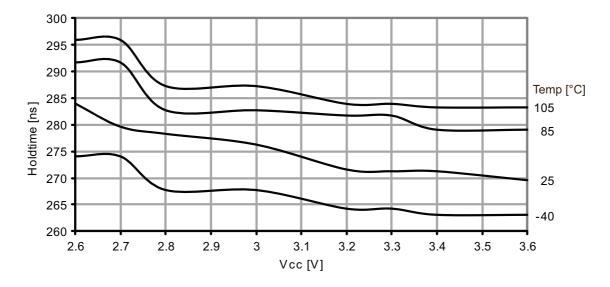

Figure 37-330. SDA hold time vs.  $V_{\text{CC}}$ .

## 38. Errata

### 38.1 ATxmega64A3U, ATxmega128A3U, ATxmega192A3U, ATxmega256A3U

#### 38.1.1 Rev. G

- The DAC Channel 1 has not been calibrated in the Xmega devices released prior to April 2012.

- AWeX fault protection restore is not done correct in Pattern Generation Mode.

#### 1. AWeX fault protection restore is not done correct in Pattern Generation Mode

When a fault is detected the OUTOVEN register is cleared, and when fault condition is cleared, OUTOVEN is restored according to the corresponding enabled DTI channels. For Common Waveform Channel Mode (CWCM), this has no effect as the OUTOVEN is correct after restoring from fault. For Pattern Generation Mode (PGM), OUTOVEN should instead have been restored according to the DTLSBUF register.

#### Problem fix/Workaround

Problem fix/Workaround

For CWCM no workaround is required.

For PGM in latched mode, disable the DTI channels before returning from the fault condition. Then, set correct OUTOVEN value and enable the DTI channels, before the direction (DIR) register is written to enable the correct outputs again.

For PGM in cycle-by-cycle mode there is no workaround.

#### 38.1.2 Rev. A-F

Not sampled.