Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                            |

|---------------------------|----------------------------------------------------------------------------|

| Product Status            | Active                                                                     |

| Core Processor            | AVR                                                                        |

| Core Size                 | 8/16-Bit                                                                   |

| Speed                     | 32MHz                                                                      |

| Connectivity              | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                               |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                 |

| Number of I/O             | 50                                                                         |

| Program Memory Size       | 256KB (128K x 16)                                                          |

| Program Memory Type       | FLASH                                                                      |

| EPROM Size                | 4K x 8                                                                     |

| AM Size                   | 16K x 8                                                                    |

| oltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                                |

| ata Converters            | A/D 16x12b; D/A 2x12b                                                      |

| scillator Type            | Internal                                                                   |

| perating Temperature      | -40°C ~ 105°C (TA)                                                         |

| lounting Type             | Surface Mount                                                              |

| ackage / Case             | 64-VFQFN Exposed Pad                                                       |

| upplier Device Package    | 64-QFN (9x9)                                                               |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/atxmega256a3u-m7 |

# 3. Overview

The Atmel AVR XMEGA is a family of low power, high performance, and peripheral rich 8/16-bit microcontrollers based on the AVR enhanced RISC architecture. By executing instructions in a single clock cycle, the AVR XMEGA device achieves throughputs CPU approaching one million instructions per second (MIPS) per megahertz, allowing the system designer to optimize power consumption versus processing speed.

The AVR CPU combines a rich instruction set with 32 general purpose working registers. All 32 registers are directly connected to the arithmetic logic unit (ALU), allowing two independent registers to be accessed in a single instruction, executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs many times faster than conventional single-accumulator or CISC based microcontrollers.

The AVR XMEGA A3U devices provide the following features: in-system programmable flash with read-while-write capabilities; internal EEPROM and SRAM; four-channel DMA controller, eight-channel event system and programmable multilevel interrupt controller, 50 general purpose I/O lines, 16-bit real-time counter (RTC); seven flexible, 16-bit timer/counters with compare and PWM channels; seven USARTs; two two-wire serial interfaces (TWIs); one full speed USB 2.0 interface; three serial peripheral interfaces (SPIs); AES and DES cryptographic engine; two 16-channel, 12-bit ADCs with programmable gain; one 2-channel 12-bit DAC; four analog comparators (ACs) with window mode; programmable watchdog timer with separate internal oscillator; accurate internal oscillators with PLL and prescaler; and programmable brown-out detection.

The program and debug interface (PDI), a fast, two-pin interface for programming and debugging, is available. The devices also have an IEEE std. 1149.1 compliant JTAG interface, and this can also be used for boundary scan, on-chip debug and programming.

The ATx devices have five software selectable power saving modes. The idle mode stops the CPU while allowing the SRAM, DMA controller, event system, interrupt controller, and all peripherals to continue functioning. The power-down mode saves the SRAM and register contents, but stops the oscillators, disabling all other functions until the next TWI, USB resume, or pin-change interrupt, or reset. In power-save mode, the asynchronous real-time counter continues to run, allowing the application to maintain a timer base while the rest of the device is sleeping. In standby mode, the external crystal oscillator keeps running while the rest of the device is sleeping. This allows very fast startup from the external crystal, combined with low power consumption. In extended standby mode, both the main oscillator and the asynchronous timer continue to run. To further reduce power consumption, the peripheral clock to each individual peripheral can optionally be stopped in active mode and idle sleep mode.

Atmel offers a free QTouch library for embedding capacitive touch buttons, sliders and wheels functionality into AVR microcontrollers.

The devices are manufactured using Atmel high-density, nonvolatile memory technology. The program flash memory can be reprogrammed in-system through the PDI or JTAG interfaces. A boot loader running in the device can use any interface to download the application program to the flash memory. The boot loader software in the boot flash section will continue to run while the application flash section is updated, providing true read-while-write operation. By combining an 8/16-bit RISC CPU with in-system, self-programmable flash, the AVR XMEGA is a powerful microcontroller family that provides a highly flexible and cost effective solution for many embedded applications.

All Atmel AVR XMEGA devices are supported with a full suite of program and system development tools, including C compilers, macro assemblers, program debugger/simulators, programmers, and evaluation kits.

MCU are the two-wire interface address match interrupt, asynchronous port interrupts, and the USB resume interrupt.

# 11.3.3 Power-save Mode

Power-save mode is identical to power down, with one exception. If the real-time counter (RTC) is enabled, it will keep running during sleep, and the device can also wake up from either an RTC overflow or compare match interrupt.

# 11.3.4 Standby Mode

Standby mode is identical to power down, with the exception that the enabled system clock sources are kept running while the CPU, peripheral, and RTC clocks are stopped. This reduces the wake-up time.

# 11.3.5 Extended Standby Mode

Extended standby mode is identical to power-save mode, with the exception that the enabled system clock sources are kept running while the CPU and peripheral clocks are stopped. This reduces the wake-up time.

# 31. Programming and Debugging

#### 31.1 Features

- Programming

- External programming through PDI or JTAG interfaces

- Minimal protocol overhead for fast operation

- Built-in error detection and handling for reliable operation

- Boot loader support for programming through any communication interface

- Debugging

- Nonintrusive, real-time, on-chip debug system

- No software or hardware resources required from device except pin connection

- Program flow control

- Go, Stop, Reset, Step Into, Step Over, Step Out, Run-to-Cursor

- Unlimited number of user program breakpoints

- Unlimited number of user data breakpoints, break on:

- Data location read, write, or both read and write

- Data location content equal or not equal to a value

- Data location content is greater or smaller than a value

- Data location content is within or outside a range

- No limitation on device clock frequency

- Program and Debug Interface (PDI)

- Two-pin interface for external programming and debugging

- Uses the Reset pin and a dedicated pin

- No I/O pins required during programming or debugging

- JTAG interface

- Four-pin, IEEE Std. 1149.1 compliant interface for programming and debugging

- Boundary scan capabilities according to IEEE Std. 1149.1 (JTAG)

## 31.2 Overview

The Program and Debug Interface (PDI) is an Atmel proprietary interface for external programming and on-chip debugging of a device.

The PDI supports fast programming of nonvolatile memory (NVM) spaces; flash, EEPOM, fuses, lock bits, and the user signature row.

Debug is supported through an on-chip debug system that offers nonintrusive, real-time debug. It does not require any software or hardware resources except for the device pin connection. Using the Atmel tool chain, it offers complete program flow control and support for an unlimited number of program and complex data breakpoints. Application debug can be done from a C or other high-level language source code level, as well as from an assembler and disassembler level.

Programming and debugging can be done through two physical interfaces. The primary one is the PDI physical layer, which is available on all devices. This is a two-pin interface that uses the Reset pin for the clock input (PDI\_CLK) and one other dedicated pin for data input and output (PDI\_DATA). A JTAG interface is also available on most devices, and this can be used for programming and debugging through the four-pin JTAG interface. The JTAG interface is IEEE Std. 1149.1 compliant, and supports boundary scan. Any external programmer or on-chip debugger/emulator can be directly connected to either of these interfaces. Unless otherwise stated, all references to the PDI assume access through the PDI physical layer.

| Symbol | Parameter                    | Condition             |                                   | Min. | Тур. | Max. | Units     |

|--------|------------------------------|-----------------------|-----------------------------------|------|------|------|-----------|

|        | Offset Error, input referred | 1x gain, normal mode  |                                   |      | -2   |      |           |

|        |                              | 8x gain, normal mode  |                                   |      | -5   |      | mV        |

|        |                              | 64x gain, normal mode |                                   |      | -4   |      |           |

|        | Noise                        | 1x gain, normal mode  | .,                                |      | 0.5  |      |           |

|        |                              | 8x gain, normal mode  | $V_{CC} = 3.6V$<br>Ext. $V_{REF}$ |      | 1.5  |      | mV<br>rms |

|        |                              | 64x gain, normal mode | □Λι. ▼REF                         |      | 11   |      |           |

Note:

1. Maximum numbers are based on characterisation and not tested in production, and valid for 5% to 95% input voltage range.

## 36.1.7 DAC Characteristics

Table 36-12. Power supply, reference and output range.

| Symbol               | Parameter                   | Condition                               | Min.                  | Тур. | Max.                   | Units |

|----------------------|-----------------------------|-----------------------------------------|-----------------------|------|------------------------|-------|

| AV <sub>CC</sub>     | Analog supply voltage       |                                         | V <sub>CC</sub> - 0.3 |      | V <sub>CC</sub> + 0.3  |       |

| AV <sub>REF</sub>    | External reference voltage  |                                         | 1.0                   |      | V <sub>CC</sub> - 0.6  | V     |

| R <sub>channel</sub> | DC output impedance         |                                         |                       |      | 50                     | Ω     |

|                      | Linear output voltage range |                                         | 0.15                  |      | AV <sub>CC</sub> -0.15 | V     |

| R <sub>AREF</sub>    | Reference input resistance  |                                         |                       | >10  |                        | ΜΩ    |

| CAREF                | Reference input capacitance | Static load                             |                       | 7    |                        | pF    |

|                      | Minimum Resistance load     |                                         | 1                     |      |                        | kΩ    |

|                      | Maximum capacitance load    |                                         |                       |      | 100                    | pF    |

|                      | Maximum capacitance load    | 1000 $Ω$ serial resistance              |                       |      | 1                      | nF    |

|                      | Output sink/source          | Operating within accuracy specification |                       |      | AV <sub>CC</sub> /1000 | A     |

|                      | Output sillivisource        | Safe operation                          |                       |      | 10                     | mA    |

Table 36-13. Clock and timing.

| Symbol                           | Parameter                                   | Condition      |   | Min. | Тур. | Max. | Units |

|----------------------------------|---------------------------------------------|----------------|---|------|------|------|-------|

| f                                | f Conversion rate C <sub>load</sub> =100pF, | Normal mode    | 0 |      | 1000 | kono |       |

| f <sub>DAC</sub> Conversion rate | maximum step size                           | Low power mode | 0 |      | 500  | ksps |       |

# 36.1.11 External Reset Characteristics

Table 36-18. External reset characteristics.

| Symbol           | Parameter                                  | Condition                    | Min. | Тур.                 | Max. | Units |

|------------------|--------------------------------------------|------------------------------|------|----------------------|------|-------|

| t <sub>EXT</sub> | Minimum reset pulse width                  |                              |      | 95                   | 1000 | ns    |

|                  | Reset threshold voltage (V <sub>IH</sub> ) | V <sub>CC</sub> = 2.7 - 3.6V |      | 0.60*V <sub>CC</sub> |      |       |

| V                |                                            | V <sub>CC</sub> = 1.6 - 2.7V |      | 0.70*V <sub>CC</sub> |      | V     |

| V <sub>RST</sub> | Reset threshold voltage (V <sub>IL</sub> ) | V <sub>CC</sub> = 2.7 - 3.6V |      | 0.40*V <sub>CC</sub> |      |       |

|                  |                                            | V <sub>CC</sub> = 1.6 - 2.7V |      | 0.30*V <sub>CC</sub> |      |       |

| R <sub>RST</sub> | Reset pin Pull-up Resistor                 |                              |      | 25                   |      | kΩ    |

## 36.1.12 Power-on Reset Characteristics

Table 36-19. Power-on reset characteristics.

| Symbol                | Parameter                                     | Condition                                | Min. | Тур. | Max. | Units |

|-----------------------|-----------------------------------------------|------------------------------------------|------|------|------|-------|

| V <sub>POT-</sub> (1) | POR threshold voltage falling V <sub>CC</sub> | V <sub>CC</sub> falls faster than 1V/ms  | 0.4  | 1.0  |      | V     |

|                       |                                               | V <sub>CC</sub> falls at 1V/ms or slower | 0.8  | 1.0  |      |       |

| V <sub>POT+</sub>     | POR threshold voltage rising V <sub>CC</sub>  |                                          |      | 1.3  | 1.59 | V     |

Note: 1.  $V_{POT-}$  values are only valid when BOD is disabled. When BOD is enabled  $V_{POT-} = V_{POT+}$

# 36.1.13 Flash and EEPROM Memory Characteristics

Table 36-20. Endurance and data retention.

| Symbol | Parameter | Condition          |                | Min. | Тур. | Max. | Units |      |

|--------|-----------|--------------------|----------------|------|------|------|-------|------|

|        |           |                    | 25°C           | 10K  |      |      |       |      |

|        |           | Write/Erase cycles | 85°C           | 10K  |      |      | Cycle |      |

| Flash  | Elach     |                    | 105°C          | 2K   |      |      |       |      |

|        | riasii    |                    | 25°C           | 100  |      |      |       |      |

|        |           | Data               | Data retention | 85°C | 25   |      |       | Year |

|        |           |                    | 105°C          | 10   |      |      |       |      |

|        |           |                    | 25°C           | 100K |      |      |       |      |

|        |           | Write/Erase cycles | 85°C           | 100K |      |      | Cycle |      |

|        | EEPROM    |                    | 105°C          | 30K  |      |      |       |      |

|        | LLI NOW   | Data retention     | 25°C           | 100  |      |      |       |      |

|        |           |                    | 85°C           | 25   |      |      | Year  |      |

|        |           |                    | 105°C          | 10   |      |      |       |      |

# 36.1.14.6 External clock characteristics

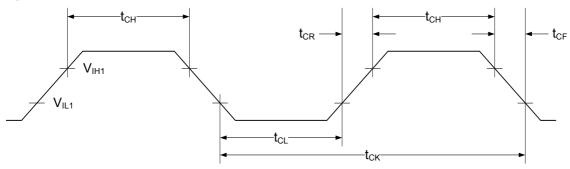

Figure 36-3. External clock drive waveform

Table 36-27. External clock used as system clock without prescaling.

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units   |  |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|---------|--|

| 1 /+              | Clock Frequency (1)                               | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 12   | MHz     |  |

| 1/t <sub>CK</sub> | Clock Frequency V                                 | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 32   | IVII IZ |  |

| 4                 | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 83.3 |      |      | ns      |  |

| t <sub>CK</sub>   | CIOCK P GIIOU                                     | V <sub>CC</sub> = 2.7 - 3.6V | 31.5 |      |      | 115     |  |

| +                 | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | ns      |  |

| t <sub>CH</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | 113     |  |

| 4                 | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 30.0 |      |      | ns      |  |

| t <sub>CL</sub>   |                                                   | V <sub>CC</sub> = 2.7 - 3.6V | 12.5 |      |      | 115     |  |

| +                 | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   | ns      |  |

| t <sub>CR</sub>   | ruse time (to maximum nequency)                   | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    | 115     |  |

| +                 | Fall Time (for recycles as from the state)        | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 10   | ne      |  |

| t <sub>CF</sub>   | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 3    | ns      |  |

| $\Delta t_{CK}$   | Change in period from one clock cycle to the next |                              |      |      | 10   | %       |  |

Note: 1. The maximum frequency vs. supply voltage is linear between 1.8V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

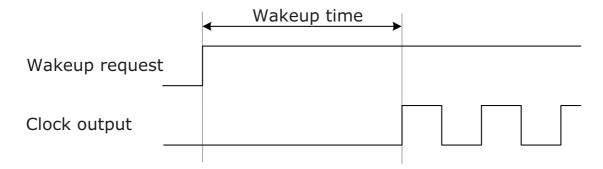

# 36.2.4 Wake-up time from sleep modes

Table 36-38. Device wake-up time from sleep modes with various system clock sources.

| Symbol              | Parameter                          | Condition                     | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|---------------------|------------------------------------|-------------------------------|------|---------------------|------|-------|

|                     |                                    | External 2MHz clock           |      | 2                   |      |       |

|                     | Standby, and Extended Standby mode | 32.768kHz internal oscillator |      | 120                 |      |       |

|                     |                                    | 2MHz internal oscillator      |      | 2                   |      | μs    |

|                     |                                    | 32MHz internal oscillator     |      | 0.2                 |      |       |

| <sup>L</sup> wakeup |                                    | External 2MHz clock           |      | 4.5                 |      |       |

|                     | Wake-up time from Power-save       | 32.768kHz internal oscillator |      | 320                 |      |       |

|                     | and Power-down mode                | 2MHz internal oscillator      |      | 9                   |      | μs    |

|                     |                                    | 32MHz internal oscillator     |      | 5                   |      |       |

The wake-up time is the time from the wake-up request is given until the peripheral clock is available on pin, see Figure 36-2. All peripherals and modules start execution from the first clock cycle, expect the CPU that is halted for four clock cycles before program execution starts.

Figure 36-9. Wake-up time definition.

Note:

Table 36-53. Programming time.

| Symbol | Parameter         | Condition                                         | Min. | Typ. <sup>(1)</sup> | Max. | Units |

|--------|-------------------|---------------------------------------------------|------|---------------------|------|-------|

|        | Chip Erase        | 128KB Flash, EEPROM <sup>(2)</sup> and SRAM Erase |      | 75                  |      | ms    |

|        | Application Erase | Section erase                                     |      | 6                   |      | ms    |

|        |                   | Page Erase                                        |      | 4                   |      |       |

|        | Flash             | Page Write                                        |      | 4                   |      | ms    |

|        |                   | Atomic Page Erase and Write                       |      | 8                   |      |       |

|        |                   | Page Erase                                        |      | 4                   |      |       |

|        | EEPROM            | Page Write                                        |      | 4                   |      | ms    |

|        |                   | Atomic Page Erase and Write                       |      | 8                   |      |       |

Notes:

#### 36.2.14 Clock and Oscillator Characteristics

#### 36.2.14.1 Calibrated 32.768kHz Internal Oscillator characteristics

Table 36-54. 32.768kHz internal oscillator characteristics.

| Symbol | Parameter                    | Condition                        | Min. | Тур.   | Max. | Units |

|--------|------------------------------|----------------------------------|------|--------|------|-------|

|        | Frequency                    |                                  |      | 32.768 |      | kHz   |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V | -0.5 |        | 0.5  | %     |

|        | User calibration accuracy    |                                  | -0.5 |        | 0.5  | %     |

#### 36.2.14.2 Calibrated 2MHz RC Internal Oscillator characteristics

Table 36-55. 2MHz internal oscillator characteristics.

| Symbol | Parameter                    | Condition                                                    | Min. | Тур. | Max. | Units |

|--------|------------------------------|--------------------------------------------------------------|------|------|------|-------|

|        | Frequency range              | DFLL can tune to this frequency over voltage and temperature | 1.8  |      | 2.2  | MHz   |

|        | Factory calibrated frequency |                                                              |      | 2.0  |      | MHz   |

|        | Factory calibration accuracy | T = 85°C, V <sub>CC</sub> = 3.0V                             | -1.5 |      | 1.5  | %     |

|        | User calibration accuracy    |                                                              | -0.2 |      | 0.2  | %     |

|        | DFLL calibration stepsize    |                                                              |      | 0.22 |      | %     |

<sup>1.</sup> Programming is timed from the 2MHz internal oscillator.

<sup>2.</sup> EEPROM is not erased if the EESAVE fuse is programmed.

| Symbol             | Parameter               | Condition                       | Min.      | Тур. | Max. | Units |     |

|--------------------|-------------------------|---------------------------------|-----------|------|------|-------|-----|

| t <sub>delay</sub> | Propagation delay       | V <sub>CC</sub> = 3.0V, T= 85°C | mode = HS |      | 30   | 90    |     |

|                    |                         | mode = HS                       |           |      | 30   |       | no  |

|                    |                         | V <sub>CC</sub> = 3.0V, T= 85°C | mode = LP |      | 130  | 500   | ns  |

|                    |                         | mode = LP                       |           |      | 130  |       |     |

|                    | 64-Level Voltage Scaler | Integral non-linearity (INL)    |           |      | 0.3  | 0.5   | Isb |

# 36.3.9 Bandgap and Internal 1.0V Reference Characteristics

Table 36-80. Bandgap and Internal 1.0V reference characteristics.

| Symbol | Parameter                              | Condition                                   | Min.                         | Тур. | Max. | Units |  |

|--------|----------------------------------------|---------------------------------------------|------------------------------|------|------|-------|--|

|        | Startus time                           | As reference for ADC or DAC                 | 1 Clk <sub>PER</sub> + 2.5µs |      |      |       |  |

|        | Startup time                           | As input voltage to ADC and AC              |                              | 1.5  |      | μs    |  |

|        | Bandgap voltage                        |                                             |                              | 1.1  |      | V     |  |

| INT1V  | Internal 1.00V reference               | T= 85°C, after calibration                  | 0.99                         | 1    | 1.01 | mV    |  |

|        | Variation over voltage and temperature | Relative to T= 85°C, V <sub>CC</sub> = 3.0V |                              | ±1.0 |      | %     |  |

## 36.3.10 Brownout Detection Characteristics

Table 36-81. Brownout detection characteristics.

| Symbol            | Parameter                           | Condition       | Min. | Тур. | Max. | Units |  |  |

|-------------------|-------------------------------------|-----------------|------|------|------|-------|--|--|

| V <sub>BOT</sub>  | BOD level 0 falling V <sub>CC</sub> |                 | 1.60 | 1.62 | 1.72 |       |  |  |

|                   | BOD level 1 falling V <sub>CC</sub> |                 |      | 1.8  |      |       |  |  |

|                   | BOD level 2 falling V <sub>CC</sub> |                 |      | 2.0  |      |       |  |  |

|                   | BOD level 3 falling V <sub>CC</sub> |                 |      | 2.2  |      | V     |  |  |

|                   | BOD level 4 falling V <sub>CC</sub> |                 |      | 2.4  |      | V     |  |  |

|                   | BOD level 5 falling V <sub>CC</sub> |                 |      | 2.6  |      |       |  |  |

|                   | BOD level 6 falling V <sub>CC</sub> |                 |      | 2.8  |      |       |  |  |

|                   | BOD level 7 falling V <sub>CC</sub> |                 |      | 3.0  |      |       |  |  |

| ŧ                 | Detection time                      | Continuous mode |      | 0.4  |      | 110   |  |  |

| t <sub>BOD</sub>  |                                     | Sampled mode    |      | 1000 |      | μs    |  |  |

| V <sub>HYST</sub> | Hysteresis                          |                 |      | 1.6  |      | %     |  |  |

Table 36-101. Current consumption for modules and peripherals.

| Symbol          | Parameter                           | Condition <sup>(1)</sup>                                        | Min.               | Тур. | Max. | Units |      |

|-----------------|-------------------------------------|-----------------------------------------------------------------|--------------------|------|------|-------|------|

|                 | ULP oscillator                      |                                                                 |                    |      | 1.0  |       | μA   |

|                 | 32.768kHz int. oscillator           |                                                                 |                    |      | 27   |       | μA   |

|                 | 2MHz int. oscillator                |                                                                 |                    | 85   |      | μA    |      |

|                 |                                     | DFLL enabled with 32.768kHz int. osc. as reference              |                    |      | 115  |       |      |

|                 | 32MHz int. oscillator               |                                                                 |                    |      | 270  |       | μA   |

|                 |                                     | DFLL enabled with 32.768kHz int. osc. as reference              |                    |      | 460  |       | μΑ   |

|                 | PLL                                 | 20x multiplication factor,<br>32MHz int. osc. DIV4 as reference |                    |      | 220  |       | μA   |

|                 | Watchdog Timer                      |                                                                 |                    |      | 1    |       | μA   |

|                 | BOD                                 | Continuous mode                                                 |                    |      | 138  |       | μA   |

|                 |                                     | Sampled mode, includes ULP oscillator                           |                    |      | 1.2  |       | μΑ   |

|                 | Internal 1.0V reference             |                                                                 |                    |      | 100  |       | μA   |

| I <sub>CC</sub> | Temperature sensor                  |                                                                 |                    |      | 95   |       | μA   |

|                 | ADC                                 | 250ksps<br>V <sub>REF</sub> = Ext ref                           |                    |      | 3.0  |       |      |

|                 |                                     |                                                                 | CURRLIMIT = LOW    |      | 2.6  |       | mA   |

|                 |                                     |                                                                 | CURRLIMIT = MEDIUM |      | 2.1  |       |      |

|                 |                                     |                                                                 | CURRLIMIT = HIGH   |      | 1.6  |       |      |

|                 | DAC                                 | 250ksps<br>V <sub>REF</sub> = Ext ref<br>No load                | Normal mode        |      | 1.9  |       | mA   |

|                 |                                     |                                                                 | Low Power mode     |      | 1.1  |       | IIIA |

|                 | 40                                  | High Speed Mode                                                 |                    |      | 330  |       |      |

|                 | AC Low Power Mode                   |                                                                 |                    |      | 130  |       | μA   |

|                 | DMA                                 | 615KBps between I/O registers and SRAM                          |                    |      | 115  |       | μA   |

|                 | Timer/Counter                       |                                                                 |                    |      | 16   |       | μA   |

|                 | USART                               | Rx and Tx enabled, 9600 BAUD                                    |                    |      | 2.5  |       | μA   |

|                 | Flash memory and EEPROM programming |                                                                 |                    |      | 4    |       | mA   |

Note:

All parameters measured as the difference in current consumption between module enabled and disabled. All data at  $V_{CC}$  = 3.0V,  $Clk_{SYS}$  = 1MHz external clock without prescaling, T = 25°C unless other conditions are givenAll parameters measured as the difference in current consumption between module enabled and disabled. All data at  $V_{CC}$  = 3.0V,  $Clk_{SYS}$  = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

# 37. Typical Characteristics

# 37.1 ATxmega64A3U

# 37.1.1 Current consumption

# 37.1.1.1 Active mode supply current

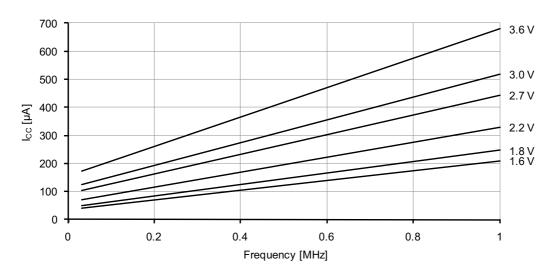

Figure 37-1. Active supply current vs. frequency.  $f_{SYS} = 0$  - 1MHz external clock, T = 25°C.

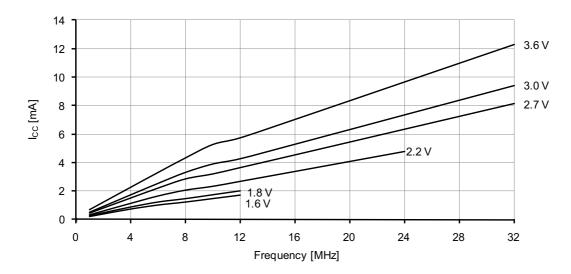

Figure 37-2. Active supply current vs. frequency.  $f_{SYS} = 1 - 32MHz$  external clock,  $T = 25^{\circ}C$ .

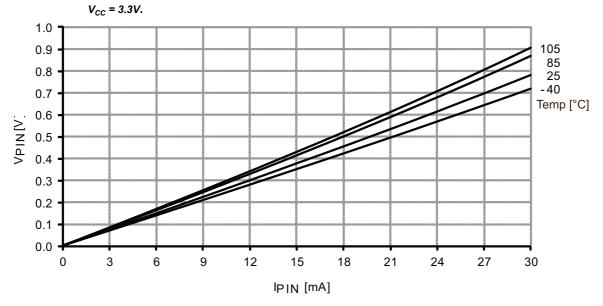

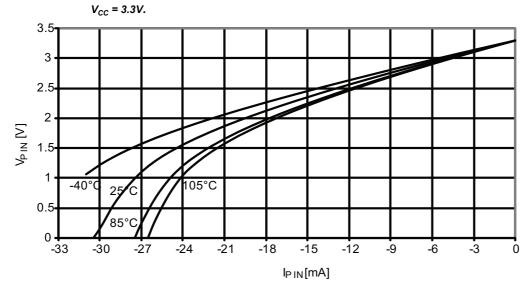

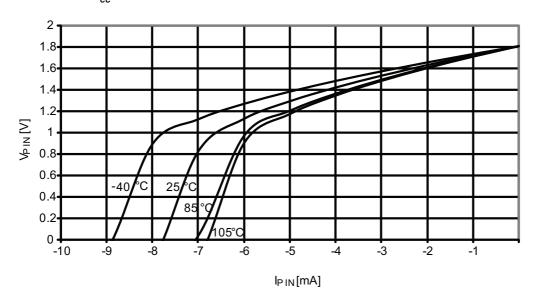

Figure 37-29. I/O pin output voltage vs. sink current.

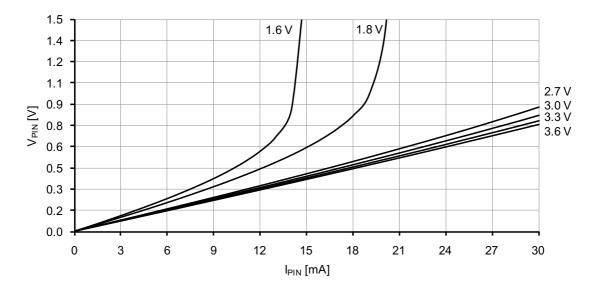

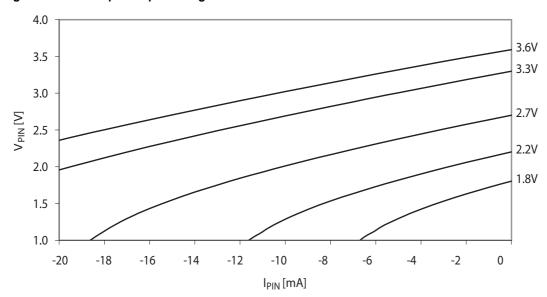

Figure 37-30. I/O pin output voltage vs. sink current.

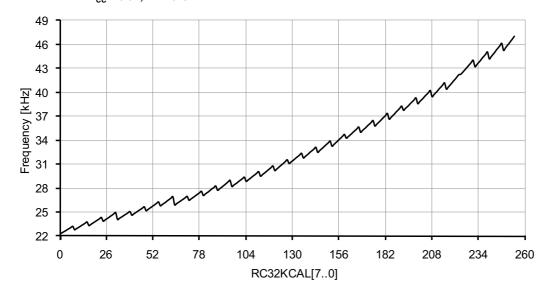

Figure 37-70. 32.768kHz internal oscillator frequency vs. calibration value.  $V_{CC}=3.0V,\,T=25^{\circ}\text{C}.$

## 37.1.10.3 2MHz Internal Oscillator

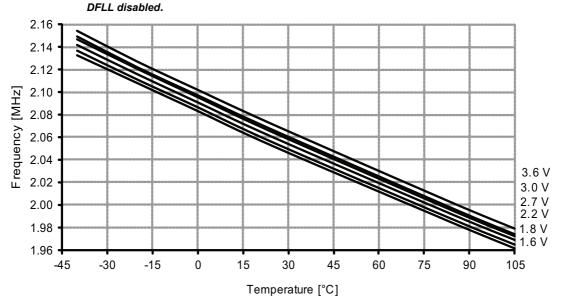

Figure 37-71. 2MHz internal oscillator frequency vs. temperature.

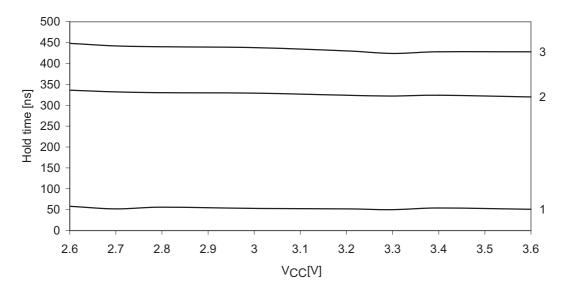

Figure 37-82. SDA hold time vs. supply voltage.

## 37.1.12 PDI characteristics

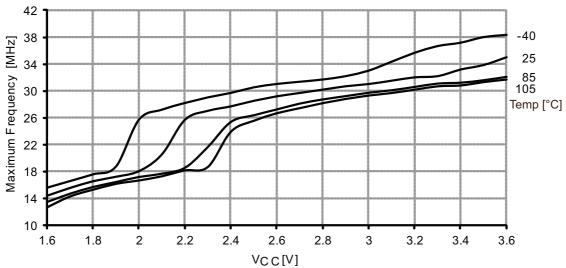

Figure 37-83. Maximum PDI frequency vs. V<sub>CC</sub>.

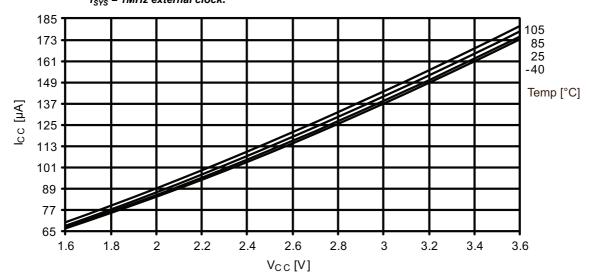

Figure 37-94. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 1MHz$  external clock.

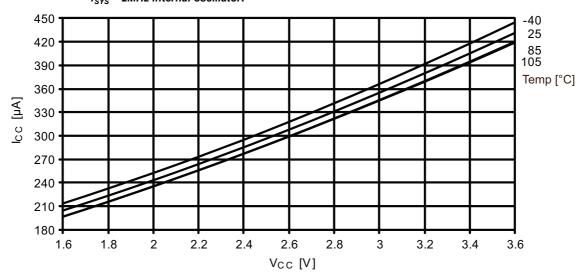

Figure 37-95. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 2MHz$  internal oscillator.

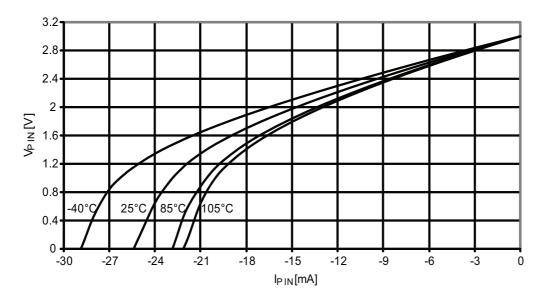

Figure 37-191. I/O pin output voltage vs. source current.

Figure 37-192. I/O pin output voltage vs. source current.

# 37.3.2.3 Thresholds and Hysteresis

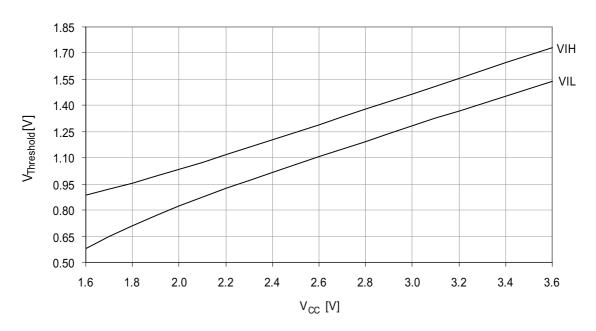

Figure 37-197. I/O pin input threshold voltage vs.  $V_{CC.}$  $T = 25^{\circ}C.$

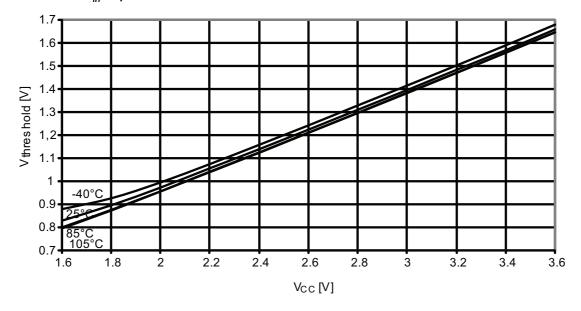

Figure 37-198. I/O pin input threshold voltage vs.  $V_{\rm CC}$ .  $V_{\rm IH}$  I/O pin read as "1".

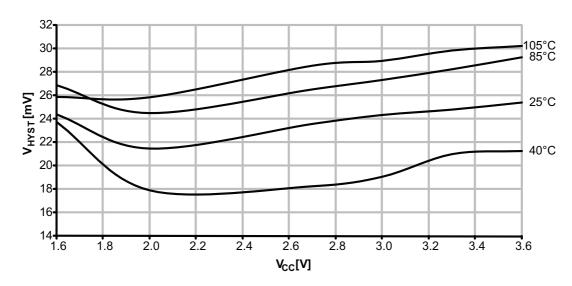

Figure 37-219. Analog comparator hysteresis vs. V<sub>CC</sub>. *High-speed mode, large hysteresis*.

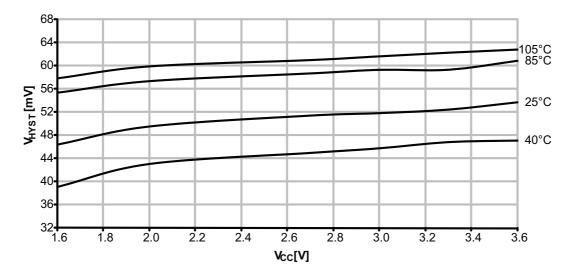

Figure 37-220. Analog comparator hysteresis vs.  $V_{CC}$ . Low power, large hysteresis.

# 37.4.2.2 Output Voltage vs. Sink/Source Current

Figure 37-272. I/O pin output voltage vs. source current.  $V_{\rm CC}$  = 1.8V.

Figure 37-273. I/O pin output voltage vs. source current.  $V_{\rm CC}$  = 3.0V.

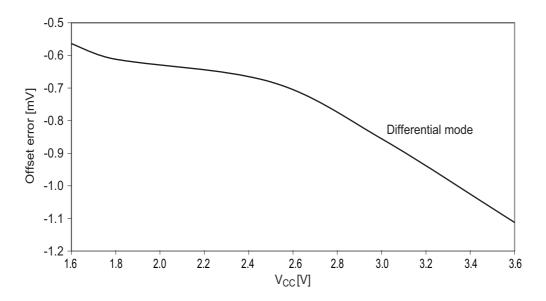

Figure 37-294. Offset error vs.  $V_{CC}$ .  $T = 25 \, ^{\circ}C$ ,  $V_{REF} = external \ 1.0V$ , ADC sampling speed = 500ksps.

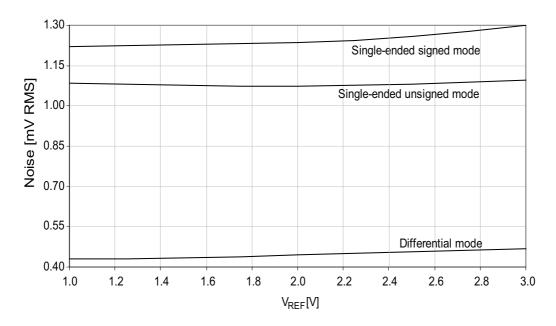

Figure 37-295. Noise vs.  $V_{REF}$ .  $T = 25\, {\rm C}, \ V_{CC} = 3.6 V, \ ADC \ sampling \ speed = 500 ksps.$