Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | AVR                                                                       |

| Core Size                  | 8/16-Bit                                                                  |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART, USB                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                |

| Number of I/O              | 50                                                                        |

| Program Memory Size        | 64KB (32K x 16)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 4K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 3.6V                                                               |

| Data Converters            | A/D 16x12b; D/A 2x12b                                                     |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 64-TQFP                                                                   |

| Supplier Device Package    | 64-TQFP (14x14)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/atxmega64a3u-an |

MCU are the two-wire interface address match interrupt, asynchronous port interrupts, and the USB resume interrupt.

# 11.3.3 Power-save Mode

Power-save mode is identical to power down, with one exception. If the real-time counter (RTC) is enabled, it will keep running during sleep, and the device can also wake up from either an RTC overflow or compare match interrupt.

# 11.3.4 Standby Mode

Standby mode is identical to power down, with the exception that the enabled system clock sources are kept running while the CPU, peripheral, and RTC clocks are stopped. This reduces the wake-up time.

# 11.3.5 Extended Standby Mode

Extended standby mode is identical to power-save mode, with the exception that the enabled system clock sources are kept running while the CPU and peripheral clocks are stopped. This reduces the wake-up time.

# 16. TC0/1 - 16-bit Timer/Counter Type 0 and 1

#### 16.1 Features

- Seven 16-bit timer/counters

- Four timer/counters of type 0

- Three timer/counters of type 1

- Split-mode enabling two 8-bit timer/counter from each timer/counter type 0

- 32-bit Timer/Counter support by cascading two timer/counters

- Up to four compare or capture (CC) channels

- Four CC channels for timer/counters of type 0

- Two CC channels for timer/counters of type 1

- Double buffered timer period setting

- Double buffered capture or compare channels

- Waveform generation:

- Frequency generation

- Single-slope pulse width modulation

- Dual-slope pulse width modulation

- Input capture:

- Input capture with noise cancelling

- Frequency capture

- Pulse width capture

- 32-bit input capture

- Timer overflow and error interrupts/events

- One compare match or input capture interrupt/event per CC channel

- Can be used with event system for:

- Quadrature decoding

- Count and direction control

- Capture

- Can be used with DMA and to trigger DMA transactions

- High-resolution extension

- Increases frequency and waveform resolution by 4x (2-bit) or 8x (3-bit)

- Advanced waveform extension:

- Low- and high-side output with programmable dead-time insertion (DTI)

- Event controlled fault protection for safe disabling of drivers

#### 16.2 Overview

Atmel AVR XMEGA devices have a set of seven flexible 16-bit Timer/Counters (TC). Their capabilities include accurate program execution timing, frequency and waveform generation, and input capture with time and frequency measurement of digital signals. Two timer/counters can be cascaded to create a 32-bit timer/counter with optional 32-bit capture.

A timer/counter consists of a base counter and a set of compare or capture (CC) channels. The base counter can be used to count clock cycles or events. It has direction control and period setting that can be used for timing. The CC channels can be used together with the base counter to do compare match control, frequency generation, and pulse width waveform modulation, as well as various input capture operations. A timer/counter can be configured for either capture or compare functions, but cannot perform both at the same time.

# 32. Pinout and Pin Functions

The device pinout is shown in "Pinout/Block Diagram" on page 5. In addition to general purpose I/O functionality, each pin can have several alternate functions. This will depend on which peripheral is enabled and connected to the actual pin. Only one of the pin functions can be used at time.

# 32.1 Alternate Pin Function Description

The tables below show the notation for all pin functions available and describe its function.

# 32.1.1 Operation/Power Supply

| V <sub>CC</sub>  | Digital supply voltage |

|------------------|------------------------|

| AV <sub>CC</sub> | Analog supply voltage  |

| GND              | Ground                 |

#### 32.1.2 Port Interrupt functions

| SYNC  | Port pin with full synchronous and limited asynchronous interrupt function |

|-------|----------------------------------------------------------------------------|

| ASYNC | Port pin with full synchronous and full asynchronous interrupt function    |

#### 32.1.3 Analog functions

| ACn              | Analog Comparator input pin n            |

|------------------|------------------------------------------|

| ACnOUT           | Analog Comparator n Output               |

| ADCn             | Analog to Digital Converter input pin n  |

| DACn             | Digital to Analog Converter output pin n |

| A <sub>REF</sub> | Analog Reference input pin               |

#### 32.1.4 Timer/Counter and AWEX functions

| OCnxLS | Output Compare Channel x Low Side for Timer/Counter n  |

|--------|--------------------------------------------------------|

| OCnxHS | Output Compare Channel x High Side for Timer/Counter n |

### 32.1.5 Communication functions

| SCL    | Serial Clock for TWI                                               |

|--------|--------------------------------------------------------------------|

| SDA    | Serial Data for TWI                                                |

| SCLIN  | Serial Clock In for TWI when external driver interface is enabled  |

| SCLOUT | Serial Clock Out for TWI when external driver interface is enabled |

| SDAIN  | Serial Data In for TWI when external driver interface is enabled   |

| SDAOUT | Serial Data Out for TWI when external driver interface is enabled  |

| XCKn   | Transfer Clock for USART n                                         |

| RXDn   | Receiver Data for USART n                                          |

Table 36-5. Current consumption for modules and peripherals.

| Symbol          | Parameter                                                 | Condition <sup>(1)</sup>                           |                                                                 | Min. | Тур. | Max. | Units |

|-----------------|-----------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|------|------|------|-------|

|                 | ULP oscillator                                            |                                                    |                                                                 |      | 1.0  |      | μA    |

|                 | 32.768kHz int. oscillator                                 |                                                    |                                                                 |      | 26   |      | μA    |

|                 | 2MHz int. oscillator                                      |                                                    |                                                                 |      | 85   |      |       |

|                 | ZIVITIZ IIII. OSCIIIAIOI                                  | DFLL enabled with 32.768kHz int. osc. as reference |                                                                 |      | 115  |      | μA    |

|                 | 32MHz int. oscillator                                     |                                                    |                                                                 |      | 270  |      | μA    |

|                 | 32WHZ IIII. OSCIIIAIOI                                    | DFLL enabled with                                  | 32.768kHz int. osc. as reference                                |      | 460  |      | μΑ    |

|                 | PLL                                                       | -                                                  | 20x multiplication factor,<br>32MHz int. osc. DIV4 as reference |      | 220  |      | μΑ    |

|                 | Watchdog Timer                                            |                                                    |                                                                 |      | 1    |      | μA    |

|                 | BOD Continuous mode Sampled mode, includes ULP oscillator |                                                    |                                                                 |      | 138  |      |       |

|                 |                                                           |                                                    |                                                                 | 1.2  |      | μA   |       |

|                 | Internal 1.0V reference                                   |                                                    |                                                                 |      | 100  |      | μA    |

| I <sub>CC</sub> | Temperature sensor                                        |                                                    |                                                                 |      | 95   |      | μA    |

|                 | ADC                                                       | 250ksps<br>V <sub>REF</sub> = Ext ref              |                                                                 |      | 3.0  |      | mA    |

|                 |                                                           |                                                    | CURRLIMIT = LOW                                                 |      | 2.6  |      |       |

|                 |                                                           |                                                    | CURRLIMIT = MEDIUM                                              |      | 2.1  |      |       |

|                 |                                                           |                                                    | CURRLIMIT = HIGH                                                |      | 1.6  |      |       |

|                 | DAC                                                       | 250ksps                                            | Normal mode                                                     |      | 1.9  |      | mA    |

|                 | DAC                                                       | V <sub>REF</sub> = Ext ref<br>No load              | Low Power mode                                                  |      | 1.1  |      |       |

|                 | 40                                                        | High Speed Mode                                    |                                                                 |      | 330  |      |       |

|                 | AC                                                        | Low Power Mode                                     |                                                                 |      | 130  |      | μA    |

|                 | DMA                                                       | 615KBps between                                    | I/O registers and SRAM                                          |      | 115  |      | μA    |

|                 | Timer/Counter                                             |                                                    |                                                                 |      | 16   |      | μA    |

|                 | USART                                                     | Rx and Tx enabled                                  | d, 9600 BAUD                                                    |      | 2.5  |      | μA    |

|                 | Flash memory and EEPROM programming                       |                                                    |                                                                 | 4    |      | mA   |       |

Note: 1. All parameters measured as the difference in current consumption between module enabled and disabled. All data at V<sub>CC</sub> = 3.0V, Clk<sub>SYS</sub> = 1MHz external clock without prescaling, T = 25°C unless other conditions are given.

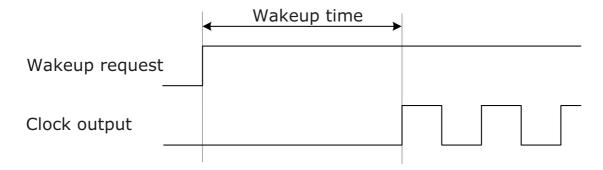

# 36.1.4 Wake-up time from sleep modes

Table 36-6. Device wake-up time from sleep modes with various system clock sources.

| Symbol              | Parameter                                        | Condition                     | Min. | Typ. (1) | Max. | Units |

|---------------------|--------------------------------------------------|-------------------------------|------|----------|------|-------|

|                     |                                                  | External 2MHz clock           |      | 2        |      |       |

|                     | Wake-up time from Idle,                          | 32.768kHz internal oscillator |      | 120      |      |       |

|                     | Standby, and Extended Standby mode               | 2MHz internal oscillator      |      | 2        |      | μs    |

|                     |                                                  | 32MHz internal oscillator     |      | 0.2      |      |       |

| <sup>L</sup> wakeup | Wake-up time from Power-save and Power-down mode | External 2MHz clock           |      | 4.5      |      | μs    |

|                     |                                                  | 32.768kHz internal oscillator |      | 320      |      |       |

|                     |                                                  | 2MHz internal oscillator      |      | 9        |      |       |

|                     |                                                  | 32MHz internal oscillator     |      | 5        |      |       |

Note: 1. The wake-up time is the time from the wake-up request is given until the peripheral clock is available on pin, see Figure 36-2. All peripherals and modules start execution from the first clock cycle, expect the CPU that is halted for four clock cycles before program execution starts.

Figure 36-2. Wake-up time definition.

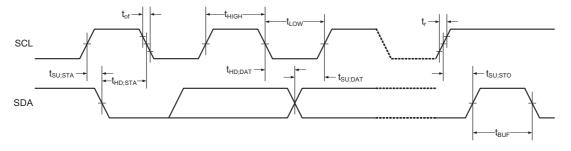

#### 36.1.16 Two-Wire Interface Characteristics

Table 36-32 describes the requirements for devices connected to the Two-Wire Interface Bus. The Atmel AVR XMEGA Two-Wire Interface meets or exceeds these requirements under the noted conditions. Timing symbols refer to Figure 36-7.

Figure 36-7. Two-wire interface bus timing.

Table 36-32. Two-wire interface characteristics.

| Symbol              | Parameter                                        | Condition                                             | Min.                        | Тур. | Max.                 | Units |

|---------------------|--------------------------------------------------|-------------------------------------------------------|-----------------------------|------|----------------------|-------|

| V <sub>IH</sub>     | Input High Voltage                               |                                                       | 0.7*V <sub>CC</sub>         |      | V <sub>CC</sub> +0.5 | V     |

| V <sub>IL</sub>     | Input Low Voltage                                |                                                       | -0.5                        |      | 0.3*V <sub>CC</sub>  | V     |

| V <sub>hys</sub>    | Hysteresis of Schmitt Trigger Inputs             |                                                       | 0.05*V <sub>CC</sub> (1)    |      | 0                    | V     |

| V <sub>OL</sub>     | Output Low Voltage                               | 3mA, sink current                                     | 0                           |      | 0.4                  | V     |

| t <sub>r</sub>      | Rise Time for both SDA and SCL                   |                                                       | 20+0.1C <sub>b</sub> (1)(2) |      | 0                    | ns    |

| t <sub>of</sub>     | Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$ | 10pF < C <sub>b</sub> < 400pF (2)                     | 20+0.1C <sub>b</sub> (1)(2) |      | 300                  | ns    |

| t <sub>SP</sub>     | Spikes Suppressed by Input Filter                |                                                       | 0                           |      | 50                   | ns    |

| I <sub>I</sub>      | Input Current for each I/O Pin                   | $0.1V_{CC} < V_{I} < 0.9V_{CC}$                       | -10                         |      | 10                   | μA    |

| Cı                  | Capacitance for each I/O Pin                     |                                                       |                             |      | 10                   | pF    |

| f <sub>SCL</sub>    | SCL Clock Frequency                              | f <sub>PER</sub> (3)>max(10f <sub>SCL</sub> , 250kHz) | 0                           |      | 400                  | kHz   |

| D                   | Value of Pull-up resistor                        | f <sub>SCL</sub> ≤ 100kHz                             | $\frac{V_{CC} - 0.4V}{3mA}$ |      | $\frac{100ns}{C_b}$  |       |

| R <sub>P</sub>      |                                                  | f <sub>SCL</sub> > 100kHz                             |                             |      | $\frac{300ns}{C_b}$  | Ω     |

|                     | Hold Time (reported) CTART condition             | $f_{SCL} \le 100 kHz$                                 | 4.0                         |      |                      |       |

| t <sub>HD;STA</sub> | Hold Time (repeated) START condition             | f <sub>SCL</sub> > 100kHz                             | 0.6                         |      |                      | μs    |

|                     | Law Pariod of SCL Clock                          | $f_{SCL} \le 100 kHz$                                 | 4.7                         |      |                      | 110   |

| t <sub>LOW</sub>    | Low Period of SCL Clock                          | f <sub>SCL</sub> > 100kHz                             | 1.3                         |      |                      | μs    |

| 4                   | High Period of SCL Clock                         | $f_{SCL} \le 100 kHz$                                 | 4.0                         |      |                      | ue    |

| t <sub>HIGH</sub>   | Thigh renou of SCL Clock                         | f <sub>SCL</sub> > 100kHz                             | 0.6                         |      |                      | μs    |

Table 36-92. External clock with prescaler <sup>(1)</sup>for system clock.

| Symbol            | Parameter                                         | Condition                    | Min. | Тур. | Max. | Units   |

|-------------------|---------------------------------------------------|------------------------------|------|------|------|---------|

| 1/t <sub>CK</sub> | Clock Frequency (2)                               | V <sub>CC</sub> = 1.6 - 1.8V | 0    |      | 90   | MHz     |

| 1/1CK             | Clock Frequency                                   | V <sub>CC</sub> = 2.7 - 3.6V | 0    |      | 142  | IVII IZ |

|                   | Clock Period                                      | V <sub>CC</sub> = 1.6 - 1.8V | 11   |      |      | no      |

| t <sub>CK</sub>   | Clock Fellou                                      | V <sub>CC</sub> = 2.7 - 3.6V | 7    |      |      | ns      |

| +                 | Clock High Time                                   | V <sub>CC</sub> = 1.6 - 1.8V | 4.5  |      |      | ns      |

| t <sub>CH</sub>   | Clock Flight Time                                 | V <sub>CC</sub> = 2.7 - 3.6V | 2.4  |      |      |         |

| 4                 | Clock Low Time                                    | V <sub>CC</sub> = 1.6 - 1.8V | 4.5  |      |      | ns      |

| t <sub>CL</sub>   | Clock Low Time                                    | V <sub>CC</sub> = 2.7 - 3.6V | 2.4  |      |      |         |

| +                 | Dies Time (for movimum fragues ov)                | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  | ns      |

| t <sub>CR</sub>   | Rise Time (for maximum frequency)                 | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  |         |

| +                 | Fall Time (for maximum frequency)                 | V <sub>CC</sub> = 1.6 - 1.8V |      |      | 1.5  | ns      |

| t <sub>CF</sub>   | r all time (ior maximum frequency)                | V <sub>CC</sub> = 2.7 - 3.6V |      |      | 1.0  | 113     |

| $\Delta t_{CK}$   | Change in period from one clock cycle to the next |                              |      |      | 10   | %       |

Notes:

# 36.3.14.7 External 16MHz crystal oscillator and XOSC characteristics

Table 36-93. External 16MHz crystal oscillator and XOSC characteristics.

| Symbol | Parameter             | Condition  |                     | Min. | Тур.   | Max. | Units |

|--------|-----------------------|------------|---------------------|------|--------|------|-------|

|        |                       | XOSCPWR=0  | FRQRANGE=0          |      | <10    |      |       |

|        | Cycle to cycle jitter | XUSCPVVR=0 | FRQRANGE=1, 2, or 3 |      | <1     |      | ns    |

|        |                       | XOSCPWR=1  |                     |      | <1     |      |       |

|        | Long term jitter      | XOSCPWR=0  | FRQRANGE=0          |      | <6     |      |       |

|        |                       | AUSCHWR-U  | FRQRANGE=1, 2, or 3 |      | <0.5   |      | ns    |

|        |                       | XOSCPWR=1  |                     |      | <0.5   |      |       |

|        |                       |            | FRQRANGE=0          |      | <0.1   |      |       |

|        | Eroguenov error       | XOSCPWR=0  | FRQRANGE=1          |      | <0.05  |      | %     |

|        | Frequency error       |            | FRQRANGE=2 or 3     |      | <0.005 |      | 70    |

|        |                       | XOSCPWR=1  |                     |      | <0.005 |      |       |

|        |                       |            | FRQRANGE=0          |      | 40     |      |       |

|        | Duty cycle            | XOSCPWR=0  | FRQRANGE=1          |      | 42     |      | %     |

|        |                       |            | FRQRANGE=2 or 3     |      | 45     |      | 70    |

|        |                       | XOSCPWR=1  |                     |      | 48     |      |       |

<sup>1.</sup> System Clock Prescalers must be set so that maximum CPU clock frequency for device is not exceeded.

<sup>2.</sup> The maximum frequency vs. supply voltage is linear between 1.6V and 2.7V, and the same applies for all other parameters with supply voltage conditions.

Table 36-127. SPI timing characteristics and requirements.

| Symbol             | Parameter               | Condition | Min.                   | Тур.                                   | Max. | Units |

|--------------------|-------------------------|-----------|------------------------|----------------------------------------|------|-------|

| t <sub>sck</sub>   | SCK Period              | Master    |                        | (See Table 21-4 in<br>XMEGA AU Manual) |      |       |

| t <sub>SCKW</sub>  | SCK high/low width      | Master    |                        | 0.5*SCK                                |      |       |

| t <sub>SCKR</sub>  | SCK Rise time           | Master    |                        | 2.7                                    |      |       |

| t <sub>SCKF</sub>  | SCK Fall time           | Master    |                        | 2.7                                    |      |       |

| t <sub>MIS</sub>   | MISO setup to SCK       | Master    |                        | 10                                     |      |       |

| t <sub>MIH</sub>   | MISO hold after SCK     | Master    |                        | 10                                     |      |       |

| t <sub>MOS</sub>   | MOSI setup SCK          | Master    |                        | 0.5*SCK                                |      |       |

| t <sub>MOH</sub>   | MOSI hold after SCK     | Master    |                        | 1                                      |      |       |

| t <sub>ssck</sub>  | Slave SCK Period        | Slave     | 4*t Clk <sub>PER</sub> |                                        |      |       |

| t <sub>SSCKW</sub> | SCK high/low width      | Slave     | 2*t Clk <sub>PER</sub> |                                        |      | ns    |

| t <sub>SSCKR</sub> | SCK Rise time           | Slave     |                        |                                        | 1600 |       |

| t <sub>SSCKF</sub> | SCK Fall time           | Slave     |                        |                                        | 1600 |       |

| t <sub>SIS</sub>   | MOSI setup to SCK       | Slave     | 3                      |                                        |      |       |

| t <sub>SIH</sub>   | MOSI hold after SCK     | Slave     | t Clk <sub>PER</sub>   |                                        |      |       |

| t <sub>sss</sub>   | SS setup to SCK         | Slave     | 21                     |                                        |      |       |

| t <sub>SSH</sub>   | SS hold after SCK       | Slave     | 20                     |                                        |      |       |

| t <sub>sos</sub>   | MISO setup SCK          | Slave     |                        | 8                                      |      |       |

| t <sub>SOH</sub>   | MISO hold after SCK     | Slave     |                        | 13                                     |      |       |

| t <sub>soss</sub>  | MISO setup after SS low | Slave     |                        | 11                                     |      |       |

| t <sub>SOSH</sub>  | MISO hold after SS high | Slave     |                        | 8                                      |      |       |

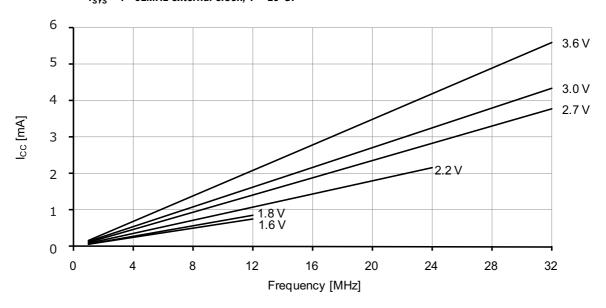

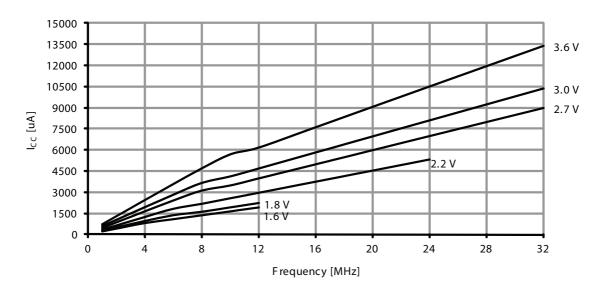

Figure 37-9. Idle mode supply current vs. frequency.  $f_{SYS} = 1 - 32MHz$  external clock, T = 25°C.

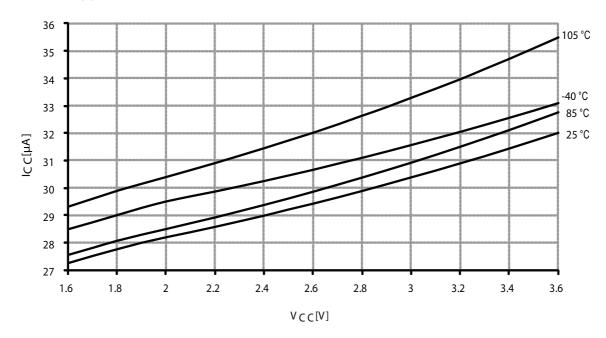

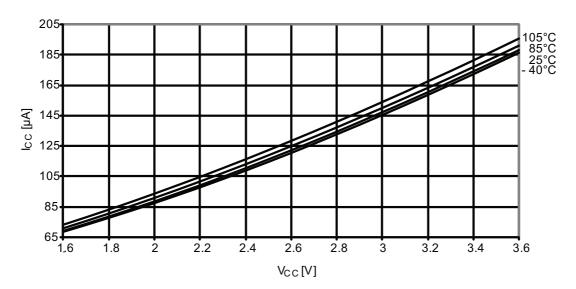

Figure 37-10. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 32.768kHz$  internal oscillator.

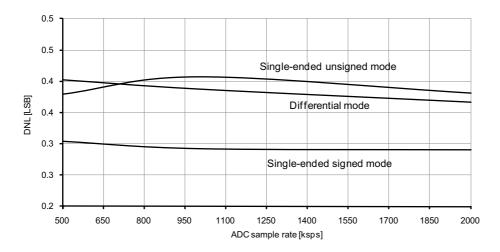

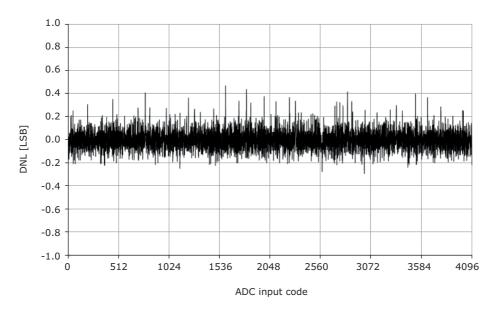

Figure 37-40. DNL error vs. input code.

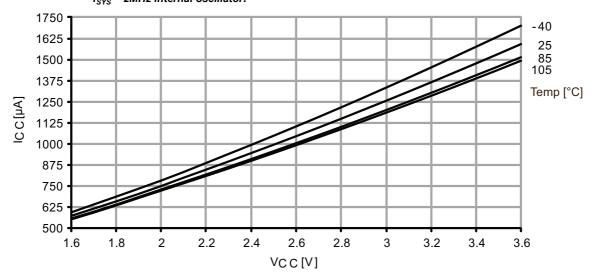

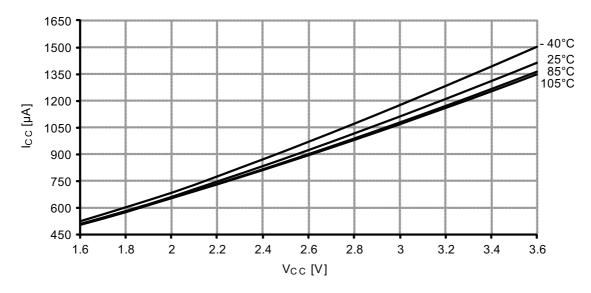

Figure 37-88. Active mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 2MHz$  internal oscillator.

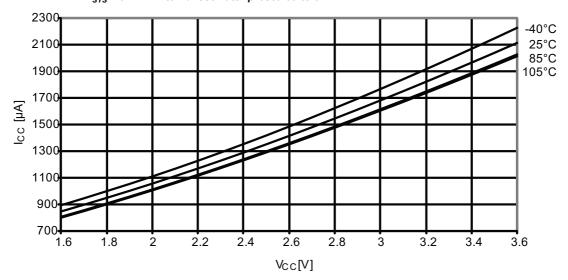

Figure 37-89. Active mode supply current vs.  $V_{\text{CC}}$ .

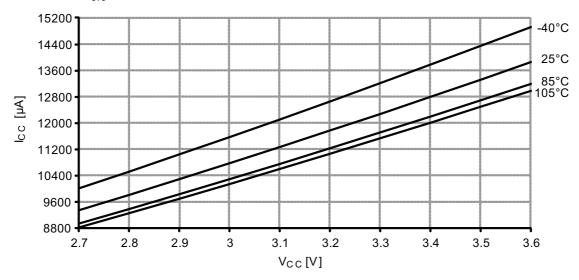

Figure 37-173. Active mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 32MHz$  internal oscillator.

# 37.3.1.2 Idle mode supply current

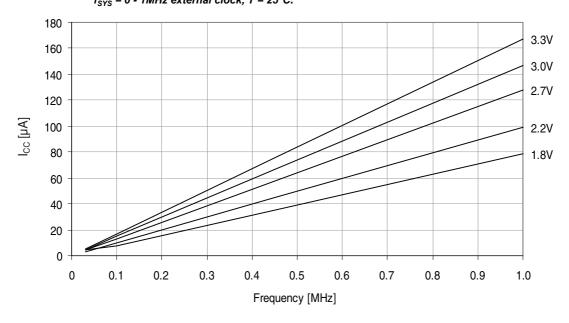

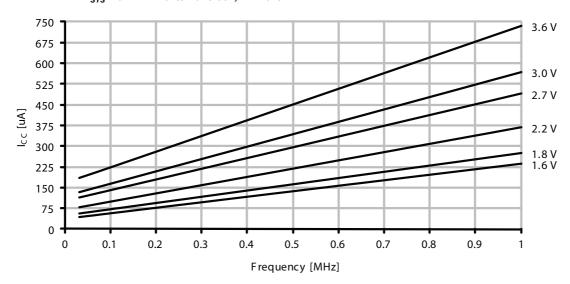

Figure 37-174. Idle mode supply current vs. frequency.  $f_{SYS} = 0$  - 1MHz external clock,  $T = 25^{\circ}C$ .

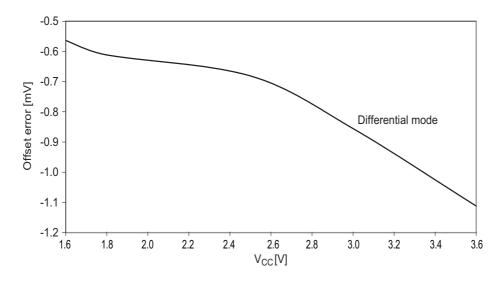

Figure 37-211. Offset error vs.  $V_{CC}$ .  $T = 25 \, ^{\circ}C$ ,  $V_{REF} = external \ 1.0V$ , ADC sampling speed = 500ksps.

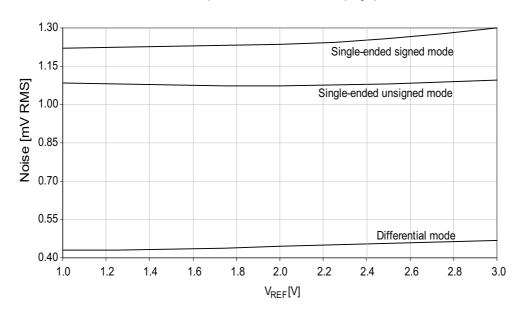

Figure 37-212. Noise vs.  $V_{REF}$ .  $T = 25 \, \text{C}$ ,  $V_{CC} = 3.6 V$ , ADC sampling speed = 500ksps.

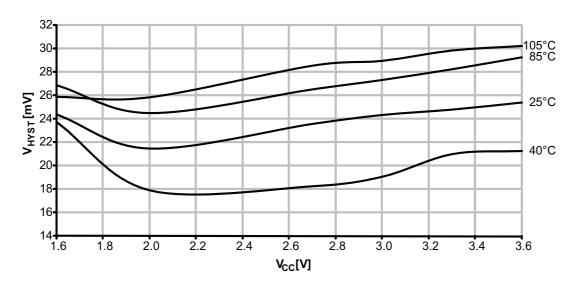

Figure 37-219. Analog comparator hysteresis vs. V<sub>CC</sub>. *High-speed mode, large hysteresis*.

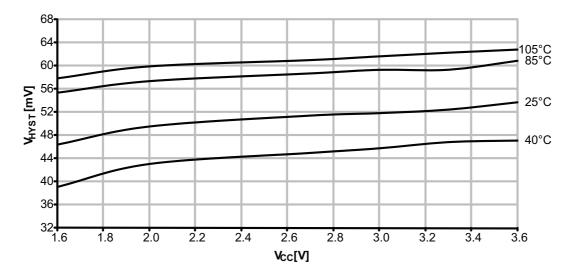

Figure 37-220. Analog comparator hysteresis vs.  $V_{CC}$ . Low power, large hysteresis.

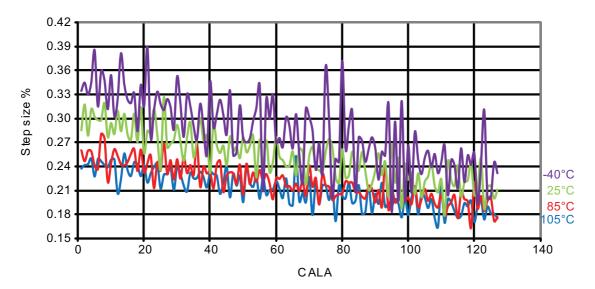

Figure 37-242. 32MHz internal oscillator CALA calibration step size.  $V_{\rm CC}$  = 3.0 $V_{\rm CC}$

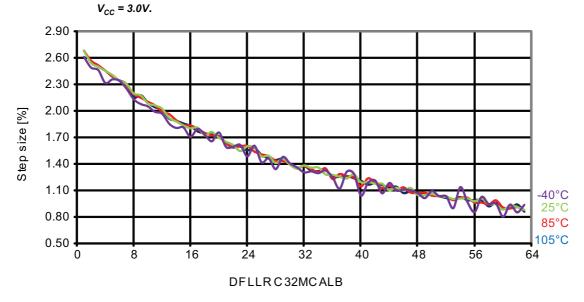

Figure 37-243. 32MHz internal oscillator frequency vs. CALB calibration value.

# 37.4 ATxmega256A3U

# 37.4.1 Current consumption

# 37.4.1.1 Active mode supply current

Figure 37-250. Active supply current vs. frequency.  $f_{SYS} = 0$  - 1MHz external clock,  $T = 25^{\circ}$ C.

Figure 37-251. Active supply current vs. frequency.  $f_{SYS} = 1 - 32MHz$  external clock,  $T = 25^{\circ}C$ .

Figure 37-260. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 1MHz$  external clock.

Figure 37-261. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 2MHz$  internal oscillator.

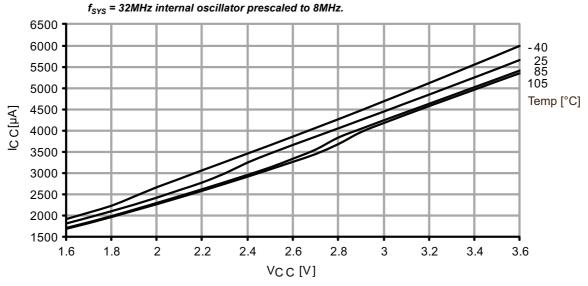

Figure 37-262. Idle mode supply current vs.  $V_{CC}$ .  $f_{SYS} = 32MHz$  internal oscillator prescaled to 8MHz.

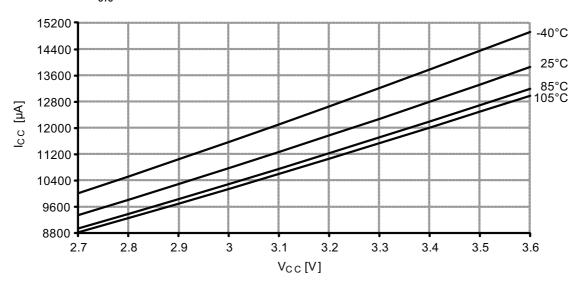

Figure 37-263. Idle mode current vs.  $V_{CC}$ .  $f_{SYS} = 32MHz$  internal oscillator.

# 37.4.1.3 Power-down mode supply current

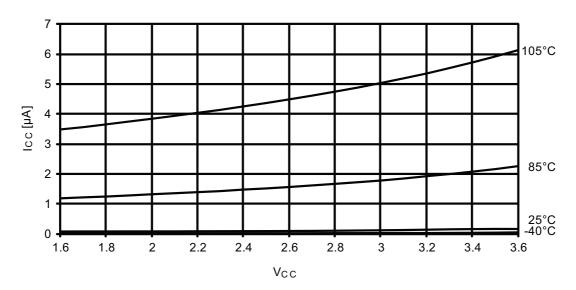

Figure 37-264. Power-down mode supply current vs.  $V_{CC}$ . All functions disabled.

Figure 37-265. Power-down mode supply current vs. V<sub>CC</sub>. Watchdog and sampled BOD enabled.

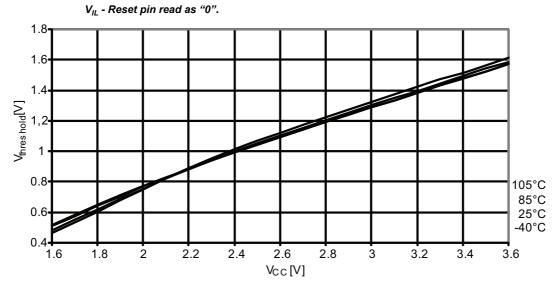

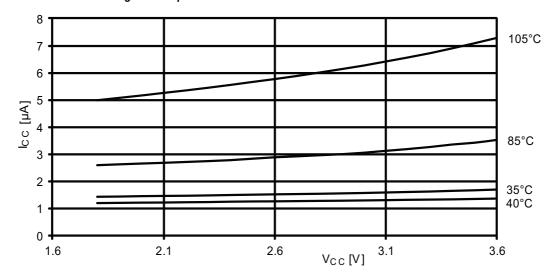

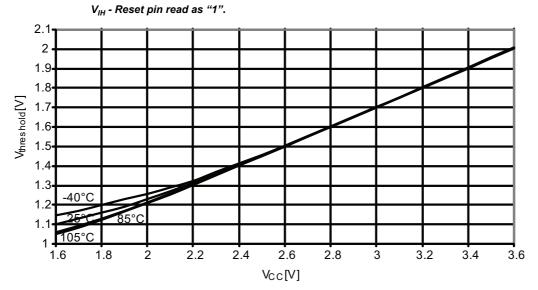

Figure 37-314. Reset pin input threshold voltage vs.  $V_{CC.}$

Figure 37-315. Reset pin input threshold voltage vs.  $\mathbf{V}_{\text{CC.}}$