#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | C166                                                                          |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 40MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                              |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 111                                                                           |

| Program Memory Size        | -                                                                             |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 11K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 24x10b                                                                    |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 144-BQFP                                                                      |

| Supplier Device Package    | P-MQFP-144-8                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c167csl40mcabxqla2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 16-Bit Single-Chip Microcontroller C166 Family

C167CS

# C167CS-4R, C167CS-L

- High Performance 16-bit CPU with 4-Stage Pipeline

- 80/60/50 ns Instruction Cycle Time at 25/33/40 MHz CPU Clock

- 400/303/250 ns Multiplication (16 × 16 bit), 800/606/500 ns Division (32-/16-bit)

- Enhanced Boolean Bit Manipulation Facilities

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Single-Cycle Context Switching Support

- 16 MBytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area

- 16-Priority-Level Interrupt System with 56 Sources, Sample-Rate down to 40/30/25 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC)

- Clock Generation via on-chip PLL (factors 1:1.5/2/2.5/3/4/5), via prescaler or via direct clock input

- On-Chip Memory Modules

- 3 KBytes On-Chip Internal RAM (IRAM)

- 8 KBytes On-Chip Extension RAM (XRAM)

- 32 KBytes On-Chip Program Mask ROM

- On-Chip Peripheral Modules

- 24-Channel 10-bit A/D Converter with Programmable Conversion Time down to 7.8 μs

- Two 16-Channel Capture/Compare Units

- 4-Channel PWM Unit

- Two Multi-Functional General Purpose Timer Units with 5 Timers

- Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

- Two On-Chip CAN Interfaces (Rev. 2.0B active) with  $2 \times 15$  Message Objects (Full CAN/Basic CAN), can work on one bus with 30 objects

- On-Chip Real Time Clock

- Up to 16 MBytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses with 8-Bit or 16-Bit Data Bus Width

- Five Programmable Chip-Select Signals

- Hold- and Hold-Acknowledge Bus Arbitration Support

- Idle, Sleep, and Power Down Modes with Flexible Power Management

- Programmable Watchdog Timer and Oscillator Watchdog

- Up to 111 General Purpose I/O Lines, partly with Selectable Input Thresholds and Hysteresis

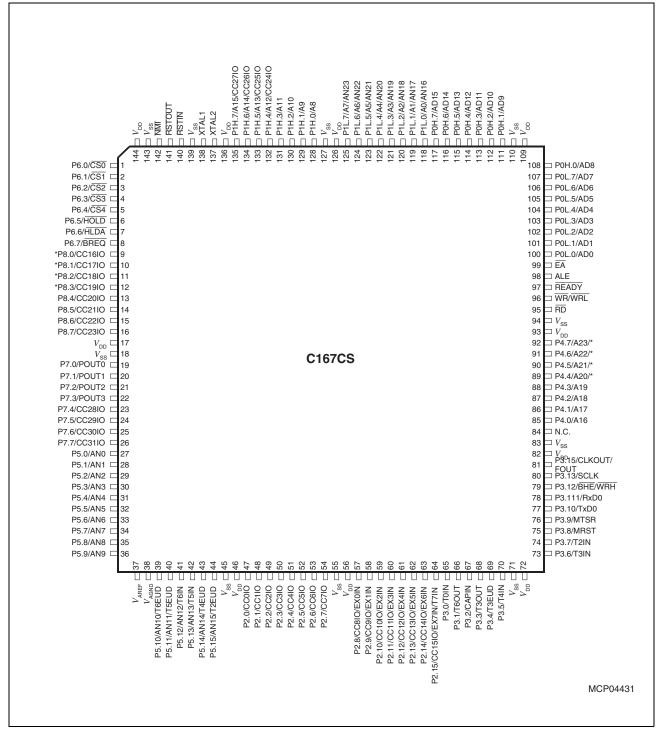

#### Pin Configuration

(top view)

#### Figure 2

\*) The marked pins of Port 4 and Port 8 can have CAN interface lines assigned to them. Table 2 on the pages below lists the possible assignments.

| Table 2 | Pi          | n Definit      | tions and Functions (cont'd)                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|---------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Symbol  | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Ρ7      |             | IO             | Port 7 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 7 outputs can be configured as push/<br>pull or open drain drivers. The input threshold of Port 7 is<br>selectable (TTL or special).<br>The following Port 7 pins also serve for alternate functions: |  |  |  |  |  |  |  |

| P7.0    | 19          | 0              | POUT0 PWM Channel 0 Output                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| P7.1    | 20          | 0              | POUT1 PWM Channel 1 Output                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| P7.2    | 21          | 0              | POUT2 PWM Channel 2 Output                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| P7.3    | 22          | 0              | POUT3 PWM Channel 3 Output                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| P7.4    | 23          | I/O            | CC28IO CAPCOM2: CC28 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| P7.5    | 24          | I/O            | CC29IO CAPCOM2: CC29 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| P7.6    | 25          | I/O            | CC30IO CAPCOM2: CC30 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| P7.7    | 26          | I/O            | CC31IO CAPCOM2: CC31 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |

| P5      |             | I              | Port 5 is a 16-bit input-only port with Schmitt-Trigger char.<br>The pins of Port 5 also serve as analog input channels for the A/D converter, or they serve as timer inputs:                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

| P5.0    | 27          | 1              | ANO                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.1    | 28          | 1              | AN1                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.2    | 29          | 1              | AN2                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.3    | 30          | 1              | AN3                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.4    | 31          | 1              | AN4                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.5    | 32          | 1              | AN5                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.6    | 33          | 1              | AN6                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.7    | 34          | 1              | AN7                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.8    | 35          | 1              | AN8                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.9    | 36          | 1              | AN9                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.10   | 39          | 1              | AN10, T6EUD GPT2 Timer T6 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| P5.11   | 40          | 1              | AN11, T5EUD GPT2 Timer T5 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| P5.12   | 41          |                | AN12, T6IN GPT2 Timer T6 Count Inp.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.13   | 42          | 1              | AN13, T5IN GPT2 Timer T5 Count Inp.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |

| P5.14   | 43          |                | AN14, T4EUD GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| P5.15   | 44          |                | AN15, T2EUD GPT1 Timer T2 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Table 2 | Pin Definitions and Functions (cont <sup>2</sup> d) |                |                                                      |                                                                  |  |  |  |  |  |

|---------|-----------------------------------------------------|----------------|------------------------------------------------------|------------------------------------------------------------------|--|--|--|--|--|

| Symbol  | Pin<br>Num.                                         | Input<br>Outp. | Function                                             |                                                                  |  |  |  |  |  |

| PORT1   |                                                     | IO             | PORT1 co                                             | nsists of the two 8-bit bidirectional I/O ports P1L              |  |  |  |  |  |

| P1L.0-7 | 118-                                                |                | and P1H. I                                           | t is bit-wise programmable for input or output via               |  |  |  |  |  |

|         | 125                                                 |                | direction b                                          | lirection bits. For a pin configured as input, the output driver |  |  |  |  |  |

| P1H.0-7 | 128-                                                |                | is put into                                          | high-impedance state. PORT1 is used as the                       |  |  |  |  |  |

|         | 135                                                 |                | 16-bit addr                                          | ess bus (A) in demultiplexed bus modes and also                  |  |  |  |  |  |

|         |                                                     |                | after switching from a demultiplexed bus mode to a   |                                                                  |  |  |  |  |  |

|         |                                                     |                |                                                      | d bus mode.                                                      |  |  |  |  |  |

|         |                                                     |                |                                                      | ing PORT1 pins also serve for alternate functions:               |  |  |  |  |  |

| P1L.0   | 118                                                 | 1              | AN16                                                 | Analog Input Channel 16                                          |  |  |  |  |  |

| P1L.1   | 119                                                 | 1              | AN17                                                 |                                                                  |  |  |  |  |  |

| P1L.2   | 120                                                 | 1              | AN18                                                 | 5 1                                                              |  |  |  |  |  |

| P1L.3   | 121                                                 | 1              | AN19                                                 | Analog Input Channel 19                                          |  |  |  |  |  |

| P1L.4   | 122                                                 |                | AN20                                                 | Analog Input Channel 20                                          |  |  |  |  |  |

| P1L.5   | 123                                                 |                | AN21                                                 | Analog Input Channel 21                                          |  |  |  |  |  |

| P1L.6   | 124                                                 |                | AN22                                                 | Analog Input Channel 22                                          |  |  |  |  |  |

| P1L.7   | 125                                                 |                | AN23                                                 | Analog Input Channel 23                                          |  |  |  |  |  |

| P1H.4   | 132                                                 | I/O            | CC24IO                                               | CAPCOM2: CC24 Capture Inp./Compare Outp.                         |  |  |  |  |  |

| P1H.5   | 133                                                 | I/O            | CC25IO                                               | CAPCOM2: CC25 Capture Inp./Compare Outp.                         |  |  |  |  |  |

| P1H.6   | 134                                                 | I/O            | CC26IO                                               | CAPCOM2: CC26 Capture Inp./Compare Outp.                         |  |  |  |  |  |

| P1H.7   | 135                                                 | I/O            | CC27IO                                               | CAPCOM2: CC27 Capture Inp./Compare Outp.                         |  |  |  |  |  |

| XTAL2   | 137                                                 | 0              | XTAL2:                                               | Output of the oscillator amplifier circuit.                      |  |  |  |  |  |

| XTAL1   | 138                                                 | 1              | XTAL1:                                               | Input to the oscillator amplifier and input to                   |  |  |  |  |  |

|         |                                                     |                |                                                      | the internal clock generator                                     |  |  |  |  |  |

|         |                                                     |                | To clock th                                          | ne device from an external source, drive XTAL1,                  |  |  |  |  |  |

|         |                                                     |                | while leaving XTAL2 unconnected. Minimum and maximum |                                                                  |  |  |  |  |  |

|         |                                                     |                | high/low a                                           | nd rise/fall times specified in the AC                           |  |  |  |  |  |

|         |                                                     |                | Characteri                                           | stics must be observed.                                          |  |  |  |  |  |

#### External Bus Controller

All of the external memory accesses are performed by a particular on-chip External Bus Controller (EBC). It can be programmed either to Single Chip Mode when no external memory is required, or to one of four different external memory access modes, which are as follows:

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Demultiplexed

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/ output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output.

Important timing characteristics of the external bus interface (Memory Cycle Time, Memory Tri-State Time, Length of ALE and Read Write Delay) have been made programmable to allow the user the adaption of a wide range of different types of memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via register pairs ADDRSELx / BUSCONx) which control the access to different resources with different bus characteristics. These address windows are arranged hierarchically where BUSCON4 overrides BUSCON3 and BUSCON2 overrides BUSCON1. All accesses to locations not covered by these 4 address windows are controlled by BUSCON0.

Up to 5 external  $\overline{CS}$  signals (4 windows plus default) can be generated in order to save external glue logic. The C167CS offers the possibility to switch the  $\overline{CS}$  outputs to an unlatched mode. In this mode the internal filter logic is switched off and the  $\overline{CS}$  signals are directly generated from the address. The unlatched  $\overline{CS}$  mode is enabled by setting CSCFG (SYSCON.6).

Access to very slow memories or memories with varying access times is supported via a particular 'Ready' function.

A HOLD/HLDA protocol is available for bus arbitration and allows to share external resources with other bus masters. The bus arbitration is enabled by setting bit HLDEN in register PSW. After setting HLDEN once, pins P6.7 ... P6.5 (BREQ, HLDA, HOLD) are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA pin is an output. By setting bit DP6.7 to '1' the Slave Mode is selected where pin HLDA is switched to input. This allows to directly connect the slave controller to another master controller without glue logic.

For applications which require less than 16 MBytes of external memory space, this address space can be restricted to 1 MByte, 256 KByte, or to 64 KByte. In this case Port 4 outputs four, two, or no address lines at all. It outputs all 8 address lines, if an address space of 16 MBytes is used.

# Table 3 C167CS Interrupt Nodes

| Source of Interrupt or PEC Service Request | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location   | Trap<br>Number  |

|--------------------------------------------|-----------------|----------------|---------------------|----------------------|-----------------|

| CAPCOM Register 0                          | CC0IR           | CC0IE          | CC0INT              | 00'0040 <sub>H</sub> | 10 <sub>H</sub> |

| CAPCOM Register 1                          | CC1IR           | CC1IE          | CC1INT              | 00'0044 <sub>H</sub> | 11 <sub>H</sub> |

| CAPCOM Register 2                          | CC2IR           | CC2IE          | CC2INT              | 00'0048 <sub>H</sub> | 12 <sub>H</sub> |

| CAPCOM Register 3                          | CC3IR           | CC3IE          | <b>CC3INT</b>       | 00'004C <sub>H</sub> | 13 <sub>H</sub> |

| CAPCOM Register 4                          | CC4IR           | CC4IE          | CC4INT              | 00'0050 <sub>H</sub> | 14 <sub>H</sub> |

| CAPCOM Register 5                          | CC5IR           | CC5IE          | CC5INT              | 00'0054 <sub>H</sub> | 15 <sub>H</sub> |

| CAPCOM Register 6                          | CC6IR           | CC6IE          | CC6INT              | 00'0058 <sub>H</sub> | 16 <sub>H</sub> |

| CAPCOM Register 7                          | CC7IR           | CC7IE          | CC7INT              | 00'005C <sub>H</sub> | 17 <sub>H</sub> |

| CAPCOM Register 8                          | CC8IR           | CC8IE          | CC8INT              | 00'0060 <sub>H</sub> | 18 <sub>H</sub> |

| CAPCOM Register 9                          | CC9IR           | CC9IE          | CC9INT              | 00'0064 <sub>H</sub> | 19 <sub>H</sub> |

| CAPCOM Register 10                         | CC10IR          | CC10IE         | CC10INT             | 00'0068 <sub>H</sub> | 1A <sub>H</sub> |

| CAPCOM Register 11                         | CC11IR          | CC11IE         | CC11INT             | 00'006C <sub>H</sub> | 1B <sub>H</sub> |

| CAPCOM Register 12                         | CC12IR          | CC12IE         | CC12INT             | 00'0070 <sub>H</sub> | 1C <sub>H</sub> |

| CAPCOM Register 13                         | CC13IR          | CC13IE         | CC13INT             | 00'0074 <sub>H</sub> | 1D <sub>H</sub> |

| CAPCOM Register 14                         | CC14IR          | CC14IE         | CC14INT             | 00'0078 <sub>H</sub> | 1E <sub>H</sub> |

| CAPCOM Register 15                         | CC15IR          | CC15IE         | CC15INT             | 00'007C <sub>H</sub> | 1F <sub>H</sub> |

| CAPCOM Register 16                         | CC16IR          | CC16IE         | CC16INT             | 00'00C0 <sub>H</sub> | 30 <sub>H</sub> |

| CAPCOM Register 17                         | CC17IR          | CC17IE         | CC17INT             | 00'00C4 <sub>H</sub> | 31 <sub>H</sub> |

| CAPCOM Register 18                         | CC18IR          | CC18IE         | CC18INT             | 00'00C8 <sub>H</sub> | 32 <sub>H</sub> |

| CAPCOM Register 19                         | CC19IR          | CC19IE         | CC19INT             | 00'00CC <sub>H</sub> | 33 <sub>H</sub> |

| CAPCOM Register 20                         | CC20IR          | CC20IE         | CC20INT             | 00'00D0 <sub>H</sub> | 34 <sub>H</sub> |

| CAPCOM Register 21                         | CC21IR          | CC21IE         | CC21INT             | 00'00D4 <sub>H</sub> | 35 <sub>H</sub> |

| CAPCOM Register 22                         | CC22IR          | CC22IE         | CC22INT             | 00'00D8 <sub>H</sub> | 36 <sub>H</sub> |

| CAPCOM Register 23                         | CC23IR          | CC23IE         | CC23INT             | 00'00DC <sub>H</sub> | 37 <sub>H</sub> |

| CAPCOM Register 24                         | CC24IR          | CC24IE         | CC24INT             | 00'00E0 <sub>H</sub> | 38 <sub>H</sub> |

| CAPCOM Register 25                         | CC25IR          | CC25IE         | CC25INT             | 00'00E4 <sub>H</sub> | 39 <sub>H</sub> |

| CAPCOM Register 26                         | CC26IR          | CC26IE         | CC26INT             | 00'00E8 <sub>H</sub> | 3A <sub>H</sub> |

| CAPCOM Register 27                         | CC27IR          | CC27IE         | CC27INT             | 00'00EC <sub>H</sub> | 3B <sub>H</sub> |

| CAPCOM Register 28                         | CC28IR          | CC28IE         | CC28INT             | 00'00E0 <sub>H</sub> | 3C <sub>H</sub> |

| CAPCOM Register 29                         | CC29IR          | CC29IE         | CC29INT             | 00'0110 <sub>H</sub> | 44 <sub>H</sub> |

#### **CAN-Modules**

The integrated CAN-Modules handle the completely autonomous transmission and reception of CAN frames in accordance with the CAN specification V2.0 part B (active), i.e. the on-chip CAN-Modules can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

The modules provide Full CAN functionality on up to 15 message objects each. Message object 15 may be configured for Basic CAN functionality. Both modes provide separate masks for acceptance filtering which allows to accept a number of identifiers in Full CAN mode and also allows to disregard a number of identifiers in Basic CAN mode. All message objects can be updated independent from the other objects and are equipped for the maximum message length of 8 bytes.

The bit timing is derived from the XCLK and is programmable up to a data rate of 1 Mbit/ s. Each CAN-Module uses two pins of Port 4 or Port 8 to interface to an external bus transceiver. The interface pins are assigned via software.

**Module CAN2** is identical with the first one, except that it uses a separate address area and a separate interrupt node.

The two CAN modules can be internally coupled by assigning their interface pins to the same two port pins, or they can interface to separate CAN buses.

Note: When any CAN interface is assigned to Port 4, the respective segment address lines on Port 4 cannot be used. This will limit the external address space.

#### Watchdog Timer

The Watchdog Timer represents one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Watchdog Timer is always enabled after a reset of the chip, and can only be disabled in the time interval until the EINIT (end of initialization) instruction has been executed. Thus, the chip's start-up procedure is always monitored. The software has to be designed to service the Watchdog Timer before it overflows. If, due to hardware or software related failures, the software fails to do so, the Watchdog Timer overflows and generates an internal hardware reset and pulls the RSTOUT pin low in order to allow external hardware components to be reset.

The Watchdog Timer is a 16-bit timer, clocked with the system clock divided by 2/4/128/256. The high byte of the Watchdog Timer register can be set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the high byte of the Watchdog Timer is reloaded. Thus, time intervals between 12.8  $\mu$ s and 419 ms can be monitored (@ 40 MHz).

The default Watchdog Timer interval after reset is 3.27 ms (@ 40 MHz).

#### **Oscillator Watchdog**

The Oscillator Watchdog (OWD) monitors the clock signal generated by the on-chip oscillator (either with a crystal or via external clock drive). For this operation the PLL provides a clock signal which is used to supervise transitions on the oscillator clock. This PLL clock is independent from the XTAL1 clock. When the expected oscillator clock transitions are missing the OWD activates the PLL Unlock/OWD interrupt node and supplies the CPU with the PLL clock signal. Under these circumstances the PLL will oscillate with its basic frequency.

In direct drive mode the PLL base frequency is used directly ( $f_{CPU} = 2 \dots 5 \text{ MHz}$ ). In prescaler mode the PLL base frequency is divided by 2 ( $f_{CPU} = 1 \dots 2.5 \text{ MHz}$ ).

Note: The CPU clock source is only switched back to the oscillator clock after a hardware reset.

**The oscillator watchdog can be disabled** by setting bit OWDDIS in register SYSCON. In this case (OWDDIS = '1') the PLL remains idle and provides no clock signal, while the CPU clock signal is derived directly from the oscillator clock or via prescaler or SDD. Also no interrupt request will be generated in case of a missing oscillator clock.

Note: At the end of a reset bit OWDDIS reflects the inverted level of pin RD at that time. Thus the oscillator watchdog may also be disabled via hardware by (externally) pulling the RD line low upon a reset, similar to the standard reset configuration via PORT0.

#### **Instruction Set Summary**

Table 6 lists the instructions of the C167CS in a condensed way.

The various addressing modes that can be used with a specific instruction, the operation of the instructions, parameters for conditional execution of instructions, and the opcodes for each instruction can be found in the "C166 Family Instruction Set Manual".

This document also provides a detailed description of each instruction.

| Mnemonic           | Description                                                                                          | Bytes |

|--------------------|------------------------------------------------------------------------------------------------------|-------|

| ADD(B)             | Add word (byte) operands                                                                             | 2/4   |

| ADDC(B)            | Add word (byte) operands with Carry                                                                  | 2/4   |

| SUB(B)             | Subtract word (byte) operands                                                                        | 2/4   |

| SUBC(B)            | Subtract word (byte) operands with Carry                                                             | 2/4   |

| MUL(U)             | (Un)Signed multiply direct GPR by direct GPR (16-16-bit)                                             | 2     |

| DIV(U)             | (Un)Signed divide register MDL by direct GPR (16-/16-bit)                                            | 2     |

| DIVL(U)            | (Un)Signed long divide reg. MD by direct GPR (32-/16-bit)                                            | 2     |

| CPL(B)             | Complement direct word (byte) GPR                                                                    | 2     |

| NEG(B)             | Negate direct word (byte) GPR                                                                        | 2     |

| AND(B)             | Bitwise AND, (word/byte operands)                                                                    | 2/4   |

| OR(B)              | Bitwise OR, (word/byte operands)                                                                     | 2/4   |

| XOR(B)             | Bitwise XOR, (word/byte operands)                                                                    | 2/4   |

| BCLR               | Clear direct bit                                                                                     | 2     |

| BSET               | Set direct bit                                                                                       | 2     |

| BMOV(N)            | Move (negated) direct bit to direct bit                                                              | 4     |

| BAND, BOR,<br>BXOR | AND/OR/XOR direct bit with direct bit                                                                | 4     |

| BCMP               | Compare direct bit to direct bit                                                                     | 4     |

| BFLDH/L            | Bitwise modify masked high/low byte of bit-addressable direct word memory with immediate data        | 4     |

| CMP(B)             | Compare word (byte) operands                                                                         | 2/4   |

| CMPD1/2            | Compare word data to GPR and decrement GPR by 1/2                                                    | 2/4   |

| CMPI1/2            | Compare word data to GPR and increment GPR by 1/2                                                    | 2/4   |

| PRIOR              | Determine number of shift cycles to normalize direct<br>word GPR and store result in direct word GPR | 2     |

| SHL / SHR          | Shift left/right direct word GPR                                                                     | 2     |

| ROL / ROR          | Rotate left/right direct word GPR                                                                    | 2     |

| ASHR               | Arithmetic (sign bit) shift right direct word GPR                                                    | 2     |

#### Table 6Instruction Set Summary

| Table 6 Ins            | struction Set Summary (cont'd)                                                      |       |

|------------------------|-------------------------------------------------------------------------------------|-------|

| Mnemonic               | Description                                                                         | Bytes |

| MOV(B)                 | Move word (byte) data                                                               | 2/4   |

| MOVBS                  | Move byte operand to word operand with sign extension                               | 2/4   |

| MOVBZ                  | Move byte operand to word operand with zero extension                               | 2/4   |

| JMPA, JMPI,<br>JMPR    | Jump absolute/indirect/relative if condition is met                                 | 4     |

| JMPS                   | Jump absolute to a code segment                                                     | 4     |

| J(N)B                  | Jump relative if direct bit is (not) set                                            | 4     |

| JBC                    | Jump relative and clear bit if direct bit is set                                    | 4     |

| JNBS                   | Jump relative and set bit if direct bit is not set                                  | 4     |

| CALLA, CALLI,<br>CALLR | Call absolute/indirect/relative subroutine if condition is met                      | 4     |

| CALLS                  | Call absolute subroutine in any code segment                                        | 4     |

| PCALL                  | Push direct word register onto system stack and call absolute subroutine            | 4     |

| TRAP                   | Call interrupt service routine via immediate trap number                            | 2     |

| PUSH, POP              | Push/pop direct word register onto/from system stack                                | 2     |

| SCXT                   | Push direct word register onto system stack and update register with word operand   | 4     |

| RET                    | Return from intra-segment subroutine                                                | 2     |

| RETS                   | Return from inter-segment subroutine                                                | 2     |

| RETP                   | Return from intra-segment subroutine and pop direct word register from system stack | 2     |

| RETI                   | Return from interrupt service subroutine                                            | 2     |

| SRST                   | Software Reset                                                                      | 4     |

| IDLE                   | Enter Idle Mode                                                                     | 4     |

| PWRDN                  | Enter Power Down Mode (supposes NMI-pin being low)                                  | 4     |

| SRVWDT                 | Service Watchdog Timer                                                              | 4     |

| DISWDT                 | Disable Watchdog Timer                                                              | 4     |

| EINIT                  | Signify End-of-Initialization on RSTOUT-pin                                         | 4     |

| ATOMIC                 | Begin ATOMIC sequence                                                               | 2     |

| EXTR                   | Begin EXTended Register sequence                                                    | 2     |

| EXTP(R)                | Begin EXTended Page (and Register) sequence                                         | 2/4   |

| EXTS(R)                | Begin EXTended Segment (and Register) sequence                                      | 2/4   |

| NOP                    | Null operation                                                                      | 2     |

| Table 7 CTOTCS negisters, Ordered by Marile (Contra) |                             |                     |                 |                                    |                                         |                   |  |  |  |

|------------------------------------------------------|-----------------------------|---------------------|-----------------|------------------------------------|-----------------------------------------|-------------------|--|--|--|

| Name                                                 |                             | Physical<br>Address |                 | 8-Bit<br>Addr.                     | Description                             | Reset<br>Value    |  |  |  |

| XP3IC                                                | XP3IC b F19E <sub>H</sub> E |                     | CF <sub>H</sub> | RTC/PLL Interrupt Control Register | 0000 <sub>H</sub>                       |                   |  |  |  |

| XPERCON                                              |                             | F024 <sub>H</sub>   | Ε               | 12 <sub>H</sub>                    | X-Peripheral Control Register           | 0401 <sub>H</sub> |  |  |  |

| ZEROS                                                | b                           | FF1C <sub>H</sub>   |                 | 8E <sub>H</sub>                    | Constant Value 0's Register (read only) | 0000 <sub>H</sub> |  |  |  |

### Table 7 C167CS Registers, Ordered by Name (cont'd)

<sup>1)</sup> The system configuration is selected during reset.

<sup>2)</sup> The reset value depends on the indicated reset source.

### **Absolute Maximum Ratings**

| Parameter                                                                  | Symbol            | Limit | Values                | Unit | Notes      |  |

|----------------------------------------------------------------------------|-------------------|-------|-----------------------|------|------------|--|

|                                                                            |                   | min.  | max.                  |      |            |  |

| Storage temperature                                                        | T <sub>ST</sub>   | -65   | 150                   | °C   | -          |  |

| Junction temperature                                                       | TJ                | -40   | 150                   | °C   | under bias |  |

| Voltage on $V_{\text{DD}}$ pins with respect to ground ( $V_{\text{SS}}$ ) | V <sub>DD</sub>   | -0.5  | 6.5                   | V    | -          |  |

| Voltage on any pin with respect to ground $(V_{SS})$                       | V <sub>IN</sub>   | -0.5  | V <sub>DD</sub> + 0.5 | V    | -          |  |

| Input current on any pin during overload condition                         | -                 | -10   | 10                    | mA   | -          |  |

| Absolute sum of all input<br>currents during overload<br>condition         | -                 | -     | 100                   | mA   | -          |  |

| Power dissipation                                                          | P <sub>DISS</sub> | -     | 1.5                   | W    | -          |  |

## Table 8 Absolute Maximum Rating Parameters

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

#### Parameter Interpretation

The parameters listed in the following partly represent the characteristics of the C167CS and partly its demands on the system. To aid in interpreting the parameters right, when evaluating them for a design, they are marked in column "Symbol":

CC (Controller Characteristics):

The logic of the C167CS will provide signals with the respective characteristics.

**SR** (System Requirement):

The external system must provide signals with the respective characteristics to the C167CS.

#### DC Characteristics

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                            | Sym              | bol | Limit                        | Values                       | Unit | <b>Test Condition</b>          |  |

|------------------------------------------------------|------------------|-----|------------------------------|------------------------------|------|--------------------------------|--|

|                                                      |                  |     | min.                         | max.                         |      |                                |  |

| Input low voltage (TTL,<br>all except XTAL1)         | $V_{IL}$         | SR  | -0.5                         | 0.2 V <sub>DD</sub><br>- 0.1 | V    | _                              |  |

| Input low voltage XTAL1                              | $V_{IL2}$        | SR  | -0.5                         | 0.3 V <sub>DD</sub>          | V    | _                              |  |

| Input low voltage<br>(Special Threshold)             | V <sub>ILS</sub> | SR  | -0.5                         | 2.0                          | V    | _                              |  |

| Input high voltage (TTL, all except RSTIN and XTAL1) | $V_{IH}$         | SR  | 0.2 V <sub>DD</sub><br>+ 0.9 | V <sub>DD</sub> + 0.5        | V    | _                              |  |

| Input high voltage RSTIN<br>(when operated as input) | V <sub>IH1</sub> | SR  | 0.6 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | -                              |  |

| Input high voltage XTAL1                             | V <sub>IH2</sub> | SR  | 0.7 V <sub>DD</sub>          | V <sub>DD</sub> + 0.5        | V    | -                              |  |

| Input high voltage<br>(Special Threshold)            | V <sub>IHS</sub> | SR  | 0.8 V <sub>DD</sub><br>- 0.2 | V <sub>DD</sub> + 0.5        | V    | -                              |  |

| Input Hysteresis<br>(Special Threshold)              | HYS              |     | 400                          | -                            | mV   | Series resistance = 0 $\Omega$ |  |

| Output low voltage <sup>2)</sup>                     | $V_{OL}$         | CC  | _                            | 1.0                          | V    | $I_{OL} \le I_{OLmax}^{3)}$    |  |

|                                                      |                  |     | _                            | 0.45                         | V    | $I_{OL} \le I_{OLnom}^{3)4)}$  |  |

| Output high voltage <sup>5)</sup>                    | V <sub>OH</sub>  | CC  | V <sub>DD</sub> -<br>1.0     | -                            | V    | $I_{OH} \ge I_{OHmax}^{3)}$    |  |

|                                                      |                  |     | V <sub>DD</sub> -<br>0.45    | -                            | V    | $I_{OH} \ge I_{OHnom}^{3)4)$   |  |

| Input leakage current (Port 5)                       | I <sub>OZ1</sub> | CC  | _                            | ±200                         | nA   | $0 V < V_{IN} < V_{DD}$        |  |

## **DC Characteristics** (cont'd)

(Operating Conditions apply)<sup>1)</sup>

| Parameter                                                  | Symbol                          | Limit | Values | Unit | <b>Test Condition</b>                         |

|------------------------------------------------------------|---------------------------------|-------|--------|------|-----------------------------------------------|

|                                                            |                                 | min.  | max.   |      |                                               |

| Input leakage current (all other)                          | I <sub>OZ2</sub> CC             | _     | ±500   | nA   | 0.45 V < V <sub>IN</sub><br>< V <sub>DD</sub> |

| RSTIN inactive current <sup>6)</sup>                       | I <sub>RSTH</sub> <sup>7)</sup> | _     | -10    | μA   | $V_{\rm IN} = V_{\rm IH1}$                    |

| RSTIN active current <sup>6)</sup>                         | I <sub>RSTL</sub> <sup>8)</sup> | -100  | -      | μA   | $V_{\rm IN} = V_{\rm IL}$                     |

| READY/RD/WR inact. current <sup>9)</sup>                   | I <sub>RWH</sub> <sup>7)</sup>  | _     | -40    | μA   | $V_{OUT}$ = 2.4 V                             |

| READY/RD/WR active current <sup>9)</sup>                   | I <sub>RWL</sub> <sup>8)</sup>  | -500  | -      | μA   | $V_{OUT} = V_{OLmax}$                         |

| ALE inactive current <sup>9)</sup>                         | I <sub>ALEL</sub> <sup>7)</sup> | _     | 40     | μA   | $V_{OUT} = V_{OLmax}$                         |

| ALE active current <sup>9)</sup>                           | I <sub>ALEH</sub> <sup>8)</sup> | 500   | -      | μA   | $V_{OUT} = 2.4 \text{ V}$                     |

| Port 6 inactive current <sup>9)</sup>                      | I <sub>P6H</sub> <sup>7)</sup>  | _     | -40    | μA   | $V_{OUT} = 2.4 \text{ V}$                     |

| Port 6 active current <sup>9)</sup>                        | I <sub>P6L</sub> <sup>8)</sup>  | -500  | -      | μA   | $V_{OUT} = V_{OL1max}$                        |

| PORT0 configuration current <sup>10)</sup>                 | I <sub>P0H</sub> <sup>7)</sup>  | _     | -10    | μA   | $V_{\rm IN} = V_{\rm IHmin}$                  |

|                                                            | I <sub>P0L</sub> <sup>8)</sup>  | -100  | -      | μA   | $V_{\rm IN} = V_{\rm ILmax}$                  |

| XTAL1 input current                                        | I <sub>IL</sub> CC              | _     | ±20    | μA   | $0 V < V_{IN} < V_{DD}$                       |

| Pin capacitance <sup>11)</sup><br>(digital inputs/outputs) | C <sub>IO</sub> CC              | _     | 10     | pF   | f = 1  MHz<br>$T_A = 25 \text{ °C}$           |

<sup>1)</sup> Keeping signal levels within the levels specified in this table, ensures operation without overload conditions. For signal levels outside these specifications also refer to the specification of the overload current  $I_{OV}$ .

<sup>2)</sup> For pin RSTIN this specification is only valid in bidirectional reset mode.

<sup>3)</sup> The maximum deliverable output current of a port driver depends on the selected output driver mode, see **Table 10, Current Limits for Port Output Drivers**. The limit for pin groups must be respected.

- <sup>4)</sup> As a rule, with decreasing output current the output levels approach the respective supply level ( $V_{OL} \rightarrow V_{SS}$ ,  $V_{OH} \rightarrow V_{DD}$ ). However, only the levels for nominal output currents are guaranteed.

- <sup>5)</sup> This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- <sup>6)</sup> These parameters describe the  $\overline{\text{RSTIN}}$  pullup, which equals a resistance of ca. 50 to 250 k $\Omega$ .

- <sup>7)</sup> The maximum current may be drawn while the respective signal line remains inactive.

- <sup>8)</sup> The minimum current must be drawn in order to drive the respective signal line active.

- <sup>9)</sup> This specification is valid during Reset and during Hold-mode or Adapt-mode. During Hold-mode Port 6 pins are only affected, if they are used (configured) for CS output and the open drain function is not enabled. The READY-pullup is always active, except for Powerdown mode.

- <sup>10)</sup> This specification is valid during Reset and during Adapt-mode.

- <sup>11)</sup> Not 100% tested, guaranteed by design and characterization.

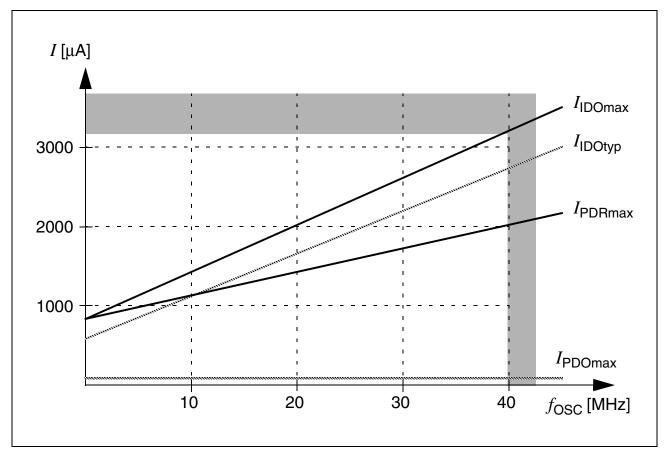

Figure 9 Idle and Power Down Supply Current as a Function of Oscillator Frequency

## A/D Converter Characteristics

(Operating Conditions apply)

| Parameter                                       | Symbol            |                  | Limit                 | Values                                        | Unit | Test                                           |  |

|-------------------------------------------------|-------------------|------------------|-----------------------|-----------------------------------------------|------|------------------------------------------------|--|

|                                                 |                   |                  | min.                  | max.                                          |      | Condition                                      |  |

| Analog reference supply                         | VAREF             | SR               | 4.0                   | V <sub>DD</sub> + 0.1                         | V    | 1)                                             |  |

| Analog reference ground                         | VAGNE             | SR               | V <sub>SS</sub> - 0.1 | $V_{\rm SS}$ + 0.2                            | V    | -                                              |  |

| Analog input voltage range                      | $V_{AIN}$         | SR               | V <sub>AGND</sub>     | V <sub>AREF</sub>                             | V    | 2)                                             |  |

| Basic clock frequency                           | f <sub>BC</sub>   |                  | 0.5                   | 6.25                                          | MHz  | 3)                                             |  |

| Conversion time                                 | t <sub>C</sub>    | CC               | -                     | $40 t_{\rm BC} + t_{\rm S} \\ + 2t_{\rm CPU}$ | -    | 4)<br>$t_{CPU} = 1/f_{CPU}$                    |  |

| Calibration time after reset                    | t <sub>CAL</sub>  | CC               | -                     | 3328 t <sub>BC</sub>                          | _    | 5)                                             |  |

| Total unadjusted error                          | TUE               | CC <sup>1)</sup> | _                     | ±2                                            | LSB  | Channels<br>0 15                               |  |

|                                                 |                   |                  | _                     | ±10                                           | LSB  | Channels<br>16 23                              |  |

| Internal resistance of reference voltage source | R <sub>AREF</sub> | SR               | _                     | t <sub>BC</sub> /60<br>- 0.25                 | kΩ   | <i>t</i> <sub>BC</sub> in [ns] <sup>6)7)</sup> |  |

| Internal resistance of analog source            | R <sub>ASRC</sub> | ; SR             | _                     | t <sub>S</sub> /450<br>- 0.25                 | kΩ   | t <sub>S</sub> in [ns] <sup>7)8)</sup>         |  |

| ADC input capacitance                           | $C_{AIN}$         | CC               | -                     | 33                                            | pF   | 7)                                             |  |

#### Table 13 A/D Converter Characteristics

<sup>1)</sup> TUE is tested at  $V_{AREF} = 5.0 \text{ V}$ ,  $V_{AGND} = 0 \text{ V}$ ,  $V_{DD} = 4.9 \text{ V}$ . It is guaranteed by design for all other voltages within the defined voltage range.

If the analog reference supply voltage exceeds the power supply voltage by up to 0.2 V

(i.e.  $V_{AREF} = V_{DD} = +0.2 \text{ V}$ ) the maximum TUE is increased to  $\pm 3/11 \text{ LSB}$ . This range is not 100% tested. The specified TUE is guaranteed only if the absolute sum of input overload currents on Port 5 pins and P1H pins (see  $I_{OV}$  specification) does not exceed 10 mA.

During the reset calibration sequence the maximum TUE may be  $\pm$ 4 LSB ( $\pm$ 12 LSB for channels 16 ... 23).

- <sup>2)</sup> V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- <sup>3)</sup> The limit values for  $f_{BC}$  must not be exceeded when selecting the CPU frequency and the ADCTC setting.

- <sup>4)</sup> This parameter includes the sample time  $t_{S}$ , the time for determining the digital result and the time to load the result register with the conversion result.

Values for the basic clock  $t_{BC}$  depend on programming and can be taken from Table 14.

This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

| Parameter                                                                                  |                         | bol | Li   | Unit            |    |

|--------------------------------------------------------------------------------------------|-------------------------|-----|------|-----------------|----|

|                                                                                            |                         |     | min. | max.            |    |

| Output delay from CLKOUT falling edge<br>Valid for: address (MUX on PORT0), write data out | <i>tc</i> <sub>10</sub> | CC  | 0    | 14              | ns |

| Output delay from CLKOUT edge Valid for: latched $\overline{CS}$ , ALE (normal)            | <i>tc</i> <sub>11</sub> | CC  | -3   | 6               | ns |

| Output delay from CLKOUT edge<br>Valid for: WR, WRL, WRH, WrCS                             | <i>tc</i> <sub>12</sub> | CC  | -4   | 7               | ns |

| Output delay from CLKOUT edge<br>Valid for: RD, RdCS                                       | tc <sub>13</sub>        | CC  | -2   | 7               | ns |

| Input setup time to CLKOUT falling edge<br>Valid for: read data in                         | <i>tc</i> <sub>14</sub> | SR  | 10   | -               | ns |

| Input hold time after CLKOUT falling edge Valid for: read data in <sup>1)</sup>            | tc <sub>15</sub>        | SR  | 0    | -               | ns |

| Output delay from CLKOUT falling edge<br>Valid for: address (on PORT1 and/or P4), BHE      | <i>tc</i> <sub>16</sub> | CC  | 0    | 9 <sup>2)</sup> | ns |

| Output hold time after CLKOUT falling edge Valid for: address, BHE <sup>3)</sup>           | <i>tc</i> <sub>17</sub> | CC  | -2   | 8               | ns |

| Output hold time after CLKOUT edge <sup>4)</sup><br>Valid for: write data out              | <i>tc</i> <sub>18</sub> | CC  | -1   | -               | ns |

| Output delay from CLKOUT falling edge Valid for: ALE (extended), early $\overline{CS}$     | <i>tc</i> <sub>19</sub> | CC  | -4   | 4               | ns |

| Turn off delay after CLKOUT edge <sup>4)</sup><br>Valid for: write data out                | <i>tc</i> <sub>20</sub> | CC  | -    | 7               | ns |

| Turn on delay after CLKOUT falling edge <sup>4)</sup><br>Valid for: write data out         | <i>tc</i> <sub>21</sub> | CC  | -5   | -               | ns |

| Output hold time after CLKOUT edge Valid for: early $\overline{CS}$                        | tc <sub>22</sub>        | CC  | -6   | 4               | ns |

#### Table 17 External Bus Cycle Timing (Operating Conditions apply)

1) Read data are latched with the same (internal) clock edge that triggers the address change and the rising edge of RD. Therefore address changes before the end of RD have no impact on (demultiplexed) read cycles.

<sup>2)</sup> If the capacitive load on the respective output pins is limited to 30 pF the maximum output delay  $tc_{16}$  can be reduced to 8 ns.

<sup>3)</sup> Due to comparable propagation delays the address does not change before  $\overline{\text{WR}}$  goes high. The minimum output delay ( $tc_{17\text{min}}$ ) is therefore the actual value of  $tc_{12}$ .

<sup>4)</sup> Not 100% tested, guaranteed by design and characterization.

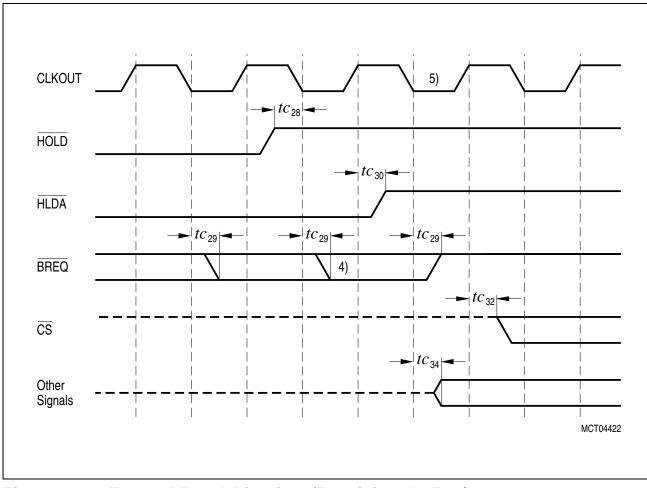

## **External Bus Arbitration**

#### Table 20Bus Arbitration Timing (Operating Conditions apply)

| Parameter                                    |                         | Symbol |      | Limit Values |    |

|----------------------------------------------|-------------------------|--------|------|--------------|----|

|                                              |                         |        | min. | max.         |    |

| HOLD input setup time to CLKOUT falling edge | tc <sub>28</sub>        | SR     | 14   | -            | ns |

| CLKOUT to BREQ delay                         | tc <sub>29</sub>        | CC     | -3   | 6            | ns |

| CLKOUT to HLDA delay                         | <i>tc</i> <sub>30</sub> | CC     | -2   | 6            | ns |

| CSx release <sup>1)</sup>                    | <i>tc</i> <sub>31</sub> | CC     | 0    | 10           | ns |

| CSx drive                                    | tc <sub>32</sub>        | CC     | -3   | 4            | ns |

| Other signals release <sup>1)</sup>          | tc <sub>33</sub>        | CC     | 0    | 10           | ns |

| Other signals drive <sup>1)</sup>            | tc <sub>34</sub>        | CC     | 0    | 6            | ns |

<sup>1)</sup> Not 100% tested, guaranteed by design and characterization.

Figure 23 External Bus Arbitration, (Regaining the Bus)

#### Notes

<sup>4)</sup> This is the last chance for BREQ to trigger the indicated regain-sequence. Even if BREQ is activated earlier, the regain-sequence is initiated by HOLD going high. Please note that HOLD may also be deactivated without the C167CS requesting the bus.

<sup>5)</sup> The next C167CS driven bus cycle may start here.

# Infineon goes for Business Excellence

"Business excellence means intelligent approaches and clearly defined processes, which are both constantly under review and ultimately lead to good operating results.

Better operating results and business excellence mean less idleness and wastefulness for all of us, more professional success, more accurate information, a better overview and, thereby, less frustration and more satisfaction."

Dr. Ulrich Schumacher

http://www.infineon.com