#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 21                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 12x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                    |

| Supplier Device Package    | 28-SSOP                                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpm028t-i-ss |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MM0256GPM064 FAMILY

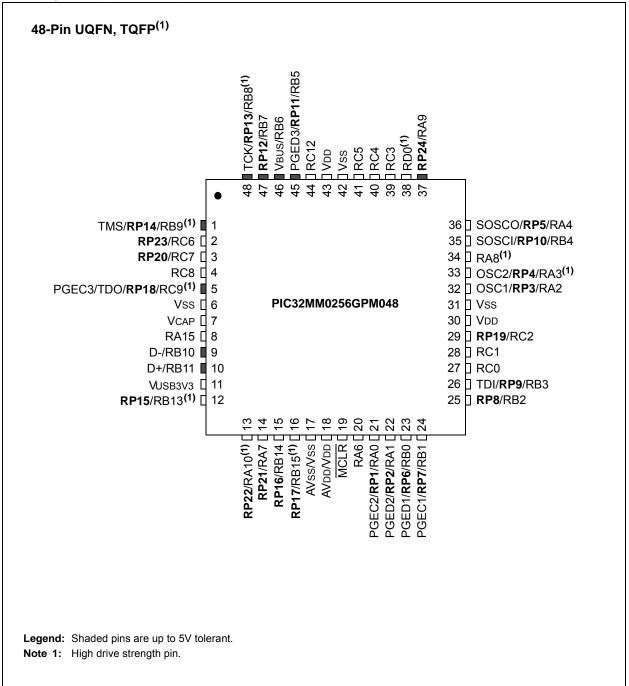

#### **Pin Diagrams (Continued)**

NOTES:

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|----------------------------------|-------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0 R/W-0            |                   | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | NVMADDR<31:24> <sup>(1)</sup>    |       |                   |                   |                        |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | NVMADDR<23:16> <sup>(1)</sup>    |       |                   |                   |                        |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | NVMADDR<15:8> <sup>(1)</sup>     |       |                   |                   |                        |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0                  | R/W-0 R/W-0       |                  | R/W-0            |  |  |  |  |  |

| 7:0          |                                  |       |                   | NVMADI            | DR<7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |  |

#### REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

### Legend:

| Logona.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-0 NVMADDR<31:0>: Flash Address bits<sup>(1)</sup>

| NVMOP<3:0><br>Selection | Flash Address Bits (NVMADDR<31:0>)                                                                                              |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Page Erase              | Address identifies the page to erase (NVMADDR<10:0> are ignored).                                                               |

| Row Program             | Address identifies the row to program (NVMADDR<7:0> are ignored).                                                               |

| Double-Word Program     | Address identifies the double-word (64-bit) to program<br>(NVMADDR<2:0> bits are ignored). <b>Note:</b> Must be 64-bit aligned. |

## **Note 1:** For all other NVMOP<3:0> bits settings, the Flash address is ignored. See the NVMCON register (Register 5-1) for additional information on these bits.

| Note: | The bits in this register are only reset by a Power-on Reset (POR) and are not affected by other Reset sources. |

|-------|-----------------------------------------------------------------------------------------------------------------|

|-------|-----------------------------------------------------------------------------------------------------------------|

| Bit         Bit         Bit           Range         31/23/15/7         30/22/1 |     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------------------------------------------------------------------------|-----|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04                                                                          | U-0 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24                                                                          |     | _                 | _                 | —                 | _                 | _                 | —                | _                |

| 22:16                                                                          | U-0 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16                                                                          |     | _                 |                   | —                 | _                 | —                 | —                | —                |

| 15.0                                                                           | U-0 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8                                                                           |     | _                 |                   | —                 | _                 |                   | —                | —                |

| 7.0                                                                            | U-0 | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0                                                                            | _   | _                 | _                 | —                 | RDWR              | [                 | DMACH<2:0>       | •                |

#### REGISTER 8-2: DMASTAT: DMA STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-4 Unimplemented: Read as '0'

bit 3 RDWR: DMA Read/Write Status bit

1 = Last DMA bus access was a read

0 = Last DMA bus access was a write

## bit 2-0 DMACH<2:0>: DMA Channel bits

These bits contain the value of the most recent active DMA channel.

#### REGISTER 8-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit Bit 31/23/15/7 30/22/14/6 |     |     |        |        |     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------------------|-----|-----|--------|--------|-----|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | R-0                           | R-0 | R-0 | R-0    | R-0    | R-0 | R-0               | R-0              |                  |  |  |  |  |  |

| 31:24        | DMAADDR<31:24>                |     |     |        |        |     |                   |                  |                  |  |  |  |  |  |

| 00.40        | R-0                           | R-0 | R-0 | R-0    | R-0    | R-0 | R-0               | R-0              |                  |  |  |  |  |  |

| 23:16        | DMAADDR<23:16>                |     |     |        |        |     |                   |                  |                  |  |  |  |  |  |

| 15.0         | R-0                           | R-0 | R-0 | R-0    | R-0    | R-0 | R-0               | R-0              |                  |  |  |  |  |  |

| 15:8         | DMAADDR<15:8>                 |     |     |        |        |     |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0                           | R-0 | R-0 | R-0    | R-0    | R-0 | R-0               | R-0              |                  |  |  |  |  |  |

| 7:0          |                               |     |     | DMAADD | R<7:0> |     |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        |                   |                       |                   | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                     | _                 | _                 | —                  | _                 | -                | —                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0 R/W-0        |                   | R/W-0            | R/W-0            |

| 15:8         | —                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0 R/W-0       |                  | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | —                 | —                  | (                 | CRCCH<2:0>       |                  |

#### REGISTER 8-4: DCRCCON: DMA CRC CONTROL REGISTER

#### Legend:

| · <b>J</b> · · ·  |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-30 Unimplemented: Read as '0'

bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (reverse source byte order)

- 00 = No swapping (source byte order)

#### bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered, as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

- When CRCTYP (DCRCCON<5>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (not reflected)

- When CRCTYP (DCRCCON<5>) = 0 (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits

When CRCTYP (DCRCCON<5>) = 1 (CRC module is in IP Header mode):

These bits are unused.

When CRCTYP (DCRCCON<5>) = 0 (CRC module is in LFSR mode):

- Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- bit 6 CRCAPP: CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but not to the destination; when a block transfer completes, the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC, obeying WBO as it writes the data to the destination

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

#### 10.10 I/O Ports Control Registers

#### TABLE 10-5: PORTA REGISTER MAP

| ess (                       |                                 | Bits          |                               |       |       |          |                   |        |      |      |                            |                      |      |      |      |      |       |      |               |

|-----------------------------|---------------------------------|---------------|-------------------------------|-------|-------|----------|-------------------|--------|------|------|----------------------------|----------------------|------|------|------|------|-------|------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                         | 30/14 | 29/13 | 28/12    | 27/11             | 26/10  | 25/9 | 24/8 | 23/7                       | 22/6                 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All<br>Resets |

| 0000                        |                                 | 31:16         | —                             | —     | —     | _        | _                 | _      | —    | —    | —                          | _                    | _    | —    | —    | —    | —     | _    | 0000          |

| 2BB0 ANSEL                  | ANSELA                          | 15:0          | _                             | _     | A     | NSA<13:1 | 1> <sup>(2)</sup> | _      | _    | _    |                            | ANSA6 <sup>(2)</sup> | _    |      |      | ANSA | <3:0> |      | 000F          |

| 2BC0                        | TRISA                           | 31:16         | —                             | _     | —     | _        | _                 | _      | —    | _    |                            | _                    | _    |      | _    |      | _     |      | 0000          |

| 2000                        | IRISA                           | 15:0          |                               |       |       |          |                   |        |      |      |                            |                      |      |      |      | 021F |       |      |               |

| 2BD0                        | PORTA                           | 31:16         | —                             | —     | —     | —        | —                 | —      | —    |      | —                          | —                    | _    | —    | —    | —    | —     | —    | 0000          |

| 2000                        | 1 OKIA                          | 15:0          |                               |       |       |          |                   |        |      | RA   | <15:0> <sup>(3)</sup>      |                      |      |      |      |      |       |      | xxxx          |

| 2BE0                        | LATA                            | 31:16         | —                             |       | —     | —        | —                 | —      | —    |      | —                          | —                    | —    | —    | —    | —    | —     | —    | 0000          |

| LDLU                        | <b>D</b> (1) (                  | 15:0          | LATA<15:0> <sup>(3)</sup> 000 |       |       |          |                   |        |      |      |                            | 0000                 |      |      |      |      |       |      |               |

| 2BF0                        | ODCA                            | 31:16         | _                             |       | —     | —        | —                 | —      | —    |      | —                          | —                    | —    | —    | —    | —    |       | —    | 0000          |

|                             |                                 | 15:0          |                               |       |       |          |                   |        |      | ODC  | A<15:0> <sup>(3)</sup>     |                      |      |      |      |      |       |      | 0000          |

| 2C00                        | CNPUA                           | 31:16         | —                             |       | —     | —        | —                 | —      | —    |      |                            | —                    | —    | —    | —    | —    | —     | —    | 0000          |

|                             |                                 | 15:0          |                               |       |       |          |                   |        |      | CNPL | JA<15:0> <sup>(3</sup>     | 5)<br>               |      |      |      |      |       |      | 0000          |

| 2C10                        | CNPDA                           | 31:16         | _                             |       | —     | —        | —                 | —      | —    |      |                            |                      | —    | —    | —    | —    |       | _    | 0000          |

|                             |                                 | 15:0          |                               |       |       |          |                   |        |      | CNP  | DA<15:0> <sup>(4</sup>     | .)                   |      |      |      |      |       |      | 0000          |

| 2C20                        | CNCONA                          | 31:16         | -                             |       |       |          | —                 | —      | _    |      | _                          | _                    | _    |      | _    |      |       |      | 0000          |

|                             |                                 | 15:0          | ON                            |       |       |          | CNSTYLE           | PORT32 |      |      | _                          |                      |      | _    |      |      |       |      | 0000          |

| 2C30                        | CNEN0A                          | 31:16         |                               |       | _     |          |                   |        |      |      | -                          |                      |      |      |      |      |       |      | 0000          |

|                             |                                 | 15:0<br>31:16 |                               |       |       |          |                   |        |      |      | 0A<15:0> <sup>(3</sup>     | ,                    |      |      |      |      |       |      | 0000          |

| 2C40                        | CNSTATA                         | 15:0          | —                             |       | _     | _        | _                 | —      | _    |      | <br>ATA<15:0>              | (3)                  | —    |      | —    | _    | —     |      | 0000          |

|                             |                                 | 31:16         |                               |       | _     |          |                   | _      | _    |      |                            | _                    | _    |      |      | _    | _     | _    | 0000          |

| 2C50                        | CNEN1A                          | 15:0          |                               |       |       |          |                   |        |      |      | <br>1A<15:0> <sup>(3</sup> |                      |      |      |      |      |       |      | 0000          |

|                             |                                 | 31:16         |                               |       | _     |          | _                 | _      | _    |      |                            | _                    |      | _    | _    | _    | _     | _    | 0000          |

| 2C60                        | CNFA                            | 15:0          |                               |       |       |          |                   |        |      |      | <br>A<15:0> <sup>(3)</sup> |                      |      |      |      |      |       |      | 0000          |

|                             |                                 | 10.0          |                               |       |       |          |                   |        |      |      |                            |                      |      |      |      |      |       |      | 3000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

2: These bits are not available on 48, 36 or 28-pin devices.

3: Bits<14:11> are not available on 48-pin devices; bits<15:10> and bits<8:5> are not available on 36-pin devices.

4: Bits<15:5> are not available on 28-pin devices.

DS60001387C-page 120

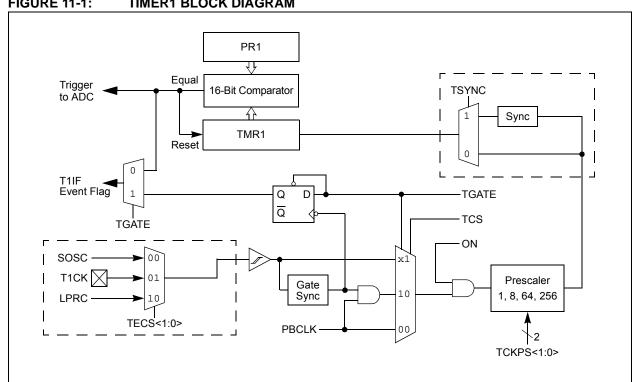

#### 11.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS60001105) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

PIC32MM0256GPM064 family devices feature one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can be clocked from different sources, such as the Peripheral Bus Clock (PBCLK), Secondary Oscillator (SOSC), T1CK pin or LPRC oscillator.

The following modes are supported by Timer1:

- · Synchronous Internal Timer

- · Synchronous Internal Gated Timer

- Synchronous External Timer

- · Asynchronous External Timer

The timer has a selectable clock prescaler and can operate in Sleep and Idle modes.

#### FIGURE 11-1: **TIMER1 BLOCK DIAGRAM**

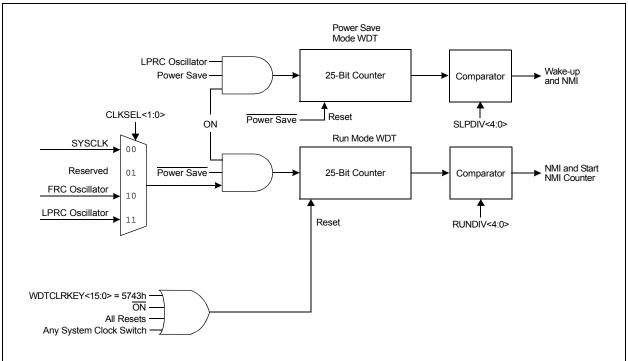

### 13.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- · Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

#### FIGURE 13-1: WATCHDOG TIMER BLOCK DIAGRAM

#### REGISTER 15-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty

Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

#### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Set when CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

#### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

# 16.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS61116) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard.

Each I<sup>2</sup>C module has a 2-pin interface:

- SCLx pin is clock

- · SDAx pin is data

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C Interface Supporting Both Master and Slave Operation

- I<sup>2</sup>C Slave mode Supports 7-Bit and 10-Bit Addressing

- I<sup>2</sup>C Master mode Supports 7-Bit and 10-Bit Addressing

- I<sup>2</sup>C Port allows Bidirectional Transfers between Master and Slaves

- Serial Clock Synchronization for the I<sup>2</sup>C Port can be used as a Handshake Mechanism to Suspend and Resume Serial Transfer (SCLREL control)

- I<sup>2</sup>C Supports Multi-Master Operation; Detects Bus Collision and Arbitrates Accordingly

- · Provides Support for Address Bit Masking

- SMBus Support

Figure 16-1 illustrates the I<sup>2</sup>C module block diagram.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | —                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R-0, HSC          | R-0, HSC          | R/C-0, HSC        | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | ACKTIM            | —                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D/A               | Р                 | S                 | R/W               | RBF              | TBF              |

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER

| Legend:           | HS = Hardware Settable bit | HSC = Hardware Settable/Clearable bit  |  |  |  |  |

|-------------------|----------------------------|----------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0'     |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared C = Clearable bit |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

| bit 15    | ACKSTAT: Acknowledge Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                               |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = NACK received from slave                                                                                                                                                                       |

|           | 0 = ACK received from slave                                                                                                                                                                        |

|           | Hardware is set or clear at the end of slave Acknowledge.                                                                                                                                          |

| bit 14    | <b>TRSTAT:</b> Transmit Status bit (when operating as I <sup>2</sup> C master, applicable to master transmit operation)                                                                            |

|           | 1 = Master transmit is in progress (8 bits + ACK)                                                                                                                                                  |

|           | 0 = Master transmit is not in progress                                                                                                                                                             |

| 1.1.40    | Hardware is set at the beginning of master transmission. Hardware is clear at the end of slave Acknowledge.                                                                                        |

| bit 13    | ACKTIM: Acknowledge Time Status bit (valid in I <sup>2</sup> C Slave mode only)                                                                                                                    |

|           | <ul> <li>1 = I<sup>2</sup>C bus is in an Acknowledge sequence, set on 8th falling edge of SCLx clock</li> <li>0 = Not an Acknowledge sequence, cleared on 9th rising edge of SCLx clock</li> </ul> |

| bit 12-11 | Unimplemented: Read as '0'                                                                                                                                                                         |

| bit 10    | BCL: Master Bus Collision Detect bit                                                                                                                                                               |

|           | 1 = A bus collision has been detected during a master operation                                                                                                                                    |

|           | 0 = No collision<br>Hardware is set at detection of a bus collision.                                                                                                                               |

|           |                                                                                                                                                                                                    |

| bit 9     | GCSTAT: General Call Status bit                                                                                                                                                                    |

|           | 1 = General call address was received<br>0 = General call address was not received                                                                                                                 |

|           | Hardware is set when the address matches the general call address. Hardware is clear at Stop detection.                                                                                            |

| bit 8     | ADD10: 10-Bit Address Status bit                                                                                                                                                                   |

| bit 0     | 1 = 10-bit address was matched                                                                                                                                                                     |

|           | 0 = 10-bit address was not matched                                                                                                                                                                 |

|           | Hardware is set at match of the 2nd byte of matched 10-bit address. Hardware is clear at Stop detection.                                                                                           |

| bit 7     | IWCOL: I2Cx Write Collision Detect bit                                                                                                                                                             |

|           | 1 = An attempt to write to the I2CxTRN register failed because the I <sup>2</sup> C module is busy                                                                                                 |

|           | 0 = No collision                                                                                                                                                                                   |

|           | Hardware is set at occurrence of a write to I2CxTRN while busy (cleared by software).                                                                                                              |

| bit 6     | I2COV: I2Cx Receive Overflow Flag bit                                                                                                                                                              |

|           | <ul> <li>1 = A byte was received while the I2CxRCV register is still holding the previous byte</li> <li>0 = No overflow</li> </ul>                                                                 |

|           | Hardware is set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).                                                                                                                   |

|           |                                                                                                                                                                                                    |

|           |                                                                                                                                                                                                    |

#### REGISTER 16-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 5 | <b>D/A:</b> Data/Address bit (when operating as I <sup>2</sup> C slave)                                        |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | 1 = Indicates that the last byte received was data                                                             |

|       | 0 = Indicates that the last byte received was a device address                                                 |

|       | Hardware is clear at a device address match. Hardware is set by reception of a slave byte.                     |

| bit 4 | P: Stop bit                                                                                                    |

|       | 1 = Indicates that a Stop bit has been detected last                                                           |

|       | 0 = Stop bit was not detected last                                                                             |

|       | Hardware is set or clear when Start, Repeated Start or Stop is detected.                                       |

| bit 3 | S: Start bit                                                                                                   |

|       | 1 = Indicates that a Start (or Repeated Start) bit has been detected last                                      |

|       | 0 = Start bit was not detected last                                                                            |

|       | Hardware is set or clear when Start, Repeated Start or Stop is detected.                                       |

| bit 2 | <b>R/W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)                              |

|       | 1 = Read – Indicates data transfer is output from slave                                                        |

|       | 0 = Write – Indicates data transfer is input to slave                                                          |

|       | Hardware is set or clear after reception of an I <sup>2</sup> C device address byte.                           |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                            |

|       | 1 = Receive is complete, I2CxRCV is full                                                                       |

|       | 0 = Receive is not complete, I2CxRCV is empty                                                                  |

|       | Hardware is set when I2CxRCV is written with the received byte. Hardware is clear when software reads I2CxRCV. |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                           |

|       | 1 = Transmit is in progress, I2CxTRN is full                                                                   |

|       |                                                                                                                |

0 = Transmit is complete, I2CxTRN is empty

Hardware is set when software writes to I2CxTRN. Hardware is clear at completion of the data transmission.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | —                 | —                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7:0          | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            |                  | VBUSVD           |

#### REGISTER 18-3: U1OTGSTAT: USB OTG STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "Type B" cable has been inserted into the USB receptacle 0 = A "Type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has been stable for the previous 1 ms

- 0 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has not been stable for the previous 1 ms

- bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = The VBUS voltage is above VA\_SESS\_VLD (as defined in the USB OTG Specification) on the A or B-device 0 = The VBUS voltage is below VA\_SESS\_VLD on the A or B-device

- bit 2 SESEND: B-Device Session End Indicator bit

1 = The VBUS voltage is above VB\_SESS\_END (as defined in the USB OTG Specification) on the B-device 0 = The VBUS voltage is below VB\_SESS\_END on the B-device

#### bit 1 Unimplemented: Read as '0'

bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

1 = The VBUS voltage is above VA\_VBUS\_VLD (as defined in the USB OTG Specification) on the A-device 0 = The VBUS voltage is below VA\_VBUS\_VLD on the A-device

#### REGISTER 19-1: RTCCON1: RTCC CONTROL 1 REGISTER (CONTINUED)

- bit 11 WRLOCK: RTCC Registers Write Lock bit

- 1 = Registers associated with accurate timekeeping are locked

- 0 = Registers associated with accurate timekeeping may be written to by user

- bit 10-8 Unimplemented: Read as '0'

- bit 7 RTCOE: RTCC Output Enable bit

1 = RTCC clock output is enabled; signal selected by OUTSEL<2:0> is presented on the RTCC pin 0 = RTCC clock output is disabled

- bit 6-4 OUTSEL<2:0>: RTCC Signal Output Selection bits

- 111 = Reserved

•••

- 011 = Reserved

- 010 = RTCC input clock source (user-defined divided output based on the combination of the RTCCON2 bits, DIV<15:0> and PS<1:0>)

- 001 = Seconds clock

- 000 = Alarm event

- bit 3-0 Unimplemented: Read as '0'

- **Note 1:** The counter decrements on any alarm event. The counter is prevented from rolling over from '00' to 'FF' unless CHIME = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 31:24        |                   |                   |                   | USERIE            | RID<15:8>         |                   |                  |                  |  |

| 00.40        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        |                   |                   |                   | USERI             | D<7:0>            |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 15:8         | FVBUSIO           | FUSBIDIO          | _                 | —                 | —                 | _                 |                  | _                |  |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | r-1               | r-1              | r-1              |  |

| 7:0          |                   |                   |                   | ALTI2C            | SOSCHP            |                   | _                |                  |  |

#### REGISTER 26-1: FDEVOPT/AFDEVOPT: DEVICE OPTIONS CONFIGURATION REGISTER

| Legend: |                   | r = Reserved bit | P = Programmable bit                    |

|---------|-------------------|------------------|-----------------------------------------|

|         | R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|         | -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

bit 31-16 USERID<15:0>: User ID bits (2 bytes which can programmed to any value)

- bit 15 FVBUSIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 14 FUSBIDIO: USB USBID Selection bit

- 1 = USBID pin is controlled by the USB module

- 0 = USBID pin is controlled by the port function

- bit 13-5 **Reserved:** Program as '1'

- bit 4 ALTI2C: Alternate I2C1 Location Select bit

- 1 = SDA1 and SCL1 are on pins, RB8 and RB9

- 0 = SDA1 and SCL1 are moved to alternate I<sup>2</sup>C locations, RB5 and RC9

- SOSCHP: Secondary Oscillator (SOSC) High-Power Enable bit

- 1 = SOSC operates in normal power mode

- 0 = SOSC operates in High-Power mode

- bit 2-0 Reserved: Program as '1'

bit 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 | _                | _                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | _                 | _                 | _                 | —                 | _                 | —                 | _                | _                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 |                  | _                |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | R/P               | r-1              | r-1              |

| 7:0          | _                 | _                 | _                 | ICS<              | :1:0>             | JTAGEN            | _                | _                |

#### REGISTER 26-2: FICD/AFICD: ICD/DEBUG CONFIGURATION REGISTER

| Legend:           | r = Reserved bit | P = Programmable bit |                                    |  |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

bit 31-5 Reserved: Program as '1'

bit 4-3 ICS<1:0>: ICE/ICD Communication Channel Selection bits

11 = Communicates on PGEC1/PGED1

10 = Communicates on PGEC2/PGED2

01 = Communicates on PGEC3/PGED3

00 = Not connected

bit 2 JTAGEN: JTAG Enable bit

1 = JTAG is enabled

0 = JTAG is disabled

bit 1-0 Reserved: Program as '1'

#### TABLE 29-12: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| Operatin            | <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |                                         |     |     |     |       |                                                                    |  |  |  |  |

|---------------------|---------------------------------------------------------------------------|-----------------------------------------|-----|-----|-----|-------|--------------------------------------------------------------------|--|--|--|--|

| Param<br>No. Symbol |                                                                           | Characteristics                         | Min | Тур | Max | Units | Comments                                                           |  |  |  |  |

| DVR10               | Vbg                                                                       | Internal Band Gap Reference             |     | 1.2 | —   | V     |                                                                    |  |  |  |  |

| DVR20               | Vrgout                                                                    | Regulator Output Voltage                | _   | 1.8 | _   | V     | Vdd > 1.9V                                                         |  |  |  |  |

| DVR21               | Cefc                                                                      | External Filter Capacitor Value         | 4.7 | 10  | -   | μF    | Series Resistance < $3\Omega$<br>recommended; < $5\Omega$ required |  |  |  |  |

| DVR30               | Vlvr                                                                      | Low-Voltage Regulator<br>Output Voltage | 0.9 | —   | 1.2 | V     | RETEN = 1,<br>RETVR (FPOR<2>) = 0                                  |  |  |  |  |

#### TABLE 29-13: HIGH/LOW-VOLTAGE DETECT CHARACTERISTICS

| Operati      | <b>Operating Conditions:</b> -40°C < TA < +85°C (unless otherwise stated) |                                         |                   |      |      |      |       |            |  |  |  |  |

|--------------|---------------------------------------------------------------------------|-----------------------------------------|-------------------|------|------|------|-------|------------|--|--|--|--|

| Param<br>No. | Symbol                                                                    | Characteristic                          |                   |      | Тур  | Max  | Units | Conditions |  |  |  |  |

| DC18         | C18 VHLVD HLVD Voltage on VDD                                             | HLVDL<3:0> = 0101                       | 3.25              | —    | 3.63 | V    |       |            |  |  |  |  |

|              |                                                                           | Transition                              | HLVDL<3:0> = 0110 | 2.95 | —    | 3.30 | V     |            |  |  |  |  |

|              |                                                                           |                                         | HLVDL<3:0> = 0111 | 2.75 | —    | 3.09 | V     |            |  |  |  |  |

|              |                                                                           | HLVDL<3:0> = 1000                       | 2.65              | _    | 2.98 | V    |       |            |  |  |  |  |

|              |                                                                           |                                         | HLVDL<3:0> = 1001 | 2.45 | —    | 2.80 | V     |            |  |  |  |  |

|              |                                                                           |                                         | HLVDL<3:0> = 1010 | 2.35 | —    | 2.69 | V     |            |  |  |  |  |

|              |                                                                           |                                         | HLVDL<3:0> = 1011 | 2.25 | _    | 2.55 | V     |            |  |  |  |  |

|              |                                                                           |                                         | HLVDL<3:0> = 1100 | 2.15 | —    | 2.44 | V     |            |  |  |  |  |

|              |                                                                           |                                         | HLVDL<3:0> = 1101 | 2.08 | —    | 2.33 | V     |            |  |  |  |  |

|              |                                                                           |                                         | HLVDL<3:0> = 1110 | 2.00 | _    | 2.22 | V     |            |  |  |  |  |

| DC101        | VTHL                                                                      | HLVD Voltage on<br>LVDIN Pin Transition | HLVDL<3:0> = 1111 | —    | 1.2  |      | V     |            |  |  |  |  |

| AC CHARACTERISTICS |         |                               |                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                                  |  |

|--------------------|---------|-------------------------------|---------------------------|------------------------------------------------------|------|-------|--------------------------------------------------|--|

| Param<br>No.       | Sym     | Characteristics               |                           | Min. <sup>(1)</sup>                                  | Max. | Units | Conditions                                       |  |

| IM25               | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                  | _    | ns    |                                                  |  |

|                    |         |                               | 400 kHz mode              | 100                                                  |      | ns    | 1                                                |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | 100                                                  |      | ns    |                                                  |  |

| IM26               | THD:DAT | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                    | _    | μS    |                                                  |  |

|                    |         |                               | 400 kHz mode              | 0                                                    | 0.9  | μs    |                                                  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | 0                                                    | 0.3  | μS    |                                                  |  |

| IM30               | Tsu:sta | Start Condition<br>Setup Time | 100 kHz mode              | TPBCLK * (BRG + 2)                                   | _    | μS    | Only relevant for Repeated Start condition       |  |

|                    |         |                               | 400 kHz mode              | TPBCLK * (BRG + 2)                                   | _    | μS    |                                                  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | TPBCLK * (BRG + 2)                                   |      | μS    |                                                  |  |

| IM31               | Thd:sta | Start Condition<br>Hold Time  | 100 kHz mode              | TPBCLK * (BRG + 2)                                   |      | μS    | After this period, the first cloc                |  |

|                    |         |                               | 400 kHz mode              | TPBCLK * (BRG + 2)                                   |      | μS    | pulse is generated                               |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | TPBCLK * (BRG + 2)                                   | _    | μs    |                                                  |  |

| IM33               | Tsu:sto | Stop Condition<br>Setup Time  | 100 kHz mode              | TPBCLK * (BRG + 2)                                   |      | μS    |                                                  |  |

|                    |         |                               | 400 kHz mode              | TPBCLK * (BRG + 2)                                   | _    | μS    |                                                  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | TPBCLK * (BRG + 2)                                   |      | μS    |                                                  |  |

| IM34               | Thd:sto | Stop Condition<br>Hold Time   | 100 kHz mode              | TPBCLK * (BRG + 2)                                   |      | ns    |                                                  |  |

|                    |         |                               | 400 kHz mode              | TPBCLK * (BRG + 2)                                   | _    | ns    |                                                  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | TPBCLK * (BRG + 2)                                   |      | ns    |                                                  |  |

| IM40               | TAA:SCL | Output Valid<br>from Clock    | 100 kHz mode              | —                                                    | 3500 | ns    |                                                  |  |

|                    |         |                               | 400 kHz mode              | —                                                    | 1000 | ns    |                                                  |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | —                                                    | 350  | ns    |                                                  |  |

| IM45               | TBF:SDA | Bus Free Time                 | 100 kHz mode              | 4.7                                                  |      | μs    | The amount of time the bus                       |  |

|                    |         |                               | 400 kHz mode              | 1.3                                                  |      | μs    | must be free before a new transmission can start |  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup> | 0.5                                                  | —    | μs    |                                                  |  |

| IM50               | Св      | Bus Capacitive Loading        |                           | —                                                    | _    | pF    | See Parameter DO58                               |  |

| IM51               | Tpgd    | Pulse Gobbler D               | Delay                     | 52                                                   | 312  | ns    | (Note 3)                                         |  |

#### TABLE 29-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum Pin Capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

# 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М        | MILLIMETERS |      |  |

|-------------------------|--------|----------|-------------|------|--|

| Dimensior               | Limits | MIN      | NOM         | MAX  |  |

| Number of Pins          | Ν      | 28       |             |      |  |

| Pitch                   | е      |          | 0.65 BSC    |      |  |

| Overall Height          | Α      | 0.80     | 0.90        | 1.00 |  |

| Standoff                | A1     | 0.00     | 0.02        | 0.05 |  |

| Terminal Thickness      | A3     |          | 0.20 REF    |      |  |

| Overall Width           | E      |          | 6.00 BSC    |      |  |

| Exposed Pad Width       | E2     | 3.65     | 3.70        | 4.20 |  |

| Overall Length          | D      | 6.00 BSC |             |      |  |

| Exposed Pad Length      | D2     | 3.65     | 3.70        | 4.20 |  |

| Terminal Width          | b      | 0.23     | 0.30        | 0.35 |  |

| Terminal Length         | L      | 0.50     | 0.55        | 0.70 |  |

| Terminal-to-Exposed Pad | K      | 0.20     | -           | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

## **PRODUCT IDENTIFICATION SYSTEM**

| o order or obtain info                                       | rmation, e.g., on pricing or delivery, refer to the factory or the listed sales of                                                          | fice.                                                                                                                                                                                         |

|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Family<br>Key Feature Set<br>Pin Count<br>Tape and Reel Flag |                                                                                                                                             | Example:<br>PIC32MM0064GPM028-I/MV:<br>PIC32 General Purpose Device<br>with MIPS32 <sup>®</sup> microAptiv™ UC<br>Core, 64-Kbyte Program Memory<br>28-Pin, Industrial Temp.,<br>UQFN Package. |

| Architecture                                                 | MM = MIPS32 <sup>®</sup> microAptiv™ UC CPU Core                                                                                            |                                                                                                                                                                                               |

| Flash Memory Size                                            | 0064 = 64 Kbytes<br>0128 = 128 Kbytes<br>0256 = 256 Kbytes                                                                                  |                                                                                                                                                                                               |

| Family                                                       | GP = General Purpose Family                                                                                                                 |                                                                                                                                                                                               |

| Key Feature                                                  | <ul> <li>M = Up to 25 MHz operating frequency with basic peripheral set of 3 UARTs,<br/>3 SPIs, 3 I<sup>2</sup>C modules and USB</li> </ul> |                                                                                                                                                                                               |

| Pin Count                                                    | 028 = 28-pin<br>036 = 36/40-pin<br>048 = 48-pin<br>064 = 64-pin                                                                             |                                                                                                                                                                                               |

| Pattern                                                      | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                            |                                                                                                                                                                                               |