Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXFl

| Detalls                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 27                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 15x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 36-SQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpm036t-i-m2 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. This data sheet contains device-specific information for the PIC32MM0256GPM064 family devices.

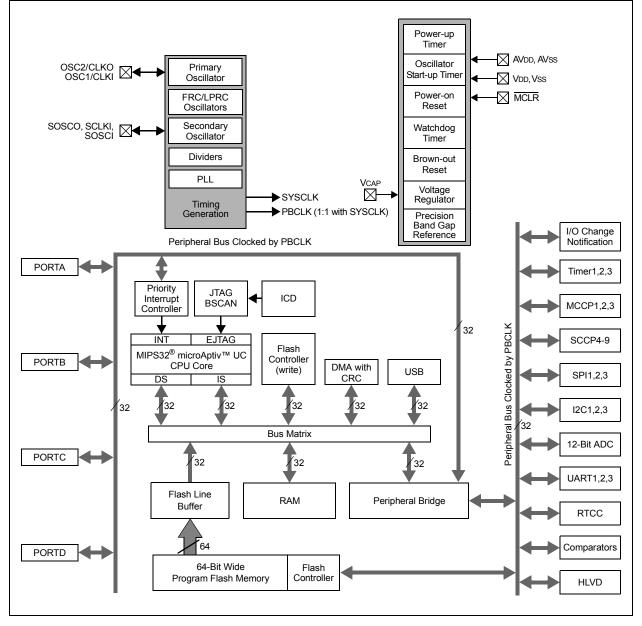

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MM0256GPM064 family of devices.

Table 1-1 lists the pinout I/O descriptions for the pins shown in the device pin tables.

## FIGURE 1-1: PIC32MM0256GPM064 FAMILY BLOCK DIAGRAM

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

## REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER

| Bit<br>Range | Bit Bit Bit Bit 31/23/15/7 30/22/14/6 29/21/13/5 2 |        | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2          | Bit<br>25/17/9/1 | Bit<br>24/16/8/0  |       |  |  |

|--------------|----------------------------------------------------|--------|----------------------|-------------------|----------------------------|------------------|-------------------|-------|--|--|

| 31:24        | R/W-0                                              | R/W-0  | R/W-0                | R/W-0             | R/W-0                      | R/W-0            | R/W-0 R/W-0 R/W-0 |       |  |  |

|              |                                                    | PRI7SS | <3:0>(1)             |                   | PRI6SS<3:0> <sup>(1)</sup> |                  |                   |       |  |  |

| 00.40        | R/W-0 R/W-0                                        |        | R/W-0                | R/W-0             | R/W-0                      | R/W-0 R/W-0      |                   | R/W-0 |  |  |

| 23:16        |                                                    | PRI5SS | <3:0> <sup>(1)</sup> |                   | PRI4SS<3:0> <sup>(1)</sup> |                  |                   |       |  |  |

| 45.0         | R/W-0                                              | R/W-0  | R/W-0                | R/W-0             | R/W-0                      | R/W-0            | R/W-0             | R/W-0 |  |  |

| 15:8         |                                                    | PRI3SS | <3:0> <sup>(1)</sup> |                   | PRI2SS<3:0> <sup>(1)</sup> |                  |                   |       |  |  |

| 7.0          | R/W-0 R/W-0 R/W-0 R/W-0                            |        |                      |                   | U-0                        | U-0              | U-0               | R/W-0 |  |  |

| 7:0          |                                                    | PRI1SS | <3:0>(1)             |                   | —                          |                  |                   | SS0   |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-28 PRI7SS<3:0>: Interrupt with Priority Level 7 Shadow Set bits<sup>(1)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                 | _                 | _                 |                   | IP3<2:0>          |                   | IS3<1:0>         |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |

| 23:16        | _                 | _                 | _                 |                   | IP2<2:0>          | IS2<1:0>          |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | _                 | _                 |                   | IP1<2:0>          |                   | IS1<1:0>         |                  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0 R/W-0       |                  | R/W-0            |  |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<1:0>         |                  |  |

## REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x

#### Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: | Interrupt | Priority 3 bits |

|-----------|-----------|-----------|-----------------|

- - 00 = Interrupt subpriority is 0

# bit 23-21 Unimplemented: Read as '0'

- bit 20-18 IP2<2:0>: Interrupt Priority 2 bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority 2 bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 |     |     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-----|-----|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0 | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —   | -   | _                 |                   |                   | _                | —                |  |

| 00.40        | U-0               | U-0 | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —   | -   | _                 | _                 | _                 | _                | —                |  |

| 45.0         | R/W-0             | U-0 | U-0 | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |

| 15:8         | ON <sup>(1)</sup> | —   | _   | SUSPEND           | DMABUSY           | _                 | -                | —                |  |

| 7.0          | U-0               | U-0 | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 7:0          | _                 | _   | _   | _                 | _                 | _                 | _                | _                |  |

#### REGISTER 8-1: DMACON: DMA CONTROLLER CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

#### bit 14-13 Unimplemented: Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

- bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** The user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0                              | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                                  | —     | —                 | —                 | —                 | —                 | —                | —                |  |

| 23:16        | U-0                              | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:10        |                                  | —     | _                 | -                 | —                 | —                 | —                | —                |  |

| 45.0         | U-0                              | U-0   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         | —                                | _     | _                 | _                 | —                 | —                 | —                | —                |  |

| 7.0          | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                                  |       |                   | CHPDA             | Γ<7:0>            |                   |                  |                  |  |

## REGISTER 8-18: DCHxDAT: DMA CHANNEL x PATTERN DATA REGISTER

# Legend:

| Ecgena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow terminate on match. All Other modes: Unused.

## REGISTER 9-6: OSCTUN: FRC TUNING REGISTER (CONTINUED)

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step-size is an approximation and is neither characterized, nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 26.4 "System Registers Write |

|-------|---------------------------------------------------------------------------------------------------|

|       | Protection" for details.                                                                          |

# 11.1 Timer1 Control Register

## TABLE 11-1: TIMER1 REGISTER MAP

| ress<br>)                   | <b>b</b> a                      | е        |       | Bits  |       |       |       |       |      |       |                     |      |      | ts     |      |       |      |      |           |

|-----------------------------|---------------------------------|----------|-------|-------|-------|-------|-------|-------|------|-------|---------------------|------|------|--------|------|-------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Rang | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7                | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Reset |

| 0000                        | TIOON                           | 31:16    | _     | _     | —     | —     | —     | _     | —    | —     | —                   | —    | —    | —      | _    | —     | —    | —    | 0000      |

| 8000                        | T1CON                           | 15:0     | ON    | —     | SIDL  | TWDIS | TWIP  | —     | TECS | <1:0> | TGATE               | _    | TCKP | S<1:0> | _    | TSYNC | TCS  | —    | 0000      |

| 0010                        | TMR1                            | 31:16    |       | _     | _     | _     | _     | _     | _    | _     | _                   | _    | _    | _      | _    | _     | _    | _    | 0000      |

| 8010                        | TIVIRT                          | 15:0     |       |       |       |       |       |       |      | TMR1< | <15:0>              |      |      |        |      |       |      |      | 0000      |

| 8020                        | PR1                             | 31:16    | _     | _     | —     | _     | —     | _     |      | —     | _                   | —    | _    | _      |      | _     |      | —    | 0000      |

| 0020                        |                                 | 15:0     |       |       |       |       |       |       |      | PR1<1 | 5:0> <sup>(2)</sup> |      |      |        |      |       |      |      | FFFF      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

**2:** PR1 values of '0' and '1' are reserved.

# PIC32MM0256GPM064 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | —                 | _                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | —                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | SIDL              | _                 | —                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS<2:0>        |                   | —                 |                   | TCS              | —                |

## REGISTER 12-2: T3CON: TIMER3 CONTROL REGISTER

#### Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer3 On bit

- 1 = Timer3 is enabled

- 0 = Timer3 is disabled

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Timer3 Stop in Idle Mode bit

- 1 = Discontinues operation when device enters Idle mode

- 0 = Continues operation even in Idle mode

#### bit 12-8 Unimplemented: Read as '0'

bit 7 **TGATE:** Timer3 Gated Time Accumulation Enable bit When TCS = 1:

This bit is ignored.

## When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

## bit 6-4 TCKPS<2:0>: Timer3 Input Clock Prescale Select bits

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

## bit 3-2 Unimplemented: Read as '0'

- bit 1 TCS: Timer3 Clock Source Select bit

- 1 = External clock is from the T3CK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

## TABLE 14-1: MCCP/SCCP REGISTER MAP (CONTINUED)

|                             |                                 |           |       |                 |       |       |       |        |      |      |            |       |       |        |         |         |       | <u> </u> |               |

|-----------------------------|---------------------------------|-----------|-------|-----------------|-------|-------|-------|--------|------|------|------------|-------|-------|--------|---------|---------|-------|----------|---------------|

| ress<br>()                  | -                               | e         |       |                 |       |       |       |        |      |      | Bits       |       |       |        |         |         |       |          |               |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14           | 29/13 | 28/12 | 27/11 | 26/10  | 25/9 | 24/8 | 23/7       | 22/6  | 21/5  | 20/4   | 19/3    | 18/2    | 17/1  | 16/0     | All<br>Resets |

| 0020                        | CCP9STAT                        | 31:16     |       | —               | —     | _     |       | —      | _    |      | —          | _     | _     | PRLWIP | TMRHWIP | TMRLWIP | RBWIP | RAWIP    | 0000          |

| 0930                        | CCP95TAI                        | 15:0      | —     | _               | _     | —     | —     | ICGARM | —    |      | CCPTRIG    | TRSET | TRCLR | ASEVT  | SCEVT   | ICDIS   | ICOV  | ICBNE    | 0000          |

| 0940                        | CCP9TMR                         | 31:16     |       |                 |       |       |       |        |      | ΤN   | 1RH<15:0>  |       |       |        |         |         |       |          | 0000          |

| 0940                        | CCF91WK                         | 15:0      |       | TMRL<15:0> 0000 |       |       |       |        |      |      |            |       |       |        |         |         | 0000  |          |               |

| 0950                        | CCP9PR                          | 31:16     |       | PRH<15:0> 0000  |       |       |       |        |      |      |            |       |       |        | 0000    |         |       |          |               |

| 0950                        | COF9FR                          | 15:0      |       |                 |       |       |       |        |      | Р    | RL<15:0>   |       |       |        |         |         |       |          | 0000          |

| 0960                        | CCP9RA                          | 31:16     | —     | —               | —     | —     | —     | —      | —    |      | _          | —     |       | —      | _       | —       | —     | —        | 0000          |

| 0900                        | CCF9RA                          | 15:0      |       |                 |       |       |       |        |      | CN   | /IPA<15:0> |       |       |        |         |         |       |          | 0000          |

| 0970                        | CCP9RB                          | 31:16     | —     | —               | —     | —     | —     | —      | —    |      | _          | —     |       | —      | _       | —       | —     | —        | 0000          |

| 0970                        | CCF9RD                          | 15:0      |       |                 |       |       |       |        |      |      |            |       |       |        |         | 0000    |       |          |               |

| 0090                        | CCP9BUF                         | 31:16     |       | BUFH<15:0> 0000 |       |       |       |        |      |      |            |       |       |        | 0000    |         |       |          |               |

| 0980                        | CCF9BUF                         | 15:0      |       | BUFL<15:0> 0000 |       |       |       |        |      |      |            |       |       |        |         | 0000    |       |          |               |

PIC32MM0256GPM064 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0        |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|-------------------------|

| 24.24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 31:24        | —                    | _                 | _                 | —                 | -                        | _                 | -                | —                       |

| 00.40        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                     |

| 23:16        | —                    | _                 | _                 | —                 | —                        | _                 | _                | —                       |

| 45.0         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                   |

| 15:8         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                  |

| 7.0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup> | -                 | -                 | _                 | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

# REGISTER 15-2: SPIxCON2: SPIx CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

|-------------------|------------------|-----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: SPIx Sign-Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign-extended

- 0 = Data from RX FIFO is not sign-extended

- bit 14-13 Unimplemented: Read as '0'

| bit 12  | FRMERREN: Enable Interrupt Events via FRMERR bit                                                                                                                                         |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Frame error overflow generates error events                                                                                                                                          |

|         | 0 = Frame error does not generate error events                                                                                                                                           |

| bit 11  | SPIROVEN: Enable Interrupt Events via SPIROV bit                                                                                                                                         |

|         | 1 = Receive Overflow (ROV) generates error events                                                                                                                                        |

|         | 0 = Receive Overflow does not generate error events                                                                                                                                      |

| bit 10  | SPITUREN: Enable Interrupt Events via SPITUR bit                                                                                                                                         |

|         | 1 = Transmit Underrun (TUR) generates error events                                                                                                                                       |

|         | 0 = Transmit Underrun does not generate error events                                                                                                                                     |

| bit 9   | IGNROV: Ignore Receive Overflow (ROV) bit (for audio data transmissions)                                                                                                                 |

|         | <ul> <li>1 = A ROV is not a critical error; during ROV, data in the FIFO is not overwritten by receive data</li> <li>0 = A ROV is a critical error which stops SPIx operation</li> </ul> |

| bit 8   | IGNTUR: Ignore Transmit Underrun (TUR) bit (for audio data transmissions)                                                                                                                |

|         | <ul> <li>1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty</li> <li>0 = A TUR is a critical error which stops SPIx operation</li> </ul>         |

| bit 7   | AUDEN: Enable Audio Codec Support bit <sup>(1)</sup>                                                                                                                                     |

|         | <ul><li>1 = Audio protocol is enabled</li><li>0 = Audio protocol is disabled</li></ul>                                                                                                   |

| bit 6-4 | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 3   | AUDMONO: Transmit Audio Data Format bit <sup>(1,2)</sup>                                                                                                                                 |

|         | <ul> <li>1 = Audio data is mono (each data word is transmitted on both left and right channels)</li> <li>0 = Audio data is stereo</li> </ul>                                             |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                                               |

| bit 1-0 | AUDMOD<1:0>: Audio Protocol Mode bits <sup>(1,2)</sup>                                                                                                                                   |

|         | 11 = PCM/DSP mode                                                                                                                                                                        |

|         | 10 = Right Justified mode                                                                                                                                                                |

|         | 01 = Left Justified mode<br>00 = I <sup>2</sup> S mode                                                                                                                                   |

|         |                                                                                                                                                                                          |

| Note 1: | These bits can only be written when the ON bit = 0.                                                                                                                                      |

| 2:      | These bits are only valid for AUDEN = 1.                                                                                                                                                 |

## REGISTER 18-6: U1IR: USB INTERRUPT REGISTER (CONTINUED)

- bit 0 URSTIF: USB Reset Interrupt bit (Device mode)<sup>(5)</sup>

- 1 = Valid USB Reset has occurred

- 0 = No USB Reset has occurred

- DETACHIF: USB Detach Interrupt bit (Host mode)(6)

- 1 = Peripheral detachment was detected by the USB module

- 0 = Peripheral detachment was not detected

- **Note 1:** This bit is only valid if the HOSTEN bit is set (see Register 18-11), there is no activity on the USB for 2.5 μs and the current bus state is not SE0.

- **2:** When not in Suspend mode, this interrupt should be disabled.

- 3: Clearing this bit will cause the STAT FIFO to advance.

- 4: Only error conditions enabled through the U1EIE register will set this bit.

- 5: Device mode.

- 6: Host mode.

## TABLE 21-1: CLC1, CLC2 AND CLC3 REGISTER MAP

| Properiod         Properiod        <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          | <u> </u>                        |           | <u>, o</u> |         |          |       |       |       |          |       |       |         |          |       |       |       |          |        |            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------|-----------|------------|---------|----------|-------|-------|-------|----------|-------|-------|---------|----------|-------|-------|-------|----------|--------|------------|

| h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h         h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ess                      |                                 |           |            |         |          |       |       |       |          | E     | Bits  |         |          |       |       |       |          |        |            |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15      | 30/14   | 29/13    | 28/12 | 27/11 | 26/10 | 25/9     | 24/8  | 23/7  | 22/6    | 21/5     | 20/4  | 19/3  | 18/2  | 17/1     | 16/0   | All Resets |

| Image: bit is informed bit informed bit informed bit is informed bit informe | 2490                     |                                 | 32:16     |            | _       | —        | _     |       | —     | —        | _     | _     | —       | —        |       | G4POL | G3POL | G2POL    | G1POL  | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2400                     | CLUTCON                         | 15:0      | ON         | _       | SIDL     | _     | INTP  | INTN  | —        | _     | LCOE  | LCOUT   | LCPOL    | —     | _     | I     | MODE<2:0 | >      | 0000       |

| Image: Finite Final Fina | 2490                     | CLC1SEL                         | 32:16     | _          | _       | —        | _     |       | _     | —        | _     | _     | _       | —        | _     |       | —     | —        | —      | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2400                     | OLOTOLL                         | 15:0      | —          |         | DS4<2:0> |       | —     |       | DS3<2:0> |       | —     |         | DS2<2:0> |       | —     |       | DS1<2:0> |        | 0000       |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 24A0                     | CLC1GLS                         | 32:16     | -          | -       |          |       | -     | -     | -        | -     |       |         |          | G3D3N |       |       |          |        | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | 0101010                         |           | G2D4T      | G2D4N   | G2D3T    | G2D3N | G2D2T | G2D2N | G2D1T    | G2D1N | G1D4T | G1D4N   | G1D3T    | G1D3N | -     | -     | -        | -      | 0000       |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2500                     | CLC2CON                         |           |            |         |          |       |       |       | —        | _     |       |         |          | —     | G4POL |       |          |        | -          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                 |           | ON         | —       | SIDL     | —     | INTP  | INTN  | —        | —     | LCOE  | LCOUT   | LCPOL    | —     | —     | l l   | MODE<2:0 | >      |            |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2510                     | CLC2SEL                         |           | _          | —       |          | —     | —     |       |          | —     |       | —       |          | _     |       | _     | —        | —      |            |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                 |           | —          | 0.00.00 |          | 0.000 | —     |       |          | 0.0.0 |       | 000.011 |          | 00001 |       | 00001 | 1        | 000.00 |            |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2520                     | CLC2GLS                         |           | -          | -       |          |       | -     | -     | -        | -     |       |         |          |       |       |       |          |        |            |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                 |           | -          | -       |          |       | _     | -     | -        | -     |       | G1D4N   |          |       | -     | -     | -        | -      | -          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2580                     | CLC3CON                         |           |            |         |          |       |       |       |          |       |       |         |          |       |       |       |          |        |            |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                 |           | -          |         | _        | -     |       |       |          |       |       |         |          |       |       |       |          |        |            |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2590                     | CLC3SEL                         |           |            |         |          | _     |       |       |          | _     |       | _       |          | _     |       | _     |          | _      | -          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |                                 |           | G4D4T      | G4D4N   |          | G4D3N |       |       |          | G4D1N |       | G3D4N   |          | G3D3N |       | G3D2N |          | G3D1N  | -          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 25A0                     | CLC3GLS                         |           |            | -       |          |       | -     | -     | -        | -     |       |         |          |       |       |       |          |        |            |