Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpm064-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

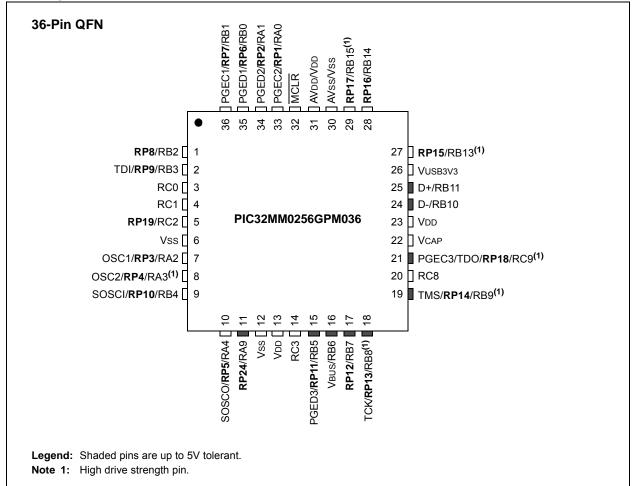

# **Pin Diagrams (Continued)**

### TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN QFN DEVICES

| Pin | Function                                                    | Pin | Function                                                                       |

|-----|-------------------------------------------------------------|-----|--------------------------------------------------------------------------------|

| 1   | AN4/C1INB/RP8/SDA2/OCM2E/RB2                                | 19  | TMS/REFCLKI/RP14/SDA1/T1CK/T1G/U1RTS/U1BCLK/SDO1/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3                           | 20  | AN14/LVDIN/C2INC/RC8                                                           |

| 3   | AN12/C2IND/T2CK/T2G/RC0                                     | 21  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /USBOEN/SDO3/RC9 <sup>(1)</sup>            |

| 4   | AN13/T3CK/T3G/RC1                                           | 22  | VCAP                                                                           |

| 5   | RP19/OCM2A/RC2                                              | 23  | VDD                                                                            |

| 6   | Vss                                                         | 24  | D-/RB10                                                                        |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                                 | 25  | D+/RB11                                                                        |

| 8   | OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3 <sup>(1)</sup>            | 26  | VUSB3V3                                                                        |

| 9   | SOSCI/AN7/RP10/OCM3C/RB4                                    | 27  | AN8/ <b>RP15</b> /SCL3/SCK3/RB13 <sup>(1)</sup>                                |

| 10  | SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4                           | 28  | CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14                     |

| 11  | RP24/OCM3A/RA9                                              | 29  | AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15 <sup>(1)</sup>         |

| 12  | Vss                                                         | 30  | AVss/Vss                                                                       |

| 13  | Vdd                                                         | 31  | AVdd/Vdd                                                                       |

| 14  | RC3                                                         | 32  | MCLR                                                                           |

| 15  | PGED3/RP11/ASDA1 <sup>(2)</sup> /USBID/SS3/FSYNC3/OCM3E/RB5 | 33  | PGEC2/VREF+/CVREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                             |

| 16  | VBUS/RB6                                                    | 34  | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                                         |

| 17  | RP12/SDA3/SDI3/OCM3F/RB7                                    | 35  | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                                      |

| 18  | TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>           | 36  | PGEC1/AN3/C1INC/C2INA/ <b>RP7</b> /OCM2D/RB1                                   |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

|           |                |                        | Pin Number    |                |                        |                        |             |                |                    |  |  |

|-----------|----------------|------------------------|---------------|----------------|------------------------|------------------------|-------------|----------------|--------------------|--|--|

| Pin Name  | 28-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 36-Pin<br>QFN | 40-Pin<br>UQFN | 48-Pin<br>QFN/<br>TQFP | 64-Pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description        |  |  |

| RA0       | 2              | 27                     | 33            | 36             | 21                     | 11                     | I/O         | ST/DIG         | PORTA digital I/Os |  |  |

| RA1       | 3              | 28                     | 34            | 37             | 22                     | 12                     | I/O         | ST/DIG         |                    |  |  |

| RA2       | 9              | 6                      | 7             | 7              | 32                     | 25                     | I/O         | ST/DIG         |                    |  |  |

| RA3       | 10             | 7                      | 8             | 8              | 33                     | 26                     | I/O         | ST/DIG         |                    |  |  |

| RA4       | 12             | 9                      | 10            | 10             | 36                     | 29                     | I/O         | ST/DIG         |                    |  |  |

| RA5       | —              | —                      | _             | _              | _                      | 54                     | I/O         | ST/DIG         |                    |  |  |

| RA6       | —              | —                      | —             | _              | 20                     | 10                     | I/O         | ST/DIG         |                    |  |  |

| RA7       | —              | —                      | _             | _              | 14                     | 1                      | I/O         | ST/DIG         |                    |  |  |

| RA8       | —              | _                      | _             | _              | 34                     | 27                     | I/O         | ST/DIG         |                    |  |  |

| RA9       | —              | —                      | 11            | 11             | 37                     | 30                     | I/O         | ST/DIG         |                    |  |  |

| RA10      | —              | _                      | _             | _              | 13                     | 64                     | I/O         | ST/DIG         |                    |  |  |

| RA11      | —              | _                      | _             | _              | _                      | 8                      | I/O         | ST/DIG         |                    |  |  |

| RA12      | —              | —                      | _             | _              | _                      | 7                      | I/O         | ST/DIG         |                    |  |  |

| RA13      | —              | _                      | _             | _              | _                      | 6                      | I/O         | ST/DIG         |                    |  |  |

| RA14      | —              | _                      | _             | _              | _                      | 59                     | I/O         | ST/DIG         |                    |  |  |

| RA15      | —              | —                      | —             | _              | 8                      | 58                     | I/O         | ST/DIG         |                    |  |  |

| RB0       | 4              | 1                      | 35            | 38             | 23                     | 13                     | I/O         | ST/DIG         | PORTB digital I/Os |  |  |

| RB1       | 5              | 2                      | 36            | 39             | 24                     | 14                     | I/O         | ST/DIG         |                    |  |  |

| RB2       | 6              | 3                      | 1             | 1              | 25                     | 15                     | I/O         | ST/DIG         |                    |  |  |

| RB3       | 7              | 4                      | 2             | 2              | 26                     | 16                     | I/O         | ST/DIG         |                    |  |  |

| RB4       | 11             | 8                      | 9             | 9              | 35                     | 28                     | I/O         | ST/DIG         |                    |  |  |

| RB5       | 14             | 11                     | 15            | 15             | 45                     | 43                     | I/O         | ST/DIG         |                    |  |  |

| RB6       | 15             | 12                     | 16            | 16             | 46                     | 44                     | I/O         | ST/DIG         |                    |  |  |

| RB7       | 16             | 13                     | 17            | 17             | 47                     | 46                     | I/O         | ST/DIG         |                    |  |  |

| RB8       | 17             | 14                     | 18            | 18             | 48                     | 48                     | I/O         | ST/DIG         |                    |  |  |

| RB9       | 18             | 15                     | 19            | 20             | 1                      | 49                     | I/O         | ST/DIG         |                    |  |  |

| RB10      | 21             | 18                     | 24            | 27             | 9                      | 60                     | I/O         | ST/DIG         |                    |  |  |

| RB11      | 22             | 19                     | 25            | 28             | 10                     | 61                     | I/O         | ST/DIG         |                    |  |  |

| RB13      | 24             | 21                     | 27            | 30             | 12                     | 63                     | I/O         | ST/DIG         |                    |  |  |

| RB14      | 25             | 22                     | 28            | 31             | 15                     | 2                      | I/O         | ST/DIG         |                    |  |  |

| RB15      | 26             | 23                     | 29            | 32             | 16                     | 3                      | I/O         | ST/DIG         |                    |  |  |

| Legend: S |                |                        |               |                |                        |                        |             |                |                    |  |  |

# TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION (CONTINUED)

**Legend:** ST = Schmitt Trigger input buffer I2C =  $I^2C/SMBus$  input buffer

DIG = Digital input/output ANA = Analog level input/output P = Power

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3    | Bit<br>26/18/10/2     | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|---------------------|--------------------|-------------------|---------------------|----------------------|-----------------------|--------------------|--------------------|

| 24.04        | R/W-1, HS           | R/W-1, HS          | U-0               | U-0                 | R/W-0, HS            | R/W-0, HS             | U-0                | U-0                |

| 31:24        | PORIO               | PORCORE            |                   |                     | BCFGERR              | BCFGFAIL              | _                  | —                  |

| 00.40        | U-0                 | U-0                | U-0               | U-0                 | U-0                  | U-0                   | U-0                | U-0                |

| 23:16        | —                   | _                  | _                 |                     | —                    | _                     | _                  | _                  |

| 15:8         | U-0                 | U-0                | U-0               | U-0                 | U-0                  | U-0                   | R/W-0, HS          | U-0                |

| 10.0         | —                   | _                  | _                 |                     | —                    | _                     | CMR                | —                  |

| 7.0          | R/W-0, HS           | R/W-0, HS          | U-0               | R/W-0, HS           | R/W-0, HS            | R/W-0, HS             | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR <sup>(1)</sup> | SWR <sup>(1)</sup> |                   | WDTO <sup>(1)</sup> | SLEEP <sup>(1)</sup> | IDLE <sup>(1,2)</sup> | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

### REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Legend:           | HS = Hardware Settable bit |                           |                    |

|-------------------|----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | PORIO: VDD POR Flag bit                                                                  |

|-----------|------------------------------------------------------------------------------------------|

|           | Set by hardware at detection of a VDD POR event.                                         |

|           | 1 = A Power-on Reset has occurred due to VDD voltage                                     |

|           | 0 = A Power-on Reset has not occurred due to VDD voltage                                 |

| bit 30    | PORCORE: Core Voltage POR Flag bit                                                       |

|           | Set by hardware at detection of a core POR event.                                        |

|           | 1 = A Power-on Reset has occurred due to core voltage                                    |

|           | 0 = A Power-on Reset has not occurred due to core voltage                                |

| bit 29-28 | Unimplemented: Read as '0'                                                               |

| bit 27    | BCFGERR: Primary Configuration Registers Error Flag bit                                  |

|           | 1 = An error occurred during a read of the Primary Configuration registers               |

|           | 0 = No error occurred during a read of the Primary Configuration registers               |

| bit 26    | BCFGFAIL: Primary/Alternate Configuration Registers Error Flag bit                       |

|           | 1 = An error occurred during a read of the Primary and Alternate Configuration registers |

|           | 0 = No error occurred during a read of the Primary and Alternate Configuration registers |

| bit 25-10 | Unimplemented: Read as '0'                                                               |

| bit 9     | CMR: Configuration Mismatch Reset Flag bit                                               |

|           | 1 = A Configuration Mismatch Reset has occurred                                          |

|           | 0 = A Configuration Mismatch Reset has not occurred                                      |

| bit 8     | Unimplemented: Read as '0'                                                               |

| bit 7     | EXTR: External Reset (MCLR) Pin Flag bit <sup>(1)</sup>                                  |

|           | 1 = Master Clear (pin) Reset has occurred                                                |

|           | 0 = Master Clear (pin) Reset has not occurred                                            |

| bit 6     | SWR: Software Reset Flag bit <sup>(1)</sup>                                              |

|           | 1 = Software Reset was executed                                                          |

|           | 0 = Software Reset was not executed                                                      |

| bit 5     | Unimplemented: Read as '0'                                                               |

| bit 4     | WDTO: Watchdog Timer Time-out Flag bit <sup>(1)</sup>                                    |

|           | 1 = WDT time-out has occurred                                                            |

|           | 0 = WDT time-out has not occurred                                                        |

| Note 1:   | User software must clear these bits to view the next detection.                          |

|           |                                                                                          |

2: The IDLE bit will also be set when the device wakes from Sleep.

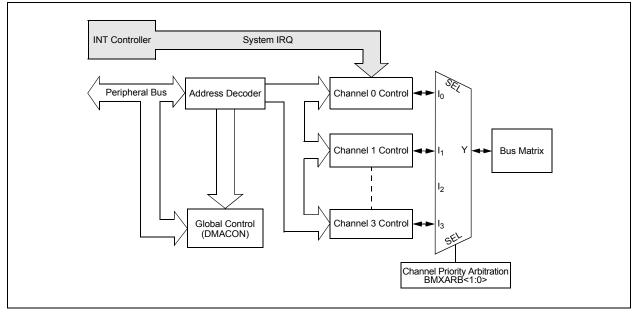

# 8.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note 1: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "DMA Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Direct Memory Access (DMA) Controller is a bus master module useful for data transfers between peripherals and memory without CPU intervention. The source and destination of a DMA transfer can be any of the memory-mapped modules, that do not have a dedicated DMA, existent in the PIC32 (such as SPI, UART, PMP, etc.) or the memory itself.

The following are some of the key features of the DMA Controller module:

- Four Identical Channels, Each Featuring:

- Auto-Increment Source and Destination Address registers

- Source and Destination Pointers

- Memory to memory and memory to peripheral transfers

- Automatic Word Size Detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- FIGURE 8-1: DMA BLOCK DIAGRAM

- Fixed Priority Channel Arbitration

- · Flexible DMA Channel Operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA Requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA Channel Status Interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA Debug Support Features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

- User Selectable Bus Arbitration Priority (refer to Section 4.2 "Bus Matrix (BMX)")

- 8 System Clocks Per Cell Transfer

| TABLE 10-0. |          |                |             | 10       |                |

|-------------|----------|----------------|-------------|----------|----------------|

| Value       | RPn Pins | Pin Assignment | Value       | RPn Pins | Pin Assignment |

| 00001       | RP1      | RA0 Pin        | 01110       | RP14     | RB9 Pin        |

| 00010       | RP2      | RA1 Pin        | 01111       | RP15     | RB13 Pin       |

| 00011       | RP3      | RA2 Pin        | 10000       | RP16     | RB14 Pin       |

| 00100       | RP4      | RA3 Pin        | 10001       | RP17     | RB15 Pin       |

| 00101       | RP5      | RA4 Pin        | 10010       | RP18     | RC9 Pin        |

| 00110       | RP6      | RB0 Pin        | 10011       | RP19     | RC2 Pin        |

| 00111       | RP7      | RB1 Pin        | 10100       | RP20     | RC7 Pin        |

| 01000       | RP8      | RB2 Pin        | 10101       | RP21     | RA7 Pin        |

| 01001       | RP9      | RB3 Pin        | 10110       | RP22     | RA10 Pin       |

| 01010       | RP10     | RB4 Pin        | 10111       | RP23     | RC6 Pin        |

| 01011       | RP11     | RB5 Pin        | 11000       | RP24     | RA9 Pin        |

| 01100       | RP12     | RB7 Pin        | 11001-11111 | Re       | served         |

| 01101       | RP13     | RB8 Pin        |             |          |                |

# TABLE 10-3: REMAPPABLE INPUT SOURCES PIN ASSIGNMENTS<sup>(1)</sup>

**Note 1:** All RPx pins are not available on all packages.

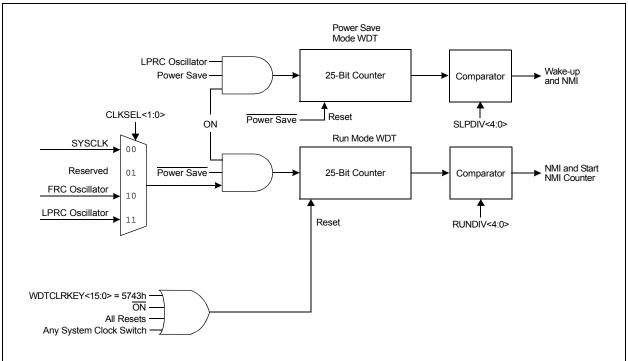

# 13.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 62. "Dual Watchdog Timer" (DS60001365) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. When enabled, the Watchdog Timer (WDT) can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

Some of the key features of the WDT module are:

- · Configuration or Software Controlled

- User-Configurable Time-out Period

- Different Time-out Periods for Run and Sleep/Idle modes

- Operates from LPRC Oscillator in Sleep/Idle modes

- Different Clock Sources for Run mode

- · Can Wake the Device from Sleep or Idle

### FIGURE 13-1: WATCHDOG TIMER BLOCK DIAGRAM

## REGISTER 15-1: SPIxCON: SPIx CONTROL REGISTER (CONTINUED)

| bit 7   | SSEN: Slave Select Enable (Slave mode) bit                                                                                                                                                                                                                                                                                                                                                        |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | $1 = \overline{SSx}$ pin is used for Slave mode                                                                                                                                                                                                                                                                                                                                                   |

|         | $0 = \overline{SSx}$ pin is not used for Slave mode, pin is controlled by port function                                                                                                                                                                                                                                                                                                           |

| bit 6   | CKP: Clock Polarity Select bit <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                     |

|         | <ul> <li>1 = Idle state for clock is a high level; active state is a low level</li> <li>0 = Idle state for clock is a low level; active state is a high level</li> </ul>                                                                                                                                                                                                                          |

| bit 5   | MSTEN: Master Mode Enable bit                                                                                                                                                                                                                                                                                                                                                                     |

|         | 1 = Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

|         | 0 = Slave mode                                                                                                                                                                                                                                                                                                                                                                                    |

| bit 4   | DISSDI: Disable SDIx bit <sup>(4)</sup>                                                                                                                                                                                                                                                                                                                                                           |

|         | <ul> <li>1 = SDIx pin is not used by the SPIx module (pin is controlled by port function)</li> <li>0 = SDIx pin is controlled by the SPIx module</li> </ul>                                                                                                                                                                                                                                       |

| bit 3-2 | STXISEL<1:0>: SPIx Transmit Buffer Empty Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                      |

|         | <ul> <li>11 = Interrupt is generated when the buffer is not full (has one or more empty elements)</li> <li>10 = Interrupt is generated when the buffer is empty by one-half or more</li> <li>01 = Interrupt is generated when the buffer is completely empty</li> <li>00 = Interrupt is generated when the last transfer is shifted out of SPIxSR and transmit operations are complete</li> </ul> |

| bit 1-0 | SRXISEL<1:0>: SPIx Receive Buffer Full Interrupt Mode bits                                                                                                                                                                                                                                                                                                                                        |

|         | <ul> <li>11 = Interrupt is generated when the buffer is full</li> <li>10 = Interrupt is generated when the buffer is full by one-half or more</li> <li>01 = Interrupt is generated when the buffer is not empty</li> </ul>                                                                                                                                                                        |

|         | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                                                                                                                                                                                                                              |

| Note 1: | These bits can only be written when the ON bit = 0. Refer to <b>Section 29.0</b> " <b>Electrical Characteristics</b> " for maximum clock frequency requirements.                                                                                                                                                                                                                                  |

| 2:      | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).                                                                                                                                                                                                                                                                         |

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: These bits are present for legacy compatibility and are superseded by PPS functionality on these devices (see Section 10.9 "Peripheral Pin Select (PPS)" for more information).

# REGISTER 15-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty

Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

### bit 2 Unimplemented: Read as '0'

### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

### Enhanced Buffer mode:

Set when CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

### TABLE 18-1: USB OTG REGISTER MAP (CONTINUED)

| ess                         |                                 | æ         |       |       |       |       |       |       |      |      | Bits |      |      |          |        |        |         |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 8770                        | U1EP7                           | 31:16     | —     | —     | —     |       | _     | -     | -    | —    | _    | _    | -    | —        |        | -      | -       | -      | 0000       |

| 0//0                        |                                 | 15:0      | —     | —     | —     | _     | —     | —     | _    | —    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 8780                        | U1EP8                           | 31:16     | —     | —     | —     | _     | —     | —     | _    | —    | —    | —    | _    | —        | _      | _      | _       | _      | 0000       |

| 0700                        | UILI U                          | 15:0      | —     | —     | —     | _     | —     | _     |      | —    | _    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 8790                        | U1EP9                           | 31:16     | —     | —     | —     | _     | —     | —     | _    | —    | —    | —    | _    | —        | _      | _      | _       | _      | 0000       |

| 0730                        | UTLI 9                          | 15:0      | —     | —     | —     | _     | —     | —     | _    | —    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 87A0                        | U1EP10                          | 31:16     | —     | —     | —     | _     | —     | _     |      | —    | _    | —    | —    | —        | _      | _      | _       | _      | 0000       |

| 0770                        | UTELLIU                         | 15:0      | —     | —     | —     | _     | —     | —     | _    | —    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 87B0                        | U1EP11                          | 31:16     | —     | —     | —     | _     | —     | —     | _    | —    | —    | —    | _    | —        | _      | _      | _       | _      | 0000       |

| 07 00                       | UIEFII                          | 15:0      | —     | —     | —     | _     | —     | —     | -    | —    | —    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 87C0                        | U1EP12                          | 31:16     | _     | _     | —     | _     | —     | —     | -    | —    | _    | —    | —    | —        | -      | -      | -       | _      | 0000       |

| 0/00                        | UTEL 12                         | 15:0      | _     | _     | —     | _     | —     | —     | -    | —    | _    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 87D0                        | U1EP13                          | 31:16     | —     | —     | —     | _     | —     | —     | -    | —    | —    | —    | —    | —        | -      | -      | -       | -      | 0000       |

| 0/ 00                       | UTEL 15                         | 15:0      | _     | _     | —     | _     | —     | —     | -    | —    | _    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 87E0                        | U1EP14                          | 31:16     | —     | —     | —     | —     | —     | —     | _    | —    | —    | —    | _    | —        | _      | —      | _       | _      | 0000       |

| 07 EU                       | UILF 14                         | 15:0      | —     | —     | _     | _     | —     | —     | _    | —    | —    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 87F0                        | U1EP15                          | 31:16     | —     | _     | —     | -     | —     | —     | -    | —    | _    | —    | -    | —        |        | -      | -       | -      | 0000       |

| 07F0                        | UILF IS                         | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 10.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for these bits is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 00.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | —                 | —                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7:0          | ID                |                   | LSTATE            | _                 | SESVD             | SESEND            |                  | VBUSVD           |

### REGISTER 18-3: U1OTGSTAT: USB OTG STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "Type B" cable has been inserted into the USB receptacle 0 = A "Type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has been stable for the previous 1 ms

- 0 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has not been stable for the previous 1 ms

- bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = The VBUS voltage is above VA\_SESS\_VLD (as defined in the USB OTG Specification) on the A or B-device 0 = The VBUS voltage is below VA\_SESS\_VLD on the A or B-device

- bit 2 SESEND: B-Device Session End Indicator bit

1 = The VBUS voltage is above VB\_SESS\_END (as defined in the USB OTG Specification) on the B-device 0 = The VBUS voltage is below VB\_SESS\_END on the B-device

### bit 1 Unimplemented: Read as '0'

bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

1 = The VBUS voltage is above VA\_VBUS\_VLD (as defined in the USB OTG Specification) on the A-device 0 = The VBUS voltage is below VA\_VBUS\_VLD on the A-device

# PIC32MM0256GPM064 FAMILY

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 2 |     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|------------------------------------|-----|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0                                | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | _                                  | _   | —                 | _                 | _                 | _                 | _                | —                |  |  |  |  |  |  |

| 00.40        | U-0                                | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | —                                  | —   | _                 |                   | —                 |                   | _                | —                |  |  |  |  |  |  |

| 45.0         | U-0                                | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 15:8         | —                                  | —   | _                 | —                 | —                 | _                 | _                | —                |  |  |  |  |  |  |

| 7.0          | R-0                                | R-0 | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                                    |     |                   | FRML<7:0>         |                   |                   |                  |                  |  |  |  |  |  |  |

# REGISTER 18-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** 11-Bit Frame Number Lower bits These register bits are updated with the current frame number whenever a SOF token is received.

#### Bit Bit Bit Bit Bit Bit Bit Bit Bit Range 31/23/15/7 30/22/14/6 29/21/13/5 28/20/12/4 27/19/11/3 26/18/10/2 25/17/9/1 24/16/8/0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 31:24 \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ \_ \_\_\_\_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 23:16 \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ \_\_\_\_ U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 15:8 U-0 U-0 U-0 U-0 U-0 R-0 R-0 R-0 7:0 FRMH<2:0> — — — — —

# REGISTER 18-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| Legend:           |                  |                                      |                    |  |

|-------------------|------------------|--------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | t U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                 | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** Upper 3 Bits of the Frame Numbers bits These register bits are updated with the current frame number whenever a SOF token is received.

# PIC32MM0256GPM064 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | —                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | —                 | —                 | —                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | CH0NA<2:0>        |                   |                   |                   | CH0SA<4:0>        |                  |                  |

#### REGISTER 20-5: AD1CHS: ADC INPUT SELECT REGISTER

| Leaend: |  |

|---------|--|

| Logona. |  |

| Ecgenia.          |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7-5 CH0NA<2:0>: Negative Input Select bits

- 111-001 = Reserved

- 000 = Negative input is AVss

- bit 4-0 CH0SA<4:0>: Positive Input Select bits

- 111111 = Reserved

- 11110 = Positive input is AVDD

- 11101 = Positive input is AVss

- 11100 = Positive input is Band Gap Reference (VBG)

- 11011 = VDD core

- 10100-10110 = Reserved

- 10011 = Positive input is AN19<sup>(1)</sup>

- 10010 = Positive input is AN18<sup>(1)</sup> 10001 = Positive input is AN17<sup>(1)</sup>

- 10000 = Positive input is AN16<sup>(1)</sup> 01111 = Positive input is AN15<sup>(2)</sup>

- 01110 = Positive input is AN14<sup>(3)</sup>

- 01101 = Positive input is AN13<sup>(3)</sup>

- 01100 = Positive input is AN12<sup>(3)</sup> 01011 = Positive input is AN11

- 01010 = Positive input is AN10

- 01001 = Positive input is AN9

- 01000 = Positive input is AN8

- 00111 = Positive input is AN7

- 00110 = Positive input is AN6 00101 = Positive input is AN5

- 00100 = Positive input is AN4

- 00011 = Positive input is AN3

- 00010 = Positive input is AN2

- 00001 = Positive input is AN1

- 00000 = Positive input is AN0

- Note 1: This option is not available in 28, 36, 40 or 48-pin packages.

- 2: This option is not available in 28, 36 or 40-pin packages.

- 3: This option is not available in 28-pin packages.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0              | U-0              |  |  |

|              | _                 | _                 | _                 | _                 | _                   | _                   | _                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | R/W-0               | R/W-0               | R/W-0            | R/W-0            |  |  |

|              | _                 | —                 | —                 | —                 | G4POL               | G3POL               | G2POL            | G1POL            |  |  |

| 15:8         | R/W-0             | U-0               | R/W-0             | U-0               | R/W-0               | R/W-0               | U-0              | U-0              |  |  |

|              | ON                | —                 | SIDL              | _                 | INTP <sup>(1)</sup> | INTN <sup>(1)</sup> | _                | —                |  |  |

| 7:0          | R/W-0             | R-0, HS, HC       | R/W-0             | U-0               | U-0                 | R/W-0 R/W-0         |                  | R/W-0            |  |  |

|              | LCOE              | LCOUT             | LCPOL             |                   |                     | MODE<2:0>           |                  |                  |  |  |

# REGISTER 21-1: CLCxCON: CLCx CONTROL REGISTER

| Legend:           | HC = Hardware Clearable bit | HS = Hardware Settable bit         |                    |  |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-20 Unimplemented: Read as '0'

| bit 19  | G4POL: Gate 4 Polarity Control bit                                                                                                                          |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = The output of Channel 4 logic is inverted when applied to the logic cell                                                                                |

|         | 0 = The output of Channel 4 logic is not inverted                                                                                                           |

| bit 18  | G3POL: Gate 3 Polarity Control bit                                                                                                                          |

|         | 1 = The output of Channel 3 logic is inverted when applied to the logic cell                                                                                |

|         | 0 = The output of Channel 3 logic is not inverted                                                                                                           |

| bit 17  | G2POL: Gate 2 Polarity Control bit                                                                                                                          |

|         | <ul> <li>1 = The output of Channel 2 logic is inverted when applied to the logic cell</li> <li>0 = The output of Channel 2 logic is not inverted</li> </ul> |

| bit 16  | G1POL: Gate 1 Polarity Control bit                                                                                                                          |

|         | <ul> <li>1 = The output of Channel 1 logic is inverted when applied to the logic cell</li> <li>0 = The output of Channel 1 logic is not inverted</li> </ul> |

| bit 15  | ON: CLCx Enable bit                                                                                                                                         |

|         | 1 = CLCx is enabled and mixing input signals                                                                                                                |

|         | 0 = CLCx is disabled and has logic zero outputs                                                                                                             |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                  |

| bit 13  | SIDL: CLCx Stop in Idle Mode bit                                                                                                                            |

|         | <ul><li>1 = Discontinues module operation when device enters Idle mode</li><li>0 = Continues module operation in Idle mode</li></ul>                        |

| bit 12  | Unimplemented: Read as '0'                                                                                                                                  |

| bit 11  | INTP: CLCx Positive Edge Interrupt Enable bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Interrupt will be generated when a rising edge occurs on LCOUT</li> <li>0 = Interrupt will not be generated</li> </ul>                         |

| bit 10  | INTN: CLCx Negative Edge Interrupt Enable bit <sup>(1)</sup>                                                                                                |

|         | <ul> <li>1 = Interrupt will be generated when a falling edge occurs on LCOUT</li> <li>0 = Interrupt will not be generated</li> </ul>                        |

| bit 9-8 | Unimplemented: Read as '0'                                                                                                                                  |

| bit 7   | LCOE: CLCx Port Enable bit                                                                                                                                  |

|         | 1 = CLCx port pin output is enabled                                                                                                                         |

|         | 0 = CLCx port pin output is disabled                                                                                                                        |

| Note 1: | The INTP and INTN bits should not be set at the same time for proper interrupt function                                                                     |

Note 1: The INTP and INTN bits should not be set at the same time for proper interrupt functionality.

# REGISTER 21-3: CLCxGLS: CLCx GATE LOGIC INPUT SELECT REGISTER (CONTINUED)

| bit 20   | G3D3N: Gate 3 Data Source 3 Negated Enable bit                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = The Data Source 3 inverted signal is enabled for Gate 3                                                                                        |

|          | 0 = The Data Source 3 inverted signal is disabled for Gate 3                                                                                       |

| bit 19   | G3D2T: Gate 3 Data Source 2 True Enable bit                                                                                                        |

|          | <ul> <li>1 = The Data Source 2 signal is enabled for Gate 3</li> <li>0 = The Data Source 2 signal is disabled for Gate 3</li> </ul>                |

| bit 18   | G3D2N: Gate 3 Data Source 2 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 2 inverted signal is enabled for Gate 3                                                                                        |

|          | 0 = The Data Source 2 inverted signal is disabled for Gate 3                                                                                       |

| bit 17   | G3D1T: Gate 3 Data Source 1 True Enable bit                                                                                                        |

|          | <ul> <li>1 = The Data Source 1 signal is enabled for Gate 3</li> <li>0 = The Data Source 1 signal is disabled for Gate 3</li> </ul>                |

| bit 16   | <b>G3D1N:</b> Gate 3 Data Source 1 Negated Enable bit                                                                                              |

| bit to   | 1 = The Data Source 1 inverted signal is enabled for Gate 3                                                                                        |

|          | 0 = The Data Source 1 inverted signal is disabled for Gate 3                                                                                       |

| bit 15   | G2D4T: Gate 2 Data Source 4 True Enable bit                                                                                                        |

|          | 1 = The Data Source 4 signal is enabled for Gate 2                                                                                                 |

| 1.11.4.4 | 0 = The Data Source 4 signal is disabled for Gate 2                                                                                                |

| bit 14   | <b>G2D4N:</b> Gate 2 Data Source 4 Negated Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 2                               |

|          | 0 = The Data Source 4 inverted signal is disabled for Gate 2                                                                                       |

| bit 13   | <b>G2D3T:</b> Gate 2 Data Source 3 True Enable bit                                                                                                 |

|          | 1 = The Data Source 3 signal is enabled for Gate 2                                                                                                 |

|          | 0 = The Data Source 3 signal is disabled for Gate 2                                                                                                |

| bit 12   | G2D3N: Gate 2 Data Source 3 Negated Enable bit                                                                                                     |

|          | <ul><li>1 = The Data Source 3 inverted signal is enabled for Gate 2</li><li>0 = The Data Source 3 inverted signal is disabled for Gate 2</li></ul> |

| bit 11   | <b>G2D2T:</b> Gate 2 Data Source 2 True Enable bit                                                                                                 |

| bit II   | 1 = The Data Source 2 signal is enabled for Gate 2                                                                                                 |

|          | 0 = The Data Source 2 signal is disabled for Gate 2                                                                                                |

| bit 10   | G2D2N: Gate 2 Data Source 2 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 2 inverted signal is enabled for Gate 2                                                                                        |

| hit O    | 0 = The Data Source 2 inverted signal is disabled for Gate 2                                                                                       |

| bit 9    | <b>G2D1T:</b> Gate 2 Data Source 1 True Enable bit<br>1 = The Data Source 1 signal is enabled for Gate 2                                           |

|          | 0 = The Data Source 1 signal is disabled for Gate 2                                                                                                |

| bit 8    | G2D1N: Gate 2 Data Source 1 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 1 inverted signal is enabled for Gate 2                                                                                        |

|          | 0 = The Data Source 1 inverted signal is disabled for Gate 2                                                                                       |

| bit 7    | G1D4T: Gate 1 Data Source 4 True Enable bit                                                                                                        |

|          | <ul> <li>1 = The Data Source 4 signal is enabled for Gate 1</li> <li>0 = The Data Source 4 signal is disabled for Gate 1</li> </ul>                |

| bit 6    | G1D4N: Gate 1 Data Source 4 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 4 inverted signal is enabled for Gate 1                                                                                        |

|          | 0 = The Data Source 4 inverted signal is disabled for Gate 1                                                                                       |

| bit 5    | <b>G1D3T</b> : Gate 1 Data Source 3 True Enable bit                                                                                                |

|          | <ul> <li>1 = The Data Source 3 signal is enabled for Gate 1</li> <li>0 = The Data Source 3 signal is disabled for Gate 1</li> </ul>                |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 |     |         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----|---------|-------------------|------------------|------------------|

| 04.04        | r-1               | r-1               | r-1               | r-1 | r-1     | r-1               | r-1              | r-1              |

| 31:24        | —                 | _                 |                   |     |         | -                 | _                | _                |

| 00.40        | r-1               | r-1               | r-1               | r-1 | r-1     | r-1               | r-1              | r-1              |

| 23:16        | —                 | —                 | -                 | -   | _       | —                 | —                | —                |

| 45.0         | r-1               | r-1               | r-1               | r-1 | r-1     | r-1               | r-1              | r-1              |

| 15:8         | —                 | —                 | -                 | -   | _       | —                 | —                | —                |

| 7.0          | r-1               | r-1               | r-1               | r-1 | R/P     | R/P               | R/P              | R/P              |

| 7:0          |                   |                   |                   |     | LPBOREN | RETVR             | BORE             | N<1:0>           |

### REGISTER 26-3: FPOR/AFPOR: POWER-UP SETTINGS CONFIGURATION REGISTER

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-4 Reserved: Program as '1'

bit 3 LPBOREN: Low-Power BOR Enable bit

1 = Low-Power BOR is enabled when main BOR is disabled

0 = Low-Power BOR is disabled

- bit 2 **RETVR:** Retention Voltage Regulator Enable bit

- 1 = Retention regulator is disabled

0 = Retention regulator is enabled and controlled by the RETEN bit during Sleep

### bit 1-0 BOREN<1:0>: Brown-out Reset Enable bits

- 11 = Brown-out Reset is enabled in hardware; SBOREN bit is disabled

- 10 = Brown-out Reset is enabled only while device is active and disabled in Sleep; SBOREN bit is disabled

- 01 = Brown-out Reset is controlled with the SBOREN bit setting

- 00 = Brown-out Reset is disabled in hardware; SBOREN bit is disabled

# TABLE 26-6: BAND GAP REGISTER MAP

| ess                                           |                      | ۵     | Bits  |       |       |       |       |      |      |      |      |      |      |      |      |        | s      |           |      |

|-----------------------------------------------|----------------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|--------|--------|-----------|------|

| Virtual Addre<br>(BF80_#)<br>Register<br>Name | Bit Range            | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0   | All Reset |      |

| 2200                                          | ANCFG <sup>(1)</sup> | 31:16 | —     | _     | —     | -     | -     | _    | -    | _    |      | —    | -    |      | -    | _      | —      | _         | 0000 |

| 2300                                          | ANCEG /              | 15:0  | _     | _     | _     |       |       | _    |      | _    |      | -    |      |      |      | VBGADC | VBGCMP |           | 0000 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

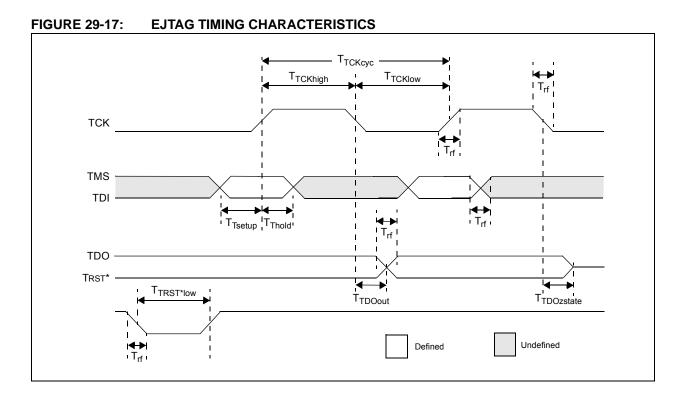

## TABLE 29-37: EJTAG TIMING REQUIREMENTS

| AC CHARACTERISTICS |            |                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |            |  |  |

|--------------------|------------|-----------------------------------------------------|-------------------------------------------------------|------|-------|------------|--|--|

| Param<br>No.       | Symbol     | Description <sup>(1)</sup>                          | Min.                                                  | Max. | Units | Conditions |  |  |

| EJ1                | Ттсксус    | TCK Cycle Time                                      | 25                                                    | —    | ns    |            |  |  |

| EJ2                | Ттскнідн   | TCK High Time                                       | 10                                                    | _    | ns    |            |  |  |

| EJ3                | TTCKLOW    | TCK Low Time                                        | 10                                                    | _    | ns    |            |  |  |

| EJ4                | TTSETUP    | TAP Signals Setup Time<br>before Rising TCK         | 5                                                     | —    | ns    |            |  |  |

| EJ5                | TTHOLD     | TAP Signals Hold Time<br>after Rising TCK           | 3                                                     | —    | ns    |            |  |  |

| EJ6                | Ттрооит    | TDO Output Delay Time<br>from Falling TCK           |                                                       | 5    | ns    |            |  |  |

| EJ7                | TTDOZSTATE | TDO 3-State Delay Time<br>from Falling TCK          |                                                       | 5    | ns    |            |  |  |

| EJ8                | TTRSTLOW   | TRST Low Time                                       | 25                                                    | _    | ns    |            |  |  |

| EJ9                | Trf        | TAP Signals Rise/Fall<br>Time, All Input and Output | _                                                     | _    | ns    |            |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

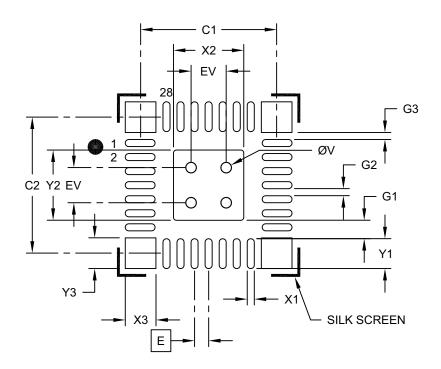

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M6) - 4x4x0.6 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## **RECOMMENDED LAND PATTERN**

|                                 | MILLIMETERS |          |      |      |

|---------------------------------|-------------|----------|------|------|

| Dimension Limits                |             | MIN      | NOM  | MAX  |

| Contact Pitch                   | E           | 0.40 BSC |      |      |

| Center Pad Width                | X2          |          |      | 2.00 |

| Center Pad Length               | Y2          |          |      | 2.00 |

| Contact Pad Spacing             | C1          |          | 3.90 |      |

| Contact Pad Spacing             | C2          |          | 3.90 |      |

| Contact Pad Width (X28)         | X1          |          |      | 0.20 |

| Contact Pad Length (X28)        | Y1          |          |      | 0.85 |

| Contact Pad to Center Pad (X28) | G1          |          | 0.52 |      |

| Contact Pad to Pad (X24)        | G2          | 0.20     |      |      |

| Contact Pad to Corner Pad (X8)  | G3          | 0.20     |      |      |

| Corner Anchor Width (X4)        | X3          |          |      | 0.78 |

| Corner Anchor Length (X4)       | Y3          |          |      | 0.78 |

| Thermal Via Diameter            | V           |          | 0.30 |      |

| Thermal Via Pitch               | EV          |          | 1.00 |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2333-M6 Rev B

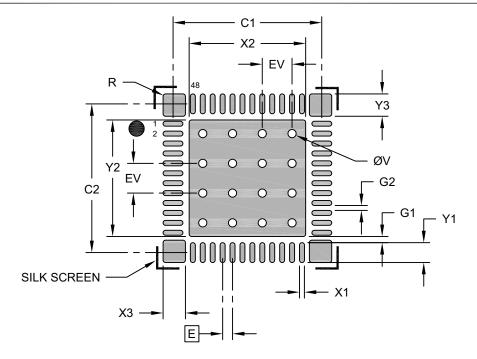

# 48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M4) - 6x6 mm Body [UQFN] With Corner Anchors and 4.6x4.6 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |          |      |      |

|---------------------------------|-------------|----------|------|------|

| Dimension                       | MIN         | NOM      | MAX  |      |

| Contact Pitch                   | Е           | 0.40 BSC |      |      |

| Center Pad Width                | X2          |          |      | 4.70 |

| Center Pad Length               | Y2          |          |      | 4.70 |

| Contact Pad Spacing             | C1          |          | 6.00 |      |

| Contact Pad Spacing             | C2          |          | 6.00 |      |

| Contact Pad Width (X48)         | X1          |          |      | 0.20 |

| Contact Pad Length (X48)        | Y1          |          |      | 0.80 |

| Corner Anchor Pad Width (X4)    | X3          |          |      | 0.90 |

| Corner Anchor Pad Length (X4)   | Y3          |          |      | 0.90 |

| Pad Corner Radius (X 20)        | R           |          |      | 0.10 |

| Contact Pad to Center Pad (X48) | G1          | 0.25     |      |      |

| Contact Pad to Contact Pad      | G2          | 0.20     |      |      |

| Thermal Via Diameter            | V           |          | 0.33 |      |

| Thermal Via Pitch               | EV          |          | 1.20 |      |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing C04-2442A-M4

NOTES: