Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 52                                                                                |

| Program Memory Size        | 64KB (64K x 8)                                                                    |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 16K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 20x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0064gpm064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

## 2.1 Basic Connection Requirements

Getting started with the PIC32MM0256GPM064 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pin (see Section 2.4 "Voltage Regulator Pin (VCAP)")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5** "**ICSP Pins**")

- OSC1 and OSC2 pins, when external oscillator source is used (see Section 2.7 "External Oscillator Pins")

- VUSB3V3 pin, this pin must be powered for USB operation (see Section 18.4 "Powering the USB Transceiver")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS, is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances, as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

## REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit Bit<br>29/21/13/5 28/20/12/4 |       | Bit<br>27/19/11/3          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|----------------------------------|-------|----------------------------|-------------------|----------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0                            | R/W-0 | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |

| 31:24        |                   | PRI7SS            | <3:0>(1)                         |       | PRI6SS<3:0> <sup>(1)</sup> |                   |                      |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0                            | R/W-0 | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |

| 23:16        |                   | PRI5SS            | <3:0> <sup>(1)</sup>             |       |                            | PRI4SS            | <3:0> <sup>(1)</sup> |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                            | R/W-0 | R/W-0                      | R/W-0             | R/W-0                | R/W-0            |  |  |  |

| 15:8         |                   | PRI3SS            | <3:0> <sup>(1)</sup>             |       | PRI2SS<3:0> <sup>(1)</sup> |                   |                      |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                            | R/W-0 | U-0                        | U-0               | U-0                  | R/W-0            |  |  |  |

| 7:0          |                   | PRI1SS            | <3:0>(1)                         |       | —                          |                   |                      | SS0              |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-28 PRI7SS<3:0>: Interrupt with Priority Level 7 Shadow Set bits<sup>(1)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        | IFS<31:24>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:16        | IFS<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | IFS<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | IFS               | <7:0>             |                   |                  |                  |  |  |  |  |  |  |  |

#### REGISTER 7-5: IFSx: INTERRUPT FLAG STATUS REGISTER x

## Legend:

| 3                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IFS<31:0>: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-3 for the exact bit definitions.

### REGISTER 7-6: IECx: INTERRUPT ENABLE CONTROL REGISTER x

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit<br>30/22/14/6 29/21/13/5 |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|----------------------------------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        | IEC<31:24>        |                                  |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:16        | IEC<23:16>        |                                  |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | IEC<15:8>         |                                  |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0                            | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

|              |                   |                                  |       | IEC               | <7:0>             |                   |                  |                  |  |  |  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC<31-0>: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-3 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | _                 | _                 |                   | IP3<2:0>          | IS3<1:0>          |                  |                  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | _                 |                   | IP2<2:0>          |                   | IS2<             | 1:0>             |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 |                   | IP1<2:0>          |                   | IS1<             | 1:0>             |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | 1:0>             |

## REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x

#### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: | Interrupt | Priority 3 bits |

|-----------|-----------|-----------|-----------------|

- - 00 = Interrupt subpriority is 0

## bit 23-21 Unimplemented: Read as '0'

- bit 20-18 IP2<2:0>: Interrupt Priority 2 bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority 2 bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

# PIC32MM0256GPM064 FAMILY

NOTES:

## TABLE 10-8: PORTD REGISTER MAP

| ess                         |                                 |           |       |       |       |       |         |        |      | Bits |      |      |      |      |      |              |                       |      |               |  |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------|--------|------|------|------|------|------|------|------|--------------|-----------------------|------|---------------|--|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(2)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10  | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2         | 17/1                  | 16/0 | All<br>Resets |  |

| 2EB0                        | ANSELD                          | 31:16     |       | _     | —     | _     | _       |        | _    | _    | —    | _    | _    | _    |      | _            | —                     | _    | 0000          |  |

| ZLBU                        | ANGLED                          | 15:0      | -     | —     | —     | —     | —       |        | —    | —    | —    | —    | _    | —    | —    | —            | —                     | —    | 0000          |  |

| 2EC0                        | TRISD                           | 31:16     | -     | —     | —     | —     | —       |        | —    | —    | —    | —    | _    | —    | —    | —            | —                     | —    | 0000          |  |

| 200                         | TRISD                           | 15:0      | -     | —     | —     | —     | —       |        | —    | —    | —    | —    | _    | —    |      | TRISD        | <3:0>(1)              |      | 030F          |  |

| 2ED0                        | PORTD                           | 31:16     |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| ZEDU                        | FURID                           | 15:0      |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | RD<3         | 3:0>(1)               |      | 0000          |  |

| 2EE0                        | LATD                            | 31:16     |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| ZEEU                        | LAID                            | 15:0      |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | LATD<        | :3:0>(1)              |      | 0000          |  |

| 2EF0                        | ODCD                            | 31:16     |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| ZEFU                        | UDCD                            | 15:0      |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | ODCD         | <3:0>(1)              |      | 0000          |  |

| 2F00                        | CNPUD                           | 31:16     |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| 2F00                        | CINFUD                          | 15:0      |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | CNPUD        | <3:0>(1)              |      | 0000          |  |

| 2F10                        | CNPDD                           | 31:16     |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| 2F10                        | CINFUD                          | 15:0      |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | CNPDD        | <3:0>(1)              |      | 0000          |  |

| 2F20                        | CNCOND                          | 31:16     |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| 2620                        | CINCOIND                        | 15:0      | ON    | —     | —     | _     | CNSTYLE | PORT32 | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| 2F30                        | CNEN0D                          | 31:16     |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | —            | —                     | —    | 0000          |  |

| 2530                        | CINEINUD                        | 15:0      |       | —     | —     | _     | —       |        | —    |      | —    | —    |      | —    |      | CNIE0D       | )<3:0>(1)             |      | 0000          |  |

| 2F40                        | CNSTATD                         | 31:16     | _     | _     | _     | _     | _       | _      | _    | _    | —    | _    | -    | -    | _    | _            | _                     | _    | 0000          |  |

| 2F40                        | CNSTALD                         | 15:0      | _     | _     | _     | _     | _       | _      | _    | _    | —    | _    | -    | -    |      | CNSTAT       | D<3:0> <sup>(1)</sup> |      | 0000          |  |

| 2F50                        | CNEN1D                          | 31:16     | _     | _     | _     | _     | _       | _      | _    | _    | —    | _    | -    | -    | _    | _            | _                     | _    | 0000          |  |

| 2F50                        | CNENTD                          | 15:0      | _     | _     | _     | _     | _       | _      | _    | _    | —    | _    | -    | -    |      | CNIE1D       | )<3:0>(1)             |      | 0000          |  |

| 2F60                        | CNFD                            | 31:16     | _     | _     | _     | _     | _       | _      | _    | _    | —    | _    | -    | -    | _    | _            | _                     | _    | 0000          |  |

| 2F00                        | CNFD                            | 15:0      | _     | _     | _     | _     | _       | _      | _    | _    | —    | _    | -    | -    |      | CNFD-        | <3:0>(1)              |      | 0000          |  |

| 2F70                        | SR0D                            | 31:16     |       | _     | —     | _     | _       |        | _    | _    | _    | _    | _    | _    | -    | _            | _                     | —    | 0000          |  |

| 2F70                        | 2KUD                            | 15:0      | _     | —     | _     | _     | —       |        | _    | —    | _    | _    | _    | —    |      | SR0D<3:0>(1) |                       |      |               |  |

| 2F80                        | SR1D                            | 31:16     | _     | _     | _     |       | _       |        | _    |      | _    | _    | _    | _    | _    |              | —                     | —    | 0000          |  |

| 200                         | SKID                            | 15:0      | _     | _     | —     | _     | _       |        | _    | _    | _    | _    | _    | _    |      | SR1D<        | <3:0>(1)              |      | 0000          |  |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Bits<3:1> are not available on 48-pin devices; bits are not available on 36 and 28-pin devices.

2: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

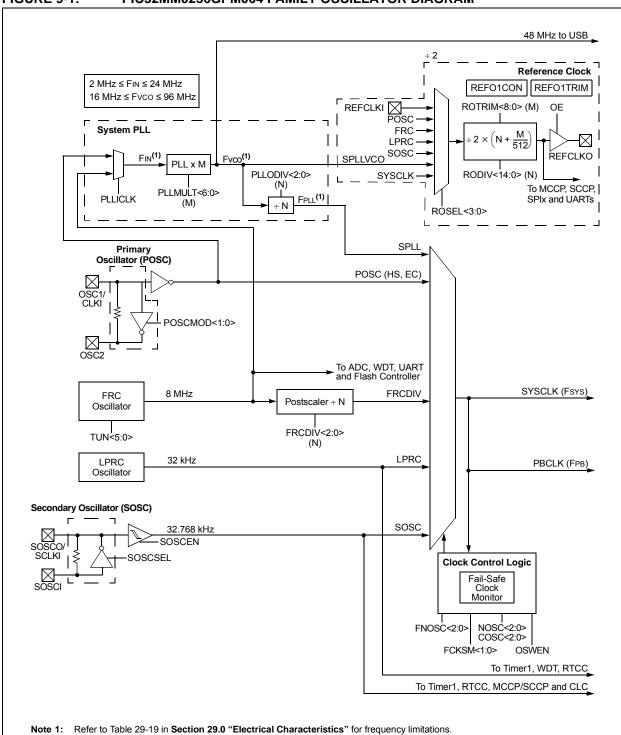

#### 11.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 14. "Timers" (DS60001105) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

PIC32MM0256GPM064 family devices feature one synchronous/asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can be clocked from different sources, such as the Peripheral Bus Clock (PBCLK), Secondary Oscillator (SOSC), T1CK pin or LPRC oscillator.

The following modes are supported by Timer1:

- · Synchronous Internal Timer

- · Synchronous Internal Gated Timer

- Synchronous External Timer

- · Asynchronous External Timer

The timer has a selectable clock prescaler and can operate in Sleep and Idle modes.

#### FIGURE 11-1: **TIMER1 BLOCK DIAGRAM**

## 11.1 Timer1 Control Register

## TABLE 11-1: TIMER1 REGISTER MAP

| ress<br>)                   | <b>b</b> a                      | е        | Bits  |       |       |       |       |       |      |       |        |      |      |        | ts   |       |      |      |           |

|-----------------------------|---------------------------------|----------|-------|-------|-------|-------|-------|-------|------|-------|--------|------|------|--------|------|-------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Rang | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Reset |

| 0000                        | TIOON                           | 31:16    | _     | _     | —     | —     | —     | _     | —    | —     | —      | —    | —    | —      | _    | —     | —    | —    | 0000      |

| 8000                        | T1CON                           | 15:0     | ON    | —     | SIDL  | TWDIS | TWIP  | —     | TECS | <1:0> | TGATE  | _    | TCKP | S<1:0> | _    | TSYNC | TCS  | —    | 0000      |

| 0010                        | TMR1                            | 31:16    |       | _     | _     | _     | _     | _     | _    | _     | _      | _    | _    | _      | _    | _     | _    | _    | 0000      |

| 8010                        | TIVIRT                          | 15:0     |       |       |       |       |       |       |      | TMR1< | <15:0> |      |      |        |      |       |      |      | 0000      |

| 8020                        | PR1                             | 31:16    | _     | _     | —     | _     | —     | _     |      | —     | _      | —    | _    | _      |      | _     |      | —    | 0000      |

| 0020                        |                                 | 15:0     |       |       |       |       |       |       |      |       |        |      |      |        | FFFF |       |      |      |           |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

**2:** PR1 values of '0' and '1' are reserved.

## TABLE 14-1: MCCP/SCCP REGISTER MAP (CONTINUED)

| ress<br>()                  | 20                              | е                                              |                  |        |          |        |         |        |           |       | Bits       |         |         |        |         |          |          |       |               |

|-----------------------------|---------------------------------|------------------------------------------------|------------------|--------|----------|--------|---------|--------|-----------|-------|------------|---------|---------|--------|---------|----------|----------|-------|---------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                      | 31/15            | 30/14  | 29/13    | 28/12  | 27/11   | 26/10  | 25/9      | 24/8  | 23/7       | 22/6    | 21/5    | 20/4   | 19/3    | 18/2     | 17/1     | 16/0  | All<br>Resets |

| 0000                        | CCP6CON1                        | 31:16                                          | OPSSRC           | RTRGEN |          |        |         | OPS<   | 3:0>      |       | TRIGEN     | ONESHOT | ALTSYNC |        |         | SYNC<4:0 | >        |       | 0000          |

| 0600                        | CCP6CONT                        | 15:0                                           | ON               | _      | SIDL     | CCPSLP | TMRSYNC | C      | LKSEL<2:0 | >     | TMRF       | S<1:0>  | T32     | CCSEL  |         | MOE      | )<3:0>   |       | 0000          |

| 0040                        | CCP6CON2                        | 31:16                                          | OENSYNC          | _      | OCFEN    | OCEEN  | OCDEN   | OCCEN  | OCBEN     | OCAEN | ICGS       | M<1:0>  | _       | AUXO   | JT<1:0> |          | ICS<2:0> |       | 0100          |

| 0610                        | CCPOCOINZ                       | 15:0                                           | PWMRSEN          | ASDGM  | _        | SSDG   | _       | _      | _         | _     |            |         |         | ASDO   | G<7:0>  |          |          |       | 0000          |

| 0600                        | CCP6CON3                        | 31:16                                          | OETRIG           | 0      | SCNT<2:0 | >      | —       | _      | _         | _     | _          | _       | POLACE  | _      | PSSAC   | E<1:0>   | —        | —     | 0000          |

| 0620                        | CCPOCONS                        | 15:0                                           |                  |        |          |        |         |        |           |       |            |         | 0000    |        |         |          |          |       |               |

| 0620                        | CODESTAT                        | 31:16 - - - - - - - PRLWIP TMRLWIP RBWIP RBWIP |                  |        |          |        |         |        |           |       | 0000       |         |         |        |         |          |          |       |               |

| 0630                        | CCP05TAI                        | 15:0                                           | _                | _      | _        | _      | _       | ICGARM | _         | _     | CCPTRIG    | TRSET   | TRCLR   | ASEVT  | SCEVT   | ICDIS    | ICOV     | ICBNE | 0000          |

| 0640                        | CCP6TMR                         | 31:16                                          |                  |        |          |        |         |        |           | ΤN    | /IRH<15:0> |         |         |        |         |          |          |       | 0000          |

| 0040                        | CCFOTIMR                        | 15:0                                           |                  |        |          |        |         |        |           |       |            | 0000    |         |        |         |          |          |       |               |

| 0650                        | CCP6PR                          | B 31:16 PRH<15:0> 0                            |                  |        |          |        |         |        |           |       | 0000       |         |         |        |         |          |          |       |               |

| 0050                        | CUPUPK                          | 15:0 PRL<15:0> 00                              |                  |        |          |        |         |        |           |       |            | 0000    |         |        |         |          |          |       |               |

| 0660                        | CCP6RA                          | 31:16                                          | —                | —      | _        |        | —       | _      |           | —     | _          | —       | —       | _      | _       | _        |          |       | 0000          |

| 0000                        | COPURA                          | 15:0                                           |                  |        |          |        |         |        |           | C     | MPA<15:0>  |         |         |        |         |          |          |       | 0000          |

| 0670                        | CCP6RB                          | 31:16                                          | —                | —      | —        | _      | —       | —      | —         | —     | —          | —       | —       | —      | —       | —        | -        | _     | 0000          |

| 0070                        | COPURD                          | 15:0                                           |                  |        |          |        |         |        |           | CN    | MPB<15:0>  |         |         |        |         |          |          |       | 0000          |

| 0680                        | CCP6BUF                         | 31:16                                          |                  |        |          |        |         |        |           | BL    | JFH<15:0>  |         |         |        |         |          |          |       | 0000          |

| 0000                        | CCF0D01                         | 15:0                                           |                  |        |          |        |         |        |           | Bl    | JFL<15:0>  |         |         |        |         |          |          |       | 0000          |

| 0700                        | CCP7CON1                        | 31:16                                          | OPSSRC           | RTRGEN | —        | _      |         | OPS<   | 3:0>      |       | TRIGEN     | ONESHOT | ALTSYNC |        |         | SYNC<4:0 | >        |       | 0000          |

| 0700                        |                                 | 15:0                                           | ON               | _      | SIDL     | CCPSLP | TMRSYNC | C      | LKSEL<2:0 | >     | TMRF       | PS<1:0> | T32     | CCSEL  |         | MOE      | )<3:0>   |       | 0000          |

| 0710                        | CCP7CON2                        | 31:16                                          | OENSYNC          | _      | OCFEN    | OCEEN  | OCDEN   | OCCEN  | OCBEN     | OCAEN | ICGS       | M<1:0>  | —       | AUXO   | JT<1:0> |          | ICS<2:0> |       | 0100          |

| 0/10                        |                                 | 15:0                                           | PWMRSEN          | ASDGM  |          | SSDG   | _       | —      | _         | —     |            |         |         | ASDO   | G<7:0>  |          |          |       | 0000          |

| 0720                        | CCP7CON3                        | 31:16                                          | OETRIG           | 0      | SCNT<2:0 | >      | —       | —      | _         |       | —          | —       | POLACE  | —      | PSSAC   | E<1:0>   | _        | —     | 0000          |

| 0720                        |                                 | 15:0                                           | —                | _      | —        |        | —       | —      | _         |       | —          | —       | —       | —      | —       | —        | _        | —     | 0000          |

| 0730                        | CCP7STAT                        | 31:16                                          | _                | _      |          | _      | —       | —      | _         | —     | —          | —       | _       | PRLWIP | TMRHWIP | TMRLWIP  | RBWIP    | RAWIP | 0000          |

| 5150                        |                                 | 15:0                                           | _                | —      | —        | —      | —       | ICGARM | _         | -     | CCPTRIG    | TRSET   | TRCLR   | ASEVT  | SCEVT   | ICDIS    | ICOV     | ICBNE | 0000          |

| 0740                        | CCP7TMR                         | 31:16                                          |                  |        |          |        |         |        |           | ΤN    | /IRH<15:0> |         |         |        |         |          |          |       | 0000          |

| 07-10                       |                                 | 15:0                                           |                  |        |          |        |         |        |           | TN    | /IRL<15:0> |         |         |        |         |          |          |       | 0000          |

| 0750                        | CCP7PR                          | 31:16                                          | 6 PRH<15:0> 0000 |        |          |        |         |        |           |       |            |         |         |        |         |          |          |       |               |

| 5755                        | 501711                          | 15:0                                           |                  |        |          |        |         |        |           | Р     | RL<15:0>   |         |         |        |         |          |          |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|------------------|--|--|--|--|

| 04.04        | R/W-0 U-0         |                   | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-1            |  |  |  |  |

| 31:24        | OENSYNC —         |                   | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN            |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | U-0                  | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |  |  |  |

| 23:16        | ICGSM             | 1<1:0>            | -                    | AUXOL                | JT<1:0>              |                      | ICS<2:0>             |                  |  |  |  |  |

| 45.0         | R/W-0 R/W-0       |                   | U-0                  | R/W-0                | U-0                  | U-0                  | U-0                  | U-0              |  |  |  |  |

| 15:8         | PWMRSEN           | ASDGM             | _                    | SSDG                 | _                    | _                    | —                    | _                |  |  |  |  |

| 7.0          | R/W-0 R/W-0       |                   | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |  |  |  |

| 7:0          | ASDG<7:0>         |                   |                      |                      |                      |                      |                      |                  |  |  |  |  |

## REGISTER 14-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31 **OENSYNC:** Output Enable Synchronization bit

- 1 = Update by output enable bits occurs on the next Time Base Reset or rollover

- 0 = Update by output enable bits occurs immediately

- bit 30 Unimplemented: Read as '0'

#### bit 29-24 OC<F:A>EN: Output Enable/Steering Control bits<sup>(1)</sup>

- 1 = OCx pin is controlled by the CCPx module and produces an output compare or PWM signal

- 0 = OCx pin is not controlled by the CCPx module; the pin is available to the port logic or another peripheral multiplexed on the pin

#### bit 23-22 ICGSM<1:0>: Input Capture Gating Source Mode Control bits

- 11 = Reserved

- 10 = One-Shot mode: Falling edge from gating source disables future capture events (ICDIS = 1)

- 01 = One-Shot mode: Rising edge from gating source enables future capture events (ICDIS = 0)

- 00 = Level-Sensitive mode: A high level from gating source will enable future capture events; a low level will disable future capture events

- bit 21 Unimplemented: Read as '0'

#### bit 20-19 AUXOUT<1:0>: Auxiliary Output Signal on Event Selection bits

- 11 = Input capture or output compare event; no signal in Timer mode

- 10 = Signal output depends on module operating mode

- 01 = Time base rollover event (all modes)

- 00 = Disabled

- bit 18-16 ICS<2:0>: Input Capture Source Select bits

- 111 = CLC4 output

- 110 = CLC3 output

- 101 = CLC2 output

- 100 = CLC1 output

- 011 = Comparator 3 output

- 010 = Comparator 2 output

- 001 = Comparator 1 output

- 000 = ICMx pin<sup>(2)</sup>

- bit 15 PWMRSEN: CCPx PWM Restart Enable bit

- 1 = ASEVT bit clears automatically at the beginning of the next PWM period, after the shutdown input has ended

- 0 = ASEVT must be cleared in software to resume PWM activity on output pins

- Note 1: OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

- **2:** This pin is remappable from SCCP modules.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 |                   | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 |                   | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 |                   |                  | _                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

## REGISTER 18-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| R = Re  | adable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|---------|-------------|------------------|---------------------------|--------------------|

| -n = Va | alue at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device is enabled

- 0 = Direct connection to a low-speed device is disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NACK'd transactions are disabled

- 0 = Retry NACK'd transactions are enabled; retry done in hardware

- bit 5 Unimplemented: Read as '0'

- bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

### If EPTXEN = 1 and EPRXEN = 1:

1 = Disables Endpoint n from control transfers; only TX and RX transfers are allowed

0 = Enables Endpoint n for control (SETUP) transfers; TX and RX transfers are also allowed Otherwise, this bit is ignored.

#### bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint handshake is enabled

- 0 = Endpoint handshake is disabled (typically used for isochronous endpoints)

## 22.1 Comparator Control Registers

## TABLE 22-1: COMPARATORS 1, 2 AND 3 REGISTER MAP

| ess                         |                                 | â         |       |       |       |       |       |       |      | Bits     |      |        |      |      |      |       |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|----------|------|--------|------|------|------|-------|-------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0  | All Resets |

| 2200                        | CMSTAT                          | 31:16     | _     | —     | —     |       |       |       | —    | _        |      |        |      | —    |      | C3EVT | C2EVT | C1EVT | 0000       |

| 2300                        | CIVISTAT                        | 15:0      | _     | —     | SIDL  |       |       |       | _    | CVREFSEL | _    |        |      | —    |      | C3OUT | C2OUT | C10UT | 0000       |

| 2310                        | CM1CON                          | 31:16     | _     | —     | —     |       |       |       | _    | —        |      |        | _    | —    |      | _     | —     |       | 0000       |

| 2310                        | CIVITCON                        | 15:0      | ON    | COE   | CPOL  | -     |       |       | CEVT | COUT     | EVPO | L<1:0> | -    | CREF | -    | —     | ССН   | <1:0> | 0000       |

| 2330                        | CM2CON                          | 31:16     | -     | —     | —     | -     |       |       | —    | _        |      | -      | -    | —    | -    | —     | —     |       | 0000       |

| 2330                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | _     | _     | _     | CEVT | COUT     | EVPO | L<1:0> | _    | CREF | _    | _     | ССН   | <1:0> | 0000       |

| 2350                        | CM3CON                          | 31:16     | _     | —     | —     |       |       |       | _    | —        | _    |        |      | —    |      | _     | _     |       | 0000       |

| 2350                        | CIVISCON                        | 15:0      | ON    | COE   | CPOL  | -     | _     | _     | CEVT | COUT     | EVPO | L<1:0> | _    | CREF | _    | —     | CCH   | <1:0> | 0000       |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

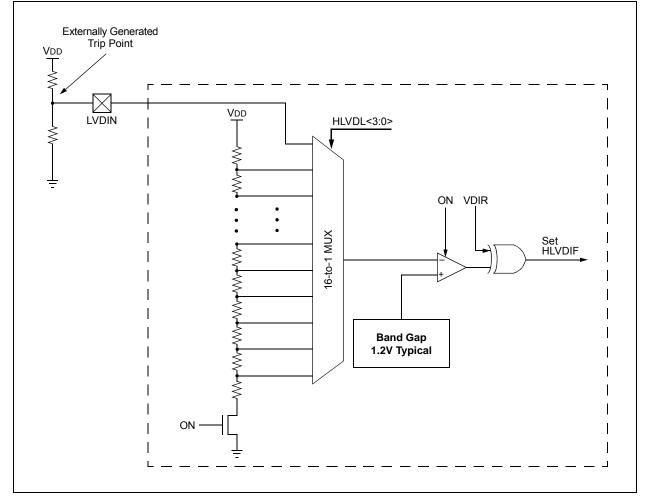

## 24.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The High/Low-Voltage Detect (HLVD) module is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The HLVD Control register (see Register 24-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

## FIGURE 24-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

## TABLE 25-2: PERIPHERAL MODULE DISABLE REGISTERS MAP

| ess                         |                                 |           |        |        |        |        |         |        |        | Bits   |      |      |      |        |      |        |        |        |            |

|-----------------------------|---------------------------------|-----------|--------|--------|--------|--------|---------|--------|--------|--------|------|------|------|--------|------|--------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14  | 29/13  | 28/12  | 27/11   | 26/10  | 25/9   | 24/8   | 23/7 | 22/6 | 21/5 | 20/4   | 19/3 | 18/2   | 17/1   | 16/0   | All Resets |

| 35B0                        | PMDCON                          | 31:16     |        | _      | _      |        | _       | _      |        | _      |      |      |      | —      | _    | _      |        | —      | FFFF       |

| 3380                        | FINDCON                         | 15:0      | _      | —      | —      | —      | PMDLOCK | —      | —      | —      | —    | -    | —    | —      | —    | —      | —      | —      | F7FF       |

| 35C0                        | PMD1                            | 31:16     | _      | —      | —      | —      | —       | —      | —      | —      | —    | -    | —    | HLVDMD | —    | —      | —      | —      | FFEF       |

| 3300                        | FIVIDI                          | 15:0      | _      | —      | —      | VREFMD | —       | —      | —      | —      | —    | -    | —    | —      | —    | —      | —      | ADCMD  | EFFE       |

| 35D0                        | PMD2                            | 31:16     | _      | —      | —      | —      | CLC4MD  | CLC3MD | CLC2MD | CLC1MD | —    | -    | —    | —      | —    | —      | —      | —      | FOFF       |

| 3300                        | FIVIDZ                          | 15:0      | _      | —      | —      | —      | —       | —      | —      | —      | —    | -    | —    | —      | —    | CMP3MD | CMP2MD | CMP1MD | FFF8       |

| 35E0                        | PMD3                            | 31:16     | _      | —      | _      | _      | —       | _      | _      | —      | _    | _    | _    | —      | _    | —      | _      | CCP9MD | FFFE       |

| 00L0                        | T WID5                          | 15:0      | CCP8MD | CCP7MD | CCP6MD | CCP5MD | CCP4MD  | CCP3MD | CCP2MD | CCP1MD | _    | _    | —    | —      | _    | —      | _      | —      | 00FF       |

| 35F0                        | PMD4                            | 31:16     | —      | —      | —      | —      | —       | _      | _      | —      | _    | _    | —    | —      | _    | —      | _      | —      | FFFF       |

| 331.0                       |                                 | 15:0      | —      | —      | —      | —      | —       | _      | _      | —      | _    | _    | —    | —      | _    | T3MD   | T2MD   | T1MD   | FFF8       |

| 3600                        | PMD5                            | 31:16     | —      | —      | —      | —      | —       | _      | _      | USBMD  | _    | _    | —    | —      | _    | I2C3MD | I2C2MD | I2C1MD | FEF8       |

| 3000                        | T WID5                          | 15:0      | —      | —      | —      | —      | —       | SPI3MD | SPI2MD | SPI1MD | _    | _    | —    | —      | _    | U3MD   | U2MD   | U1MD   | F8F8       |

| 3610                        | PMD6                            | 31:16     | _      | —      | _      | _      | —       | _      | _      | —      | _    | _    | _    | —      | _    | —      | _      | —      | FEFF       |

| 5010                        | i wiDo                          | 15:0      | _      | —      | _      | _      | —       | _      | _      | REFOMD | _    | _    | _    | —      | _    | —      | _      | RTCCMD | FEFE       |

| 3620                        | PMD7                            | 31:16     | _      | —      | _      | _      | —       | _      | _      | —      | _    | _    | _    | —      | _    | —      | _      | —      | FFFF       |

| 5020                        |                                 | 15:0      | _      | —      | _      | —      | —       | _      | —      | —      | _    | —    | —    | DMAMD  | _    | —      | _      | _      | FFEF       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

## 28.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- · Simulators

- MPLAB X SIM Software Simulator

- · Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 28.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac  $OS^{®}$  X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- · Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| Operatir     | <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                           |            |     |            |    |          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------|---------------------------|------------|-----|------------|----|----------|--|--|--|--|

| Param<br>No. | Symbol Characteristic Min Ivn Max Units Comments                                             |                           |            |     |            |    |          |  |  |  |  |

| D300         | VIOFF                                                                                        | Input Offset Voltage      | -20        | —   | +20        | mV | (Note 1) |  |  |  |  |

| D301         | VICM                                                                                         | Input Common-Mode Voltage | Vss – 0.3V | _   | VDD + 0.3V | V  | (Note 1) |  |  |  |  |

| D307         | TRESP                                                                                        | Response Time             | —          | 150 | _          | ns | (Note 2) |  |  |  |  |

## TABLE 29-14: COMPARATOR DC SPECIFICATIONS

**Note 1:** Parameters are characterized but not tested.

2: Measured with one input at VDD/2 and the other transitioning from VSS to VDD, 40 mV step, 15 mV overdrive.

## TABLE 29-15: VOLTAGE REFERENCE DC SPECIFICATIONS

| Operatin     | <b>Operating Conditions:</b> 2.0V < VDD < 3.6V, -40°C < TA < +85°C (unless otherwise stated) |                         |     |     |     |       |          |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------|-------------------------|-----|-----|-----|-------|----------|--|--|--|--|

| Param<br>No. | Symbol                                                                                       | Characteristic          | Min | Тур | Max | Units | Comments |  |  |  |  |

| VRD310       | TSET                                                                                         | Settling Time           | —   | _   | 10  | μs    | (Note 1) |  |  |  |  |

| VRD311       | VRAA                                                                                         | Absolute Accuracy       | -1  | —   | 1   | LSb   |          |  |  |  |  |

| VRD312       | VRur                                                                                         | Unit Resistor Value (R) | _   | 4.5 | _   | kΩ    |          |  |  |  |  |

**Note 1:** Measures the interval while DACDAT<4:0> transitions from '11111' to '00000'.

# 48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M4) - 6x6 mm Body [UQFN] With Corner Anchors and 4.6x4.6 mm Exposed Pad

Microchip Technology Drawing C04-442A-M4 Sheet 1 of 2

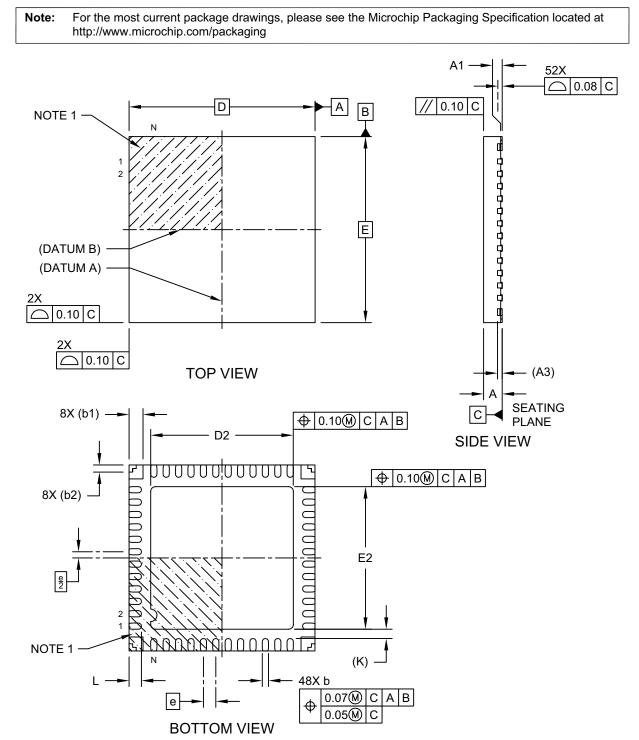

## 48-Lead Thin Quad Flatpack (PT) - 7x7x1.0 mm Body [TQFP] With Thermal Tab

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

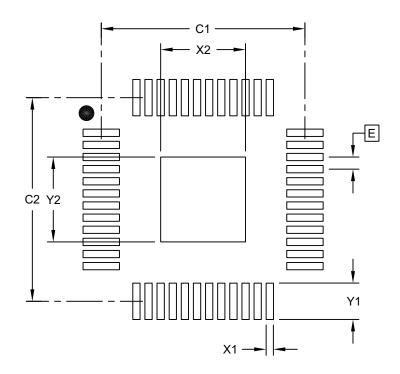

## RECOMMENDED LAND PATTERN

|                            | Units                      |          |      |      |  |  |

|----------------------------|----------------------------|----------|------|------|--|--|

| Dimensi                    | on Limits                  | MIN      | NOM  | MAX  |  |  |

| Contact Pitch              | E                          | 0.50 BSC |      |      |  |  |

| Optional Center Tab Width  | tional Center Tab Width X2 |          |      |      |  |  |

| Optional Center Tab Length | Y2                         |          | 3.50 |      |  |  |

| Contact Pad Spacing        | C1                         |          | 8.40 |      |  |  |

| Contact Pad Spacing        | C2                         |          | 8.40 |      |  |  |

| Contact Pad Width (X48)    | X1                         |          |      | 0.30 |  |  |

| Contact Pad Length (X48)   | Y1                         |          |      | 1.50 |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2183A