Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-VQFN Exposed Pad                                                              |

| Supplier Device Package    | 28-QFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0128gpm028-i-ml |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 4.0 MEMORY ORGANIZATION

PIC32MM microcontrollers provide 4 GBytes of unified virtual memory address space. All memory regions, including program memory, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The data memory can be made executable, allowing the CPU to execute code from data memory.

Key features include:

- 32-Bit Native Data Width

- Separate Boot Flash Memory (BFM) for Protected Code

- Robust Bus Exception Handling to Intercept Runaway Code

- Simple Memory Mapping with Fixed Mapping Translation (FMT) Unit

The PIC32MM0256GPM064 family devices implement two address spaces: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions. Physical addresses are used by peripherals, such as Flash controllers, that access memory independently of the CPU.

The virtual address space is divided into two segments of 512 Mbytes each, labeled kseg0 and kseg1. The Program Flash Memory (PFM) and Data RAM Memory (DRM) are accessible from either kseg0 or kseg1, while the Boot Flash Memory (BFM) and peripheral SFRs are accessible only from kseg1.

The Fixed Mapping Translation (FMT) unit translates the memory segments into corresponding physical address regions. Figure 4-1 through Figure 4-3 illustrate the fixed mapping scheme, implemented by the PIC32MM0256GPM064 family core, between the virtual and physical address space.

The mapping of the memory segments depends on the CPU error level, set by the ERL bit in the CPU STATUS register. Error level is set (ERL = 1) by the CPU on a Reset, Soft Reset or Non-Maskable Interrupt (NMI). In this mode, the CPU can access memory by the physical address. This mode is provided for compatibility with other MIPS processor cores that use a TLB-based MMU. The C start-up code clears the ERL bit to zero, so that when application software starts up, it sees the proper virtual to physical memory mapping.

# 4.1 Alternate Configuration Bits Space

Every Configuration Word has an associated Alternate Word (designated by the letter A as the first letter in the name of the word). During device start-up, Primary Words are read, and if uncorrectable ECC errors are found, the BCFGERR (RCON<27>) flag is set and Alternate Words are used. If uncorrectable ECC errors are found in Primary and Alternate Words, the BCFGFAIL (RCON<26>) flag is set, and the default configuration is used. The Primary Configuration bits' area is located at the address range, from 0x1FC01780 to 0x1FC017E8. The Alternate Configuration bits' area is located at the address range, from 0x1FC01700 to 0x1FC01768.

## 4.2 Bus Matrix (BMX)

The BMX is a switch fabric that connects the system bus initiators (Flash controller, CPU instruction, CPU data, system DMA and USB) to bus targets (RAM, Flash and peripherals without integrated DMA). All data and instructions are transferred through this bus. Only one initiator can connect to a given target at a time. Multiple initiators can be active at one time provided each one has a separate target. Multiple priority modes (Round Robin, Fixed CPU Highest and Fixed CPU Lowest) are available to allow the priority to be tailored to the application needs. Mode 0 is a Fixed Priority mode with the CPU having the highest priority (refer to Table 4-1). For most applications, this mode should be sufficient; however, it is possible for the CPU to generate sufficient bus traffic to 'starve' the other initiators attempting to access Flash memory, preventing them from performing transfers in the required time limit. If this 'starvation' occurs, the Round Robin or CPU Lowest mode should be chosen.

Mode 1 is a Fixed Priority mode with the CPU having the lowest priority (refer to Table 4-1). This mode can reduce the latency of DMA transfers because the DMA engines have a higher priority than the CPU.

Mode 2 is a Round Robin or Rotating Priority mode. The initiator's priority for each target rotates with every access. This ensures, not that the initiator is starved, but the latency for accesses changes with every access; this makes the latency variable.

The Arbitration mode is selected by the BMXARB<1:0> bits (CFGCON<25:24>).

**Note:** The CPU has two initiators: one for data and the other for instructions. In all Arbitration modes, the CPU data initiator has higher priority than the CPU instruction initiator.

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                           | Branches to                                                              | Status<br>Bits Set | Debug Bits<br>Set                                                          | EXCCODE        | XC32 Function Name         |

|---------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------|----------------|----------------------------|

| СрU                                         | Execution of a coprocessor instruction for a coprocessor that is not enabled.                         | EBASE + 0x180                                                            | CU, EXL            | —                                                                          | CpU (0x0B)     | _general_exception_handler |

| RI                                          | Execution of a reserved instruction.                                                                  | EBASE + 0x180                                                            | EXL                | —                                                                          | RI (0x0A)      | _general_exception_handler |

| Ov                                          | Execution of an arithmetic instruction that overflowed.                                               | EBASE + 0x180                                                            | EXL                | _                                                                          | Ov (0x0C)      | _general_exception_handler |

| Tr                                          | Execution of a trap (when trap condition is true).                                                    | EBASE + 0x180                                                            | EXL                | —                                                                          | Tr (0x0D)      | _general_exception_handler |

| DDBL                                        | EJTAG data address break (address only) or<br>EJTAG data value break on load (address and<br>value).  | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| DDBS                                        | EJTAG data address break (address only) or<br>EJTAG data value break on store (address and<br>value). | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DDBL for a<br>load<br>instruction<br>or DDBS for<br>a store<br>instruction | _              | _                          |

| AdES                                        | Store address alignment error.                                                                        | EBASE + 0x180                                                            | EXL                | _                                                                          | ADES<br>(0x05) | _general_exception_handler |

| DBE                                         | Load or store bus error.                                                                              | EBASE + 0x180                                                            | EXL                | —                                                                          | DBE (0x07)     | _general_exception_handler |

| CBrk                                        | EJTAG complex breakpoint.                                                                             | 0xBFC0_0480<br>(ProbEn = 0 in ECR)<br>0xBFC0_0200<br>(ProbEn = 1 in ECR) | _                  | DIBImpr,<br>DDBLImpr<br>and/or<br>DDBSImpr                                 | _              | _                          |

|                                             |                                                                                                       | Lowest Priority                                                          | <u> </u>           | <u> </u>                                                                   | <u> </u>       |                            |

# TABLE 7-1: MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC MICROPROCESSOR CORE EXCEPTION TYPES (CONTINUED)

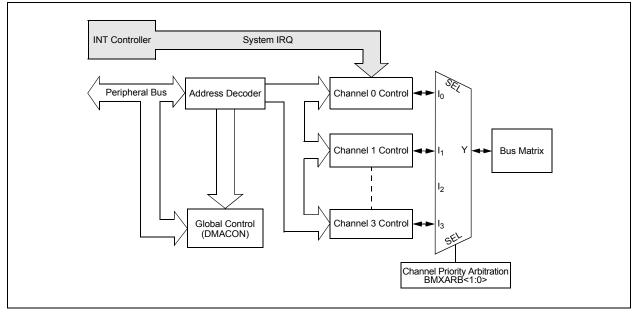

# 8.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note 1: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "DMA Controller" (DS60001117) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Direct Memory Access (DMA) Controller is a bus master module useful for data transfers between peripherals and memory without CPU intervention. The source and destination of a DMA transfer can be any of the memory-mapped modules, that do not have a dedicated DMA, existent in the PIC32 (such as SPI, UART, PMP, etc.) or the memory itself.

The following are some of the key features of the DMA Controller module:

- Four Identical Channels, Each Featuring:

- Auto-Increment Source and Destination Address registers

- Source and Destination Pointers

- Memory to memory and memory to peripheral transfers

- Automatic Word Size Detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- FIGURE 8-1: DMA BLOCK DIAGRAM

- Fixed Priority Channel Arbitration

- · Flexible DMA Channel Operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA Requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA Channel Status Interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA Debug Support Features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

- User Selectable Bus Arbitration Priority (refer to Section 4.2 "Bus Matrix (BMX)")

- 8 System Clocks Per Cell Transfer

# 9.3 FRC Active Clock Tuning

PIC32MM0256GPM064 family devices include an automatic mechanism to calibrate the FRC during run time. This system uses active clock tuning from a source of known accuracy to maintain the FRC within a very narrow margin of its nominal 8 MHz frequency. This allows for a frequency accuracy that is well within the requirements of the *"USB 2.0 Specification"* regarding full-speed USB devices.

| Note: | The self-tune feature maintains sufficient |  |  |  |  |  |  |  |  |

|-------|--------------------------------------------|--|--|--|--|--|--|--|--|

|       | accuracy for operation in USB Device       |  |  |  |  |  |  |  |  |

|       | mode. For applications that function as a  |  |  |  |  |  |  |  |  |

|       | USB host, a high-accuracy clock source     |  |  |  |  |  |  |  |  |

|       | (±0.05%) is still required.                |  |  |  |  |  |  |  |  |

The self-tune system is controlled by the bits in the upper half of the OSCTUN register. Setting the ON bit (OSCTUN<15>) enables the self-tuning feature, allowing the hardware to calibrate to a source selected by the SRC bit (OSCTUN<12>). When SRC = 1, the system uses the Start-of-Frame (SOF) packets from an external USB host for its source. When SRC = 0, the system uses the crystal-controlled SOSC for its calibration source. Regardless of the source, the system uses the TUN<5:0> bits (OSCTUN<5:0>) to change the FRC Oscillator's frequency. Frequency monitoring and adjustment is dynamic, occurring continuously during run time. While the system is active, the TUNx bits cannot be written to by software.

| Note: | To use the USB as a reference clock tuning<br>source (SRC = 1), the microcontroller must<br>be configured for USB device operation<br>and connected to a non-suspended USB<br>host or hub port. |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | If the SOSC is to be used as the reference clock tuning source (SRC = $0$ ), the SOSC                                                                                                           |

clock tuning source (SRC = 0), the SOSC must also be enabled for clock tuning to occur.

The self-tune system can generate a hardware interrupt, FSTIF. The interrupt can result from a drift of the FRC from the reference, by greater than 0.2% in either direction, or whenever the frequency deviation is beyond the ability of the TUNx bits to correct (i.e., greater than 1.5%). The LOCK and ORNG status bits (OSCTUN<11,9>) are used to indicate these conditions.

The POL and ORPOL bits (OSCTUN<10,8>) configure the FSTIF interrupt to occur in the presence or the absence of the conditions. It is the user's responsibility to monitor both the LOCK and ORNG bits to determine the exact cause of the interrupt.

Note: The POL and ORPOL bits should be ignored when the self-tune system is disabled (ON = 0).

**Note:** After exiting out of self-tune, 6 writes may be required to update the TUN<5:0> bits.

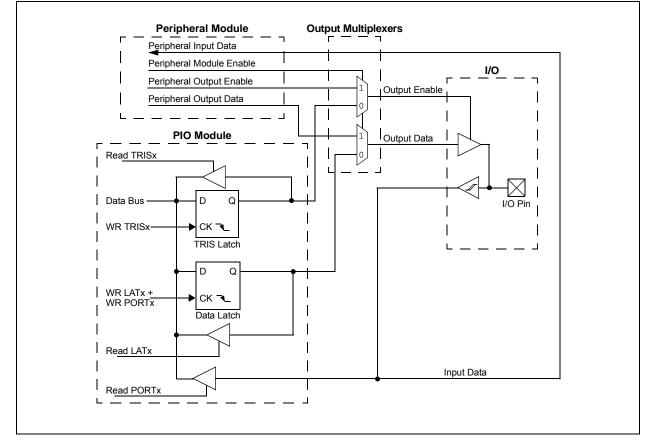

# 10.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. Many of the device pins are shared among the peripherals and the Parallel I/O (PIO) ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity. Some pins in the devices are 5V tolerant pins. Some of the key features of the I/O ports are:

- Individual Output Pin Open-Drain Enable/Disable

- Individual Input Pin Weak Pull-up and Pull-Down

- Monitor Selective Inputs and Generate Interrupt when Change in Pin State is Detected

- Operation during Sleep and Idle modes

- Fast Bit Manipulation using the CLR, SET and INV Registers

Figure 10-1 illustrates a block diagram of a typical multiplexed I/O port.

## FIGURE 10-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

# 11.1 Timer1 Control Register

## TABLE 11-1: TIMER1 REGISTER MAP

| ress<br>)                   | <b>b</b> a                      | е        |                             |       |       |       |       |       |      | Bi        | ts     |      |      |        |      |       |      |      | ts        |

|-----------------------------|---------------------------------|----------|-----------------------------|-------|-------|-------|-------|-------|------|-----------|--------|------|------|--------|------|-------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Rang | 31/15                       | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7   | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Reset |

| 0000                        | TIOON                           | 31:16    | _                           | _     | —     | —     | —     | _     | —    | —         | —      | —    | —    | —      | _    | —     | —    | —    | 0000      |

| 8000                        | T1CON                           | 15:0     | ON                          | —     | SIDL  | TWDIS | TWIP  | —     | TECS | TECS<1:0> |        | _    | TCKP | S<1:0> | _    | TSYNC | TCS  | —    | 0000      |

| 0010                        | TMR1                            | 31:16    |                             | _     | _     | _     | _     | _     | _    | _         | _      | _    | _    | _      | _    | _     | _    | _    | 0000      |

| 8010                        | TIVIRT                          | 15:0     |                             |       |       |       |       |       |      | TMR1<     | <15:0> |      |      |        |      |       |      |      | 0000      |

| 8020                        | PR1                             | 31:16    | _                           | _     | —     | _     | —     | _     |      | —         | _      | —    | _    | _      |      | _     |      | —    | 0000      |

| 0020                        |                                 | 15:0     | PR1<15:0> <sup>(2)</sup> FF |       |       |       |       |       |      |           |        |      |      | FFFF   |      |       |      |      |           |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

**2:** PR1 values of '0' and '1' are reserved.

# 14.0 CAPTURE/COMPARE/PWM/ TIMER MODULES (MCCP AND SCCP)

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 30. "Capture/Compare/PWM/ Timer (MCCP and SCCP)" (DS60001381) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

## 14.1 Introduction

PIC32MM0256GPM064 family devices include nine Capture/Compare/PWM/Timer (CCP) modules. These modules are similar to the multipurpose timer modules found on many other 32-bit microcontrollers. They also provide the functionality of the comparable input capture, output compare and general purpose timer peripherals found in all earlier PIC32 devices.

CCP modules can operate in one of three major modes:

- General Purpose Timer

- · Input Capture

- Output Compare/PWM

There are two different forms of the module, distinguished by the number of PWM outputs that the module can generate. Single Capture/Compare/PWM/Timer (SCCPs) output modules provide only one PWM output. Multiple Capture/Compare/PWM/Timer (MCCPs) output modules can provide up to six outputs and an extended range of output control features, depending on the pin count of the particular device.

All modules (SCCP and MCCP) include these features:

- User-Selectable Clock Inputs, including System Clock and External Clock Input Pins

- Input Clock Prescaler for Time Base

- Output Postscaler for module Interrupt Events or Triggers

- Synchronization Output Signal for coordinating other MCCP/SCCP modules with User-Configurable Alternate and Auxiliary Source Options

- Fully Asynchronous Operation in all modes and in Low-Power Operation

- Special Output Trigger for ADC Conversions

- 16-Bit and 32-Bit General Purpose Timer modes with Optional Gated Operation for Simple Time Measurements

- · Capture modes:

- Backward compatible with previous input capture peripherals of the PIC32 family

- 16-bit or 32-bit capture of time base on external event

- Up to four-level deep FIFO capture buffer

- Capture source input multiplexer

- Gated capture operation to reduce noise-induced false captures

- · Output Compare/PWM modes:

- Backward compatible with previous output compare peripherals of the PIC32 family

- Single Edge and Dual Edge Compare modes

- Center-Aligned Compare mode

- Variable Frequency Pulse mode

- External Input mode

MCCP modules also include these extended PWM features:

- Single Output Steerable mode

- Brush DC Motor (Forward and Reverse) modes

- · Half-Bridge with Dead-Time Delay mode

- Push-Pull PWM mode

- Output Scan mode

- Auto-Shutdown with Programmable Source and Shutdown State

- Programmable Output Polarity

The SCCP and MCCP modules can be operated in only one of the three major modes (Capture, Compare or Timer) at any time. The other modes are not available unless the module is reconfigured.

A conceptual block diagram for the module is shown in Figure 14-1. All three modes use the time base generator and the common Timer register pair (CCPxTMR). Other shared hardware components, such as comparators and buffer registers, are activated and used as a particular mode requires.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3    | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|----------------------|----------------------|----------------------|----------------------|----------------------|------------------|--|

| 04.04        | R/W-0 U-0         |                   | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-1            |  |

| 31:24        | OENSYNC           |                   | OCFEN <sup>(1)</sup> | OCEEN <sup>(1)</sup> | OCDEN <sup>(1)</sup> | OCCEN <sup>(1)</sup> | OCBEN <sup>(1)</sup> | OCAEN            |  |

| 00.40        | R/W-0             | R/W-0             | U-0                  | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |

| 23:16        | ICGSM             | 1<1:0>            | —                    | AUXOL                | JT<1:0>              | ICS<2:0>             |                      |                  |  |

| 45.0         | R/W-0             | R/W-0             | U-0                  | R/W-0                | U-0                  | U-0                  | U-0                  | U-0              |  |

| 15:8         | PWMRSEN           | ASDGM             | —                    | SSDG                 | —                    | —                    | -                    | -                |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0                | R/W-0            |  |

| 7:0          |                   |                   |                      | ASDG<                | <7:0>                |                      |                      |                  |  |

## REGISTER 14-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31 **OENSYNC:** Output Enable Synchronization bit

- 1 = Update by output enable bits occurs on the next Time Base Reset or rollover

- 0 = Update by output enable bits occurs immediately

- bit 30 Unimplemented: Read as '0'

#### bit 29-24 OC<F:A>EN: Output Enable/Steering Control bits<sup>(1)</sup>

- 1 = OCx pin is controlled by the CCPx module and produces an output compare or PWM signal

- 0 = OCx pin is not controlled by the CCPx module; the pin is available to the port logic or another peripheral multiplexed on the pin

#### bit 23-22 ICGSM<1:0>: Input Capture Gating Source Mode Control bits

- 11 = Reserved

- 10 = One-Shot mode: Falling edge from gating source disables future capture events (ICDIS = 1)

- 01 = One-Shot mode: Rising edge from gating source enables future capture events (ICDIS = 0)

- 00 = Level-Sensitive mode: A high level from gating source will enable future capture events; a low level will disable future capture events

- bit 21 Unimplemented: Read as '0'

#### bit 20-19 AUXOUT<1:0>: Auxiliary Output Signal on Event Selection bits

- 11 = Input capture or output compare event; no signal in Timer mode

- 10 = Signal output depends on module operating mode

- 01 = Time base rollover event (all modes)

- 00 = Disabled

- bit 18-16 ICS<2:0>: Input Capture Source Select bits

- 111 = CLC4 output

- 110 = CLC3 output

- 101 = CLC2 output

- 100 = CLC1 output

- 011 = Comparator 3 output

- 010 = Comparator 2 output

- 001 = Comparator 1 output

- 000 = ICMx pin<sup>(2)</sup>

- bit 15 PWMRSEN: CCPx PWM Restart Enable bit

- 1 = ASEVT bit clears automatically at the beginning of the next PWM period, after the shutdown input has ended

- 0 = ASEVT must be cleared in software to resume PWM activity on output pins

- Note 1: OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

- **2:** This pin is remappable from SCCP modules.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | -                | _                |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | r-0              | r-0              |

| 23:16        | —                 | PCIE              | SCIE              | BOEN              | SDAHT             | SBCDE             | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

### REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER

| Legend:           | r = Reserved bit | HC = Hardware Clear  | HC = Hardware Clearable bit |  |  |  |  |  |

|-------------------|------------------|----------------------|-----------------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'             |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown          |  |  |  |  |  |

#### bit 31-23 Unimplemented: Read as '0'

| bit 22 | PCIE: Stop Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul> <li>1 = Enables interrupt on detection of Stop condition</li> <li>0 = Stop detection interrupts are disabled</li> </ul>                                                                                                                                                                  |

| bit 21 | SCIE: Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                 |

|        | <ul> <li>1 = Enables interrupt on detection of Start or Restart conditions</li> <li>0 = Start detection interrupts are disabled</li> </ul>                                                                                                                                                    |

| bit 20 | <b>BOEN:</b> Buffer Overwrite Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                   |

|        | <ul> <li>1 = I2CxRCV is updated and an ACK is generated for a received address/data byte, ignoring the state of the I2COV bit (I2CxSTAT&lt;6&gt;) only if the RBF bit (I2CxSTAT&lt;1&gt;) = 0</li> <li>0 = I2CxRCV is only updated when the I2COV bit (I2CxSTAT&lt;6&gt;) is clear</li> </ul> |

| bit 19 | SDAHT: SDAx Hold Time Selection bit                                                                                                                                                                                                                                                           |

|        | 1 = Minimum of 300 ns hold time on SDAx after the falling edge of SCLx                                                                                                                                                                                                                        |

- 0 = Minimum of 100 ns hold time on SDAx after the falling edge of SCLx

- bit 18 **SBCDE:** Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

- 1 = Enables slave bus collision interrupts

- 0 = Slave bus collision interrupts are disabled

- bit 17-16 **Reserved:** Maintain as '0'

- bit 15 ON: I2Cx Enable bit

- 1 = Enables the I2Cx module and configures the SDAx and SCLx pins as serial port pins

- 0 = Disables the I2Cx module; all I<sup>2</sup>C pins are controlled by port functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** I2Cx Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Releases SCLx clock

- 0 = Holds SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear at the beginning of slave transmission. Hardware is clear at the end of slave reception.

If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware is clear at the beginning of slave transmission.

## TABLE 18-1: USB OTG REGISTER MAP (CONTINUED)

| ess                         |                                 | C)        |       |       |       |       |        |        |      |      | Bits  |          |      |             |        |        |           |          | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|--------|--------|------|------|-------|----------|------|-------------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10  | 25/9 | 24/8 | 23/7  | 22/6     | 21/5 | 20/4        | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 0070                        | U1BDTP1                         | 31:16     | _     | —     | —     | _     | _      | —      | —    | _    | _     | —        | _    | _           |        | —      | _         | _        | 0000       |

| 8670                        | UIBDIPI                         | 15:0      | _     | _     | —     | _     | _      | _      | _    | _    |       |          | В    | DTPTRL<7:1> |        |        |           | _        | 0000       |

| 0000                        | U1FRML <sup>(3)</sup>           | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | —     | —        | _    | _           | _      | _      | _         | -        | 0000       |

| 8680                        | UTFRIML                         | 15:0      | _     | _     | —     | _     | _      | _      | _    | _    |       |          |      | FRML<       | 7:0>   |        |           |          | 0000       |

| 0000                        | U1FRMH <sup>(3)</sup>           | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | —     | —        | _    | _           | _      | _      | _         | _        | 0000       |

| 8690                        | 01FRMH                          |           | _     | _     | —     | _     | _      | _      | _    | _    | _     | —        | _    | _           | _      |        | FRMH<2:0> |          | 0000       |

| 9640                        | U1TOK                           | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | _     | —        | _    | _           | _      | _      | _         | _        | 0000       |

| 86A0                        | UTIOK                           | 15:0      | _     | _     | —     | _     | _      | _      | _    | _    |       | PID<3:0> |      |             |        | EP     | <3:0>     |          | 0000       |

| 0000                        | U1SOF                           | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | _     |          |      |             | _      | _      | _         | -        | 0000       |

| 86B0                        | UISOF                           | 15:0      | _     | _     | _     | _     | _      | _      | _    | _    |       |          |      | CNT<7       | /:0>   |        |           |          | 0000       |

| 0000                        | U1BDTP2                         | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | _     | —        | _    | _           | _      | _      | _         | _        | 0000       |

| 86C0                        |                                 |           |       |       |       |       | BDTPTR | H<7:0> |      |      |       | 0000     |      |             |        |        |           |          |            |

| 86D0                        | U1BDTP3                         | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | _     | —        | _    | _           | _      | _      | _         | _        | 0000       |

| 86D0                        | UIBD1P3                         | 15:0      | _     | _     | —     | _     | _      | _      | _    | _    |       |          |      | BDTPTRI     | J<7:0> |        |           |          | 0000       |

| 86E0                        | U1CNFG1                         | 31:16     | _     | _     | _     | -     | -      | —      | _    | _    | -     | —        | _    | _           | -      | —      | _         | _        | 0000       |

| 80EU                        | UTCNFGT                         | 15:0      | _     | _     | —     | _     | _      | _      | _    | _    | UTEYE | UOEMON   | _    | USBSIDL     | LSDEV  | _      | _         | UASUSPND | 0001       |

| 8700                        | U1EP0                           | 31:16     | _     | _     | —     | _     |        | _      | _    | _    |       | —        | _    | _           |        | _      | _         | _        | 0000       |

| 8700                        | UIEPU                           | 15:0      | _     | _     | _     | -     | -      | —      | _    | _    | LSPD  | RETRYDIS | _    | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9710                        | U1EP1                           | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | _     | —        | _    | _           | _      | _      | _         | _        | 0000       |

| 8710                        | UIEPI                           | 15:0      | _     | _     | —     | _     |        | _      | _    | _    |       | —        | _    | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 0700                        | U1EP2                           | 31:16     | _     | _     | —     | _     | _      | _      | _    | _    | _     | —        | _    | _           | _      | _      | _         | -        | 0000       |

| 8720                        | UTEP2                           | 15:0      | _     | _     | —     | _     | _      | _      | _    | _    | _     | —        | _    | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9720                        | U1EP3                           | 31:16     | _     | _     | —     | _     |        | _      | _    | _    |       | —        | _    | _           |        | _      | _         | _        | 0000       |

| 8730                        | UTEP3                           | 15:0      | _     | _     | _     | _     | _      | _      | _    | _    | _     | —        | _    | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9740                        |                                 | 31:16     | _     | —     | —     | —     | _      | —      | —    | —    | _     | —        | _    | _           | _      | —      | _         | _        | 0000       |

| 8740                        | U1EP4                           | 15:0      | _     | _     | _     | —     | _      | —      | _    | _    | _     | —        | _    | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 9750                        |                                 | 31:16     | _     | —     | —     | _     | _      | —      | _    | _    | _     | —        | _    | _           | _      | —      | _         | _        | 0000       |

| 8750                        | U1EP5                           | 15:0      |       | _     |       | —     | _      | —      |      |      | _     | —        | _    | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 0700                        |                                 | 31:16     | —     | —     | —     | _     | _      | —      | —    | _    | _     | —        | _    | —           | —      | —      | _         | _        | 0000       |

| 8760                        | U1EP6                           | 15:0      | _     | _     | _     | _     |        | _      | _    | _    | _     | _        | _    | EPCONDIS    | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 10.1 "CLR, SET and INV Registers" for more information.

**2**: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for these bits is undefined.

# PIC32MM0256GPM064 FAMILY

### REGISTER 18-2: U1OTGIE: USB OTG INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 | _                 |                   | -                 | —                 |                  | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | -                 |                   | _                 | _                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

#### Legend:

bit 5

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIE: ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

- LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = Activity interrupt is enabled

- 0 = Activity interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt is enabled

- 0 = B-session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt is enabled

- 0 = A-VBUS valid interrupt is disabled

## REGISTER 18-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Resets all Even/Odd Buffer Pointers to the Even buffer descriptor banks

- 0 = Even/Odd Buffer Pointers are not reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry are enabled

- 0 = USB module and supporting circuitry are disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 18-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the Resume signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

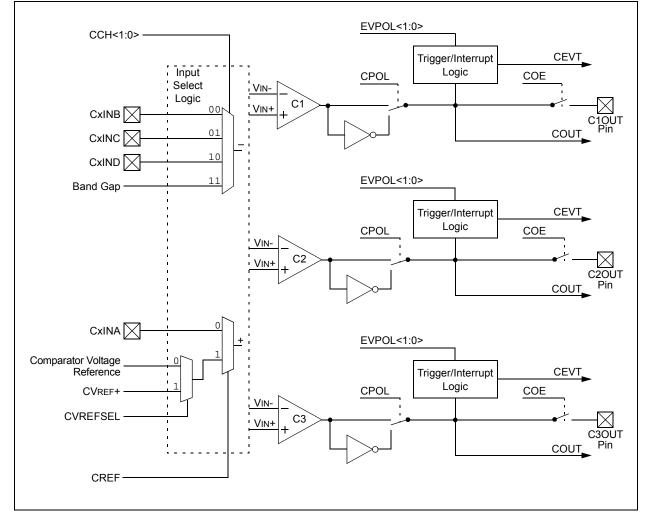

# 22.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Comparator" (DS60001110) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM. The comparator module provides three dual input comparators. The inputs to the comparator can be configured to use any one of five external analog inputs (CxINA, CxINB, CxINC, CxIND and CVREF+). The comparator outputs may be directly connected to the CxOUT pins. When the respective COE bit equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module in shown in Figure 22-1. Each comparator has its own control register, CMxCON (Register 22-2), for enabling and configuring its operation. The output and event status of two comparators is provided in the CMSTAT register (Register 22-1).

# PIC32MM0256GPM064 FAMILY

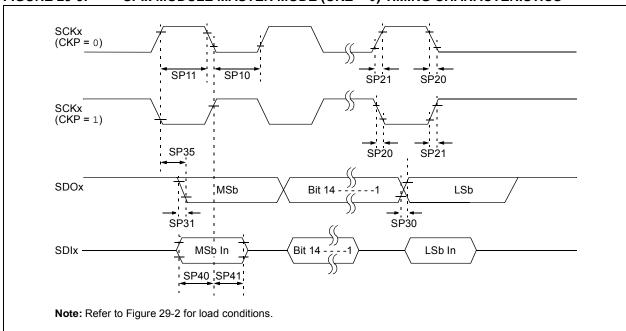

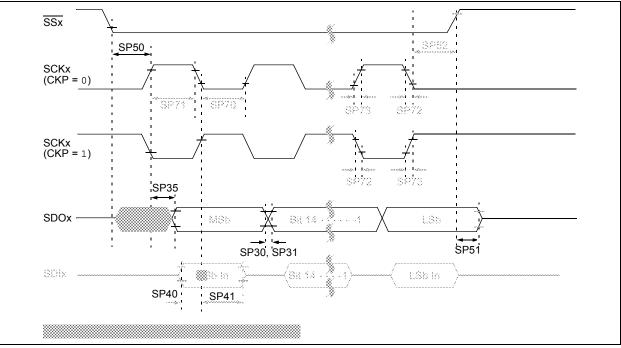

#### FIGURE 29-9: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

## TABLE 29-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | Standard Operating Conditions: 2.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |                        |      |       |                    |  |

|--------------------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|

| Param<br>No.       | Symbol                | Characteristics <sup>(1)</sup>                | Min.                                                                                                                             | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP10               | TscL                  | SCKx Output Low Time <sup>(3)</sup>           | Tsck/2                                                                                                                           | _                      | _    | ns    |                    |  |

| SP11               | TscH                  | SCKx Output High Time <sup>(3)</sup>          | Tsck/2                                                                                                                           | —                      | _    | ns    |                    |  |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(4)</sup>          | —                                                                                                                                | —                      | _    | ns    | See Parameter DO32 |  |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(4)</sup>          | _                                                                                                                                | _                      | _    | ns    | See Parameter DO31 |  |

| SP30               | TDOF                  | SDOx Data Output<br>Fall Time <sup>(4)</sup>  |                                                                                                                                  | —                      |      | ns    | See Parameter DO32 |  |

| SP31               | TDOR                  | SDOx Data Output<br>Rise Time <sup>(4)</sup>  | _                                                                                                                                | —                      |      | ns    | See Parameter DO31 |  |

| SP35               | TscH2doV,             | SDOx Data Output Valid                        | _                                                                                                                                | _                      | 7    | ns    | VDD > 2.0V         |  |

|                    | TscL2DoV              | after SCKx Edge                               | _                                                                                                                                | _                      | 10   | ns    | VDD < 2.0V         |  |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 5                                                                                                                                | —                      | _    | ns    |                    |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data<br>Input to SCKx Edge  | 5                                                                                                                                | —                      | _    | ns    |                    |  |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 10 pF load on all SPIx pins.

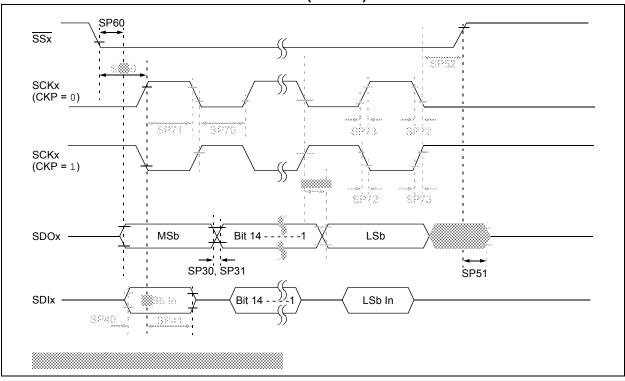

### FIGURE 29-11: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

## TABLE 29-30: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                                              | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |                     |      |       |                    |  |

|--------------------|-----------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param<br>No.       | Symbol                | Characteristics <sup>(1)</sup>                               | Min.                                                                                                                             | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70               | TscL                  | SCKx Input Low Time <sup>(3)</sup>                           | Tsck/2                                                                                                                           | _                   | —    | ns    |                    |  |

| SP71               | TscH                  | SCKx Input High Time <sup>(3)</sup>                          | Tsck/2                                                                                                                           | _                   | _    | ns    |                    |  |

| SP72               | TscF                  | SCKx Input Fall Time                                         | —                                                                                                                                | _                   | —    | ns    | See Parameter DO32 |  |

| SP73               | TscR                  | SCKx Input Rise Time                                         | _                                                                                                                                | _                   | _    | ns    | See Parameter DO31 |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>                    | —                                                                                                                                | _                   | —    | ns    | See Parameter DO32 |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>                    | —                                                                                                                                | _                   | —    | ns    | See Parameter DO31 |  |

| SP35               |                       | SDOx Data Output Valid after<br>SCKx Edge                    | —                                                                                                                                | —                   | 7    | ns    | VDD > 2.0V         |  |

|                    | TscL2DoV              |                                                              | —                                                                                                                                | —                   | 10   | ns    | VDD < 2.0V         |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge                   | 5                                                                                                                                | —                   | _    | ns    |                    |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 5                                                                                                                                | —                   | —    | ns    |                    |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 88                                                                                                                               | —                   | —    | ns    |                    |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>        | 2.5                                                                                                                              | —                   | 12   | ns    |                    |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 10                                                                                                                               | —                   | _    | ns    |                    |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

4: Assumes 10 pF load on all SPIx pins.

FIGURE 29-12: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

| AC CHARACTERISTICS  |                       |                                                       | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |      |       |            |                    |  |

|---------------------|-----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--------------------|--|

| Param<br>No. Symbol |                       | Characteristics <sup>(1)</sup>                        | Min. Typical <sup>(2)</sup>                                                                                                      | Max. | Units | Conditions |                    |  |

| SP70                | TscL                  | SCKx Input Low Time <sup>(3)</sup>                    | Tsck/2                                                                                                                           | _    | _     | ns         |                    |  |

| SP71                | TscH                  | SCKx Input High Time <sup>(3)</sup>                   | Tsck/2                                                                                                                           | _    |       | ns         |                    |  |

| SP72                | TscF                  | SCKx Input Fall Time                                  | _                                                                                                                                | _    | 10    | ns         |                    |  |

| SP73                | TscR                  | SCKx Input Rise Time                                  | _                                                                                                                                | _    | 10    | ns         |                    |  |

| SP30                | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>             | _                                                                                                                                | —    | —     | ns         | See Parameter DO32 |  |

| SP31                | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>             | _                                                                                                                                | _    | _     | ns         | See Parameter DO31 |  |

| SP35                | TscH2doV,             | , SDOx Data Output Valid after                        | _                                                                                                                                | —    | 10    | ns         | VDD > 2.0V         |  |

|                     | TscL2DoV              | SCKx Edge                                             | _                                                                                                                                | —    | 15    | ns         | VDD < 2.0V         |  |

| SP40                | TDIV2sCH,<br>TDIV2sCL | Setup Time of SDIx Data Input to SCKx Edge            | 0                                                                                                                                | —    | _     | ns         |                    |  |

| SP41                | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge             | 7                                                                                                                                | —    |       | ns         |                    |  |

| SP50                | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↓ or<br>SCKx ↑ Input                    | 88                                                                                                                               | _    | _     | ns         |                    |  |

| SP51                | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 2.5                                                                                                                              | _    | 12    | ns         |                    |  |

| SP52                | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                 | 10                                                                                                                               | _    | _     | ns         |                    |  |

| SP60                | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge              | _                                                                                                                                | —    | 12.5  | ns         |                    |  |

## TABLE 29-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

**4:** Assumes 10 pF load on all SPIx pins.

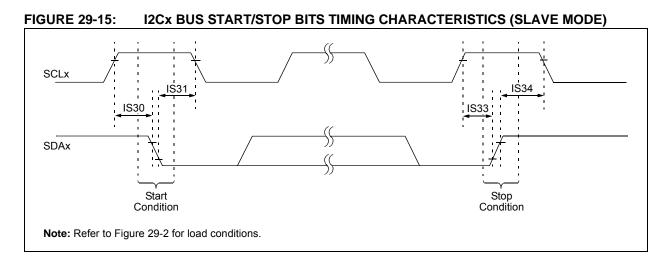

| AC CHARACTERISTICS |         |                               | Standard Operating C<br>Operating temperatur |                     | <b>3.6V (unless otherwise stated)</b><br>$\leq TA \leq +85^{\circ}C$ |       |                                    |

|--------------------|---------|-------------------------------|----------------------------------------------|---------------------|----------------------------------------------------------------------|-------|------------------------------------|

| Param<br>No.       | Sym     | Charact                       | eristics                                     | Min. <sup>(1)</sup> | Max.                                                                 | Units | Conditions                         |

| IM25               | TSU:DAT | Data Input                    | 100 kHz mode                                 | 250                 | _                                                                    | ns    |                                    |

|                    |         | Setup Time                    | 400 kHz mode                                 | 100                 |                                                                      | ns    | 1                                  |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | 100                 |                                                                      | ns    |                                    |

| IM26               | THD:DAT | Data Input                    | 100 kHz mode                                 | 0                   | _                                                                    | μS    |                                    |

|                    |         | Hold Time                     | 400 kHz mode                                 | 0                   | 0.9                                                                  | μs    |                                    |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | 0                   | 0.3                                                                  | μS    |                                    |

| IM30               | TSU:STA | Start Condition               | 100 kHz mode                                 | TPBCLK * (BRG + 2)  | _                                                                    | μS    | Only relevant for Repeated         |

|                    |         | Setup Time                    | 400 kHz mode                                 | TPBCLK * (BRG + 2)  | _                                                                    | μS    | Start condition                    |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | TPBCLK * (BRG + 2)  |                                                                      | μS    |                                    |

| IM31               | THD:STA | Start Condition               | 100 kHz mode                                 | TPBCLK * (BRG + 2)  |                                                                      | μS    | After this period, the first clock |

|                    |         | Hold Time                     | 400 kHz mode                                 | TPBCLK * (BRG + 2)  |                                                                      | μS    | pulse is generated                 |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | TPBCLK * (BRG + 2)  | _                                                                    | μs    |                                    |

| IM33               | Tsu:sto | Stop Condition<br>Setup Time  | 100 kHz mode                                 | TPBCLK * (BRG + 2)  |                                                                      | μS    |                                    |

|                    |         |                               | 400 kHz mode                                 | TPBCLK * (BRG + 2)  | _                                                                    | μS    |                                    |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | TPBCLK * (BRG + 2)  |                                                                      | μS    |                                    |

| IM34               | THD:STO | Stop Condition<br>Hold Time   | 100 kHz mode                                 | TPBCLK * (BRG + 2)  |                                                                      | ns    |                                    |

|                    |         |                               | 400 kHz mode                                 | TPBCLK * (BRG + 2)  | _                                                                    | ns    |                                    |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | TPBCLK * (BRG + 2)  |                                                                      | ns    |                                    |

| IM40               | TAA:SCL | CL Output Valid<br>from Clock | 100 kHz mode                                 | —                   | 3500                                                                 | ns    |                                    |

|                    |         |                               | 400 kHz mode                                 | —                   | 1000                                                                 | ns    |                                    |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | —                   | 350                                                                  | ns    |                                    |

| IM45 T             | TBF:SDA | Bus Free Time                 | 100 kHz mode                                 | 4.7                 |                                                                      | μs    | The amount of time the bus         |

|                    |         |                               | 400 kHz mode                                 | 1.3                 |                                                                      | μs    | must be free before a new          |

|                    |         |                               | 1 MHz mode <sup>(2)</sup>                    | 0.5                 | —                                                                    | μs    | transmission can start             |

| IM50               | Св      | Bus Capacitive                | Loading                                      | —                   | _                                                                    | pF    | See Parameter DO58                 |

| IM51               | Tpgd    | Pulse Gobbler                 | Delay                                        | 52                  | 312                                                                  | ns    | (Note 3)                           |

## TABLE 29-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum Pin Capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

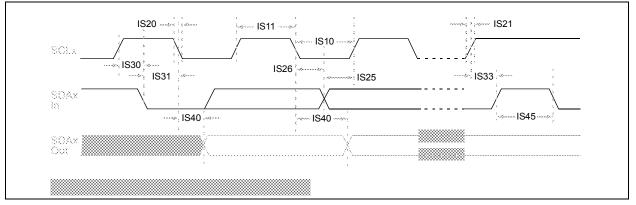

| AC CHARACTERISTICS |         |                           |                           | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |      |       |                                            |  |

|--------------------|---------|---------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|

| Param<br>No.       | Sym     | Charac                    | teristics                 | Min.                                                                                                                             | Max. | Units | Conditions                                 |  |

| IS10               | TLO:SCL | Clock Low<br>Time         | 100 kHz mode              | 4.7                                                                                                                              | _    | μS    | PBCLK must operate at a minimum of 800 kHz |  |

|                    |         |                           | 400 kHz mode              | 1.3                                                                                                                              | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |

|                    |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                              | _    | μs    |                                            |  |

| IS11               | THI:SCL | Clock High<br>Time        | 100 kHz mode              | 4.0                                                                                                                              | —    | μS    | PBCLK must operate at a minimum of 800 kHz |  |

|                    |         |                           | 400 kHz mode              | 0.6                                                                                                                              | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |

|                    |         |                           | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                              | _    | μs    |                                            |  |

| IS20 TF:SCL        | TF:SCL  | CL SDAx and 100 kl        | 100 kHz mode              | —                                                                                                                                | 300  | ns    | CB is specified to be from                 |  |

|                    |         | SCLx Fall                 | 400 kHz mode              | 20 + 0.1 Св                                                                                                                      | 300  | ns    | 10 to 400 pF                               |  |

|                    | Time    | 1 MHz mode <sup>(1)</sup> | —                         | 100                                                                                                                              | ns   |       |                                            |  |

**Note 1:** Maximum Pin Capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support