Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 38                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

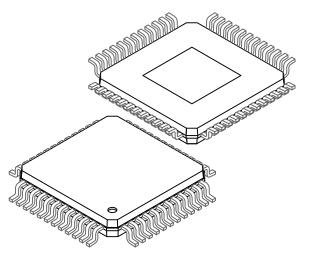

| Package / Case             | 48-TQFP Exposed Pad                                                              |

| Supplier Device Package    | 48-TQFP-EP (7x7)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0128gpm048-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

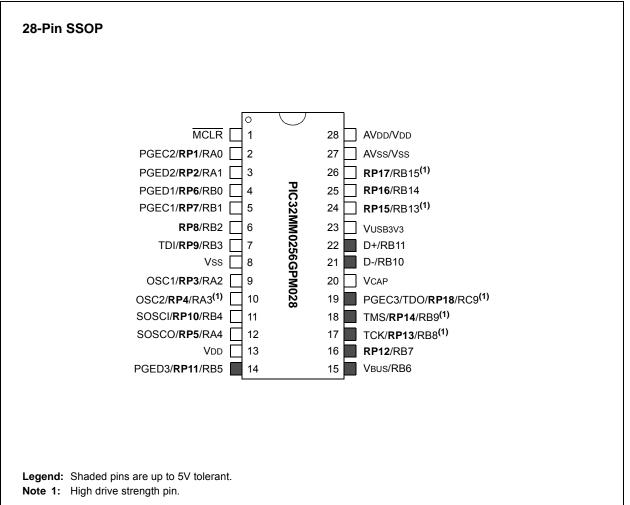

## **Pin Diagrams**

#### TABLE 2: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 28-PIN SSOP DEVICES

| Pin | Function                                                                              | Pin | Function                                                                                             |

|-----|---------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------|

| 1   | MCLR                                                                                  | 15  | VBUS/RB6                                                                                             |

| 2   | PGEC2/VREF+/CVREF+/AN0/RP1/OCM1E/INT3/RA0                                             | 16  | RP12/SDA3/SDI3/OCM3F/RB7                                                                             |

| 3   | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                                                | 17  | TCK/ <b>RP13</b> /SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>                                           |

| 4   | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                                             | 18  | TMS/REFCLKI/ <b>RP14</b> /SDA1/T1CK/T1G/T2CK/T2G/U1RTS/U1BCLK/SDO1/OCM1B/<br>INT2/RB9 <sup>(1)</sup> |

| 5   | PGEC1/AN3/C1INC/C2INA/RP7/OCM2D/RB1                                                   | 19  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /T3CK/T3G/USBOEN/SDO3/OCM2A/RC9 <sup>(1)</sup>                   |

| 6   | AN4/C1INB/RP8/SDA2/OCM2E/RB2                                                          | 20  | VCAP                                                                                                 |

| 7   | TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3                                                     | 21  | D-/RB10                                                                                              |

| 8   | Vss                                                                                   | 22  | D+/RB11                                                                                              |

| 9   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                                                           | 23  | VUSB3V3                                                                                              |

| 10  | OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3 <sup>(1)</sup>                                      | 24  | AN8/LVDIN/ <b>RP15</b> /SCL3/SCK3/OCM3A/RB13 <sup>(1)</sup>                                          |

| 11  | SOSCI/AN7/RP10/OCM3C/RB4                                                              | 25  | CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14                                           |

| 12  | SOSCO/SCLKI/ <b>RP5</b> /PWRLCLK/OCM3D/RA4                                            | 26  | AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15 <sup>(1)</sup>                               |

| 13  | Vdd                                                                                   | 27  | AVss/Vss                                                                                             |

| 14  | PGED3/ <b>RP11</b> /ASDA1 <sup>(2)</sup> /USBID/ <del>SS3</del> /FSYNC3/<br>OCM3E/RB5 | 28  | AVdd/Vdd                                                                                             |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MICROCONTROLLERS

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

## 2.1 Basic Connection Requirements

Getting started with the PIC32MM0256GPM064 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins, even if the ADC module is not used (see Section 2.2 "Decoupling Capacitors")

- MCLR pin (see Section 2.3 "Master Clear (MCLR) Pin")

- VCAP pin (see Section 2.4 "Voltage Regulator Pin (VCAP)")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5** "**ICSP Pins**")

- OSC1 and OSC2 pins, when external oscillator source is used (see Section 2.7 "External Oscillator Pins")

- VUSB3V3 pin, this pin must be powered for USB operation (see Section 18.4 "Powering the USB Transceiver")

The following pin(s) may be required as well:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS, is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of  $0.1 \ \mu F$ (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high-frequency noise: If the board is experiencing high-frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances, as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | R/W-1             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | PWPULOCK          | _                 |                   | _                 | _                 |                   | _                | _                |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | PWP<23:16>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | PWP<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | PWP               | <7:0>             |                   |                  |                  |  |  |

#### REGISTER 5-6: NVMPWP: PROGRAM FLASH WRITE-PROTECT REGISTER

## Legend:

| Legena:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 **PWPULOCK:** Program Flash Memory Page Write-Protect Unlock bit

1 = Register is not locked and can be modified

0 = Register is locked and cannot be modified

This bit is only clearable and cannot be set except by any Reset.

bit 30-24 Unimplemented: Read as '0'

bit 23-0 PWP<23:0>: Flash Program Write-Protect (Page) Address bits

Physical memory below address, 0x1DXXXXXX, is write-protected, where 'XXXXXX' is specified by PWP<23:0>. When the PWP<23:0> bits have a value of '0', write protection is disabled for the entire Program Flash Memory. If the specified address falls within the page, the entire page and all pages below the current page will be protected.

**Note:** The bits in this register are only writable when the NVMKEY unlock sequence is followed. Refer to Example 5-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | _                 | _                 | _                 |                   | IP3<2:0>          | IS3<1:0>          |                  |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | _                 | _                 | _                 |                   | IP2<2:0>          | IS2<1:0>          |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | _                 | _                 |                   | IP1<2:0>          | IS1<              | IS1<1:0>         |                  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0 R/W-0       |                  | R/W-0            |  |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          | IS0<1:0>          |                  |                  |  |

#### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x

#### Legend:

| 0                 |                  |                                          |                    |  |  |

|-------------------|------------------|------------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | e bit U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                     | x = Bit is unknown |  |  |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: | Interrupt | Priority 3 bits |

|-----------|-----------|-----------|-----------------|

- - 00 = Interrupt subpriority is 0

## bit 23-21 Unimplemented: Read as '0'

- bit 20-18 IP2<2:0>: Interrupt Priority 2 bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority 2 bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

| TABLE 10-0. |          |                |             |          |                |  |  |  |  |  |  |  |  |

|-------------|----------|----------------|-------------|----------|----------------|--|--|--|--|--|--|--|--|

| Value       | RPn Pins | Pin Assignment | Value       | RPn Pins | Pin Assignment |  |  |  |  |  |  |  |  |

| 00001       | RP1      | RA0 Pin        | 01110       | RP14     | RB9 Pin        |  |  |  |  |  |  |  |  |

| 00010       | RP2      | RA1 Pin        | 01111       | RP15     | RB13 Pin       |  |  |  |  |  |  |  |  |

| 00011       | RP3      | RA2 Pin        | 10000       | RP16     | RB14 Pin       |  |  |  |  |  |  |  |  |

| 00100       | RP4      | RA3 Pin        | 10001       | RP17     | RB15 Pin       |  |  |  |  |  |  |  |  |

| 00101       | RP5      | RA4 Pin        | 10010       | RP18     | RC9 Pin        |  |  |  |  |  |  |  |  |

| 00110       | RP6      | RB0 Pin        | 10011       | RP19     | RC2 Pin        |  |  |  |  |  |  |  |  |

| 00111       | RP7      | RB1 Pin        | 10100       | RP20     | RC7 Pin        |  |  |  |  |  |  |  |  |

| 01000       | RP8      | RB2 Pin        | 10101       | RP21     | RA7 Pin        |  |  |  |  |  |  |  |  |

| 01001       | RP9      | RB3 Pin        | 10110       | RP22     | RA10 Pin       |  |  |  |  |  |  |  |  |

| 01010       | RP10     | RB4 Pin        | 10111       | RP23     | RC6 Pin        |  |  |  |  |  |  |  |  |

| 01011       | RP11     | RB5 Pin        | 11000       | RP24     | RA9 Pin        |  |  |  |  |  |  |  |  |

| 01100       | RP12     | RB7 Pin        | 11001-11111 | Re       | served         |  |  |  |  |  |  |  |  |

| 01101       | RP13     | RB8 Pin        |             |          |                |  |  |  |  |  |  |  |  |

## TABLE 10-3: REMAPPABLE INPUT SOURCES PIN ASSIGNMENTS<sup>(1)</sup>

**Note 1:** All RPx pins are not available on all packages.

## REGISTER 15-3: SPIxSTAT: SPIx STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPIx Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB, is empty

0 = Transmit buffer, SPIxTXB, is not empty

Automatically set in hardware when SPIx transfers data from SPIxTXB to SPIxSR. Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 SPITBF: SPIx Transmit Buffer Full Status bit

1 = Transmit has not yet started, SPIxTXB is full

0 = Transmit buffer is not full

#### Standard Buffer mode:

Automatically set in hardware when the core writes to the SPIxBUF location, loading SPIxTXB. Automatically cleared in hardware when the SPIx module transfers data from SPIxTXB to SPIxSR.

#### Enhanced Buffer mode:

Set when CPU Write Pointer (CWPTR) + 1 = SPI Read Pointer (SRPTR); cleared otherwise.

#### bit 0 SPIRBF: SPIx Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB, is full

0 = Receive buffer, SPIxRXB, is not full

#### Standard Buffer mode:

Automatically set in hardware when the SPIx module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise.

| Bit<br>Range | Bit<br>31/23/15/7 |     |     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-----|-----|-------------------|------------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0               | U-0 | U-0 | U-0               | U-0                    | U-0               | U-0              | U-0                   |

| 31:24        | _                 | _   | _   | —                 | _                      | _                 | —                | —                     |

| 23:16        | U-0               | U-0 | U-0 | U-0               | U-0                    | U-0               | U-0              | U-0                   |

| 23.10        | _                 | _   | —   | —                 | —                      | —                 | —                | —                     |

| 45.0         | U-0               | U-0 | U-0 | U-0               | U-0                    | U-0               | U-0              | U-0                   |

| 15:8         | _                 | _   |     | —                 |                        | _                 | —                | —                     |

| 7.0          | R-0               | U-0 | U-0 | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0                 |

| 7:0          | UACTPND           | _   |     | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR <sup>(1)</sup> |

#### REGISTER 18-5: U1PWRC: USB POWER CONTROL REGISTER

#### Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected, but an interrupt is pending; it has not been generated yet

- 0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 **USLPGRD:** USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

#### bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit<sup>(1)</sup>

- 1 = USB module is turned on

- USB module is disabled (Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

- **Note 1:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

## TABLE 20-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                                 | é             |           |                 |       |         |          |              |         | Bits    | 5       |        |        |      |               |                |        |       |            |

|-----------------------------|---------------------------------|---------------|-----------|-----------------|-------|---------|----------|--------------|---------|---------|---------|--------|--------|------|---------------|----------------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(2)</sup> | Bit Range     | 31/15     | 30/14           | 29/13 | 28/12   | 27/11    | 26/10        | 25/9    | 24/8    | 23/7    | 22/6   | 21/5   | 20/4 | 19/3          | 18/2           | 17/1   | 16/0  | All Resets |

| 21F0                        | ADC1BUF15                       | 31:16<br>15:0 |           | ADC1BUF15<31:0> |       |         |          |              |         |         |         |        | 0000   |      |               |                |        |       |            |

| 2200                        | ADC1BUF16                       | 31:16<br>15:0 |           | ADC1BUF16<31:0> |       |         |          |              |         |         |         |        | 0000   |      |               |                |        |       |            |

| 2210                        | ADC1BUF17                       | 31:16<br>15:0 |           | ADC1BUF17<31:0> |       |         |          |              |         |         |         |        | 0000   |      |               |                |        |       |            |

| 2220                        | ADC1BUF18                       | 31:16<br>15:0 |           |                 |       |         |          |              | AI      | DC1BUF1 | 8<31:0> |        |        |      |               |                |        |       | 0000       |

| 2230                        | ADC1BUF19                       | 31:16<br>15:0 |           | ADC1BUF19<31:0> |       |         |          |              |         |         |         |        |        | 0000 |               |                |        |       |            |

| 2240                        | ADC1BUF20                       | 31:16<br>15:0 |           |                 |       |         |          |              | AI      | DC1BUF2 | 0<31:0> |        |        |      |               |                |        |       | 0000       |

| 2250                        | ADC1BUF21                       | 31:16<br>15:0 |           |                 |       |         |          |              | AI      | DC1BUF2 | 1<31:0> |        |        |      |               |                |        |       | 0000       |

| 2260                        | AD1CON1                         | 31:16         | _         |                 | _     | _       | _        | -            | _       | _       | -       | —      | _      | _    | _             | _              | _      | _     | 0000       |

|                             |                                 | 15:0          | ON        |                 | SIDL  | _       | _        | F            | ORM<2:0 | >       |         | SSR    | C<3:0> |      | MODE12        | ASAM           | SAMP   | DONE  | 0000       |

| 2270                        | AD1CON2                         | 31:16         | —         | —               |       | —       | —        | —            | _       |         | _       | _      | —      | _    | —             | —              | —      | —     | 0000       |

|                             |                                 | 15:0          |           | VCFG<2:0        |       | OFFCAL  | BUFREGEN | CSCNA        | _       |         | BUFS    | _      |        |      | PI<3:0>       |                | BUFM   | —     | 0000       |

| 2280                        | AD1CON3                         | 31:16<br>15:0 | —<br>ADRC | —<br>EXTSAM     | _     | _       | -        | —<br>1C<4:0> | —       | _       | _       | _      |        | -    | —<br>)CS<7:0> | _              | _      |       | 0000       |

|                             |                                 | 31:16         | ADRC      | EXTSAIVI        |       | _       | 5Aiv     |              | _       | _       | _       | _      | _      | AL   |               |                | _      | _     | 0000       |

| 2290                        | AD1CHS                          | 15:0          |           |                 | _     |         |          |              |         |         |         | HONA<2 |        |      |               | L<br>CHOSA<4:0 |        |       | 0000       |

| -                           |                                 | 31:16         | _         |                 | CSS   | <30:27> |          | _            | _       | _       | _       | _      | _      | _    |               | CSS<           |        |       | 0000       |

| 22A0                        | AD1CSS                          | 15:0          |           | I               | -     |         |          |              |         | CSS<15  | :0>(1)  |        |        |      | I             |                |        |       | 0000       |

| 2200                        |                                 | 31:16         |           | —               | —     | —       | —        | —            |         | _       | —       | —      | —      | —    | —             | —              | —      | —     | 0000       |

| 22C0                        | AD1CON5                         | 15:0          | ASEN      | LPEN            | _     | BGREQ   | _        | _            | ASINT   | <1:0>   | —       | _      | —      | —    | WM<           | :1:0>          | CM<    | :1:0> | 0000       |

| 22D0                        | AD1CHIT                         | 31:16         |           | _               |       |         |          | _            | —       |         | _       | _      | —      |      |               | CHH<           | 19:16> |       | 0000       |

| 2200                        | ADICIT                          | 15:0          |           |                 |       |         |          |              |         | CHH<1   | 5:0>    |        |        |      |               |                |        |       | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The CSS<19:12> bits are not implemented in 28-pin devices. The CSS<19:15> bits are not implemented in 36-pin and 40-pin devices. The CSS<17:14> bits are not implemented in 48-pin devices.

2: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|

| 24.24        | U-0                       | U-0              |

| 31:24        | _                 |                   | _                 | _                 | _                 | _                 | _                         | _                |

| 00.40        | U-0                       | U-0              |

| 23:16        | _                 | -                 | _                 |                   | _                 |                   | _                         | _                |

| 45.0         | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0                     | R/W-0            |

| 15:8         | ASEN              | LPEN              | —                 | BGREQ             | —                 | —                 | ASINT<1:0> <sup>(1)</sup> |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |

| 7:0          | _                 |                   | _                 |                   | WM<               | :1:0>             | CM<1:0>                   |                  |

#### REGISTER 20-4: AD1CON5: ADC CONTROL REGISTER 5

## Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ASEN:** Auto-Scan Enable bit

- 1 = Auto-scan is enabled

- 0 = Auto-scan is disabled

#### bit 14 LPEN: Low-Power Enable bit

- 1 = Low power is enabled after scan

- 0 = Full power is enabled after scan

- bit 13 Unimplemented: Read as '0'

#### bit 12 BGREQ: Band Gap Request bit

- 1 = Band gap is enabled when the ADC is enabled and active

- 0 = Band gap is not enabled by the ADC

- bit 11-10 Unimplemented: Read as '0'

- bit 9-8 **ASINT<1:0>:** Auto-Scan (Threshold Detect) Interrupt Mode bits<sup>(1)</sup>

- 11 = Interrupt after Threshold Detect sequence has completed and a valid compare has occurred

- 10 = Interrupt after valid compare has occurred

- 01 = Interrupt after Threshold Detect sequence has completed

- 00 = No interrupt

- bit 7-4 Unimplemented: Read as '0'

#### bit 3-2 WM<1:0>: Write Mode bits

- 11 = Reserved

- 10 = Auto-compare only (conversion results are not saved, but interrupts are generated when a valid match occurs, as defined by the CM<1:0> and ASINT<1:0> bits)

- 01 = Convert and save (conversion results saved to locations as determined by register bits when a match occurs, as defined by the CM<1:0> bits)

- 00 = Legacy operation (conversion data saved to location determined by buffer register bits)

#### bit 1-0 CM<1:0>: Compare Mode bits

- 11 = Outside Window mode (valid match occurs if the conversion result is outside of the window defined by the corresponding buffer pair)

- 10 = Inside Window mode (valid match occurs if the conversion result is inside the window defined by the corresponding buffer pair)

- 01 = Greater Than mode (valid match occurs if the result is greater than value in the corresponding buffer register)

- 00 = Less Than mode (valid match occurs if the result is less than value in the corresponding buffer register)

- **Note 1:** The ASINT<1:0> bits setting only takes effect when ASEN (AD1CON5<15>) = 1. Interrupt generation is governed by the SMPI<3:0> bits field.

# PIC32MM0256GPM064 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3             | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0                           | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | -                 | _                 |                               | —                 | _                |                  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0                         | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | _                 | —                 | _                 | —                 | CHH<19:16> <sup>(1,2,3)</sup> |                   |                  |                  |  |

| 45.0         | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0                         | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | _                 | —                 |                   | CHH<13:8>         |                               |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                         | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHF               | <del> </del> <7:0>            |                   |                  |                  |  |

## REGISTER 20-7: AD1CHIT: ADC COMPARE HIT REGISTER

## Legend:

| Logonal           |                                 |                      |                    |

|-------------------|---------------------------------|----------------------|--------------------|

| R = Readable bit  | = Readable bit W = Writable bit |                      | ad as '0'          |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

- bit 31-20 Unimplemented: Read as '0'

- bit 19-0 CHH<21:16>: ADC Compare Hit bits<sup>(1,2,3)</sup>

If CM<1:0> = 11:

1 = ADC Result Buffer n has been written with data or a match has occurred

0 = ADC Result Buffer n has not been written with data

For All Other Values of CM<1:0>:

1 = A match has occurred on ADC Result Channel n

0 = No match has occurred on ADC Result Channel n

#### Note 1: The CHH<19:12> bits are not implemented in 28-pin devices

- **2:** The CHH<19:15> bits are not implemented in 36-pin and 40-pin devices

- **3:** The CHH<17:14> bits are not implemented in 48-pin devices

| Peripheral                                               | PMDx Bit Name | Register Name and Bit Location |

|----------------------------------------------------------|---------------|--------------------------------|

| Universal Asynchronous Receiver<br>Transmitter 2 (UART2) | U2MD          | PMD5<1>                        |

| Universal Asynchronous Receiver<br>Transmitter 3 (UART3) | U3MD          | PMD5<2>                        |

| Serial Peripheral Interface 1 (SPI1)                     | SPI1MD        | PMD5<8>                        |

| Serial Peripheral Interface 2 (SPI2)                     | SPI2MD        | PMD5<9>                        |

| Serial Peripheral Interface 3 (SPI3)                     | SPI3MD        | PMD5<10>                       |

| Inter-Integrated Circuit Interface 1 (I2C1)              | I2C1MD        | PMD5<16>                       |

| Inter-Integrated Circuit Interface 2 (I2C2)              | I2C2MD        | PMD5<17>                       |

| Inter-Integrated Circuit Interface 3 (I2C3)              | I2C3MD        | PMD5<18>                       |

| Universal Serial Bus (USB)                               | USBMD         | PMD5<24>                       |

| Real-Time Clock and Calendar (RTCC)                      | RTCCMD        | PMD6<0>                        |

| Reference Clock Output (REFO1)                           | REFOMD        | PMD6<8>                        |

| Direct Memory Access (DMA)                               | DMAMD         | PMD7<4>                        |

## TABLE 25-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS (CONTINUED)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 31:24        |                   |                   |                   | USERIE            | )<15:8>           |                   |                  |                  |  |

| 00.40        | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 15:8         | FVBUSIO           | FUSBIDIO          | _                 | —                 | —                 | _                 |                  | _                |  |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | r-1               | r-1              | r-1              |  |

| 7:0          |                   | _                 |                   | ALTI2C            | SOSCHP            |                   | _                |                  |  |

#### REGISTER 26-1: FDEVOPT/AFDEVOPT: DEVICE OPTIONS CONFIGURATION REGISTER

| Legend: r = Reserved bit |                   | r = Reserved bit | P = Programmable bit                    |  |  |  |  |

|--------------------------|-------------------|------------------|-----------------------------------------|--|--|--|--|

|                          | R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |  |  |

|                          | -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |  |  |

bit 31-16 USERID<15:0>: User ID bits (2 bytes which can programmed to any value)

- bit 15 FVBUSIO: USB VBUS\_ON Selection bit

- 1 = VBUSON pin is controlled by the USB module 0 = VBUSON pin is controlled by the port function

- bit 14 FUSBIDIO: USB USBID Selection bit

- 1 = USBID pin is controlled by the USB module

- 0 = USBID pin is controlled by the port function

- bit 13-5 **Reserved:** Program as '1'

- bit 4 ALTI2C: Alternate I2C1 Location Select bit

- 1 = SDA1 and SCL1 are on pins, RB8 and RB9

- 0 = SDA1 and SCL1 are moved to alternate I<sup>2</sup>C locations, RB5 and RC9

- SOSCHP: Secondary Oscillator (SOSC) High-Power Enable bit

- 1 = SOSC operates in normal power mode

- 0 = SOSC operates in High-Power mode

- bit 2-0 Reserved: Program as '1'

bit 3

## 28.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 28.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 28.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 28.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

# PIC32MM0256GPM064 FAMILY

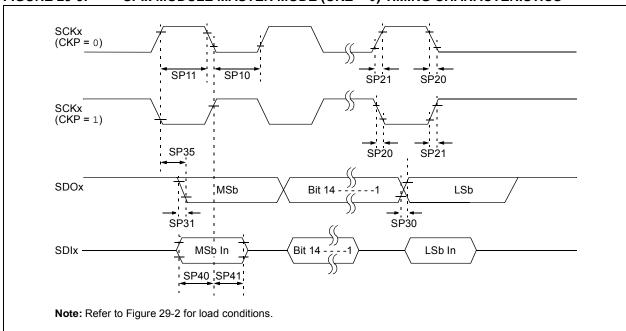

#### FIGURE 29-9: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

## TABLE 29-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                               | Standard Operating Conditions: 2.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |                        |      |       |                    |

|--------------------|-----------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|

| Param<br>No.       | Symbol                | Characteristics <sup>(1)</sup>                | Min.                                                                                                                             | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10               | TscL                  | SCKx Output Low Time <sup>(3)</sup>           | Tsck/2                                                                                                                           | _                      | _    | ns    |                    |

| SP11               | TscH                  | SCKx Output High Time <sup>(3)</sup>          | Tsck/2                                                                                                                           | —                      | _    | ns    |                    |

| SP20               | TscF                  | SCKx Output Fall Time <sup>(4)</sup>          | —                                                                                                                                | —                      | _    | ns    | See Parameter DO32 |

| SP21               | TscR                  | SCKx Output Rise Time <sup>(4)</sup>          | _                                                                                                                                | _                      | _    | ns    | See Parameter DO31 |

| SP30               | TDOF                  | SDOx Data Output<br>Fall Time <sup>(4)</sup>  |                                                                                                                                  | —                      |      | ns    | See Parameter DO32 |

| SP31               | TDOR                  | SDOx Data Output<br>Rise Time <sup>(4)</sup>  | _                                                                                                                                | —                      |      | ns    | See Parameter DO31 |

| SP35               | TscH2doV,             | SDOx Data Output Valid                        | _                                                                                                                                | _                      | 7    | ns    | VDD > 2.0V         |

|                    | TscL2DoV              | after SCKx Edge                               | _                                                                                                                                | _                      | 10   | ns    | VDD < 2.0V         |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data<br>Input to SCKx Edge | 5                                                                                                                                | —                      | _    | ns    |                    |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data<br>Input to SCKx Edge  | 5                                                                                                                                | —                      | _    | ns    |                    |

Note 1: These parameters are characterized but not tested in manufacturing.

**2:** Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 10 pF load on all SPIx pins.

| Operating    | Conditions: 2.0 | $V \le V$ DD $\le 3.6$ V, -40°C $\le$ TA $\le$ +85°C (unless ) | otherwise stated) |            |       |

|--------------|-----------------|----------------------------------------------------------------|-------------------|------------|-------|

| Param<br>No. | Symbol          | Characteristic                                                 | Min               | Max        | Units |

|              | -               | Reference Inputs                                               |                   | ·          |       |

| AD05         | VREFH           | Reference Voltage High                                         | AVss + 1.7        | AVDD       | V     |

| AD06         | VREFL           | Reference Voltage Low                                          | AVss              | AVDD – 1.7 | V     |

| AD07         | VREF            | Absolute Reference<br>Voltage                                  | AVss – 0.3        | AVDD + 0.3 | V     |

|              |                 | Analog Inputs                                                  |                   |            |       |

| AD10         | VINH-VINL       | Full-Scale Input Span                                          | VREFL             | VREFH      | V     |

| AD11         | VIN             | Absolute Input Voltage                                         | AVss – 0.3        | AVDD + 0.3 | V     |

| AD12         | VINL            | Absolute VINL Input Voltage                                    | AVss - 0.3        | AVDD + 0.3 | V     |

| AD17         | RIN             | Recommended Impedance of Analog<br>Voltage Source              | _                 | 2.5K       | Ω     |

## TABLE 29-34: ADC MODULE INPUTS SPECIFICATIONS

# TABLE 29-35: ADC ACCURACY AND CONVERSION TIMING REQUIREMENTS FOR 12-BIT MODE<sup>(1)</sup>

| Operatin     | g Conditions: \ | /dd = 3.3V, AVss = Vrefl = 0V, AVd                   | D = VREFH = 3.3 | $3V$ , $-40^{\circ}C \le TA \le$ | ≨+85°C      |       |  |  |  |  |

|--------------|-----------------|------------------------------------------------------|-----------------|----------------------------------|-------------|-------|--|--|--|--|

| Param<br>No. | Symbol          | Characteristic                                       | Min             | Typ <sup>(2)</sup>               | Мах         | Units |  |  |  |  |

|              | ADC Accuracy    |                                                      |                 |                                  |             |       |  |  |  |  |

| AD20B        | Nr              | Resolution                                           | —               | 12                               | —           | bits  |  |  |  |  |

| AD21B        | INL             | Integral Nonlinearity                                | —               | ±2.5                             | ±3.5        | LSb   |  |  |  |  |

| AD22B        | DNL             | Differential Nonlinearity                            | —               | ±0.75                            | +1.75/-0.95 | LSb   |  |  |  |  |

| AD23B        | Gerr            | Gain Error                                           | _               | +2                               | +3          | LSb   |  |  |  |  |

| AD24B        | EOFF            | Offset Error                                         | —               | +1                               | +2          | LSb   |  |  |  |  |

|              | ·               | Clock Para                                           | meters          |                                  |             |       |  |  |  |  |

| AD50B        | TAD             | ADC Clock Period                                     | 280             | —                                | —           | ns    |  |  |  |  |

| AD61B        | tPSS            | Sample Start Delay from Setting<br>Sample bit (SAMP) | 2               | —                                | 3           | Tad   |  |  |  |  |

|              |                 | Conversion                                           | n Rate          |                                  |             |       |  |  |  |  |

| AD55B        | tCONV           | Conversion Time                                      | —               | 14                               | —           | TAD   |  |  |  |  |

| AD56B        | FCNV            | Throughput Rate                                      | —               | —                                | 200         | ksps  |  |  |  |  |

Note 1: Measurements are taken with the external VREF+ and VREF- used as the ADC voltage reference.

2: Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

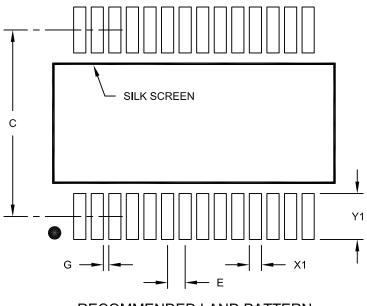

28-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | Units    |          |      | S    |

|--------------------------|----------|----------|------|------|

| Dimensio                 | n Limits | MIN      | NOM  | MAX  |

| Contact Pitch            | E        | 0.65 BSC |      |      |

| Contact Pad Spacing      | С        |          | 7.20 |      |

| Contact Pad Width (X28)  | X1       |          |      | 0.45 |

| Contact Pad Length (X28) | Y1       |          |      | 1.75 |

| Distance Between Pads    | G        | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2073A

#### 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |           |          |      |

|------------------------|-------------|-----------|----------|------|

| Dimension              | Limits      | MIN       | NOM      | MAX  |

| Number of Pins         | Ν           |           | 40       |      |

| Pitch                  | е           |           | 0.40 BSC |      |

| Overall Height         | Α           | 0.45      | 0.50     | 0.55 |

| Standoff               | A1          | 0.00      | 0.02     | 0.05 |

| Contact Thickness      | A3          | 0.127 REF |          |      |

| Overall Width          | Е           | 5.00 BSC  |          |      |

| Exposed Pad Width      | E2          | 3.60      | 3.70     | 3.80 |

| Overall Length         | D           |           | 5.00 BSC |      |

| Exposed Pad Length     | D2          | 3.60      | 3.70     | 3.80 |

| Contact Width          | b           | 0.15      | 0.20     | 0.25 |

| Contact Length         | L           | 0.30      | 0.40     | 0.50 |

| Contact-to-Exposed Pad | K           | 0.20      | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-156A Sheet 2 of 2

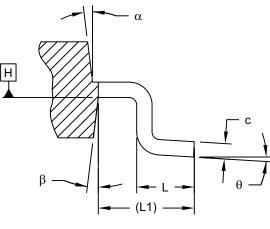

## 48-Lead Thin Quad Flatpack (PT) - 7x7x1.0 mm Body [TQFP] With Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

SECTION A-A

|                          | MILLIMETERS |                |          |      |  |

|--------------------------|-------------|----------------|----------|------|--|

| Dimension                | MIN         | NOM            | MAX      |      |  |

| Number of Leads          | Ν           |                | 48       |      |  |

| Lead Pitch               | е           |                | 0.50 BSC |      |  |

| Overall Height           | Α           | -              | -        | 1.20 |  |

| Standoff                 | A1          | 0.05           | -        | 0.15 |  |

| Molded Package Thickness | A2          | 0.95           | 1.00     | 1.05 |  |

| Foot Length              | L           | 0.45 0.60 0.75 |          |      |  |

| Footprint                | L1          | 1.00 REF       |          |      |  |

| Foot Angle               | ¢           | 0° 3.5° 7°     |          |      |  |

| Overall Width            | E           |                | 9.00 BSC |      |  |

| Overall Length           | D           |                | 9.00 BSC |      |  |

| Molded Package Width     | E1          |                | 7.00 BSC |      |  |

| Molded Package Length    | D1          |                | 7.00 BSC |      |  |

| Exposed Pad Width        | E2          |                | 3.50 BSC |      |  |

| Exposed Pad Length       | D2          |                | 3.50 BSC |      |  |

| Lead Thickness           | С           | 0.09           | -        | 0.16 |  |

| Lead Width               | b           | 0.17 0.22 0.27 |          |      |  |

| Mold Draft Angle Top     | α           | 11° 12° 13°    |          |      |  |

| Mold Draft Angle Bottom  | β           | 11°            | 12°      | 13°  |  |

Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-183A Sheet 2 of 2

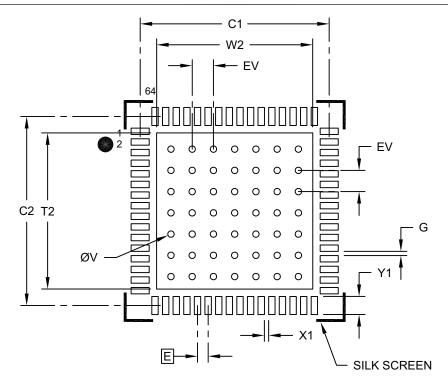

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 7.70x7.70mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                 | Units    | MILLIMETERS    |          |      |

|---------------------------------|----------|----------------|----------|------|

| Dimensior                       | n Limits | nits MIN NOM M |          | MAX  |

| Contact Pitch                   | E        |                | 0.50 BSC |      |

| Optional Center Pad Width       | W2       |                |          | 7.50 |

| Optional Center Pad Length      | T2       |                |          | 7.50 |

| Contact Pad Spacing             | C1       |                | 8.90     |      |

| Contact Pad Spacing             | C2       |                | 8.90     |      |

| Contact Pad Width (X20)         | X1       |                |          | 0.30 |

| Contact Pad Length (X20)        | Y1       |                |          | 0.90 |

| Contact Pad to Center Pad (X20) | G        | 0.20           |          |      |

| Thermal Via Diameter            | V        |                | 0.30     |      |

| Thermal Via Pitch               | EV       |                | 1.00     |      |

Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2213B

## Ε

| Electrical Characteristics |    |

|----------------------------|----|

| Absolute Maximum Ratings   |    |

| V/F Graph (Industrial)     |    |

| Errata                     | 12 |

| F                          |    |

|                            |    |

| Flash Program Memory                        |    |

|---------------------------------------------|----|

| Flash Controller Registers Write Protection | 45 |

| Write Protection                            | 45 |

## G

| Getting Started with PIC32 MCUs | 23 |

|---------------------------------|----|

| Connection Requirements         | 23 |

| Decoupling Capacitors           | 23 |

| External Oscillator Pins        | 27 |

| ICSP Pins                       |    |

| JTAG                            | 27 |

| Master Clear (MCLR) Pin         | 24 |

| Unused I/Os                     | 27 |

| Voltage Regulator (VCAP)        |    |

|                                 |    |

## Н

| High/Low-Voltage Detect (HLVD)     | 253 |

|------------------------------------|-----|

| High/Low-Voltage Detect. See HLVD. |     |

# I

| I/O Ports                                       | . 113 |

|-------------------------------------------------|-------|

| Analog/Digital Port Pins Configuration          | . 114 |

| CLR, SET and INV Registers                      | . 114 |

| GPIO Port Merging                               | . 114 |

| Open-Drain Configuration                        | . 114 |

| Parallel I/O (PIO)                              | . 114 |

| Pull-up/Pull-Down Pins                          | . 115 |

| Write/Read Timing                               | . 114 |

| Input Change Notification (ICN)                 | . 114 |

| Instruction Set                                 | . 281 |

| Inter-IC Sound. See I <sup>2</sup> S.           |       |

| Inter-Integrated Circuit (I <sup>2</sup> C      | . 167 |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |       |

| Internet Address                                | . 353 |

| Interrupts                                      |       |

| Sources and Vector Names                        | 62    |

#### Μ

| MCCP/SCCP                                                         |     |

|-------------------------------------------------------------------|-----|

| Registers                                                         | 142 |

| Memory Maps                                                       |     |

| Devices with 128 Kbytes Program Memory                            |     |

| Devices with 256 Kbytes Program Memory                            |     |

| Devices with 64 Kbytes Program Memory                             | 41  |

| Memory Organization                                               |     |

| Alternate Configuration Bits Space                                |     |

| Bus Matrix (BMX)                                                  |     |

| Flash Line Buffer                                                 |     |

| Microchip Internet Web Site                                       | 353 |

| MIPS32 <sup>®</sup> microAptiv <sup>™</sup> UC Core Configuration |     |

| MPLAB Assembler, Linker, Librarian                                |     |

| MPLAB ICD 3 In-Circuit Debugger                                   |     |

| MPLAB PM3 Device Programmer                                       |     |

| MPLAB REAL ICE In-Circuit Emulator System                         |     |

| MPLAB X Integrated Development                                    |     |

| Environment Software                                              |     |

|                                                                   |     |

| MPLAB X SIM Software Simulator                  | 285 |

|-------------------------------------------------|-----|

| MPLIB Object Librarian                          |     |

| MPLINK Object Linker                            |     |

| Multiply/Divide Unit Latencies and Repeat Rates | 31  |

## 0

| Oscillator Configuration       |  |

|--------------------------------|--|

| Clock Switching                |  |

| Sequence                       |  |

| Fail-Safe Clock Monitor (FSCM) |  |

| FRC Self-Tuning                |  |

## Ρ

| Packaging                               | 319 |

|-----------------------------------------|-----|

| Details                                 | 321 |

| Marking                                 | 319 |

| Peripheral Pin Select (PPS)             | 115 |

| PICkit 3 In-Circuit Debugger/Programmer |     |

| Pinout Description                      | 16  |

| Power-Saving Features                   | 257 |

| Idle Mode                               | 257 |

| Low-Power Brown-out Reset               | 261 |

| On-Chip Voltage Regulator               |     |

| (Low-Power Modes)                       | 261 |

| Peripheral Module Disable               | 258 |

| Retention Sleep Mode                    | 257 |

| Sleep Mode                              | 257 |

| Standby Sleep Mode                      | 257 |

| PPS                                     |     |

| Available Peripherals                   | 115 |

| Available Pins                          | 115 |

| Controlling                             | 115 |

| Controlling Configuration Changes       | 118 |

| Input Mapping                           | 116 |

| Input Pin Selection                     | 116 |

| Output Mapping                          | 118 |

| Output Pin Selection                    | 119 |

| Remappable Pin Input Source Assignments | 117 |

| Programming and Diagnostics             | 264 |

|                                         |     |

## R

| Real-Time Clock and Calendar (RTCC)<br>Real-Time Clock and Calendar. See RTCC.<br>Register Maps | . 209 |

|-------------------------------------------------------------------------------------------------|-------|

| ADC                                                                                             | 219   |

| Alternate Configuration Words Summary                                                           | 266   |

| Band Gap                                                                                        | 277   |

| CLC1, CLC2 and CLC3                                                                             | 233   |

| Comparator 1, 2 and 3                                                                           |       |

| Configuration Words Summary                                                                     | 265   |

| DMA Channels 0-3                                                                                | 79    |

| DMA Controller                                                                                  | 78    |

| Flash Controller                                                                                | 46    |

| High/Low Voltage Detect                                                                         | . 254 |

| I2C1, I2C2 and I2C3                                                                             | 169   |

| Interrupts                                                                                      | 66    |

| MCCP/SCCP                                                                                       | 143   |

| Oscillator Configuration                                                                        | . 102 |

| Peripheral Module Disable                                                                       | 260   |

| Peripheral Pin Select                                                                           | 124   |

| PORTA                                                                                           | 120   |

| PORTB                                                                                           | 121   |

| PORTC                                                                                           | 122   |

|                                                                                                 |       |