Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0128gpm064-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

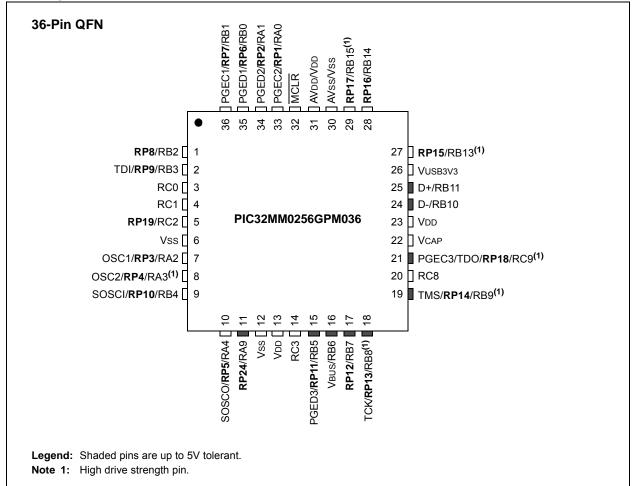

## **Pin Diagrams (Continued)**

#### TABLE 4: COMPLETE PIN FUNCTION DESCRIPTIONS FOR 36-PIN QFN DEVICES

| Pin | Function                                                    | Pin | Function                                                                       |

|-----|-------------------------------------------------------------|-----|--------------------------------------------------------------------------------|

| 1   | AN4/C1INB/RP8/SDA2/OCM2E/RB2                                | 19  | TMS/REFCLKI/RP14/SDA1/T1CK/T1G/U1RTS/U1BCLK/SDO1/OCM1B/INT2/RB9 <sup>(1)</sup> |

| 2   | TDI/AN11/C1INA/RP9/SCL2/OCM2F/RB3                           | 20  | AN14/LVDIN/C2INC/RC8                                                           |

| 3   | AN12/C2IND/T2CK/T2G/RC0                                     | 21  | PGEC3/TDO/RP18/ASCL1 <sup>(2)</sup> /USBOEN/SDO3/RC9 <sup>(1)</sup>            |

| 4   | AN13/T3CK/T3G/RC1                                           | 22  | VCAP                                                                           |

| 5   | RP19/OCM2A/RC2                                              | 23  | VDD                                                                            |

| 6   | Vss                                                         | 24  | D-/RB10                                                                        |

| 7   | OSC1/CLKI/AN5/RP3/OCM1C/RA2                                 | 25  | D+/RB11                                                                        |

| 8   | OSC2/CLKO/AN6/C3IND/RP4/OCM1D/RA3 <sup>(1)</sup>            | 26  | VUSB3V3                                                                        |

| 9   | SOSCI/AN7/RP10/OCM3C/RB4                                    | 27  | AN8/ <b>RP15</b> /SCL3/SCK3/RB13 <sup>(1)</sup>                                |

| 10  | SOSCO/SCLKI/RP5/PWRLCLK/OCM3D/RA4                           | 28  | CVREF/AN9/C3INB/RP16/RTCC/U1TX/VBUSON/SDI1/OCM3B/INT1/RB14                     |

| 11  | RP24/OCM3A/RA9                                              | 29  | AN10/C3INA/REFCLKO/RP17/U1RX/SS1/FSYNC1/OCM2B/INT0/RB15 <sup>(1)</sup>         |

| 12  | Vss                                                         | 30  | AVss/Vss                                                                       |

| 13  | Vdd                                                         | 31  | AVdd/Vdd                                                                       |

| 14  | RC3                                                         | 32  | MCLR                                                                           |

| 15  | PGED3/RP11/ASDA1 <sup>(2)</sup> /USBID/SS3/FSYNC3/OCM3E/RB5 | 33  | PGEC2/VREF+/CVREF+/AN0/ <b>RP1</b> /OCM1E/INT3/RA0                             |

| 16  | VBUS/RB6                                                    | 34  | PGED2/VREF-/AN1/ <b>RP2</b> /OCM1F/RA1                                         |

| 17  | RP12/SDA3/SDI3/OCM3F/RB7                                    | 35  | PGED1/AN2/C1IND/C2INB/C3INC/RP6/OCM2C/RB0                                      |

| 18  | TCK/RP13/SCL1/U1CTS/SCK1/OCM1A/RB8 <sup>(1)</sup>           | 36  | PGEC1/AN3/C1INC/C2INA/ <b>RP7</b> /OCM2D/RB1                                   |

Note 1: High drive strength pin.

2: Alternate pin assignments for I2C1 as determined by the I2C1SEL Configuration bit.

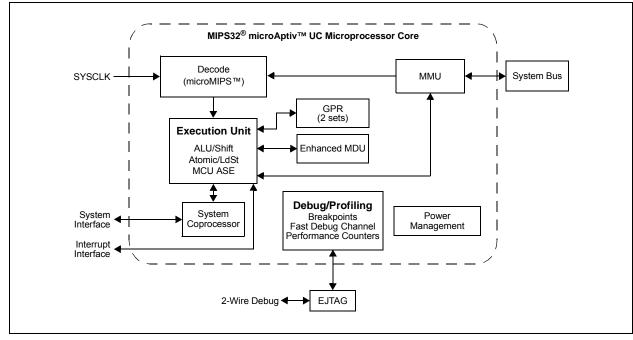

#### FIGURE 3-1: PIC32MM0256GPM064 FAMILY MICROPROCESSOR CORE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 |     |       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-----|-------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0 U-0 R/W-0     |     | R/W-0 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | _                 | _   |       | IP3<2:0>          | IS3<1:0>          |                  |                  |

| 00.40        | U-0               | U-0               | U-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | _   |       | IP2<2:0>          |                   | IS2<             | 1:0>             |

| 45.0         | U-0               | U-0               | U-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _   |       | IP1<2:0>          |                   | IS1<             | 1:0>             |

| 7.0          | U-0               | U-0               | U-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _   |       | IP0<2:0>          |                   | IS0<             | 1:0>             |

### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x

#### Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: | Interrupt | Priority 3 bits |

|-----------|-----------|-----------|-----------------|

- - 00 = Interrupt subpriority is 0

## bit 23-21 Unimplemented: Read as '0'

- bit 20-18 IP2<2:0>: Interrupt Priority 2 bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority 2 bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

NOTES:

## REGISTER 9-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7   | CLKLOCK: Clock Selection Lock Enable bit<br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified                |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6-5 | Unimplemented: Read as '0'                                                                                                                                            |

| bit 4   | SLPEN: Sleep Mode Enable bit                                                                                                                                          |

|         | <ul> <li>1 = Device will enter Sleep mode when a WAIT instruction is executed</li> <li>0 = Device will enter Idle mode when a WAIT instruction is executed</li> </ul> |

| bit 3   | CF: Clock Fail Detect bit                                                                                                                                             |

|         | <ul><li>1 = FSCM has detected a clock failure</li><li>0 = No clock failure has been detected</li></ul>                                                                |

| bit 2   | Unimplemented: Read as '0'                                                                                                                                            |

| bit 1   | SOSCEN: Secondary Oscillator (SOSC) Enable bit                                                                                                                        |

|         | <ul><li>1 = Enables the Secondary Oscillator</li><li>0 = Disables the Secondary Oscillator</li></ul>                                                                  |

| bit 0   | <b>OSWEN:</b> Oscillator Switch Enable bit <sup>(1)</sup>                                                                                                             |

|         | <ul> <li>1 = Initiates an oscillator switch to a selection specified by the NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                |

|         |                                                                                                                                                                       |

**Note 1:** The Reset value for this bit depends on the setting of the IESO (FOSCSEL<7>) bit. When IESO = 1, the Reset value is '1'. When IESO = 0, the Reset value is '0'.

Note: Writes to this register require an unlock sequence. Refer to Section 26.4 "System Registers Write Protection" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 22.40        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | _                 | -                 | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | r-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                | —                 | SIDL              | SRC               | LOCK              | POL               | ORNG             | ORPOL            |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

#### **REGISTER 9-6: OSCTUN: FRC TUNING REGISTER**

| Legend:           | r = Reserved bit |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### k

| bit 21 16 | Unimplemented: Deed on 'o'                                                                                                                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | Unimplemented: Read as '0'                                                                                                                                                                                                             |

| bit 15    | ON: Self-Tune Enable bit                                                                                                                                                                                                               |

|           | <ul> <li>1 = FRC self-tuning is enabled; the TUNx bits are controlled by hardware</li> <li>0 = FRC self-tuning is disabled; the TUNx bits are readable and writable</li> </ul>                                                         |

| bit 14    | Reserved: Used by debugger                                                                                                                                                                                                             |

| bit 13    | SIDL: FRC Self-Tune Stop in Idle bit                                                                                                                                                                                                   |

|           | 1 = Self-tuning stops during Idle mode                                                                                                                                                                                                 |

|           | 0 = Self-tuning continues during Idle mode                                                                                                                                                                                             |

| bit 12    | SRC: FRC Self-Tune Reference Clock Source bit                                                                                                                                                                                          |

|           | 1 = The USB host clock is used to tune the FRC                                                                                                                                                                                         |

|           | 0 = The 32.768 kHz SOSC clock is used to tune the FRC                                                                                                                                                                                  |

| bit 11    | LOCK: FRC Self-Tune Lock Status bit                                                                                                                                                                                                    |

|           | 1 = FRC accuracy is currently within ±0.2% of the SRC reference accuracy                                                                                                                                                               |

|           | 0 = FRC accuracy may not be within ±0.2% of the SRC reference accuracy                                                                                                                                                                 |

| bit 10    | POL: FRC Self-Tune Lock Interrupt Polarity bit                                                                                                                                                                                         |

|           | 1 = A self-tune lock interrupt is generated when LOCK is '0'                                                                                                                                                                           |

|           | 0 = A self-tune lock interrupt is generated when LOCK is '1'                                                                                                                                                                           |

| bit 9     | ORNG: FRC Self-Tune Out of Range Status bit                                                                                                                                                                                            |

|           | 1 = SRC reference clock error is beyond the range of TUN<5:0>; no tuning is performed                                                                                                                                                  |

|           | 0 = SRC reference clock is within the tunable range; tuning is performed                                                                                                                                                               |

| bit 8     | ORPOL: FRC Self-Tune Out of Range Interrupt Polarity bit                                                                                                                                                                               |

|           | 1 = A self-tune out of range interrupt is generated when STOR is '0'                                                                                                                                                                   |

|           | 0 = A self-tune out of range interrupt is generated when STOR is '1'                                                                                                                                                                   |

| bit 7-6   | Unimplemented: Read as '0'                                                                                                                                                                                                             |

| Note 1:   | OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step-size is an approximation and is neither characterized, nor tested. |

|           |                                                                                                                                                                                                                                        |

Writes to this register require an unlock sequence. Refer to Section 26.4 "System Registers Write Note: Protection" for details.

#### TABLE 18-1: USB OTG REGISTER MAP

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bits                   |                    |                      |          |            |          |                 |                    | Ī |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------------------------|--------------------|----------------------|----------|------------|----------|-----------------|--------------------|---|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6               | 21/5                 | 20/4     | 19/3       | 18/2     | 17/1            | 16/0               |   |

| 0.4.40                      |                                 | 31:16     | _     | _     | -     | _     | _     | _     | _    | —    | _                      | —                  | _                    | _        | —          | _        | _               | _                  | Ī |

| 8440                        | U1OTGIR <sup>(2)</sup>          | 15:0      | _     | _     | _     | _     | _     | _     | _    | —    | IDIF                   | T1MSECIF           | LSTATEIF             | ACTVIF   | SESVDIF    | SESENDIF | _               | VBUSVDIF           | Ì |

| 8450                        | U10TGIE                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | —                  | _                    | —        | _          | _        | _               | _                  | Ī |

|                             |                                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | IDIE                   | T1MSECIE           | LSTATEIE             | ACTVIE   | SESVDIE    | SESENDIE | _               | VBUSVDIE           | Ī |

| 0400                        | U1OTGSTAT <sup>(3)</sup>        | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | _                  | —                    | —        | —          | _        | _               | _                  | Ĩ |

| 8460                        | UIUIGSIAI                       | 15:0      |       | _     |       | _     |       | _     | _    | _    | ID                     | —                  | LSTATE               | _        | SESVD      | SESEND   |                 | VBUSVD             |   |

| 8470                        | U10TGCON                        | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | —                  | _                    | _        | _          | _        | _               | _                  | Ī |

| 0470                        | UIUIGCON                        | 15:0      | _     | _     | _     | _     |       | _     | _    | _    | DPPULUP                | DMPULUP            | DPPULDWN             | DMPULDWN | VBUSON     | OTGEN    | VBUSCHG         | VBUSDIS            |   |

| 0400                        |                                 | 31:16     |       | _     |       |       |       | —     | —    | _    |                        | —                  | _                    | _        | _          | _        |                 | _                  |   |

| 8480                        | U1PWRC                          | 15:0      |       | -     |       |       |       | —     | —    | _    | UACTPND <sup>(4)</sup> | —                  | _                    | USLPGRD  | USBBUSY    | —        | USUSPEND        | USBPWR             |   |

|                             |                                 | 31:16     |       | -     |       |       |       | —     | _    | _    |                        | _                  | _                    | _        | _          | —        |                 | _                  |   |

| 8600                        | U1IR <sup>(2)</sup>             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | STALLIF                | ATTACHIF           | RESUMEIF             | IDLEIF   | TRNIF      | SOFIF    | UERRIF          | URSTIF<br>DETACHIF | l |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     |       |      | _    | _                      | _                  | _                    | _        | _          | _        | _               |                    | t |

| 8610                        | U1IE                            | 01.10     |       |       |       |       |       |       |      |      |                        |                    |                      |          |            |          |                 | URSTIE             | t |

| 0010                        | OTIL                            | 15:0      | _     | _     | _     | —     | —     | —     | _    | _    | STALLIE                | ATTACHIE           | RESUMEIE             | IDLEIE   | TRNIE      | SOFIE    | UERRIE          | DETACHIE           | Ì |

|                             |                                 | 31:16     | _     | _     | _     | —     | _     | —     | —    | —    | _                      | —                  | —                    | —        | —          | —        | _               |                    |   |

| 8620                        | U1EIR <sup>(2)</sup>            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEF                  | BMXEF              | DMAEF                | BTOEF    | DFN8EF     | CRC16EF  | CRC5EF<br>EOFEF | PIDEF              | - |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | _                  | _                    | _        | _          | _        | _               | _                  | t |

| 8630                        | U1EIE                           |           |       |       |       |       |       |       |      |      |                        |                    |                      |          |            |          | CRC5EE          |                    | t |

|                             |                                 | 15:0      | _     | —     | _     | —     | _     | —     | _    | _    | BTSEE                  | BMXEE              | DMAEE                | BTOEE    | DFN8EE     | CRC16EE  | EOFEE           | PIDEE              |   |

| 8640                        | U1STAT <sup>(3)</sup>           | 31:16     | _     | —     | _     | —     | _     | —     | —    |      | _                      | _                  | —                    | —        | _          | —        | _               |                    |   |

| 0040                        | UIUIA                           | 15:0      | _     | —     | _     | —     | _     | —     | —    |      |                        | ENDPT              | <3:0> <sup>(4)</sup> |          | DIR        | PPBI     | _               |                    |   |

|                             |                                 | 31:16     | _     | —     | _     | —     | _     | —     | —    | _    | _                      | _                  | _                    | _        | _          | —        | _               |                    |   |

| 8650                        | U1CON                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | PKTDIS               | USBRST   | HOSTEN     | RESUME   | PPBRST          | USBEN              |   |

|                             |                                 | 10.0      |       |       |       |       |       |       |      |      |                        | 020                | TOKBUSY              | JOBILOT  |            |          |                 | SOFEN              | l |

| 8660                        | U1ADDR                          | 31:16     | -     | —     | -     | —     | —     | _     | —    | —    | -                      | —                  | —                    | —        | —          | —        | —               | —                  | 1 |

| 0000                        | O IN LEDIT                      | 15:0      | —     | —     | —     | -     | —     | —     | —    | —    | LSPDEN                 |                    |                      | DE       | EVADDR<6:0 | )>       |                 |                    | 1 |

All Resets

0000

0000

0000

0000

0000

0000 0000

0000 0000

0000 0000

0000

0000

0000

0000

0000 0000

0000

0000

0000 0000

0000

0000

0000

0000

0000

0000

0000 0000

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 10.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for these bits is undefined.

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------------------|-----------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                                |           |                   | —                 |                   |                   | _                | —                |

| 00.40        | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                                | _         | —                 | —                 |                   | —                 | _                | _                |

| 45.0         | R/W-0                            | R/W-0     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |

| 15:8         |                                  | VCFG<2:0> |                   | OFFCAL            | BUFREGEN          | CSCNA             | _                | _                |

| 7.0          | R/W-0                            | U-0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          | BUFS                             | _         |                   | SMP               | <3:0>             |                   | BUFM             | —                |

#### REGISTER 20-2: AD1CON2: ADC CONTROL REGISTER 2

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

## bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|         |                                                                                                                                                                                               | ADC Vr+                                                                                          | ADC VR-                     |                                                                 |  |  |  |  |  |  |  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------|--|--|--|--|--|--|--|

|         | 000                                                                                                                                                                                           | AVdd                                                                                             | AVss                        |                                                                 |  |  |  |  |  |  |  |

|         | 001                                                                                                                                                                                           | AVdd                                                                                             | External VREF- Pin          |                                                                 |  |  |  |  |  |  |  |

|         | 010                                                                                                                                                                                           | External VREF+ Pin                                                                               | AVss                        |                                                                 |  |  |  |  |  |  |  |

|         | 011                                                                                                                                                                                           | External VREF+ Pin                                                                               | External VREF- Pin          |                                                                 |  |  |  |  |  |  |  |

|         | 1xx                                                                                                                                                                                           | Unimplemente                                                                                     | d; do not use               |                                                                 |  |  |  |  |  |  |  |

| bit 12  | 1 = Enables                                                                                                                                                                                   |                                                                                                  | inputs of the SHA are con   | nected to the negative reference<br>trolled by AD1CHS or AD1CSS |  |  |  |  |  |  |  |

| bit 11  | <b>BUFREGEN:</b> ADC Buffer Register Enable bit<br>1 = Conversion result is loaded into the buffer location determined by the converted channel<br>0 = ADC result buffer is treated as a FIFO |                                                                                                  |                             |                                                                 |  |  |  |  |  |  |  |

| bit 10  | CSCNA: Sca                                                                                                                                                                                    | an Input Selections for CH0+                                                                     | SHA Input for Input Multipl | exer Setting bit                                                |  |  |  |  |  |  |  |

|         | 1 = Scans inputs<br>0 = Does not scan inputs                                                                                                                                                  |                                                                                                  |                             |                                                                 |  |  |  |  |  |  |  |

| bit 9-8 | Unimpleme                                                                                                                                                                                     | nted: Read as '0'                                                                                |                             |                                                                 |  |  |  |  |  |  |  |

| bit 7   | BUFS: Buffe                                                                                                                                                                                   | r Fill Status bit                                                                                |                             |                                                                 |  |  |  |  |  |  |  |

|         | 1 = ADC is c                                                                                                                                                                                  | nen BUFM = 1 (ADC buffers<br>urrently filling Buffers 11-21,<br>urrently filling Buffers 0-10, u | user should access data in  | 0-10                                                            |  |  |  |  |  |  |  |

| bit 6   | Unimpleme                                                                                                                                                                                     | nted: Read as '0'                                                                                |                             |                                                                 |  |  |  |  |  |  |  |

| bit 5-2 |                                                                                                                                                                                               | Sample/Convert Sequences                                                                         |                             |                                                                 |  |  |  |  |  |  |  |

|         |                                                                                                                                                                                               | rupts at the completion of con<br>rupts at the completion of con                                 |                             |                                                                 |  |  |  |  |  |  |  |

|         | 0000 = Inter                                                                                                                                                                                  | rupts at the completion of con<br>rupts at the completion of con                                 | nversion for each sample/c  |                                                                 |  |  |  |  |  |  |  |

| bit 1   | 1 = Buffer co                                                                                                                                                                                 | Result Buffer Mode Select b<br>onfigured as two 11-word buff<br>onfigured as one 22-word buff    | ers, ADC1BUF(010), AD       | C1BUF(1121)                                                     |  |  |  |  |  |  |  |

| bit 0   | Unimpleme                                                                                                                                                                                     | nted: Read as '0'                                                                                |                             |                                                                 |  |  |  |  |  |  |  |

## 21.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCON

- CLCxSEL

- CLCxGLS

The CLCx Control register (CLCxCON) is used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Source Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Select register (CLCxGLS) allows the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

### REGISTER 21-2: CLCxSEL: CLCx INPUT MUX SELECT REGISTER (CONTINUED)

- bit 6-4 DS2<2:0>: Data Selection MUX 2 Signal Selection bits For CLC1: 111 = SCCP5 OCMP compare match event 110 = SCCP4 OCMP compare match event 101 = SCCP4 OCM4 output 100 = UART1 RX in 011 = SPI1 SDO1 out 010 = CMP2 out 001 = CLC1 out 000 = CLCINA I/O pin For CLC2: 111 = SCCP5 OCMP compare match event 110 = SCCP4 OCMP compare match event 101 = SCCP4 OCM4 output 100 = UART2 RX in 011 = SPI2 SDO2 out 010 = CMP2 out 001 = CLC2 out 000 = CLCINA I/O pin For CLC3: 111 = SCCP7 OCMP compare match event 110 = SCCP6 OCMP compare match event 101 = SCCP6 OCM6A output 100 = UART3 RX in 011 = SPI3 SDO3 out 010 = CMP2 out 001 = CLC3 out 000 = CLCINA I/O pin For CLC4: 111 = SCCP7 OCMP compare match event 110 = SCCP6 OCMP compare match event 101 = SCCP6 OCM2A output 100 = Reserved 011 = Reserved

- 010 = CMP2 out

- 001 = CLC4 out

- 000 = CLCINA I/O pin

- bit 3 Unimplemented: Read as '0'

## 26.9 Configuration Word Registers

## TABLE 26-3: CONFIGURATION WORDS SUMMARY

| ess                         |                  |           |                |              |        |         |       |            |       | Bits    |        |         |         |        |         |           |          |        |

|-----------------------------|------------------|-----------|----------------|--------------|--------|---------|-------|------------|-------|---------|--------|---------|---------|--------|---------|-----------|----------|--------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31\15          | 30/14        | 29/13  | 28/12   | 27/11 | 26/10      | 25/9  | 24/8    | 23/7   | 22/6    | 21/5    | 20/4   | 19/3    | 18/2      | 17/1     | 16/0   |

| 17C0                        | RESERVED         | 31:16     | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 1700                        | RESERVED         | 15:0      | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 17C4                        | FDEVOPT          | 31:16     |                | USERID<15:0> |        |         |       |            |       |         |        |         |         |        |         |           |          |        |

| T/C4 FDEVOF                 | FDEVOPT          | 15:0      | <b>FVBUSIO</b> | FUSBIDIO     | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | ALTI2C | SOSCHP  | r-1       | r-1      | r-1    |

| 17C8                        | FICD             | 31:16     | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 1700                        | FICD             | 15:0      | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | ICS    | <1:0>   | JTAGEN    | r-1      | r-1    |

| 1700                        | FPOR             | 31:16     | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 17CC                        | FPOR             | 15:0      | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | LPBOREN | RETVR     | BOREN    | l<1:0> |

| 17D0                        | FWDT             | 31:16     | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 1700                        | FWDI             | 15:0      | FWDTEN         | RCLKSEI      | _<1:0> |         | R۱    | VDTPS<4:0> |       |         | WINDIS | FWDTWIN | SZ<1:0> |        | SWD     | DTPS<4:0> |          |        |

| 17D4                        | FOSCSEL          | 31:16     | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 17D4                        | FUSCSEL          | 15:0      | FCKSN          | l<1:0>       | r-1    | SOSCSEL | r-1   | OSCIOFNC   | POSCM | OD<1:0> | IESO   | SOSCEN  | r-1     | PLLSRC | r-1     | FN        | IOSC<2:0 | >      |

| 4700                        | 5050             | 31:16     | CP             | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 17D8                        | FSEC             | 15:0      | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 4700                        |                  | 31:16     | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 17DC                        | RESERVED         | 15:0      | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 4750                        |                  | 31:16     | r-0            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 17E0                        | RESERVED         | 15:0      | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 4754                        |                  | 31:16     | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

| 17E4                        | RESERVED         | 15:0      | r-1            | r-1          | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1       | r-1      | r-1    |

Legend: r-0 = Reserved bit, must be programmed as '0'; r-1 = Reserved bit, must be programmed as '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0            | R/W-0            |  |  |  |

| 31:24        | _                 | -                 | _                 | _                 | BMXERRDIS         | _                 | - BMXARB<1:0>    |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | EXECADDR<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | -                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-P             | U-0               | r-1              | r-1              |  |  |  |

| 7:0          | _                 |                   | _                 | _                 | JTAGEN            |                   | _                | _                |  |  |  |

#### REGISTER 26-7: CFGCON: CONFIGURATION CONTROL REGISTER

| Legend:           | r = Reserved bit |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

- bit 31-28 Unimplemented: Read as '0'

- bit 27 BMXERRDIS: Bus Matrix (BMX) Exception Error Disable bit 1 = Disables BMX error exception generation<sup>(1)</sup> 0 = Enables BMX error exception generation

- bit 26 **Unimplemented:** Read as '0'

- bit 25-24 BMXARB<1:0>: Bus Matrix Arbitration Mode Select bits

- 11 = Reserved

- 10 = Mode 2 Round Robin

- 01 = Mode 1 Fixed with CPU as the lowest priority

- 00 = Mode 0 Fixed with CPU as the highest priority

#### bit 23-16 EXECADDR<7:0>: RAM Program Space Start Address bits

- 11111111 = RAM program space starts at the 255-Kbyte boundary (from 0xA003FC00)

- .

00000010 = RAM program space starts at 2-Kbyte boundary (from 0xA0000800) 00000001 = RAM program space starts at 1-Kbyte boundary (from 0xA0000400) 00000000 = All data RAM is allocated to program space (from 0xA0000000)

- bit 15-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Enable bit

- 1 = Enables 4-wire JTAG

- 0 = Disables 4-wire JTAG

- bit 2 Unimplemented: Read as '0'

- bit 1-0 Reserved: Maintain as '1'

- **Note 1:** An exception is not generated when an unimplemented address is accessed. The returned value on a read operation of unimplemented memory is 0x00000000.

## TABLE 26-6: BAND GAP REGISTER MAP

| ess                       |                      | ۵         |       | Bits  |       |       |       |       |      |      |      |      |      | s    |      |        |        |      |           |

|---------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|--------|--------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2   | 17/1   | 16/0 | All Reset |

| 2200                      | ANCFG <sup>(1)</sup> | 31:16     | —     | _     | —     | -     | _     | _     | -    | _    |      | —    | _    |      | -    | _      | _      | _    | 0000      |

| 2300                      | ANCEG 7              | 15:0      | _     | _     | _     |       |       | _     |      | _    |      | -    |      |      |      | VBGADC | VBGCMP |      | 0000      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

## 28.11 Demonstration/Development Boards, Evaluation Kits and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 28.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

## 29.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC32MM0256GPM064 family AC characteristics and timing parameters.

### TABLE 29-16: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)          |

|--------------------|--------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$                   |

|                    | Operating voltage VDD range as described in Section 29.1 "DC Characteristics". |

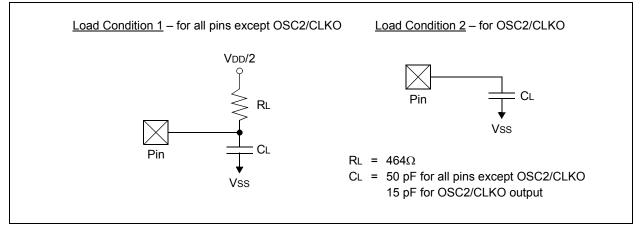

### FIGURE 29-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 29-17: CAPACITIVE LOADING CONDITIONS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                              |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|-------------------------------------------------------------------------|

| DO50         | Cosco  | OSC2/CLKO Pin         | _   | —                  | TBD | •     | In XT and HS modes when<br>external clock is used to drive<br>OSC1/CLKI |

| DO56         | Сю     | All I/O Pins and OSC2 | —   | —                  | TBD | pF    | EC mode                                                                 |

| DO58         | Св     | SCLx, SDAx            | _   | _                  | TBD | pF    | In I <sup>2</sup> C mode                                                |

**Legend:** TBD = To Be Determined

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

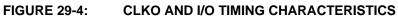

## TABLE 29-22: CLKO AND I/O TIMING REQUIREMENTS

| AC CHA       | ARACTER | ISTICS                               |     | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |     |       |            |  |  |  |

|--------------|---------|--------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--|--|--|

| Param<br>No. | Symbol  | Characteristic                       | Min | Typ <sup>(1)</sup>                                                                                                                              | Мах | Units | Conditions |  |  |  |

| DO31         | TIOR    | Port Output Rise Time                | —   | 10                                                                                                                                              | 25  | ns    |            |  |  |  |

| DO32         | TIOF    | Port Output Fall Time                | _   | 10                                                                                                                                              | 25  | ns    |            |  |  |  |

| DI35         | TINP    | INTx Pin High or Low<br>Time (input) | 1   | —                                                                                                                                               | —   | Тсү   |            |  |  |  |

| DI40         | Trbp    | CNx High or Low Time (input)         | 1   | _                                                                                                                                               | _   | Тсү   |            |  |  |  |

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated.

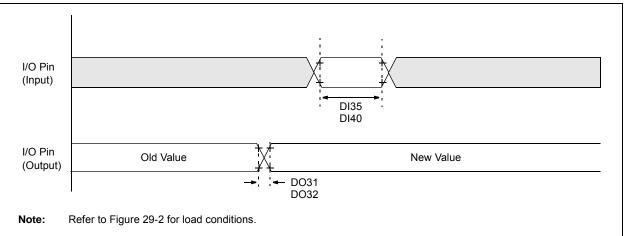

## FIGURE 29-10: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 29-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA       | RACTERIS             | TICS                                         |        | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                    |  |  |  |  |

|--------------|----------------------|----------------------------------------------|--------|-------------------------------------------------------|------|-------|--------------------|--|--|--|--|

| Param<br>No. | Symbol               | Characteristics <sup>(1)</sup>               | Min.   | Тур. <sup>(2)</sup>                                   | Max. | Units | Conditions         |  |  |  |  |

| SP10         | TscL                 | SCKx Output Low Time <sup>(3)</sup>          | Tsck/2 | —                                                     | _    | ns    |                    |  |  |  |  |

| SP11         | TscH                 | SCKx Output High Time <sup>(3)</sup>         | Tsck/2 |                                                       | _    | ns    |                    |  |  |  |  |

| SP20         | TscF                 | SCKx Output Fall Time <sup>(4)</sup>         |        |                                                       | _    | ns    | See Parameter DO32 |  |  |  |  |

| SP21         | TscR                 | SCKx Output Rise Time <sup>(4)</sup>         | _      | _                                                     | _    | ns    | See Parameter DO31 |  |  |  |  |

| SP30         | TDOF                 | SDOx Data Output Fall<br>Time <sup>(4)</sup> | —      | —                                                     | _    | ns    | See Parameter DO32 |  |  |  |  |

| SP31         | TDOR                 | SDOx Data Output Rise<br>Time <sup>(4)</sup> | —      | —                                                     | _    | ns    | See Parameter DO31 |  |  |  |  |

| SP35         | TscH2doV,            | SDOx Data Output Valid                       | _      |                                                       | 7    | ns    | VDD > 2.0V         |  |  |  |  |

|              | TscL2DoV             | after SCKx Edge                              | _      |                                                       | 10   | ns    | VDD < 2.0V         |  |  |  |  |

| SP36         | TDOV2sc,<br>TDOV2scL | SDOx Data Output Setup<br>to First SCKx Edge | 7      | —                                                     | _    | ns    |                    |  |  |  |  |

| SP40         | TDIV2scH,            | Setup Time of SDIx Data                      | 7      |                                                       | _    | ns    | VDD > 2.0V         |  |  |  |  |

|              | TDIV2scL             | Input to SCKx Edge                           | 10     | _                                                     | _    | ns    | VDD < 2.0V         |  |  |  |  |

| SP41         | TscH2DIL,            | Hold Time of SDIx Data                       | 7      |                                                       | _    | ns    | VDD > 2.0V         |  |  |  |  |

|              | TscL2DIL             | Input to SCKx Edge                           | 10     |                                                       | _    | ns    | VDD < 2.0V         |  |  |  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in the "Typ." column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 10 pF load on all SPIx pins.

## 28-Lead Plastic Quad Flat, No Lead Package (ML) - 6x6 mm Body [QFN] With 0.55 mm Terminal Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                         | Units  | М    | ILLIMETERS |      |  |  |  |

|-------------------------|--------|------|------------|------|--|--|--|

| Dimensior               | Limits | MIN  | NOM        | MAX  |  |  |  |

| Number of Pins          | Ν      |      | 28         |      |  |  |  |

| Pitch                   | е      |      | 0.65 BSC   |      |  |  |  |

| Overall Height          | Α      | 0.80 | 0.90       | 1.00 |  |  |  |

| Standoff                | A1     | 0.00 | 0.02       | 0.05 |  |  |  |

| Terminal Thickness      | A3     |      | 0.20 REF   |      |  |  |  |

| Overall Width           | E      |      | 6.00 BSC   |      |  |  |  |

| Exposed Pad Width       | E2     | 3.65 | 3.70       | 4.20 |  |  |  |

| Overall Length          | D      |      | 6.00 BSC   |      |  |  |  |

| Exposed Pad Length      | D2     | 3.65 | 3.70       | 4.20 |  |  |  |

| Terminal Width          | b      | 0.23 | 0.30       | 0.35 |  |  |  |

| Terminal Length         | L      | 0.50 | 0.55       | 0.70 |  |  |  |

| Terminal-to-Exposed Pad | K      | 0.20 | -          | -    |  |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-105C Sheet 2 of 2

## THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- **Product Support** Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Micro-chip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

## **CUSTOMER SUPPORT**

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support