Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 52                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 20x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0128gpm064-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                | 5521411410             | Pin Nu        |                |                        |                        |             |                |                                             |

|----------|----------------|------------------------|---------------|----------------|------------------------|------------------------|-------------|----------------|---------------------------------------------|

| Pin Name | 28-Pin<br>SSOP | 28-Pin<br>QFN/<br>UQFN | 36-Pin<br>QFN | 40-Pin<br>UQFN | 48-Pin<br>QFN/<br>TQFP | 64-Pin<br>QFN/<br>TQFP | Pin<br>Type | Buffer<br>Type | Description                                 |

| AN0      | 2              | 27                     | 33            | 36             | 21                     | 11                     | I           | ANA            | Analog-to-Digital Converter input channels  |

| AN1      | 3              | 28                     | 34            | 37             | 22                     | 12                     | I           | ANA            |                                             |

| AN2      | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            |                                             |

| AN3      | 5              | 2                      | 36            | 39             | 24                     | 14                     | Ι           | ANA            |                                             |

| AN4      | 6              | 3                      | 1             | 1              | 25                     | 15                     | Ι           | ANA            |                                             |

| AN5      | 9              | 6                      | 7             | 7              | 32                     | 25                     | I           | ANA            |                                             |

| AN6      | 10             | 7                      | 8             | 8              | 33                     | 26                     | I           | ANA            |                                             |

| AN7      | 11             | 8                      | 9             | 9              | 35                     | 28                     | I           | ANA            |                                             |

| AN8      | 24             | 21                     | 27            | 30             | 12                     | 63                     | I           | ANA            | -                                           |

| AN9      | 25             | 22                     | 28            | 31             | 15                     | 2                      | I           | ANA            | -                                           |

| AN10     | 26             | 23                     | 29            | 32             | 16                     | 3                      | I           | ANA            |                                             |

| AN11     | 7              | 4                      | 2             | 2              | 26                     | 16                     | I           | ANA            | -                                           |

| AN12     |                | —                      | 3             | 3              | 27                     | 19                     | I           | ANA            | -                                           |

| AN13     |                | —                      | 4             | 4              | 28                     | 20                     | I           | ANA            | -                                           |

| AN14     | —              | —                      | 20            | 21             | 4                      | 52                     | I           | ANA            |                                             |

| AN15     | —              | —                      | —             | —              | 41                     | 37                     | I           | ANA            |                                             |

| AN16     |                | —                      | _             | —              | _                      | 6                      | I           | ANA            |                                             |

| AN17     | —              | —                      | —             | —              | —                      | 7                      | I           | ANA            |                                             |

| AN18     | —              | —                      | —             | —              | —                      | 8                      | I           | ANA            |                                             |

| AN19     | —              | —                      | —             | —              | —                      | 10                     | I           | ANA            |                                             |

| AVdd     | 28             | 25                     | 31            | 34             | 18                     | 5                      | Р           | —              | Analog modules power supply                 |

| AVss     | 27             | 24                     | 30            | 33             | 17                     | 4                      | Р           | —              | Analog modules ground                       |

| C1INA    | 7              | 4                      | 2             | 2              | 26                     | 16                     | I           | ANA            | Comparator 1 Input A                        |

| C1INB    | 6              | 3                      | 1             | 1              | 25                     | 15                     | I           | ANA            | Comparator 1 Input B                        |

| C1INC    | 5              | 2                      | 36            | 39             | 24                     | 14                     | I           | ANA            | Comparator 1 Input C                        |

| C1IND    | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            | Comparator 1 Input D                        |

| C2INA    | 5              | 2                      | 36            | 39             | 24                     | 14                     | I           | ANA            | Comparator 2 Input A                        |

| C2INB    | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            | Comparator 2 Input B                        |

| C2INC    |                | —                      | 20            | 21             | 4                      | 52                     | I           | ANA            | Comparator 2 Input C                        |

| C2IND    |                | —                      | 3             | 3              | 27                     | 19                     | I           | ANA            | Comparator 2 Input D                        |

| C3INA    | 26             | 23                     | 29            | 32             | 16                     | 3                      | I           | ANA            | Comparator 3 Input A                        |

| C3INB    | 25             | 22                     | 28            | 31             | 15                     | 2                      | I           | ANA            | Comparator 3 Input B                        |

| C3INC    | 4              | 1                      | 35            | 38             | 23                     | 13                     | I           | ANA            | Comparator 3 Input C                        |

| C3IND    | 10             | 7                      | 8             | 8              | 33                     | 26                     | I           | ANA            | Comparator 3 Input D                        |

| CLKI     | 9              | 6                      | 7             | 7              | 32                     | 25                     | I           | ST             | External Clock source input (EC mode)       |

| CLKO     | 10             | 7                      | 8             | 8              | 33                     | 26                     | 0           | DIG            | System clock output                         |

| CVREF    | 25             | 22                     | 28            | 31             | 15                     | 2                      | 0           | ANA            | Comparator voltage reference output         |

| CVREF+   | 2              | 27                     | 33            | 36             | 21                     | 11                     | I           | ANA            | Positive comparator voltage reference input |

| D+       | 22             | 19                     | 25            | 28             | 10                     | 61                     | I/O         |                | USB transceiver differential plus line      |

| D-       | 21             | 18                     | 24            | 27             | 9                      | 60                     | I/O         |                | USB transceiver differential minus line     |

| FSYNC1   | 26             | 23                     | 29            | 32             | 16                     | 32                     | I/O         | ST/DIG         | SPI1 frame signal input or output           |

| FSYNC3   | 14             | 11                     | 15            | 15             | 45                     | 22                     | I/O         | ST/DIG         | SPI3 frame signal input or output           |

#### TABLE 1-1: PIC32MM0256GPM064 FAMILY PINOUT DESCRIPTION

**Legend:** ST = Schmitt Trigger input buffer

DIG = Digital input/output

P = Power

I2C = I<sup>2</sup>C/SMBus input buffer

ANA = Analog level input/output

NOTES:

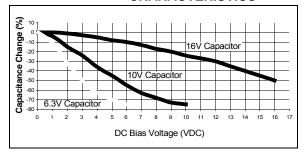

# 2.4.1 CONSIDERATIONS FOR CERAMIC CAPACITORS

In recent years, large value, low-voltage, surface-mount ceramic capacitors have become very cost effective in sizes up to a few tens of microfarad. The low-ESR, small physical size and other properties make ceramic capacitors very attractive in many types of applications.

Ceramic capacitors are suitable for use with the internal voltage regulator of this microcontroller. However, some care is needed in selecting the capacitor to ensure that it maintains sufficient capacitance over the intended operating range of the application.

Typical low-cost, 10  $\mu$ F ceramic capacitors are available in X5R, X7R and Y5V dielectric ratings (other types are also available, but are less common). The initial tolerance specifications for these types of capacitors are often specified as ±10% to ±20% (X5R and X7R) or -20%/+80% (Y5V). However, the effective capacitance that these capacitors provide in an application circuit will also vary based on additional factors, such as the applied DC bias voltage and the temperature. The total in-circuit tolerance is, therefore, much wider than the initial tolerance specification.

The X5R and X7R capacitors typically exhibit satisfactory temperature stability (ex:  $\pm 15\%$  over a wide temperature range, but consult the manufacturer's data sheets for exact specifications). However, Y5V capacitors typically have extreme temperature tolerance specifications of  $\pm 22\%$ . Due to the extreme temperature tolerance, a 10  $\mu$ F nominal rated Y5V type capacitor may not deliver enough total capacitance to meet minimum internal voltage regulator stability and transient response requirements. Therefore, Y5V capacitors are not recommended for use with the internal regulator.

In addition to temperature tolerance, the effective capacitance of large value ceramic capacitors can vary substantially, based on the amount of DC voltage applied to the capacitor. This effect can be very significant, but is often overlooked or is not always documented.

Typical DC bias voltage vs. capacitance graph for X7R type capacitors is shown in Figure 2-4.

When selecting a ceramic capacitor to be used with the internal voltage regulator, it is suggested to select a high-voltage rating, so that the operating voltage is a small percentage of the maximum rated capacitor voltage. The minimum DC rating for the ceramic capacitor on VCAP is 16V. Suggested capacitors are shown in Table 2-1.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin Input Voltage High (VIH) and Input Voltage Low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup> In-Circuit Emulator.

For more information on MPLAB® ICD 3 and REAL ICE connection requirements, refer to the following documents that are available from the Microchip web site.

- *"Using MPLAB<sup>®</sup> ICD 3"* (poster) (DS51765)

- "Development Tools Design Advisory" (DS51764)

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide" (DS51616)

- "Using MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator" (poster) (DS51749)

## TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)

| _                           | LL /-J.                         |                       |       |       |        |               |              | ,       |         | Bits   |       |      |      |                  |                 |        |         |         |            |

|-----------------------------|---------------------------------|-----------------------|-------|-------|--------|---------------|--------------|---------|---------|--------|-------|------|------|------------------|-----------------|--------|---------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range             | 31/15 | 30/14 | 29/13  | 28/12         | 27/11        | 26/10   | 25/9    | 24/8   | 23/7  | 22/6 | 21/5 | 20/4             | 19/3            | 18/2   | 17/1    | 16/0    | All Resets |

| ž                           |                                 | 31:16                 | _     | _     | _      |               | T3IP<2:0>    |         | T3IS<   | 1.0>   | _     | _    | _    |                  | T2IP<2:0>       |        | T2IS•   | <1.0>   | 0000       |

| F100                        | IPC4                            | 15:0                  |       | _     |        |               | T1IP<2:0>    |         | T1IS<   |        | _     | _    | _    |                  | _               | _      | 1210    |         | 0000       |

|                             |                                 | 31:16                 |       |       |        |               | CMP1IP<2:02  | >       | CMP1IS  |        |       |      | _    |                  |                 |        |         |         | 0000       |

| F110                        | IPC5                            | 15:0                  | _     |       |        | _             | _            | _       | _       | _      | _     | _    | _    |                  | _               |        | _       |         | 0000       |

|                             |                                 | 31:16                 | _     |       | _      | _             | _            | _       | _       | _      | _     | _    | _    | _                | _               | _      |         | _       | 0000       |

| F120                        | IPC6                            | 15:0                  | _     | _     | _      |               | CMP3IP<2:0   |         | CMP3IS  |        |       |      | _    |                  | I<br>CMP2IP<2:0 |        | CMP2I   |         | 0000       |

|                             |                                 | 31:16                 | _     |       |        | _             |              | _       | _       |        | _     |      | _    |                  |                 |        |         | _       | 0000       |

| F130                        | IPC7                            | 15:0                  | _     | _     |        |               | USBIP<2:0>   |         | USBIS   | <1.0>  |       |      |      |                  | _               | _      | _       |         | 0000       |

|                             |                                 | 31:16                 | _     | _     | _      | _             |              | _       | _       |        | _     | _    | _    | _                | _               | _      | _       |         | 0000       |

| F140                        | IPC8                            | 15:0                  | _     |       |        |               | AD1IP<2:0>   |         | AD1IS   | <1.0>  | _     |      | _    |                  | I<br>RTCCIP<2:0 |        | RTCCI   | S<1·0>  | 0000       |

|                             |                                 | 31:16                 | _     | _     | _      |               | CLC3IP<2:0   |         | CLC3IS  |        | _     | _    | _    |                  | CLC2IP<2:0      |        | CLC2    |         | 0000       |

| F150                        | IPC9                            | IPC9 15:0 CLC1IP<2:0> |       |       | CLC1IS |               |              |         |         |        | LVDIS |      | 0000 |                  |                 |        |         |         |            |

|                             |                                 |                       | _     |       | _      | SPI1RXIP<2:0> |              | SPI1RXI |         | _      | _     | _    |      | PI1TXIP<2:0      |                 | SPI1TX |         | 0000    |            |

| F160                        | IPC10                           | 31:16<br>15:0         | _     | _     | _      |               | SPI1EIP<2:0  |         | SPI1EIS |        | _     | _    | _    |                  | CLC4IP<2:0      |        | CLC4    |         | 0000       |

|                             |                                 | 31:16                 | _     | _     | _      |               | SPI3EIP<2:0  |         | SPI3EIS |        | _     | _    | _    |                  | PI2RXIP<2:0     |        | SPI2RX  |         | 0000       |

| F170                        | IPC11                           | 15:0                  | _     | _     | _      |               | SPI2TXIP<2:0 | )>      | SPI2TXI | S<1:0> | _     | _    | _    | S                | SPI2EIP<2:0     | >      | SPI2EI  | S<1:0>  | 0000       |

|                             |                                 | 31:16                 | _     | _     | _      | _             | _            | _       | _       |        | _     | _    | _    | _                | _               | _      | _       | _       | 0000       |

| F180                        | IPC12                           | 15:0                  | _     | _     | _      |               | SPI3RXIP<2:0 | )>      | SPI3RXI | S<1:0> | _     | _    | _    | SPI3TXIP<2:0> SP |                 | SPI3TX | IS<1:0> | 0000    |            |

|                             |                                 | 31:16                 | _     | _     | _      |               | U1EIP<2:0>   |         | U1EIS-  | <1:0>  | _     | _    | _    | ι                | J1TXIP<2:0      | >      | U1TXI   | S<1:0>  | 0000       |

| F190                        | IPC13                           | 15:0                  | _     | _     | _      |               | U1RXIP<2:0   | >       | U1RXIS  | s<1:0> | _     | _    | _    | _                | _               | _      | _       | _       | 0000       |

|                             |                                 | 31:16                 |       | _     | _      |               | U3RXIP<2:0   | >       | U3RXIS  | <1:0>  | —     | —    | _    |                  | U2EIP<2:0>      |        | U2EIS   | <1:0>   | 0000       |

| F1A0                        | IPC14                           | 15:0                  | _     | _     | -      |               | U2TXIP<2:0   | >       | U2TXIS  | <1:0>  | —     | —    | _    | ι                | J2RXIP<2:0      | >      | U2RXI   | S<1:0>  | 0000       |

| 5400                        | 10045                           | 31:16                 | _     | _     | _      | _             |              | —       | _       | _      | —     | —    | —    | _                | —               | —      | —       | _       | 0000       |

| F1B0                        | IPC15                           | 15:0                  | _     | _     | _      |               | U3EIP<2:0>   |         | U3EIS-  | <1:0>  | —     | —    | —    | ι                | J3TXIP<2:0      | >      | U3TXI   | S<1:0>  | 0000       |

| F100                        | IPC16                           | 31:16                 | _     | _     | _      |               | I2C1BCIP<2:0 | )>      | I2C1BCI | S<1:0> | —     | —    | —    | 12               | 2C1MIP<2:0      | >      | I2C1MI  | S<1:0>  | 0000       |

| F1C0                        | IPC16                           | 15:0                  | _     | _     | _      |               | I2C1SIP<2:0  | >       | I2C1SIS | 6<1:0> | —     | —    | _    | _                | _               | —      | _       | —       | 0000       |

| 5400                        | 10017                           | 31:16                 | _     | _     | _      |               | I2C3SIP<2:0  | >       | I2C3SIS | 6<1:0> | —     | —    | —    | 12               | C2BCIP<2:0      | )>     | I2C2BC  | IS<1:0> | 0000       |

| F1D0                        | IPC17                           | 15:0                  | _     | _     | _      |               | I2C2MIP<2:0  | >       | I2C2MIS | 6<1:0> | —     | —    | —    | Ľ                | 2C2SIP<2:0      | >      | I2C2SI  | S<1:0>  | 0000       |

| F1F0                        | IPC18                           | 31:16                 | _     | _     | _      |               | CCT1IP<2:0   | >       | CCT1IS  | i<1:0> | —     | —    | —    | C                | CCP1IP<2:0      | >      | CCP1    | S<1:0>  | 0000       |

| F1E0                        | IPUT8                           | 15:0                  |       | _     | _      |               | 12C3BCIP<2:0 | )>      | I2C3BCI | S<1:0> |       |      | _    | 12               | 2C3MIP<2:0      | >      | I2C3MI  | S<1:0>  | 0000       |

| F1F0                        | IPC19                           | 31:16                 | _     | _     | _      |               | CCT3IP<2:0   | >       | CCT3IS  | i<1:0> | _     | _    | —    | C                | CCP3IP<2:0      | >      | CCP3    | S<1:0>  | 0000       |

| FIFU                        | IPC 19                          | 15:0                  | _     |       | _      |               | CCT2IP<2:0   | >       | CCT2IS  | s<1:0> | —     | —    | _    | (                | CCP2IP<2:0      | >      | CCP2    | S<1:0>  | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | _                 | _                 | _                 |                   | IP3<2:0>          | IS3<1:0>          |                  |                  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | _                 | _                 | _                 | IP2<2:0>          |                   |                   | IS2<1:0>         |                  |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | _                 | _                 | _                 |                   | IP1<2:0>          |                   | IS1<             | IS1<1:0>         |  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 | IP0<2:0>          |                   |                   | IS0<1:0>         |                  |  |  |

### REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER x

#### Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: | Interrupt | Priority 3 bits |

|-----------|-----------|-----------|-----------------|

- - 00 = Interrupt subpriority is 0

## bit 23-21 Unimplemented: Read as '0'

- bit 20-18 IP2<2:0>: Interrupt Priority 2 bits

- 111 = Interrupt priority is 7

- •

- •

- 010 = Interrupt priority is 2 001 = Interrupt priority is 1

- 000 = Interrupt is disabled

- bit 17-16 **IS2<1:0>:** Interrupt Subpriority 2 bits

- 11 = Interrupt subpriority is 3

- 10 = Interrupt subpriority is 2

- 01 = Interrupt subpriority is 1

- 00 = Interrupt subpriority is 0

- bit 15-13 Unimplemented: Read as '0'

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-3 for the exact bit definitions.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit. In addition to the CNSTATx register, the CNFx register is implemented for each port. This register contains flags for Change Notification events. These flags are set if the valid transition edge, selected in the CNEN0x and CNEN1x registers, is detected. CNFx stores the occurrence of the event. CNFx bits must be cleared in software to get the next Change Notification interrupt. The CN interrupt is generated only for the I/Os configured as inputs (corresponding TRISx bits must be set).

## 10.8 Pin Pull-up and Pull-Down

Each I/O pin also has a weak pull-up and a weak pulldown connected to it. The pull-ups act as a current source, or sink source, connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

## 10.9 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient work arounds in application code, or a complete redesign, may be the only option.

PPS configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

### 10.9.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation, "RPn", in their full pin designation, where "RP" designates a Remappable Peripheral and "n" is the remappable port number.

### 10.9.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digital only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (MCCP, SCCP) and others.

In comparison, some digital only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and nonremappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/Os and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

## 10.9.3 CONTROLLING PPS

PPS features are controlled through two sets of SFRs: one to map peripheral inputs and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

| TABLE 10-0. |          |                |             |          |                |  |  |  |  |  |  |

|-------------|----------|----------------|-------------|----------|----------------|--|--|--|--|--|--|

| Value       | RPn Pins | Pin Assignment | Value       | RPn Pins | Pin Assignment |  |  |  |  |  |  |

| 00001       | RP1      | RA0 Pin        | 01110       | RP14     | RB9 Pin        |  |  |  |  |  |  |

| 00010       | RP2      | RA1 Pin        | 01111       | RP15     | RB13 Pin       |  |  |  |  |  |  |

| 00011       | RP3      | RA2 Pin        | 10000       | RP16     | RB14 Pin       |  |  |  |  |  |  |

| 00100       | RP4      | RA3 Pin        | 10001       | RP17     | RB15 Pin       |  |  |  |  |  |  |

| 00101       | RP5      | RA4 Pin        | 10010       | RP18     | RC9 Pin        |  |  |  |  |  |  |

| 00110       | RP6      | RB0 Pin        | 10011       | RP19     | RC2 Pin        |  |  |  |  |  |  |

| 00111       | RP7      | RB1 Pin        | 10100       | RP20     | RC7 Pin        |  |  |  |  |  |  |

| 01000       | RP8      | RB2 Pin        | 10101       | RP21     | RA7 Pin        |  |  |  |  |  |  |

| 01001       | RP9      | RB3 Pin        | 10110       | RP22     | RA10 Pin       |  |  |  |  |  |  |

| 01010       | RP10     | RB4 Pin        | 10111       | RP23     | RC6 Pin        |  |  |  |  |  |  |

| 01011       | RP11     | RB5 Pin        | 11000       | RP24     | RA9 Pin        |  |  |  |  |  |  |

| 01100       | RP12     | RB7 Pin        | 11001-11111 | Re       | served         |  |  |  |  |  |  |

| 01101       | RP13     | RB8 Pin        |             |          |                |  |  |  |  |  |  |

# TABLE 10-3: REMAPPABLE INPUT SOURCES PIN ASSIGNMENTS<sup>(1)</sup>

Note 1: All RPx pins are not available on all packages.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0                 | R/W-0                 | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | OPSSRC <sup>(1)</sup> | RTRGEN <sup>(2)</sup> | —                 | —                 | OPS<3:0> <sup>(3)</sup> |                   |                  |                  |  |

| 00.40        | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | TRIGEN                | ONESHOT               | ALTSYNC           | SYNC<4:0>         |                         |                   |                  |                  |  |

| 45.0         | R/W-0                 | U-0                   | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | ON <sup>(1)</sup>     | —                     | SIDL              | CCPSLP            | TMRSYNC CLKSEL<2:0>     |                   |                  |                  |  |

| 7.0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | TMRPS<1:0>            |                       | T32               | CCSEL             | MOD<3:0>                |                   |                  |                  |  |

#### REGISTER 14-1: CCPxCON1: CAPTURE/COMPARE/PWMx CONTROL 1 REGISTER

#### Legend:

| 5                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31 OPSSRC: Output Postscaler Source Select b |

|--------------------------------------------------|

|--------------------------------------------------|

- 1 = Output postscaler scales the Special Event Trigger output events

- 0 = Output postscaler scales the timer interrupt events

- bit 30 RTRGEN: Retrigger Enable bit<sup>(2)</sup>

- 1 = Time base can be retriggered when CCPTRIG = 1

- 0 = Time base may not be retriggered when CCPTRIG = 1

- bit 29-28 Unimplemented: Read as '0'

- bit 27-24 **OPS<3:0>:** CCPx Interrupt Output Postscale Select bits<sup>(3)</sup>

- 1111 = Interrupt every 16th time base period match

- 1110 = Interrupt every 15th time base period match

- . . .

- 0100 = Interrupt every 5th time base period match

- 0011 = Interrupt every 4th time base period match or 4th input capture event

- 0010 = Interrupt every 3rd time base period match or 3rd input capture event

- 0001 = Interrupt every 2nd time base period match or 2nd input capture event

- 0000 = Interrupt after each time base period match or input capture event

- bit 23 TRIGEN: CCPx Triggered Enable bit

- 1 = Triggered operation of the timer is enabled

- 0 = Triggered operation of the timer is disabled

- bit 22 ONESHOT: One-Shot Mode Enable bit

- 1 = One-Shot Triggered mode is enabled; trigger duration is set by OSCNT<2:0>

- 0 = One-Shot Triggered mode is disabled

#### bit 21 ALTSYNC: CCPx Clock Select bit

- 1 = An alternate signal is used as the module synchronization output signal

- 0 = The module synchronization output signal is the Time Base Reset/rollover event

#### **Note 1:** This control bit has no function in Input Capture modes.

- 2: This control bit has no function when TRIGEN = 0.

- **3:** Values greater than '0011' will cause a FIFO buffer overflow in Input Capture mode.

## REGISTER 18-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Resets all Even/Odd Buffer Pointers to the Even buffer descriptor banks

- 0 = Even/Odd Buffer Pointers are not reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry are enabled

- 0 = USB module and supporting circuitry are disabled

SOFEN: SOF Enable bit(5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 18-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the Resume signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# PIC32MM0256GPM064 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ADRC              | EXTSAM            | _                 | SAMC<4:0>         |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | ADCS<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

## REGISTER 20-3: AD1CON3: ADC CONTROL REGISTER 3

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ADRC: ADC Conversion Clock Source (TSRC) bit

- 1 = Clock derived from the Fast RC (FRC) oscillator

- 0 = Clock derived from the Peripheral Bus Clock (PBCLK, 1:1 with SYSCLK)

#### bit 14 EXTSAM: Extended Sampling Time bit

- 1 = ADC is still sampling after SAMP bit = 0

- 0 = ADC stops sampling when SAMP bit = 0

- bit 13 Unimplemented: Read as '0'

- bit 12-8 SAMC<4:0>: Auto-Sample Time bits

11111 **= 31 T**AD

- •

- .

- 00001 = 1 TAD

00000 = 0 TAD (Not allowed)

# bit 7-0 ADCS<7:0>: ADC Conversion Clock Select bits

- 11111111 = 2 TSRC ADCS<7:0> = 510 TSRC = TAD

- •

- •

00000001 = 2 • TSRC • ADCS<7:0> = 2 • TSRC = TAD 00000000 = 1 • TSRC = TAD

Where TSRC is a period of clock selected by the ADRC bit (AD1CON3<15>).

## 21.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCON

- CLCxSEL

- CLCxGLS

The CLCx Control register (CLCxCON) is used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Source Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Select register (CLCxGLS) allows the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

## REGISTER 21-3: CLCxGLS: CLCx GATE LOGIC INPUT SELECT REGISTER (CONTINUED)

| bit 20   | G3D3N: Gate 3 Data Source 3 Negated Enable bit                                                                                                     |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 1 = The Data Source 3 inverted signal is enabled for Gate 3                                                                                        |

|          | 0 = The Data Source 3 inverted signal is disabled for Gate 3                                                                                       |

| bit 19   | G3D2T: Gate 3 Data Source 2 True Enable bit                                                                                                        |

|          | <ul> <li>1 = The Data Source 2 signal is enabled for Gate 3</li> <li>0 = The Data Source 2 signal is disabled for Gate 3</li> </ul>                |

| bit 18   | G3D2N: Gate 3 Data Source 2 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 2 inverted signal is enabled for Gate 3                                                                                        |

|          | 0 = The Data Source 2 inverted signal is disabled for Gate 3                                                                                       |

| bit 17   | G3D1T: Gate 3 Data Source 1 True Enable bit                                                                                                        |

|          | <ul> <li>1 = The Data Source 1 signal is enabled for Gate 3</li> <li>0 = The Data Source 1 signal is disabled for Gate 3</li> </ul>                |

| bit 16   | <b>G3D1N:</b> Gate 3 Data Source 1 Negated Enable bit                                                                                              |

| bit to   | 1 = The Data Source 1 inverted signal is enabled for Gate 3                                                                                        |

|          | 0 = The Data Source 1 inverted signal is disabled for Gate 3                                                                                       |

| bit 15   | G2D4T: Gate 2 Data Source 4 True Enable bit                                                                                                        |

|          | 1 = The Data Source 4 signal is enabled for Gate 2                                                                                                 |

| 1.11.4.4 | 0 = The Data Source 4 signal is disabled for Gate 2                                                                                                |

| bit 14   | <b>G2D4N:</b> Gate 2 Data Source 4 Negated Enable bit<br>1 = The Data Source 4 inverted signal is enabled for Gate 2                               |

|          | 0 = The Data Source 4 inverted signal is disabled for Gate 2                                                                                       |

| bit 13   | <b>G2D3T:</b> Gate 2 Data Source 3 True Enable bit                                                                                                 |

|          | 1 = The Data Source 3 signal is enabled for Gate 2                                                                                                 |

|          | 0 = The Data Source 3 signal is disabled for Gate 2                                                                                                |

| bit 12   | G2D3N: Gate 2 Data Source 3 Negated Enable bit                                                                                                     |

|          | <ul><li>1 = The Data Source 3 inverted signal is enabled for Gate 2</li><li>0 = The Data Source 3 inverted signal is disabled for Gate 2</li></ul> |

| bit 11   | <b>G2D2T:</b> Gate 2 Data Source 2 True Enable bit                                                                                                 |

|          | 1 = The Data Source 2 signal is enabled for Gate 2                                                                                                 |

|          | 0 = The Data Source 2 signal is disabled for Gate 2                                                                                                |

| bit 10   | G2D2N: Gate 2 Data Source 2 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 2 inverted signal is enabled for Gate 2                                                                                        |

| 1.11.0   | 0 = The Data Source 2 inverted signal is disabled for Gate 2                                                                                       |

| bit 9    | <b>G2D1T:</b> Gate 2 Data Source 1 True Enable bit                                                                                                 |

|          | <ul><li>1 = The Data Source 1 signal is enabled for Gate 2</li><li>0 = The Data Source 1 signal is disabled for Gate 2</li></ul>                   |

| bit 8    | G2D1N: Gate 2 Data Source 1 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 1 inverted signal is enabled for Gate 2                                                                                        |

|          | 0 = The Data Source 1 inverted signal is disabled for Gate 2                                                                                       |

| bit 7    | G1D4T: Gate 1 Data Source 4 True Enable bit                                                                                                        |

|          | <ul> <li>1 = The Data Source 4 signal is enabled for Gate 1</li> <li>0 = The Data Source 4 signal is disabled for Gate 1</li> </ul>                |

| bit 6    | G1D4N: Gate 1 Data Source 4 Negated Enable bit                                                                                                     |

|          | 1 = The Data Source 4 inverted signal is enabled for Gate 1                                                                                        |

|          | 0 = The Data Source 4 inverted signal is disabled for Gate 1                                                                                       |

| bit 5    | G1D3T: Gate 1 Data Source 3 True Enable bit                                                                                                        |

|          | <ul> <li>1 = The Data Source 3 signal is enabled for Gate 1</li> <li>0 = The Data Source 3 signal is disabled for Gate 1</li> </ul>                |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                 | —                 | —                 | _                 | —                |                  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 23:16        | _                 | —                 | —                 | —                 | —                 | C3EVT             | C2EVT            | C1EVT            |

| 45.0         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 15:8         | -                 | —                 | SIDL              | —                 | —                 | —                 | —                | CVREFSEL         |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |

| 7:0          | _                 | _                 | _                 |                   | _                 | C3OUT             | C2OUT            | C10UT            |

### REGISTER 22-1: CMSTAT: COMPARATOR MODULE STATUS REGISTER

| Legend: HC = Hardware Clearable bit |                  | HS = Hardware Settable bit              |  |  |  |

|-------------------------------------|------------------|-----------------------------------------|--|--|--|

| R = Readable bit                    | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |  |

| -n = Value at POR                   | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |  |

bit 31-19 Unimplemented: Read as '0'

| bit 18 | C3EVT: Comparator 3 Event Status bit (read-only)            |

|--------|-------------------------------------------------------------|

|        | Shows the current event status of Comparator 3 (CM3CON<9>). |

| bit 17 | C2EVT: Comparator 2 Event Status bit (read-only)            |

|        | Shows the current event status of Comparator 2 (CM2CON<9>). |

- bit 16 **C1EVT:** Comparator 1 Event Status bit (read-only) Shows the current event status of Comparator 1 (CM1CON<9>).

- bit 15-14 Unimplemented: Read as '0'

- bit 13 SIDL: Comparator Stop in Idle Mode bit

1 = Discontinues operation of all comparators when device enters Idle mode

0 = Continues operation of all enabled comparators in Idle mode

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **CVREFSEL:** Comparator Reference Voltage Select Enable bit 1 = External voltage reference from the CVREF+ pin is selected 0 = Internal band gap voltage reference is selected

- bit 7-3 **Unimplemented:** Read as '0'

- bit 2 **C3OUT:** Comparator 3 Output Status bit (read-only) Shows the current output of Comparator 3 (CM3CON<8>).

- bit 1 **C2OUT:** Comparator 2 Output Status bit (read-only) Shows the current output of Comparator 2 (CM2CON<8>).

- bit 0 **C1OUT:** Comparator 1 Output Status bit (read-only) Shows the current output of Comparator 1 (CM1CON<8>).

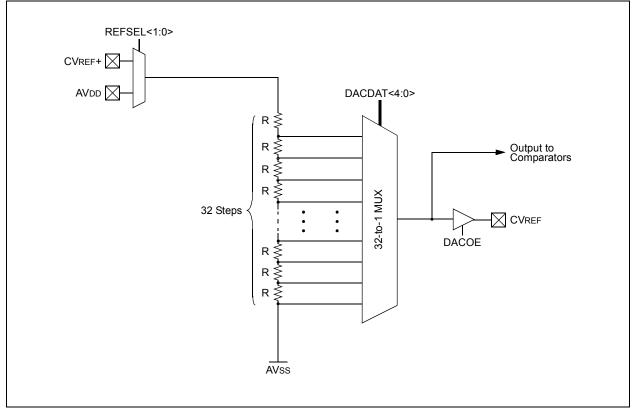

# 23.0 VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference" (DS61109) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM. The CVREF module is a 32-TAP DAC that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it may also be used independently from them.

The module's supply reference can be provided from either the device VDD/VSS or an external voltage reference pin. The CVREF output is available for the comparators and for pin output.

The voltage reference has the following features:

- 32 Output Levels are Available

- Internally Connected to Comparators to Conserve Device Pins

- · Output can be Connected to a Pin

A block diagram of the CVREF module is illustrated in Figure 23-1.

## FIGURE 23-1: VOLTAGE REFERENCE BLOCK DIAGRAM

# 27.0 INSTRUCTION SET

The PIC32MM0256GPM064 family instruction set complies with the MIPS<sup>®</sup> Release 3 instruction set architecture. Only microMIPS32<sup>™</sup> instructions are supported. The PIC32MM0256GPM064 family does not have the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

| Note: | Refer to the "MIPS® Architecture for |

|-------|--------------------------------------|

|       | Programmers Volume II-B: The         |

|       | microMIPS32™ Instruction Set" at     |

|       | www.imgtec.com for more information. |

# 29.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MM0256GPM064 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MM0256GPM064 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias40°C to +105°C<br>Storage temperature65°C to +150°C                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage on VDD with respect to Vss                                                                                                             |

| Voltage on any general purpose digital or analog pin (not 5.5V tolerant) with respect to Vss0.3V to (VDD + 0.3V)                               |

| Voltage on any general purpose digital or analog pin (5.5V tolerant) with respect to Vss:                                                      |

| When VDD = 0V:0.3V to +4.0V                                                                                                                    |

| When VDD $\geq 2.0V$ :                                                                                                                         |

| Voltage on AVDD with respect to VDD(VDD $- 0.3V$ ) to (lesser of: 4.0V or (VDD $+ 0.3V$ ))                                                     |

| Voltage on AVss with respect to Vss0.3V to +0.3V                                                                                               |

| Maximum current out of Vss pin                                                                                                                 |

| Maximum current into VDD pin <sup>(1)</sup>                                                                                                    |

| Maximum output current sunk by I/O pin 11 mA                                                                                                   |

| Maximum output current sourced by I/O pin                                                                                                      |

| Maximum output current sunk by I/O pin with increased current drive strength<br>(RA3, RA8, RA10, RB8, RB9, RB13, RB15, RC9, RC13 and RD0)      |

| Maximum output current sourced by I/O pin with increased current drive strength (RA3, RA8, RA10, RB8, RB9, RB13, RB15, RC9, RC13 and RD0)24 mA |

| Maximum current sunk by all ports                                                                                                              |

| Maximum current sourced by all ports <sup>(1)</sup>                                                                                            |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 29-1).

**NOTICE:** Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

t

# TABLE 29-5: IDLE CURRENT (IIDLE)<sup>(2)</sup>

| Parameter<br>No. | Typical <sup>(1)</sup> | Max | Units | Operating<br>Temperature | VDD  | Conditions       |  |  |

|------------------|------------------------|-----|-------|--------------------------|------|------------------|--|--|

| DC40             | .69                    | .8  | μA    | -40°C to +85°C           | 2.0V | Fsys = 1 MHz     |  |  |

|                  | .69                    | .8  | μΑ    | -40°C to +85°C           | 3.3V |                  |  |  |

| DC41             | .98                    | 1.7 | mA    | -40°C to +85°C           | 2.0V | Fsys = 8 MHz     |  |  |

|                  | .98                    | 1.7 | mA    | -40°C to +85°C           | 3.3V |                  |  |  |

| DC42             | 2.9                    | 3.7 | mA    | -40°C to +85°C           | 2.0V | Esys = 25 MHz    |  |  |

|                  | 2.9                    | 3.7 | mA    | -40°C to +85°C           | 3.3V | - FSTS - 25 MIHZ |  |  |

| DC44             | .36                    | .7  | μA    | -40°C to +85°C           | 2.0V | – Fsys = 32 kHz  |  |  |

|                  | .36                    | .7  | μA    | -40°C to +85°C           | 3.3V |                  |  |  |

Note 1: Parameters are for design guidance only and are not tested.

2: Base IIDLE current is measured with the core in Idle, the clock on and all modules turned off. OSC1 driven with external square wave from rail-to-rail (EC Clock Overshoot/Undershoot < 250 mV required). Peripheral Module Disable SFR registers are zeroed. All I/O pins are configured as inputs and pulled to Vss.</p>

# PIC32MM0256GPM064 FAMILY

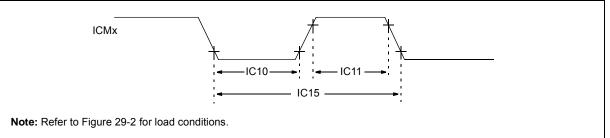

### FIGURE 29-6: MCCP AND SCCP INPUT CAPTURE MODE TIMING CHARACTERISTICS

#### TABLE 29-25: MCCP AND SCCP INPUT CAPTURE MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                 |      | ISTICS                         | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ |      |       |                                  |  |

|----------------------------------------------------|------|--------------------------------|---------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------|--|

| Param<br>No. Symbol Characteristics <sup>(1)</sup> |      | Characteristics <sup>(1)</sup> | Min.                                                                                                          | Max. | Units | Conditions                       |  |

| IC10                                               | TccL | ICMx Input Low Time            | [(12.5 ns or 1 TPBCLK)/N] + 25 ns                                                                             |      | ns    | Must also meet<br>Parameter IC15 |  |

| IC11                                               | ТссН | ICMx Input High Time           | [(12.5 ns or 1 TPBCLK)/N] + 25 ns                                                                             | _    | ns    | Must also meet<br>Parameter IC15 |  |

| IC15                                               | TCCP | ICMx Input Period              | [(25 ns or 2 TPBCLK)/N] + 50 ns                                                                               |      | ns    |                                  |  |

Note 1: These parameters are characterized but not tested in manufacturing.

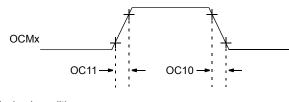

### FIGURE 29-7: MCCP AND SCCP OUTPUT COMPARE MODE TIMING CHARACTERISTICS

Note: Refer to Figure 29-2 for load conditions.

## TABLE 29-26: MCCP AND SCCP OUTPUT COMPARE MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS                                 |      |                       |         | <b>Operating (</b><br>g temperatur |       |            | .6V (unless otherwise stated) $T_A \le +85^{\circ}C$ |

|----------------------------------------------------|------|-----------------------|---------|------------------------------------|-------|------------|------------------------------------------------------|

| Param<br>No. Symbol Characteristics <sup>(1)</sup> |      | Min.                  | Typical | Max.                               | Units | Conditions |                                                      |

| OC10                                               | TccF | OCMx Output Fall Time | _       | _                                  | _     | ns         | See Parameter DO32                                   |

| OC11                                               | TccR | OCMx Output Rise Time | _       | —                                  | _     | ns         | See Parameter DO31                                   |

Note 1: These parameters are characterized but not tested in manufacturing.

## 30.1 Package Marking Information (Continued)

40-Lead UQFN (5x5x0.5 mm)

48-Lead UQFN (6x6 mm)

48-Lead TQFP (7x7x1.0 mm)

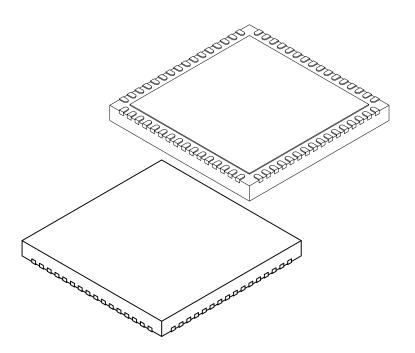

64-Lead QFN (9x9x0.9 mm)

64-Lead TQFP (10x10x1 mm)

Example

Example

## Example

## Example

## Example

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.70 x 7.70 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units |                |          |      |  |

|------------------------|-------|----------------|----------|------|--|

| Dimension              | MIN   | NOM            | MAX      |      |  |

| Number of Pins         |       | 64             |          |      |  |

| Pitch                  | е     |                | 0.50 BSC |      |  |

| Overall Height         | A     | 0.80           | 0.85     | 0.90 |  |

| Standoff               | A1    | 0.00           | 0.02     | 0.05 |  |

| Contact Thickness      | A3    | 0.20 REF       |          |      |  |

| Overall Width          | E     | 9.00 BSC       |          |      |  |

| Exposed Pad Width      | E2    | 7.60 7.70 7.80 |          |      |  |

| Overall Length         | D     | 9.00 BSC       |          |      |  |

| Exposed Pad Length     | D2    | 7.60           | 7.70     | 7.80 |  |

| Contact Width          | b     | 0.20 0.25 0.30 |          |      |  |

| Contact Length         | L     | 0.30           | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | К     | 0.20           |          |      |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-213B Sheet 2 of 2