#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

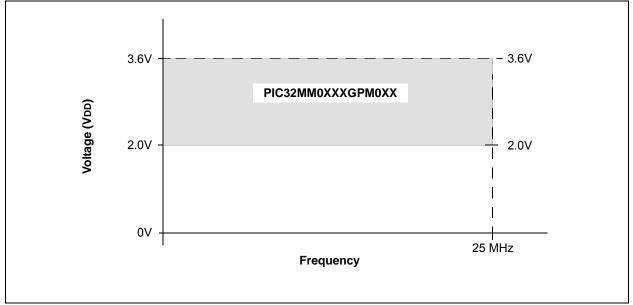

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 21                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 12x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                                   |

| Supplier Device Package    | 28-SSOP                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0256gpm028-i-ss |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.3 Power Management

The processor core offers a number of power management features, including low-power design, active power management and Power-Down modes of operation. The core is a static design that supports slowing or halting of the clocks, which reduces system power consumption during Idle periods.

The mechanism for invoking Power-Down mode is implemented through execution of the WAIT instruction, used to initiate Sleep or Idle. The majority of the power consumed by the processor core is in the clock tree and clocking registers. The PIC32MM family makes extensive use of local gated clocks to reduce this dynamic power consumption.

#### 3.4 EJTAG Debug Support

The microAptiv UC core has an Enhanced JTAG (EJTAG) interface for use in the software debug. In addition to the standard mode of operation, the microAptiv UC core provides a Debug mode that is entered after a debug exception (derived from a hard-ware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the microAptiv UC core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

#### 3.5 MIPS32<sup>®</sup> microAptiv<sup>™</sup> UC Core Configuration

Register 3-1 through Register 3-4 show the default configuration of the microAptiv UC core, which is included on PIC32MM0256GPM064 family devices.

#### TABLE 4-1: FIXED MODES ORDER OF PRIORITY

| Mode 1           | Mode 0           |  |  |  |  |

|------------------|------------------|--|--|--|--|

| CPU Lowest       | CPU Highest      |  |  |  |  |

| Highest Priority |                  |  |  |  |  |

| Flash Controller | Flash Controller |  |  |  |  |

| DMA              | CPU              |  |  |  |  |

| USB              | USB              |  |  |  |  |

| CPU              | DMA              |  |  |  |  |

| Lowest Priority  |                  |  |  |  |  |

**Note:** The Arbitration mode chosen only has an effect on system performance when a contention for a target occurs.

The Flash controller, when programming memory, always has the highest priority regardless of the priority mode setting.

Refer to **Section 48. "Memory Organization and Permissions"** (DS60001214) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32) for more information regarding Bus Matrix operation.

#### 4.3 Flash Line Buffer

The Flash line buffer is a buffer that resides between the Bus Matrix and the Flash memory. When a Flash fetch is generated, an aligned double word (64 bits) is read. This is then placed in the Flash line buffer. If the next initiator requested address's data is contained in the Flash line buffer, it is read directly without requiring another Flash fetch; if it is not in the Flash line buffer, a Flash fetch is generated.

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER (CONTINUED)

- bit 3-0 **NVMOP<3:0>:** NVM Operation bits These bits are only writable when WREN = 0. 1111 = Reserved

- •

- •

- 1000 = Reserved

- 0111 = Program Erase Operation: Erases all of Program Flash Memory (all pages must be unprotected, PWP<23:0> = 0x000000, Boot Flash Memory is not erased)

- 0110 = Reserved

- 0101 = Reserved

- 0100 = Page Erase Operation: Erases page selected by NVMADDR if it is not write-protected

- 0011 = Row Program Operation: Programs row selected by NVMADDR if it is not write-protected

- 0010 = Double-Word Program Operation: Programs two words to address selected by NVMADDR if it is not write-protected

- 0001 = Reserved

- 0000 = No operation (clears the WRERR and LVDERR status bits when executed)

- Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other Reset sources.

- 2: These bits are cleared by setting NVMOP<3:0> = 0000 and initiating a Flash operation (i.e., WR).

- 3: This bit is only writable when the NVMKEY unlock sequence is followed. Refer to Example 5-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 31:24        |                   | NVMKEY<31:24>     |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 15:8         | NVMKEY<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |

| 7:0          |                   |                   |                   | NVMK              | EY<7:0>           |                   |                  |                  |  |  |  |

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 **NVMKEY<31:0>:** Programming Unlock Register bits These bits are write-only and read as '0' on any read.

**Note:** This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM. Refer to Example 5-1.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |

| 31:24        | WDTCLRKEY<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |

| 23:16        | WDTCLRKEY<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R-y               | R-y               | R-y               | R-y              | R-y              |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | _                 | RUNDIV<4:0>       |                   |                   |                  |                  |  |

| 7.0          | R-y               | R-y               | R-y               | R-y               | R-y               | R-y               | R-y              | R/W-y            |  |

| 7:0          | CLKSE             | L<1:0>            |                   | SLPDIV<4:0>       |                   |                   |                  | WDTWINEN         |  |

#### REGISTER 13-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from C | y = Values set from Configuration bits on Reset |                    |  |  |  |

|-------------------|-----------------------|-------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bi                            | it, read as '0'    |  |  |  |

| -n = Value at POR | '1' = Bit is set      | '0' = Bit is cleared                            | x = Bit is unknown |  |  |  |

bit 31-16 WDTCLRKEY<15:0>: Watchdog Timer Clear Key bits

To clear the Watchdog Timer to prevent a time-out, software must write the value, 0x5743, to the upper 16 bits of this register address using a single 16-bit write.

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1)</sup>

- 1 = The WDT is enabled

- 0 = The WDT is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12-8 **RUNDIV<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value for Run Mode from Configuration bits On Reset, these bits are set to the values of the RWDTPS<4:0> Configuration bits in FWDT.

- bit 7-6 **CLKSEL<1:0>:** Shadow Copy of Watchdog Timer Clock Selection Value for Run Mode from Configuration bits On Reset, these bits are set to the values of the RCLKSEL<1:0> Configuration bits in FWDT.

- bit 5-1 **SLPDIV<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value for Sleep/Idle Mode from Configuration bits On Reset, these bits are set to the values of the SWDTPS<4:0> Configuration bits in FWDT.

# bit 0 WDTWINEN: Watchdog Timer Window Enable bit On Reset, this bit is set to the inverse of the value of the WINDIS Configuration bit in FWDT. 1 = Windowed mode is enabled 0 = Windowed mode is disabled

**Note 1:** This bit only has control when FWDTEN (FWDT<15>) = 0.

#### REGISTER 14-2: CCPxCON2: CAPTURE/COMPARE/PWMx CONTROL 2 REGISTER (CONTINUED)

- bit 14 **ASDGM:** CCPx Auto-Shutdown Gate Mode Enable bit

- 1 = Waits until the next Time Base Reset or rollover for shutdown to occur

- 0 = Shutdown event occurs immediately

- bit 13 Unimplemented: Read as '0'

- bit 12 SSDG: CCPx Software Shutdown/Gate Control bit

- 1 = Manually forces auto-shutdown, timer clock gate or input capture signal gate event (setting the ASDGM bit still applies)

- 0 = Normal module operation

- bit 11-8 Unimplemented: Read as '0'

```

bit 7-0 ASDG<7:0>: CCPx Auto-Shutdown/Gating Source Enable bits

```

- 1xxx xxxx = Auto-shutdown is controlled by the OCFB pin (remappable)

- x1xx xxxx = Auto-shutdown is controlled by the OCFA pin (remappable)

- xx1x xxxx = Auto-shutdown is controlled by CLC1 for MCCP1 Auto-shutdown is controlled by CLC2 for MCCP2

- Auto-shutdown is controlled by CLC3 for MCCP3

- Auto-shutdown is controlled by CLC1 for SCCP4

- Auto-shutdown is controlled by CLC2 for SCCP5

- Auto-shutdown is controlled by CLC3 for SCCP6

- Auto-shutdown is controlled by CLC4 for SCCP7

- Auto-shutdown is controlled by CLC1 for SCCP8 Auto-shutdown is controlled by CLC2 for SCCP9

- xxx1 xxxx = Auto-shutdown is controlled by the SCCP4 output for MCCP1/MCCP2/MCCP3

- Auto-shutdown is controlled by the MCCP1 output for SCCP4/SCCP5/SCCP6/SCCP7/ SCCP8/SCCP9

- xxxx 1xxx = Auto-shutdown is controlled by the SCCP5 output for MCCP1/MCCP2/MCCP3 Auto-shutdown is controlled by the MCCP2 output for SCCP4/SCCP5/SCCP6/SCCP7/ SCCP8/SCCP9

- xxxx x1xx = Auto-shutdown is controlled by Comparator 3

- xxxx xx1x = Auto-shutdown is controlled by Comparator 2

- xxxx xxx1 = Auto-shutdown is controlled by Comparator 1

- **Note 1:** OCFEN through OCBEN (bits<29:25>) are implemented in MCCP modules only.

- 2: This pin is remappable from SCCP modules.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | -                | _                |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | r-0              | r-0              |

| 23:16        | —                 | PCIE              | SCIE              | BOEN              | SDAHT             | SBCDE             | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

#### REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER

| Legend:           | r = Reserved bit HC = Hardware Clearable bit |                      |                    |

|-------------------|----------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-23 Unimplemented: Read as '0'

| bit 22 | PCIE: Stop Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul> <li>1 = Enables interrupt on detection of Stop condition</li> <li>0 = Stop detection interrupts are disabled</li> </ul>                                                                                                                                                                  |

| bit 21 | SCIE: Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                 |

|        | <ul> <li>1 = Enables interrupt on detection of Start or Restart conditions</li> <li>0 = Start detection interrupts are disabled</li> </ul>                                                                                                                                                    |

| bit 20 | <b>BOEN:</b> Buffer Overwrite Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                   |

|        | <ul> <li>1 = I2CxRCV is updated and an ACK is generated for a received address/data byte, ignoring the state of the I2COV bit (I2CxSTAT&lt;6&gt;) only if the RBF bit (I2CxSTAT&lt;1&gt;) = 0</li> <li>0 = I2CxRCV is only updated when the I2COV bit (I2CxSTAT&lt;6&gt;) is clear</li> </ul> |

| bit 19 | SDAHT: SDAx Hold Time Selection bit                                                                                                                                                                                                                                                           |

|        | 1 = Minimum of 300 ns hold time on SDAx after the falling edge of SCLx                                                                                                                                                                                                                        |

- 0 = Minimum of 100 ns hold time on SDAx after the falling edge of SCLx

- bit 18 **SBCDE:** Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

- 1 = Enables slave bus collision interrupts

- 0 = Slave bus collision interrupts are disabled

- bit 17-16 **Reserved:** Maintain as '0'

- bit 15 ON: I2Cx Enable bit

- 1 = Enables the I2Cx module and configures the SDAx and SCLx pins as serial port pins

- 0 = Disables the I2Cx module; all I<sup>2</sup>C pins are controlled by port functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** I2Cx Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Releases SCLx clock

- 0 = Holds SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear at the beginning of slave transmission. Hardware is clear at the end of slave reception.

If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware is clear at the beginning of slave transmission.

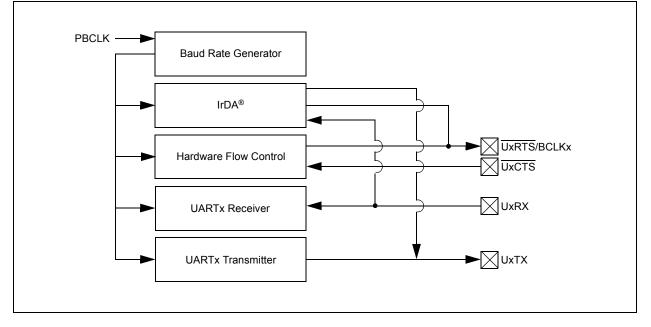

#### 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21. "UART"** (DS61107) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/ PIC32). The information in this data sheet supersedes the information in the FRM.

The UART module is one of the serial I/O modules available in the PIC32MM0256GPM064 family devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN/J2602 and IrDA<sup>®</sup>. The module also supports the hardware flow control option with the UxCTS and UxRTS pins, and also includes an IrDA<sup>®</sup> encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission

- Even, Odd or No Parity Options (for 8-bit data)

- One or Two Stop Bits

- Hardware Auto-Baud Feature

- Hardware Flow Control Option

- Fully Integrated Baud Rate Generator (BRG) with 16-Bit Prescaler

- Baud rates ranging from 47.4 bps to 6.25 Mbps at 25 MHz

- 8-Level Deep First-In-First-Out (FIFO) Transmit Data Buffer

- · 8-Level Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for Interrupt Only on Address Detect (9th bit = 1)

- · Separate Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- · LIN/J2602 Protocol Support

- IrDA Encoder and Decoder with 16x Baud Clock Output for External IrDA Encoder/Decoder Support

- · Supports Separate UART Baud Clock Input

- Ability to Continue to Run when a Receive Overflow Condition Exists

- Ability to Run and rEceive Data during Sleep mode

Figure 17-1 illustrates a simplified block diagram of the UART module.

#### FIGURE 17-1: UARTX SIMPLIFIED BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 |                   | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 |                   | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 |                   |                  | _                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

#### REGISTER 18-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| 0                 |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device is enabled

- 0 = Direct connection to a low-speed device is disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NACK'd transactions are disabled

- 0 = Retry NACK'd transactions are enabled; retry done in hardware

- bit 5 Unimplemented: Read as '0'

- bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

#### If EPTXEN = 1 and EPRXEN = 1:

1 = Disables Endpoint n from control transfers; only TX and RX transfers are allowed

0 = Enables Endpoint n for control (SETUP) transfers; TX and RX transfers are also allowed Otherwise, this bit is ignored.

#### bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint handshake is enabled

- 0 = Endpoint handshake is disabled (typically used for isochronous endpoints)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                 | —                 | _                 | MTHTEN            | MTHONE<3:0>       |                   |                  |                  |

| 45.0         | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | DAYTE             | N<1:0>            | DAYONE<3:0>       |                   |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | -                 | —                 | _                 |                   | — WDAY<2:0>       |                   |                  |                  |

#### REGISTER 19-5: **RTCDATE/ALMDATE: RTCC DATE/ALARM REGISTERS**

| Legena:          |       |

|------------------|-------|

| R = Readable bit | W = W |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-21 Unimplemented: Read as '0'

- bit 20 MTHTEN: Binary Coded Decimal Value of Months 10-Digit bit Contains a value from 0 to 1.

- bit 19-16 MTHONE<3:0>: Binary Coded Decimal Value of Months 1-Digit bits Contains a value from 0 to 9.

- bit 15-14 Unimplemented: Read as '0'

- bit 13-12 DAYTEN<1:0>: Binary Coded Decimal Value of Days 10-Digit bits Contains a value from 0 to 3.

- bit 11-8 DAYONE<3:0>: Binary Coded Decimal Value of Days 1-Digit bits Contains a value from 0 to 9.

- bit 7-3 Unimplemented: Read as '0'

- bit 2-0 WDAY<2:0>: Binary Coded Decimal Value of Weekdays Digit bits Contains a value from 0 to 6.

#### TABLE 20-1: ADC REGISTER MAP

| sse                         |                                 |               |                                                                                  |                |  |  |  |  |   | Bits    | 6       |            |  |  |      |  |  |      |

|-----------------------------|---------------------------------|---------------|----------------------------------------------------------------------------------|----------------|--|--|--|--|---|---------|---------|------------|--|--|------|--|--|------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(2)</sup> | Bit Range     | 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 |                |  |  |  |  |   |         | 16/0    | All Resets |  |  |      |  |  |      |

| 2100                        | ADC1BUF0                        | 31:16<br>15:0 |                                                                                  | ADC1BUF0<31:0> |  |  |  |  |   |         |         |            |  |  | 0000 |  |  |      |

| 2110                        | ADC1BUF1                        | 31:16<br>15:0 |                                                                                  | ADC1BUF1<31:0> |  |  |  |  |   |         |         |            |  |  | 0000 |  |  |      |

| 2120                        | ADC1BUF2                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | Δ | DC1BUF2 | 2<31:0> |            |  |  |      |  |  | 0000 |

| 2130                        | ADC1BUF3                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | ۵ | DC1BUF  | 3<31:0> |            |  |  |      |  |  | 0000 |

| 2140                        | ADC1BUF4                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | Α | DC1BUF  | 4<31:0> |            |  |  |      |  |  | 0000 |

| 2150                        | ADC1BUF5                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | A | DC1BUF  | 5<31:0> |            |  |  |      |  |  | 0000 |

| 2160                        | ADC1BUF6                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | Δ | DC1BUF  | 6<31:0> |            |  |  |      |  |  | 0000 |

| 2170                        | ADC1BUF7                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | Δ | DC1BUF  | 7<31:0> |            |  |  |      |  |  | 0000 |

| 2180                        | ADC1BUF8                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | Δ | DC1BUF  | 8<31:0> |            |  |  |      |  |  | 0000 |

| 2190                        | ADC1BUF9                        | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | Δ | DC1BUF  | 9<31:0> |            |  |  |      |  |  | 0000 |

| 21A0                        | ADC1BUF10                       | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | A | DC1BUF1 | 0<31:0> |            |  |  |      |  |  | 0000 |

| 21B0                        | ADC1BUF11                       | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | A | DC1BUF1 | 1<31:0> |            |  |  |      |  |  | 0000 |

| 21C0                        | ADC1BUF12                       | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | A | DC1BUF1 | 2<31:0> |            |  |  |      |  |  | 0000 |

| 21D0                        | ADC1BUF13                       | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | A | DC1BUF1 | 3<31:0> |            |  |  |      |  |  | 0000 |

| 21E0                        | ADC1BUF14                       | 31:16<br>15:0 |                                                                                  |                |  |  |  |  | A | DC1BUF1 | 4<31:0> |            |  |  |      |  |  | 0000 |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The CSS<19:12> bits are not implemented in 28-pin devices. The CSS<19:15> bits are not implemented in 36-pin and 40-pin devices. The CSS<17:14> bits are not implemented in 48-pin devices.

2: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                    |                   |                   | —                 |                   |                   | _                | —                |

| 00.40        | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                    | _                 | —                 | —                 |                   | —                 | _                | _                |

| 45.0         | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |

| 15:8         |                      | VCFG<2:0>         |                   | OFFCAL            | BUFREGEN          | CSCNA             | _                | _                |

| 7.0          | R/W-0                | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7:0          | 7:0 BUFS — SMPI<3:0> |                   |                   |                   |                   |                   | BUFM             | —                |

#### REGISTER 20-2: AD1CON2: ADC CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|         |                              | ADC Vr+                                                                                            | ADC VR-                     |                                                                 |

|---------|------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------------------------------|

|         | 000                          | AVdd                                                                                               | AVss                        |                                                                 |

|         | 001                          | AVdd                                                                                               | External VREF- Pin          |                                                                 |

|         | 010                          | External VREF+ Pin                                                                                 | AVss                        |                                                                 |

|         | 011                          | External VREF+ Pin                                                                                 | External VREF- Pin          |                                                                 |

|         | 1xx                          | Unimplemente                                                                                       | d; do not use               |                                                                 |

| bit 12  | 1 = Enables                  |                                                                                                    | inputs of the SHA are con   | nected to the negative reference<br>trolled by AD1CHS or AD1CSS |

| bit 11  | 1 = Conversi                 | : ADC Buffer Register Enable<br>ion result is loaded into the b<br>ult buffer is treated as a FIFC | uffer location determined b | y the converted channel                                         |

| bit 10  | CSCNA: Sca                   | an Input Selections for CH0+                                                                       | SHA Input for Input Multipl | exer Setting bit                                                |

|         | 1 = Scans in<br>0 = Does not | •                                                                                                  |                             |                                                                 |

| bit 9-8 | Unimpleme                    | nted: Read as '0'                                                                                  |                             |                                                                 |

| bit 7   | BUFS: Buffe                  | r Fill Status bit                                                                                  |                             |                                                                 |

|         | 1 = ADC is c                 | nen BUFM = 1 (ADC buffers<br>urrently filling Buffers 11-21,<br>urrently filling Buffers 0-10, u   | user should access data in  | 0-10                                                            |

| bit 6   | Unimpleme                    | nted: Read as '0'                                                                                  |                             |                                                                 |

| bit 5-2 |                              | Sample/Convert Sequences                                                                           |                             |                                                                 |

|         |                              | rupts at the completion of con<br>rupts at the completion of con                                   |                             |                                                                 |

|         | 0000 = Inter                 | rupts at the completion of con<br>rupts at the completion of con                                   | nversion for each sample/c  |                                                                 |

| bit 1   | 1 = Buffer co                | Result Buffer Mode Select b<br>onfigured as two 11-word buff<br>onfigured as one 22-word buff      | ers, ADC1BUF(010), AD       | C1BUF(1121)                                                     |

| bit 0   | Unimpleme                    | nted: Read as '0'                                                                                  |                             |                                                                 |

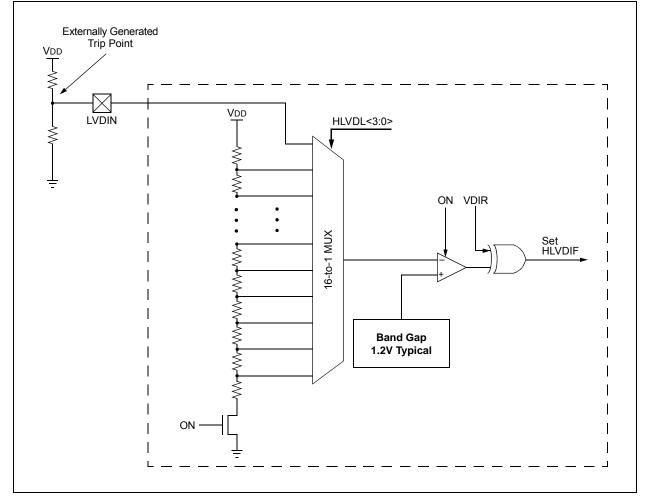

#### 24.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

The High/Low-Voltage Detect (HLVD) module is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The HLVD Control register (see Register 24-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

#### FIGURE 24-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

#### 28.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 28.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 28.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 28.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 28.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### 29.1 DC Characteristics

#### FIGURE 29-1: PIC32MM0256GPM064 FAMILY VOLTAGE-FREQUENCY GRAPH

#### TABLE 29-1: THERMAL OPERATING CONDITIONS

| Rating                                                                                                                                                                                  | Symbol | Min         | Тур         | Max  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------------|-------------|------|------|

| PIC32MM0XXXGPM0XX:                                                                                                                                                                      |        |             |             |      |      |

| Operating Junction Temperature Range                                                                                                                                                    | TJ     | -40         | —           | +125 | °C   |

| Operating Ambient Temperature Range                                                                                                                                                     | TA     | -40         | —           | +85  | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>$PINT = VDD x (IDD - \Sigma IOH)$<br>I/O Pin Power Dissipation:<br>$PI/O = \Sigma (\{VDD - VOH\} x IOH) + \Sigma (VOL x IOL)$ | PD     | PINT + PI/O |             | W    |      |

| Maximum Allowed Power Dissipation                                                                                                                                                       | Pdmax  | (           | ΓJ — TA)/θJ | IA   | W    |

#### TABLE 29-2: PACKAGE THERMAL RESISTANCE<sup>(1)</sup>

| Package     | Symbol | Тур  | Unit |

|-------------|--------|------|------|

| 28-Pin SSOP | θJA    | 71.0 | °C/W |

| 28-Pin QFN  | θJA    | 69.7 | °C/W |

| 28-Pin UQFN | θJA    | 26   | °C/W |

| 36-Pin VQFN | θJA    | 30.0 | °C/W |

| 40-Pin UQFN | θJA    | 41   | °C/W |

| 48-Pin UQFN | θJA    | 24.5 | °C/W |

| 48-Pin TQFP | θJA    | 51   | °C/W |

| 64-Pin QFN  | θJA    | 29.4 | °C/W |

| 64-Pin TQFP | θJA    | 44.5 | °C/W |

**Note 1:** Junction to ambient thermal resistance; Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

#### 29.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC32MM0256GPM064 family AC characteristics and timing parameters.

#### TABLE 29-16: TEMPERATURE AND VOLTAGE SPECIFICATIONS - AC

|                    | Standard Operating Conditions: 2.0V to 3.6V (unless otherwise stated)          |

|--------------------|--------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$                   |

|                    | Operating voltage VDD range as described in Section 29.1 "DC Characteristics". |

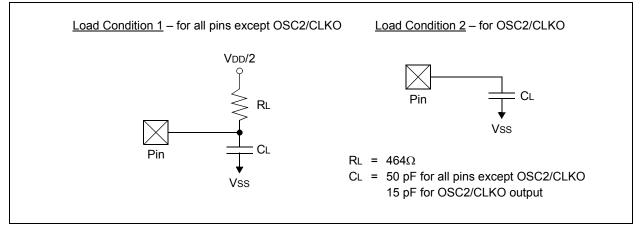

#### FIGURE 29-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 29-17: CAPACITIVE LOADING CONDITIONS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                              |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|-------------------------------------------------------------------------|

| DO50         | Cosco  | OSC2/CLKO Pin         | _   | —                  | TBD |       | In XT and HS modes when<br>external clock is used to drive<br>OSC1/CLKI |

| DO56         | Сю     | All I/O Pins and OSC2 | —   | —                  | TBD | pF    | EC mode                                                                 |

| DO58         | Св     | SCLx, SDAx            | _   | _                  | TBD | pF    | In I <sup>2</sup> C mode                                                |

**Legend:** TBD = To Be Determined

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M6) - 4x4x0.6 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                             | Units  |          |           |      |  |  |  |

|-----------------------------|--------|----------|-----------|------|--|--|--|

| Dimension                   | Limits | MIN      | NOM       | MAX  |  |  |  |

| Number of Pins              | Ν      |          | 28        |      |  |  |  |

| Pitch                       | е      |          | 0.40 BSC  |      |  |  |  |

| Overall Height              | Α      | -        | -         | 0.60 |  |  |  |

| Standoff                    | A1     | 0.00     | 0.02      | 0.05 |  |  |  |

| Terminal Thickness          | A3     |          | 0.152 REF |      |  |  |  |

| Overall Width               | E      | 4.00 BSC |           |      |  |  |  |

| Exposed Pad Width           | E2     | 1.80     | 1.90      | 2.00 |  |  |  |

| Overall Length              | D      |          | 4.00 BSC  |      |  |  |  |

| Exposed Pad Length          | D2     | 1.80     | 1.90      | 2.00 |  |  |  |

| Terminal Width              | b      | 0.15     | 0.20      | 0.25 |  |  |  |

| Corner Anchor Pad           | b1     | 0.40     | 0.45      | 0.50 |  |  |  |

| Corner Pad, Metal Free Zone | b2     | 0.18     | 0.23      | 0.28 |  |  |  |

| Terminal Length             | L      | 0.30     | 0.45      | 0.50 |  |  |  |

| Terminal-to-Exposed-Pad     | K      | -        | 0.60      | -    |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated

- 3. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-333-M6 Rev A Sheet 2 of 2

#### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.70 x 7.70 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units                         |      |          |      |  |

|------------------------|-------------------------------|------|----------|------|--|

| Dimension              | Dimension Limits              |      |          |      |  |

| Number of Pins         | N                             |      | 64       |      |  |

| Pitch                  | е                             |      | 0.50 BSC |      |  |

| Overall Height         | A                             | 0.80 | 0.85     | 0.90 |  |

| Standoff               | A1                            | 0.00 | 0.02     | 0.05 |  |

| Contact Thickness      | Contact Thickness A3 0.20 REF |      |          |      |  |

| Overall Width          | E                             |      | 9.00 BSC |      |  |

| Exposed Pad Width      | E2                            | 7.60 | 7.70     | 7.80 |  |

| Overall Length         | D                             |      | 9.00 BSC |      |  |

| Exposed Pad Length     | D2                            | 7.60 | 7.70     | 7.80 |  |

| Contact Width          | b                             | 0.20 | 0.25     | 0.30 |  |

| Contact Length         | L                             | 0.30 | 0.40     | 0.50 |  |

| Contact-to-Exposed Pad | К                             | 0.20 | -        | -    |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-213B Sheet 2 of 2

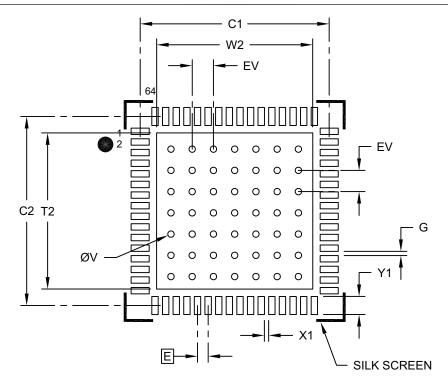

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 7.70x7.70mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                 | Units    | MILLIMETERS    |          |      |

|---------------------------------|----------|----------------|----------|------|

| Dimensior                       | n Limits | nits MIN NOM M |          | MAX  |

| Contact Pitch                   | E        |                | 0.50 BSC |      |

| Optional Center Pad Width       | W2       |                |          | 7.50 |

| Optional Center Pad Length      | T2       |                |          | 7.50 |

| Contact Pad Spacing             | C1       |                | 8.90     |      |

| Contact Pad Spacing             | C2       |                | 8.90     |      |

| Contact Pad Width (X20)         | X1       |                |          | 0.30 |

| Contact Pad Length (X20)        | Y1       |                |          | 0.90 |

| Contact Pad to Center Pad (X20) | G        | 0.20           |          |      |

| Thermal Via Diameter            | V        |                | 0.30     |      |

| Thermal Via Pitch               | EV       |                | 1.00     |      |

Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2213B

#### Ε

| Electrical Characteristics |    |

|----------------------------|----|

| Absolute Maximum Ratings   |    |

| V/F Graph (Industrial)     |    |

| Errata                     | 12 |

| F                          |    |

|                            |    |

| Flash Program Memory                        |    |

|---------------------------------------------|----|

| Flash Controller Registers Write Protection | 45 |

| Write Protection                            | 45 |

#### G

| Getting Started with PIC32 MCUs | 23 |

|---------------------------------|----|

| Connection Requirements         | 23 |

| Decoupling Capacitors           | 23 |

| External Oscillator Pins        | 27 |

| ICSP Pins                       |    |

| JTAG                            | 27 |

| Master Clear (MCLR) Pin         | 24 |

| Unused I/Os                     | 27 |

| Voltage Regulator (VCAP)        | 25 |

|                                 |    |

### Н

| High/Low-Voltage Detect (HLVD)     | 253 |

|------------------------------------|-----|

| High/Low-Voltage Detect. See HLVD. |     |

## I

| I/O Ports                                       | . 113 |

|-------------------------------------------------|-------|

| Analog/Digital Port Pins Configuration          | . 114 |

| CLR, SET and INV Registers                      | . 114 |

| GPIO Port Merging                               | . 114 |

| Open-Drain Configuration                        | . 114 |

| Parallel I/O (PIO)                              | . 114 |

| Pull-up/Pull-Down Pins                          | . 115 |

| Write/Read Timing                               | . 114 |

| Input Change Notification (ICN)                 | . 114 |

| Instruction Set                                 | . 281 |

| Inter-IC Sound. See I <sup>2</sup> S.           |       |

| Inter-Integrated Circuit (I <sup>2</sup> C      | . 167 |

| Inter-Integrated Circuit. See I <sup>2</sup> C. |       |

| Internet Address                                | . 353 |

| Interrupts                                      |       |

| Sources and Vector Names                        | 62    |

#### Μ

| MCCP/SCCP                                                         |     |

|-------------------------------------------------------------------|-----|

| Registers                                                         | 142 |

| Memory Maps                                                       |     |

| Devices with 128 Kbytes Program Memory                            |     |

| Devices with 256 Kbytes Program Memory                            |     |

| Devices with 64 Kbytes Program Memory                             | 41  |

| Memory Organization                                               |     |

| Alternate Configuration Bits Space                                |     |

| Bus Matrix (BMX)                                                  |     |

| Flash Line Buffer                                                 |     |

| Microchip Internet Web Site                                       | 353 |

| MIPS32 <sup>®</sup> microAptiv <sup>™</sup> UC Core Configuration |     |

| MPLAB Assembler, Linker, Librarian                                |     |

| MPLAB ICD 3 In-Circuit Debugger                                   |     |

| MPLAB PM3 Device Programmer                                       |     |

| MPLAB REAL ICE In-Circuit Emulator System                         |     |

| MPLAB X Integrated Development                                    |     |

| Environment Software                                              |     |

|                                                                   |     |

| MPLAB X SIM Software Simulator                  | 285 |

|-------------------------------------------------|-----|

| MPLIB Object Librarian                          |     |

| MPLINK Object Linker                            |     |

| Multiply/Divide Unit Latencies and Repeat Rates | 31  |

#### 0

| Oscillator Configuration       |  |

|--------------------------------|--|

| Clock Switching                |  |

| Sequence                       |  |

| Fail-Safe Clock Monitor (FSCM) |  |

| FRC Self-Tuning                |  |

#### Ρ

| Packaging                               | 319 |

|-----------------------------------------|-----|

| Details                                 | 321 |

| Marking                                 | 319 |

| Peripheral Pin Select (PPS)             | 115 |

| PICkit 3 In-Circuit Debugger/Programmer |     |

| Pinout Description                      | 16  |

| Power-Saving Features                   | 257 |

| Idle Mode                               | 257 |

| Low-Power Brown-out Reset               | 261 |

| On-Chip Voltage Regulator               |     |

| (Low-Power Modes)                       | 261 |

| Peripheral Module Disable               | 258 |

| Retention Sleep Mode                    | 257 |

| Sleep Mode                              | 257 |

| Standby Sleep Mode                      | 257 |

| PPS                                     |     |

| Available Peripherals                   | 115 |

| Available Pins                          | 115 |

| Controlling                             | 115 |

| Controlling Configuration Changes       | 118 |

| Input Mapping                           | 116 |

| Input Pin Selection                     | 116 |

| Output Mapping                          | 118 |

| Output Pin Selection                    | 119 |

| Remappable Pin Input Source Assignments | 117 |

| Programming and Diagnostics             | 264 |

|                                         |     |

#### R

| Real-Time Clock and Calendar (RTCC)<br>Real-Time Clock and Calendar. See RTCC.<br>Register Maps | . 209 |

|-------------------------------------------------------------------------------------------------|-------|

| ADC                                                                                             | 219   |

| Alternate Configuration Words Summary                                                           | 266   |

| Band Gap                                                                                        | 277   |

| CLC1, CLC2 and CLC3                                                                             | 233   |

| Comparator 1, 2 and 3                                                                           |       |

| Configuration Words Summary                                                                     | 265   |

| DMA Channels 0-3                                                                                | 79    |

| DMA Controller                                                                                  | 78    |

| Flash Controller                                                                                | 46    |

| High/Low Voltage Detect                                                                         | . 254 |

| I2C1, I2C2 and I2C3                                                                             | 169   |

| Interrupts                                                                                      | 66    |

| MCCP/SCCP                                                                                       | 143   |

| Oscillator Configuration                                                                        | . 102 |

| Peripheral Module Disable                                                                       | 260   |

| Peripheral Pin Select                                                                           | 124   |

| PORTA                                                                                           | 120   |

| PORTB                                                                                           | 121   |

| PORTC                                                                                           | 122   |

|                                                                                                 |       |