Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

ĿXFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® microAptiv™                                                               |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 25MHz                                                                             |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT                |

| Number of I/O              | 27                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 32K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                         |

| Data Converters            | A/D 15x10/12b                                                                     |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 36-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 36-SQFN (6x6)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0256gpm036t-i-m2 |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 5.2 Flash Control Registers

# TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | ē         |          |                                                                                       |   |   |   |      |      | Bit     | s        |   |   |      |            |      |   |   |      |

|-----------------------------|------------------------|-----------|----------|---------------------------------------------------------------------------------------|---|---|---|------|------|---------|----------|---|---|------|------------|------|---|---|------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15    | 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 |   |   |   |      |      |         |          |   |   | 16/0 | All Resets |      |   |   |      |

| 2930                        | NVMCON <sup>(1)</sup>  | 31:16     | _        |                                                                                       |   |   |   |      |      |         |          |   |   |      | 0000       |      |   |   |      |

| 2930                        | NVINCON**              | 15:0      | WR       | VR WREN WRERR LVDERR r NVMOP<3:0>                                                     |   |   |   |      |      |         |          |   |   |      |            | 0000 |   |   |      |

| 2940                        | NVMKEY                 | 31:16     |          |                                                                                       |   |   |   |      |      |         | (~31·0>  |   |   |      |            |      |   |   | 0000 |

| 2940                        |                        | 15:0      |          | NVMKEY<31:0>                                                                          |   |   |   |      |      |         |          |   |   |      |            | 0000 |   |   |      |

| 2950                        | NVMADDR <sup>(1)</sup> | 31:16     |          |                                                                                       |   |   |   |      |      | NVMADD  | P<31.0>  |   |   |      |            |      |   |   | 0000 |

| 2930                        | NVINADDR               | 15:0      |          |                                                                                       |   |   |   |      |      | NVINADD | N~31.02  |   |   |      |            |      |   |   | 0000 |

| 2960                        | NVMDATA0               | 31:16     |          |                                                                                       |   |   |   |      |      | NVMDATA | 0<31.0>  |   |   |      |            |      |   |   | 0000 |

| 2300                        | NUMBAIAO               | 15:0      |          |                                                                                       |   |   |   |      |      |         | 0 3 1.02 |   |   |      |            |      |   |   | 0000 |

| 2970                        | NVMDATA1               | 31:16     |          |                                                                                       |   |   |   |      |      | NVMDATA | 1<31.0>  |   |   |      |            |      |   |   | 0000 |

| 2370                        |                        | 15:0      |          |                                                                                       |   |   |   |      |      |         | 151.02   |   |   |      |            |      |   |   | 0000 |

| 2980                        | NVMSRCADDR             | 31:16     |          |                                                                                       |   |   |   |      | N    | VMSRCAL | DR<31:0> |   |   |      |            |      |   |   | 0000 |

| 2000                        |                        | 15:0      |          |                                                                                       |   |   |   |      |      |         |          |   |   |      |            |      |   |   | 0000 |

| 2990                        | NVMPWP <sup>(1)</sup>  | 31:16     | PWPULOCK | _                                                                                     | _ | — | _ | _    | _    | _       |          |   |   | PWP< | 23:16>     |      |   |   | 8000 |

| 2330                        |                        | 15:0      |          |                                                                                       |   |   |   |      |      | PWP<    | 15:0>    |   |   |      |            |      |   |   | 0000 |

| 29A0                        | NVMBWP <sup>(1)</sup>  | 31:16     | _        | _                                                                                     | _ | — | _ | _    | _    | _       | _        | _ | _ | _    | _          | _    | _ | _ | 0000 |

| 23A0                        |                        | 15:0      | BWPULOCK | _                                                                                     | — | — | _ | BWP2 | BWP1 | BWP0    | _        | — | — | —    | —          | —    | — | _ | 8700 |

Legend: — = unimplemented, read as '0'; r = Reserved bit. Reset values are shown in hexadecimal.

Note 1: These registers have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|---------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |  |

| 31:24        | —                 | _                 |                   | —                 | _                 |                     | _                   | —                   |  |

| 00.40        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |  |

| 23:16        | —                 | _                 | —                 | —                 | —                 | —                   | _                   | _                   |  |

| 45.0         | R/W-1             | U-0               | U-0               | U-0               | U-0               | R/W-1               | R/W-1               | R/W-1               |  |

| 15:8         | BWPULOCK —        |                   |                   | —                 | —                 | BWP2 <sup>(1)</sup> | BWP1 <sup>(1)</sup> | BWP0 <sup>(1)</sup> |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0                 | U-0                 |  |

| 7:0          |                   |                   | _                 | _                 | _                 |                     |                     | —                   |  |

### REGISTER 5-7: NVMBWP: BOOT FLASH (PAGE) WRITE-PROTECT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |  |

|-------------------|------------------|----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 BWPULOCK: Boot Alias Write-Protect Unlock bit

1 = BWPx bits are not locked and can be modified

0 = BWPx bits are locked and cannot be modified

This bit is only clearable and cannot be set except by any Reset.

#### bit 14-11 Unimplemented: Read as '0'

- bit 10 **BWP2:** Boot Alias Page 2 Write-Protect bit<sup>(1)</sup>

- 1 = Write protection for physical address, 0x01FC08000 through 0x1FC0BFFF, is enabled

- 0 = Write protection for physical address, 0x01FC08000 through 0x1FC0BFFF, is disabled

#### bit 9 **BWP1:** Boot Alias Page 1 Write-Protect bit<sup>(1)</sup>

1 = Write protection for physical address, 0x01FC04000 through 0x1FC07FFF, is enabled 0 = Write protection for physical address, 0x01FC04000 through 0x1FC07FFF, is disabled

#### bit 8 **BWP0:** Boot Alias Page 0 Write-Protect bit<sup>(1)</sup>

1 = Write protection for physical address, 0x01FC00000 through 0x1FC03FFF, is enabled 0 = Write protection for physical address, 0x01FC00000 through 0x1FC03FFF, is disabled

- bit 7-0 Unimplemented: Read as '0'

- **Note 1:** These bits are only available when the NVMKEY unlock sequence is performed and the associated Lock bit (BWPULOCK) is set.

# **Note:** The bits in this register are only writable when the NVMKEY unlock sequence is followed. Refer to Example 5-1.

# PIC32MM0256GPM064 FAMILY

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | _                 |                   |                   | _                 |                   | —                |                  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | _                 | —                 | —                 | —                 | —                 | —                |                  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |  |  |

| 15:8         | —                 | _                 | —                 |                   | _                 | S                 | SRIPL<2:0>(1)    |                  |  |  |  |  |  |

| 7.0          | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |  |  |

| 7:0          | SIRQ<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

### REGISTER 7-3: INTSTAT: INTERRUPT STATUS REGISTER

| Legend:           | HS = Hardware Settable bit | HC = Hardware Clearable bit        |                    |  |  |  |  |

|-------------------|----------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 SRIPL<2:0>: Requested Priority Level for Single Vector Mode bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-0 SIRQ<7:0>: Last Interrupt Request Serviced Status bits 1111111-00000000 = The last interrupt request number serviced by the CPU

- **Note 1:** This value should only be used when the interrupt controller is configured for Single Vector mode.

| REGISTER 7-4: | <b>IPTMR: INTERRUPT PROXIMITY TIMER REGISTER</b> |

|---------------|--------------------------------------------------|

|               |                                                  |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        |                   |                   |                   | IPTMF             | ?<31:24>          |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IPTMR<31:0>: Interrupt Proximity Timer Reload bits

Used by the interrupt proximity timer as a reload value when the interrupt proximity timer is triggered by an interrupt event.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        |                   | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:10        |                   | —                 | _                 | -                 | —                 | —                 | —                | —                |  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | —                 | —                 | —                | —                |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   | CHPDAT<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

# REGISTER 8-18: DCHxDAT: DMA CHANNEL x PATTERN DATA REGISTER

# Legend:

| Ecgena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow terminate on match. All Other modes: Unused.

# PIC32MM0256GPM064 FAMILY

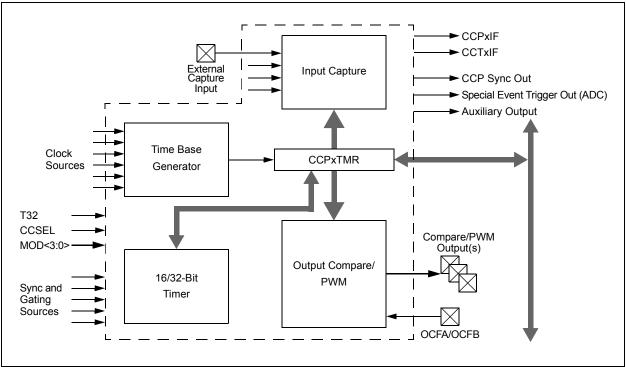

# FIGURE 14-1: MCCP/SCCP CONCEPTUAL BLOCK DIAGRAM

# 14.2 Registers

Each MCCP/SCCP module has up to seven control and status registers:

- CCPxCON1 (Register 14-1) controls many of the features common to all modes, including input clock selection, time base prescaling, timer synchronization, Trigger mode operations and postscaler selection for all modes. The module is also enabled and the operational mode is selected from this register.

- CCPxCON2 (Register 14-2) controls autoshutdown and restart operation, primarily for PWM operations, and also configures other input capture and output compare features, and configures auxiliary output operation.

- CCPxCON3 (Register 14-3) controls multiple output PWM dead time, controls the output of the output compare and PWM modes, and configures the PWM Output mode for the MCCP modules.

- CCPxSTAT (Register 14-4) contains read-only status bits showing the state of module operations.

Each module also includes eight buffer/counter registers that serve as Timer Value registers or data holding buffers:

- · CCPxTMR is the 32-Bit Timer/Counter register

- · CCPxPR is the 32-Bit Timer Period register

- CCPxR is the 32-bit primary data buffer for output compare operations

- CCPxBUF(H/L) is the 32-Bit Buffer register pair, which is used in input capture FIFO operations

#### **UART Control Registers** 17.1

# TABLE 17-1: UART1, UART2 AND UART3 REGISTER MAP

| -                           | LE 17-1.              |               |                                                                              | KTT, UAKTZ AND UAKTS REGISTER MAP |        |         |          |       |       |            |              |          |           |            |              | r       |         |        |            |

|-----------------------------|-----------------------|---------------|------------------------------------------------------------------------------|-----------------------------------|--------|---------|----------|-------|-------|------------|--------------|----------|-----------|------------|--------------|---------|---------|--------|------------|

| ess                         |                       | 0             |                                                                              |                                   |        |         |          |       |       | E          | Bits         |          |           |            |              |         |         |        |            |

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15                                                                        | 30/14                             | 29/13  | 28/12   | 27/11    | 26/10 | 25/9  | 24/8       | 23/7         | 22/6     | 21/5      | 20/4       | 19/3         | 18/2    | 17/1    | 16/0   | All Resets |

| 1800                        | U1MODE(1)             | 31:16         | _                                                                            |                                   | —      | _       | _        |       | —     | _          | SLPEN        | ACTIVE   | _         | _          | —            | CLKSE   | L<1:0>  | OVFDIS | 0000       |

| 1000                        | 0 INIODE              | 15:0          | ON                                                                           | ON – SIDL IREN RTSMD – UEN<1:0>   |        |         |          |       |       |            | WAKE         | LPBACK   | ABAUD     | RXINV      | BRGH         | PDSE    | L<1:0>  | STSEL  | 0000       |

| 1810                        | U1STA <sup>(1)</sup>  | 31:16         |                                                                              |                                   |        | UART1 M | ASK<7:0> |       |       |            |              |          |           | UART1 AD   | DR<7:0>      |         |         |        | 0000       |

| 1010                        | UIUIA                 | 15:0          | UTXISE                                                                       |                                   |        |         |          |       |       |            |              |          |           | 0110       |              |         |         |        |            |

| 1820                        | U1TXREG               | 31:16         | —                                                                            | —                                 | —      | —       | —        | —     | —     | —          | —            | —        | —         | —          | —            | —       | —       | —      | 0000       |

| 1020                        | OTHALLO               | 15:0          | —                                                                            |                                   |        |         |          |       |       |            |              |          | 0000      |            |              |         |         |        |            |

| 1830                        | U1RXREG               | 31:16         | —                                                                            | -                                 | —      | _       | —        | _     | —     | _          | _            | —        | —         | —          | —            | —       | —       | —      | 0000       |

|                             | 0.1101120             | 15:0          | —                                                                            |                                   |        |         |          |       |       |            |              | 0000     |           |            |              |         |         |        |            |

| 1840                        | U1BRG <sup>(1)</sup>  | 31:16         | —                                                                            | —                                 | —      | —       | —        | —     | —     | —          | —            | —        | —         | —          |              | —       | _       | —      | 0000       |

|                             |                       | 15:0          |                                                                              |                                   |        |         |          |       | Bau   | d Rate Ge  | nerator Pre  |          |           |            |              |         |         |        | 0000       |

| 1900                        | U2MODE(1)             | 31:16<br>15:0 | _                                                                            | —                                 | —      | —       | —        | —     | —     | —          | SLPEN        | ACTIVE   | —         | —          | —            |         | L<1:0>  | OVFDIS | 0000       |

|                             |                       |               | ON — SIDL IREN RISMD — UEN<1:0> WARE LPBACK ABAUD RXINV BRGH PDSEL<1:0> SISE |                                   |        |         |          |       |       |            | STSEL        | 0000     |           |            |              |         |         |        |            |

| 1910                        | U2STA <sup>(1)</sup>  | 31:16         |                                                                              |                                   | I      | UART2 M |          |       |       |            |              |          |           | UART2 AD   |              |         |         |        | 0000       |

|                             |                       | 15:0          | UTXISE                                                                       | L<1:0>                            | UTXINV | URXEN   | UTXBRK   | UTXEN | UTXBF | TRMT       | URXISE       |          | ADDEN     | RIDLE      | PERR         | FERR    | OERR    | URXDA  | 0110       |

| 1920                        | U2TXREG               | 31:16         | _                                                                            |                                   |        |         |          |       |       | -          | —            |          |           | —          | —            | _       |         |        | 0000       |

|                             |                       | 15:0          | _                                                                            | _                                 | —      |         |          |       | _     | TX8        |              |          |           | ART2 Trans | smit Registe | er<br>I |         |        | 0000       |

| 1930                        | U2RXREG               | 31:16<br>15:0 | -                                                                            |                                   | —      |         | _        |       |       | RX8        |              | _        | —         | ART2 Rece  | —            |         | _       | _      | 0000       |

|                             |                       | 31:16         | _                                                                            |                                   |        |         |          |       |       | КЛО        |              |          | 0         | ARTZ Rece  | eive Registe |         |         |        | 0000       |

| 1940                        | U2BRG <sup>(1)</sup>  | 15:0          | _                                                                            | _                                 | _      | —       | —        | _     |       | d Pata Car | nerator Pres |          | _         | —          |              | _       |         | _      | 0000       |

|                             |                       | 31:16         | _                                                                            |                                   |        |         |          |       | Dau   |            | SLPEN        | ACTIVE   | _         |            |              |         | L<1:0>  | OVFDIS | 0000       |

| 2000                        | U3MODE <sup>(1)</sup> | 15:0          | ON                                                                           |                                   | SIDL   | IREN    | RTSMD    | _     | UEN•  | (1:0>      | WAKE         | LPBACK   | <br>ABAUD | <br>RXINV  | BRGH         |         | L<1:0>  | STSEL  | 0000       |

|                             |                       | 31:16         | ON                                                                           |                                   | OIDE   | UART2 M |          |       | ULIN  | \$1.02     |              | LI BACK  | ADAOD     | UART2 AE   | -            | 1 DOL   | L \1.02 | OTOLL  | 0000       |

| 2010                        | U3STA <sup>(1)</sup>  | 15:0          | UTXISE                                                                       | I <1:0>                           | UTXINV | URXEN   | UTXBRK   | UTXEN | UTXBF | TRMT       | URXISE       | =1 <1.0> | ADDEN     | RIDLE      | PERR         | FERR    | OERR    | URXDA  | 0110       |

|                             |                       | 31:16         | _                                                                            |                                   | _      | _       |          | _     | _     |            |              |          |           |            |              | -       |         |        | 0000       |

| 2020                        | <b>U3TXREG</b>        | 15:0          | _                                                                            | _                                 | _      |         | _        | _     | _     | TX8        |              |          |           | ART2 Trans | smit Registe | er      |         |        | 0000       |

|                             |                       | 31:16         | _                                                                            | _                                 | _      | _       | _        | _     | _     | _          | _            | _        | _         |            |              |         | _       | _      | 0000       |

| 2030                        | U3RXREG               | 15:0          | _                                                                            |                                   | _      |         | _        | _     | _     | RX8        |              | l        |           | ART2 Rece  | ive Registe  | er      |         | l      | 0000       |

|                             |                       | 31:16         |                                                                              |                                   |        |         |          |       | _     | _          |              |          | _         | _          | _            |         |         |        | 0000       |

| 2040                        | U3BRG <sup>(1)</sup>  | 15:0          |                                                                              |                                   |        |         |          |       | Bau   | d Rate Ge  | nerator Pre  | scaler   |           |            |              |         |         |        | 0000       |

| I                           |                       |               |                                                                              |                                   |        |         |          |       | 200   |            |              |          |           |            |              |         |         |        |            |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1: These registers have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# REGISTER 18-6: U1IR: USB INTERRUPT REGISTER (CONTINUED)

- bit 0 URSTIF: USB Reset Interrupt bit (Device mode)<sup>(5)</sup>

- 1 = Valid USB Reset has occurred

- 0 = No USB Reset has occurred

- DETACHIF: USB Detach Interrupt bit (Host mode)(6)

- 1 = Peripheral detachment was detected by the USB module

- 0 = Peripheral detachment was not detected

- **Note 1:** This bit is only valid if the HOSTEN bit is set (see Register 18-11), there is no activity on the USB for 2.5 μs and the current bus state is not SE0.

- **2:** When not in Suspend mode, this interrupt should be disabled.

- 3: Clearing this bit will cause the STAT FIFO to advance.

- 4: Only error conditions enabled through the U1EIE register will set this bit.

- 5: Device mode.

- 6: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 31:24        | —                 | _                 | —                    |                      | —                 | —                 | —                      | —                |

| 00.40        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 23:16        | —                 | —                 | —                    | —                    | —                 | —                 | —                      | —                |

| 45.0         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 15:8         | _                 | _                 | _                    | _                    | _                 | —                 | _                      | _                |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |

|              | DISEF             | DIVIAEE           | DIVIAET'             | DIVER                | DENOEF            | UKU IDEF          | EOFEF <sup>(3,5)</sup> | FIDEF            |

#### REGISTER 18-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to Clear bit | HS = Hardware Settable b  | bit                |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-8 Unimplemented: Read as '0'

- bit 7 **BTSEF:** Bit Stuff Error Flag bit

- 1 = Packet rejected due to bit stuff error

- 0 = Packet accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

- 1 = Invalid base address of the BDT or the address of an individual buffer pointed to by a BDT entry

- 0 = No address error

- bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup>

- 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out has occurred

- bit 3 DFN8EF: Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0                | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | ALRMEN            | CHIME             | —                 | —                 |                      | AMAS              | K<3:0>           |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | ALMRPT            | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | R/W-0                | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | —                 | —                 | WRLOCK               | —                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0                  | U-0               | U-0              | U-0              |

| 7:0          | RTCOE             |                   | OUTSEL<2:0        | >                 | _                    | _                 | _                | _                |

#### REGISTER 19-1: RTCCON1: RTCC CONTROL 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31 ALRMEN: Alarm Enable bit

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 30 CHIME: Chime Enable bit

- 1 = Chime is enabled; ALMRPT<7:0> bits are allowed to underflow from '00' to 'FF'

- 0 = Chime is disabled; ALMRPT<7:0> bits stop once they reach '00'

#### bit 29-28 Unimplemented: Read as '0'

- bit 27-24 **AMASK<3:0>:** Alarm Mask Configuration bits

- 11xx = Reserved, do not use

- 101x = Reserved, do not use

- 1001 = Once a year (or once every 4 years when configured for February 29th)

- 1000 = Once a month

- 0111 = Once a week

- 0110 = Once a day

- 0101 = Every hour

- 0100 = Every 10 minutes

- 0011 = Every minute

- 0010 = Every 10 seconds

- 0001 = Every second

- 0000 = Every half-second

#### bit 23-16 ALMRPT<7:0>: Alarm Repeat Counter Value bits<sup>(1)</sup>

11111111 = Alarm will repeat 255 more times

- 11111110 = Alarm will repeat 254 more times

- •••

00000010 = Alarm will repeat 2 more times

- 00000001 = Alarm will repeat 1 more time

- 00000000 = Alarm will not repeat

- bit 15 ON: RTCC Enable bit

1 = RTCC is enabled and counts from selected clock source

0 = RTCC is disabled

- bit 14-12 Unimplemented: Read as '0'

- **Note 1:** The counter decrements on any alarm event. The counter is prevented from rolling over from '00' to 'FF' unless CHIME = 1.

# REGISTER 20-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

| b | it 7-4  | SSRC<3:0>: Conversion Trigger Source Select bits          1111 = CLC2 module event ends sampling and starts conversion         110 = CLC1 module event ends sampling and starts conversion         1101 = SCCP6 module event ends sampling and starts conversion         1100 = SCCP5 module event ends sampling and starts conversion         1011 = SCCP4 module event ends sampling and starts conversion         1010 = SCCP5 module event ends sampling and starts conversion         1010 = MCCP3 module event ends sampling and starts conversion         1001 = MCCP2 module event ends sampling and starts conversion         1000 = MCCP1 module event ends sampling and starts conversion         1011 = Internal counter ends sampling and starts conversion         0110 = Timer1 period match ends sampling and starts conversion (auto-convert)         0111 = Timer1 period match ends sampling and starts conversion (will not trigger during Sleep mode)         0100-0011 = Reserved         0010 = Timer3 period match ends sampling and starts conversion         0010 = Timer3 period match ends sampling and starts conversion         0001 = Active transition on INT0 pin ends sampling and starts conversion         0000 = Clearing the SAMP bit ends sampling and starts conversion |

|---|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| b | it 3    | <b>MODE12:</b> 12-Bit Operation Mode bit<br>1 = 12-bit ADC operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   |         | 0 = 10-bit ADC operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| b | it 2    | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|   |         | <ul> <li>1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| b | it 1    | SAMP: ADC Sample Enable bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |         | <ul> <li>1 = The ADC Sample-and-Hold Amplifier (SHA) is sampling</li> <li>0 = The ADC SHA is holding</li> <li>When ASAM = 0, writing '1' to this bit starts sampling. When SSRC&lt;3:0 = 0000, writing '0' to this bit will end sampling and start conversion.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| b | it 0    | DONE: ADC Conversion Status bit <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |         | 1 = Analog-to-Digital conversion is done                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   |         | <ul> <li>analog-to-Digital conversion is not done or has not started</li> <li>Clearing this bit will not affect any operation in progress.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| N | loto 1. | The DONE bit is not persistent in Automatic modes: it is cleared by bardware at the beginning of the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

- **Note 1:** The DONE bit is not persistent in Automatic modes; it is cleared by hardware at the beginning of the next sample.

- 2: The SAMP bit is cleared and cannot be written if the ADC is disabled (ON bit = 0).

# 21.1 Control Registers

The CLCx module is controlled by the following registers:

- CLCxCON

- CLCxSEL

- CLCxGLS

The CLCx Control register (CLCxCON) is used to enable the module and interrupts, control the output enable bit, select output polarity and select the logic function. The CLCx Control registers also allow the user to control the logic polarity of not only the cell output, but also some intermediate variables. The CLCx Source Select register (CLCxSEL) allows the user to select up to 4 data input sources using the 4 data input selection multiplexers. Each multiplexer has a list of 8 data sources available.

The CLCx Gate Logic Select register (CLCxGLS) allows the user to select which outputs from each of the selection MUXes are used as inputs to the input gates of the logic cell. Each data source MUX outputs both a true and a negated version of its output. All of these 8 signals are enabled, ORed together by the logic cell input gates.

# 24.1 High/Low-Voltage Detect Registers

# TABLE 24-1: HIGH/LOW-VOLTAGE DETECT REGISTER MAP

| ess                      |                                 |           |       |       |       |       |       |       |       | Bit   | s    |      |      |      |      |       |       |      | ş         |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-------|-------|------|-----------|

| Virtual Addr<br>(BF80 #) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1  | 16/0 | All Reset |

| 2020                     |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _     | _     | _    | _    | _    | -    |      | _     | _     | _    | 0000      |

| 2920                     | HLVDCON                         | 15:0      | ON    |       | SIDL  | _     | VDIR  | BGVST | IRVST | HLEVT | _    | _    | _    | _    |      | HLVDL | <3:0> |      | 0000      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at its virtual address, plus offsets of 0x4, 0x8 and 0xC, respectively.

#### TABLE 26-4: ALTERNATE CONFIGURATION WORDS SUMMARY

| ess                         |                  |           |         |          |        |         |       |            |       | Bits    |        |         |         |        |         |          |          |        |

|-----------------------------|------------------|-----------|---------|----------|--------|---------|-------|------------|-------|---------|--------|---------|---------|--------|---------|----------|----------|--------|

| Virtual Address<br>(BFC0_#) | Register<br>Name | Bit Range | 31\15   | 30/14    | 29/13  | 28/12   | 27/11 | 26/10      | 25/9  | 24/8    | 23/7   | 22/6    | 21/5    | 20/4   | 19/3    | 18/2     | 17/1     | 16/0   |

| 1740                        | RESERVED         | 31:16     | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1740                        | RESERVED         | 15:0      | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1744                        | AFDEVOPT         | 31:16     |         |          |        |         |       |            | U     | SERID<1 | 15:0>  |         |         |        |         |          |          |        |

| 1744                        | AI DE VOF I      | 15:0      | FVBUSIO | FUSBIDIO | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | ALTI2C | SOSCHP  | r-1      | r-1      | r-1    |

| 1748                        | AFICD            | 31:16     | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1740                        | ALICD            | 15:0      | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | ICS    | <1:0>   | JTAGEN   | r-1      | r-1    |

| 174C                        | AFPOR            | 31:16     | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1/40                        | ALLON            | 15:0      | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | LPBOREN | RETVR    | BOREN    | l<1:0> |

| 1750                        | AFWDT            | 31:16     | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1750                        | AIWDI            | 15:0      | FWDTEN  | RCLKSE   | L<1:0> |         | R     | WDTPS<4:0> |       |         | WINDIS | FWDTWIN | SZ<1:0> |        | SW      | DTPS<4:0 | >        |        |

| 1754                        | AFOSCSEL         | 31:16     | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 17.54                       | AI USUSEE        | 15:0      | FCKSM   | <1:0>    | r-1    | SOSCSEL | r-1   | OSCIOFNC   | POSCM | OD<1:0> | IESO   | SOSCEN  | r-1     | PLLSRC | r-1     | FI       | NOSC<2:0 | >      |

| 1758                        | AFSEC            | 31:16     | CP      | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1750                        | AI SEC           | 15:0      | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 175C                        | RESERVED         | 31:16     | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1750                        | RESERVED         | 15:0      | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1760                        | RESERVED         | 31:16     | r-0     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1700                        | NEGENVED         | 15:0      | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1764                        | RESERVED         | 31:16     | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

| 1704                        | RESERVED         | 15:0      | r-1     | r-1      | r-1    | r-1     | r-1   | r-1        | r-1   | r-1     | r-1    | r-1     | r-1     | r-1    | r-1     | r-1      | r-1      | r-1    |

Legend: r-0 = Reserved bit, must be programmed as '0'; r-1 = Reserved bit, must be programmed as '1'.

#### **REGISTER 26-4: FWDT/AFWDT: WATCHDOG TIMER CONFIGURATION REGISTER (CONTINUED)**

- bit 6-5 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Watchdog Timer window size is 25%

- 10 = Watchdog Timer window size is 37.5%

- 01 = Watchdog Timer window size is 50%

- 00 = Watchdog Timer window size is 75%

- bit 4-0 SWDTPS<4:0>: Sleep Mode Watchdog Timer Postscale Select bits

From 10100 to 11111 = 1:1048576. 10011 = 1:524288 10010 = 1:262144 10001 = 1:13107210000 = 1:65536 01111 = 1:32768 01110 = 1:16384 01101 = 1:8192 01100 = 1:4096 01011 = 1:2048 01010 = 1:1024 01001 = 1:512 01000 = 1:256 00111 = 1:128 00110 = 1:64 00101 = 1:32 00100 = 1:16 00011 = 1:8 00010 = 1:4 00001 = 1:2 00000 = 1:1

# TABLE 26-7: UNIQUE DEVICE IDENTIFIER (UDID) REGISTER MAP

| ess                         |                  | e             |       |       |       |       |       |       |      | В       | its        |      |      |      |      |      |      |      |              |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|---------|------------|------|------|------|------|------|------|------|--------------|

| Virtual Address<br>(BF84_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8    | 23/7       | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets   |

| 1840                        | UDID1            | 31:16<br>15:0 |       |       |       |       |       |       |      | UDID Wo | rd 1<31:0> |      |      |      |      |      |      |      | xxxx<br>xxxx |

| 1844                        | UDID2            | 31:16<br>15:0 |       |       |       |       |       |       |      | UDID Wo | rd 2<31:0> |      |      |      |      |      |      |      | xxxx<br>xxxx |

| 1848                        | UDID3            | 31:16<br>15:0 |       |       |       |       |       |       |      | UDID Wo | rd 3<31:0> |      |      |      |      |      |      |      | xxxx<br>xxxx |

| 184C                        | UDID4            | 31:16<br>15:0 |       |       |       |       |       |       |      | UDID Wo | rd 4<31:0> |      |      |      |      |      |      |      | xxxx<br>xxxx |

| 1850                        | UDID5            | 31:16<br>15:0 |       |       |       |       |       |       |      | UDID Wo | rd 5<31:0> |      |      |      |      |      |      |      | xxxx<br>xxxx |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# TABLE 26-8: RESERVED REGISTERS MAP

| ess                       |                  | Ð             |       |       |       |       |       |       |      | Bi         | ts         |      |      |      |      |      |      |      | s          |

|---------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------------|------------|------|------|------|------|------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7       | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2900                      | RESERVED1        | 31:16<br>15:0 |       |       |       |       |       |       | Res  | served Reg | ister 1<31 | :0>  |      |      |      |      |      |      | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| DC CH        | ARACTER | RISTICS                                                               | Standard O<br>Operating te |                    |            |        | 3.6V (unless otherwise stated) $\leq T_A \leq +85^{\circ}C$ |

|--------------|---------|-----------------------------------------------------------------------|----------------------------|--------------------|------------|--------|-------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristic                                                        | Min                        | Typ <sup>(1)</sup> | Мах        | Units  | Conditions                                                  |

|              | VIL     | Input Low Voltage <sup>(3)</sup>                                      |                            |                    |            |        |                                                             |

| DI10         |         | I/O Pins with ST Buffer                                               | Vss                        |                    | 0.2 Vdd    | V      |                                                             |

| DI15         |         | MCLR                                                                  | Vss                        |                    | 0.2 Vdd    | V      |                                                             |

| DI16         |         | OSC1 (XT mode)                                                        | Vss                        |                    | 0.2 Vdd    | V      |                                                             |

| DI17         |         | OSC1 (HS mode)                                                        | Vss                        | _                  | 0.2 Vdd    | V      |                                                             |

|              | Vih     | Input High Voltage <sup>(3)</sup>                                     |                            |                    |            |        |                                                             |

| DI20         |         | I/O Pins with ST Buffer:<br>Without 5V Tolerance<br>With 5V Tolerance | 0.8 Vdd<br>0.8 Vdd         |                    | VDD<br>5.5 | V<br>V |                                                             |

| DI25         |         | MCLR                                                                  | 0.8 VDD                    |                    | Vdd        | V      |                                                             |

| DI26         |         | OSCI (XT mode)                                                        | 0.7 Vdd                    |                    | Vdd        | V      |                                                             |

| DI27         |         | OSCI (HS mode)                                                        | 0.7 VDD                    | _                  | Vdd        | V      |                                                             |

| DI30         | ICNPU   | CNPUx Pull-up Current                                                 | 150                        | 350                | 450        | μA     | Vdd = 3.3V, Vpin = Vss                                      |

| DI30A        | ICNPD   | CNPDx Pull-Down Current                                               | 230                        | 300                | 500        | μA     | Vdd = 3.3V, Vpin = Vdd                                      |

| DI50         | lı∟     | Input Leakage Current <sup>(2)</sup><br>I/O Pins – 5V Tolerant        | _                          | _                  | 1          | μΑ     | $Vss \le VPIN \le VDD,$ pin at high-impedance               |

| DI51         |         | I/O Pins – Not 5V Tolerant                                            | —                          | —                  | 1          | μA     | $Vss \le VPIN \le VDD,$ pin at high-impedance               |

| DI55         |         | MCLR                                                                  | —                          | —                  | 1          | μA     | $Vss \leq V \text{PIN} \leq V \text{DD}$                    |

| DI56         |         | OSC1/CLKI                                                             | _                          | _                  | 1          | μΑ     | Vss $\leq$ VPIN $\leq$ VDD, XT and HS modes                 |

### TABLE 29-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in the "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: Negative current is defined as current sourced by the pin.

**3:** Refer to Table 1-1 for I/O pin buffer types.

### TABLE 29-9: DC CHARACTERISTICS: I/O PIN INPUT INJECTION CURRENT SPECIFICATIONS

| DC CHA       | ARACTER | RISTICS                                                               | Standard Ope<br>Operating ter | -                      |                       |       | .6V (unless otherwise stated) $T_A \le +85^{\circ}C$                                                                                                     |

|--------------|---------|-----------------------------------------------------------------------|-------------------------------|------------------------|-----------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No. | Symbol  | Characteristics                                                       | Min.                          | Typical <sup>(1)</sup> | Max.                  | Units | Conditions                                                                                                                                               |

| DI60a        | licl    | Input Low Injection<br>Current                                        | 0                             |                        | _5(2,5)               | mA    | This parameter applies to all pins. Maximum IICH current for this exception is 0 mA.                                                                     |

| DI60b        | Іісн    | Input High Injection<br>Current                                       | 0                             | _                      | +5 <sup>(3,4,5)</sup> | mA    | This parameter applies to all<br>pins, with the exception of all<br>5V tolerant pins and SOSCI.<br>Maximum IICH current for these<br>exceptions is 0 mA. |

| DI60c        | ∑IICT   | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(6)</sup>            | _                      | +20 <sup>(6)</sup>    | mA    | Absolute instantaneous sum of<br>all $\pm$ input injection currents<br>from all I/O pins:<br>(   IICL +   IICH   ) $\leq \sum$ IICT                      |

**Note 1:** Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: VIL Source < (Vss 0.3). Characterized but not tested.

- 3: VIH Source > (VDD + 0.3) for non-5V tolerant pins only.

- 4: Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- 5: Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL Source < (VSS − 0.3)).</p>

- 6: Any number and/or combination of I/O pins, not excluded under IICL or IICH conditions, are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 2, IICL = (((VSS 0.3) VIL Source)/RS). If Note 3, IICH = (((IICH Source (VDD + 0.3))/RS). RS = Resistance between input source voltage and device pin. If (VSS 0.3) ≤ VSOURCE ≤ (VDD + 0.3), Injection Current = 0.

| АС СН        | ARACTE  | RISTICS         |                           | Standard Operating C<br>Operating temperatur |      |       | <b>3.6V (unless otherwise stated)</b><br>$\leq TA \leq +85^{\circ}C$ |

|--------------|---------|-----------------|---------------------------|----------------------------------------------|------|-------|----------------------------------------------------------------------|

| Param<br>No. | Sym     | Charact         | eristics                  | Min. <sup>(1)</sup>                          | Max. | Units | Conditions                                                           |

| IM25         | TSU:DAT | Data Input      | 100 kHz mode              | 250                                          | _    | ns    |                                                                      |