#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

$\mathbf{X}$

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® microAptiv™                                                              |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 25MHz                                                                            |

| Connectivity               | IrDA, LINbus, SPI, UART/USART, USB, USB OTG                                      |

| Peripherals                | Brown-out Detect/Reset, DMA, HLVD, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 38                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 32K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                        |

| Data Converters            | A/D 17x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 48-UFQFN Exposed Pad                                                             |

| Supplier Device Package    | 48-UQFN (6x6)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mm0256gpm048-i-m4 |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector, and the JTAG pins on the device, as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits, and pin Input Voltage High (VIH) and Input Voltage Low (VIL) requirements.

# 2.7 External Oscillator Pins

This family of devices has options for two external oscillators: a high-frequency Primary Oscillator and a low-frequency Secondary Oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

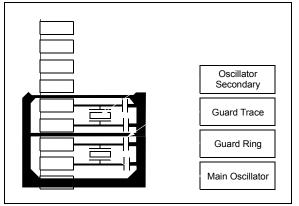

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-5. For additional information and design guidance on oscillator circuits, please refer to these Microchip Application Notes, available at the corporate web site: (www.microchip.com).

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849, "Basic PICmicro® Oscillator Design"

- AN943, "Practical PICmicro<sup>®</sup> Oscillator Analysis and Design"

- AN949, "Making Your Oscillator Work"

### FIGURE 2-5: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.8 Unused I/Os

To minimize power consumption, unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic low or logic high state.

Alternatively, inputs can be reserved by ensuring the pin is always configured as an input and externally connecting the pin to Vss or VDD. A current-limiting resistor may be used to create this connection if there is any risk of inadvertently configuring the pin as an output with the logic output state opposite of the chosen power rail. NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | —                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | -                 | —                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | —                 | -                 | -                 | —                 | _                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0               | R-1               | R-0               | R-0               | R-1              | R-0              |

| 7:0          | _                 | _                 |                   | PC                | WR                | CA                | EP               | FP               |

## REGISTER 3-2: CONFIG1: CONFIGURATION REGISTER 1; CP0 REGISTER 16, SELECT 1

| Legend:           | r = Reserved bit |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 **Reserved:** This bit is hardwired to '1' to indicate the presence of the CONFIG2 register

- bit 30-5 Unimplemented: Read as '0'

- bit 4 **PC:** Performance Counter bit

- 1 = The processor core contains performance counters

- bit 3 WR: Watch Register Presence bit

- 0 = No Watch registers are present

- bit 2 CA: Code Compression Implemented bit

- 0 = No MIPS16e<sup>®</sup> are present

- bit 1 EP: EJTAG Present bit

- 1 = Core implements EJTAG

- bit 0 **FP:** Floating Point Unit bit

- 0 = Floating point unit is not implemented

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | r-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | -                | —                |

| 00.40        | U-0               | R-0               | R-1               | R-0               | R-0               | R-0               | R-1              | R-1              |

| 23:16        | _                 | IPLW              | <1:0>             |                   | MMAR<2:0>         |                   | MCU              | ISAONEXC         |

| 45.0         | R-0               | R-1               | R-1               | R-1               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | ISA<              | :1:0>             | ULRI              | RXI               | —                 | _                 | _                | ITL              |

| 7.0          | U-0               | R-1               | R-1               | R-0               | R-1               | U-0               | U-0              | R-0              |

| 7:0          | _                 | VEIC              | VINT              | SP                | CDMM              |                   |                  | TL               |

### REGISTER 3-3: CONFIG3: CONFIGURATION REGISTER 3; CP0 REGISTER 16, SELECT 3

| Legend:           | r = Reserved bit | y = Value set from Configuration bits on POR |                    |  |  |  |

|-------------------|------------------|----------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'           |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                         | x = Bit is unknown |  |  |  |

| bit 31    | Reserved: This bit is hardwired as '0'                           |

|-----------|------------------------------------------------------------------|

| bit 30-23 | Unimplemented: Read as '0'                                       |

| bit 22-21 | IPLW<1:0>: Width of the Status IPL and Cause RIPL bits           |

|           | 01 = IPL and RIPL bits are 8 bits in width                       |

| bit 20-18 | MMAR<2:0>: microMIPS™ Architecture Revision Level bits           |

|           | 000 = Release 1                                                  |

| bit 17    | MCU: MIPS <sup>®</sup> MCU ASE Implemented bit                   |

|           | 1 = MCU ASE is implemented                                       |

| bit 16    | ISAONEXC: ISA on Exception bit                                   |

|           | 1 = microMIPS is used on entrance to an exception vector         |

| bit 15-14 | ISA<1:0>: Instruction Set Availability bits                      |

|           | 01 = Only microMIPS is implemented                               |

| bit 13    | ULRI: UserLocal Register Implemented bit                         |

|           | 1 = UserLocal Coprocessor 0 register is implemented              |

| bit 12    | RXI: RIE and XIE Implemented in PageGrain bit                    |

|           | 1 = RIE and XIE bits are implemented                             |

| bit 11-9  | Unimplemented: Read as '0'                                       |

| bit 8     | ITL: Indicates that iFlowtrace™ Hardware is Present bit          |

|           | 0 = The iFlowtrace hardware is not implemented in the core       |

| bit 7     | Unimplemented: Read as '0'                                       |

| bit 6     | VEIC: External Vector Interrupt Controller bit                   |

|           | 1 = Support for an external interrupt controller is implemented. |

| bit 5     | VINT: Vector Interrupt bit                                       |

|           | 1 = Vector interrupts are implemented                            |

| bit 4     | SP: Small Page bit                                               |

|           | 0 = 4-Kbyte page size                                            |

| bit 3     | CDMM: Common Device Memory Map bit                               |

|           | 1 = CDMM is implemented                                          |

| bit 2-1   | Unimplemented: Read as '0'                                       |

| bit 0     | TL: Trace Logic bit                                              |

|           | 0 = Trace logic is not implemented                               |

# TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)

| ess                         |                                 | Ð         |       |       |       |             |             |             |        | Bits        |      |             |      |             |            |             |        |        | s           |   |      |   |            |   |        |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------|-------------|-------------|--------|-------------|------|-------------|------|-------------|------------|-------------|--------|--------|-------------|---|------|---|------------|---|--------|--------|------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12       | 27/11       | 26/10       | 25/9   | 24/8        | 23/7 | 22/6        | 21/5 | 20/4        | 19/3       | 18/2        | 17/1   | 16/0   | All Resets  |   |      |   |            |   |        |        |      |

| F200                        | IPC20                           | 31:16     | _     | _     |       |             | CCT5IP<2:0> | >           | CCT5IS | 6<1:0>      |      | —           | _    | C           | CCP5IP<2:0 | >           | CCP5IS | 6<1:0> | 0000        |   |      |   |            |   |        |        |      |

| F200                        | IFC20                           | 15:0      | _     | _     | _     |             | CCT4IP<2:0> |             | CCT4IS | S<1:0>      | _    | —           | —    | C           | CCP4IP<2:0 | >           | CCP4IS | 6<1:0> | 0000        |   |      |   |            |   |        |        |      |

| F210                        | IPC21                           | 31:16     | _     | -     |       |             | CCT7IP<2:0> |             | CCT7IS | S<1:0>      |      | —           | _    | CCP7IP<2:0> |            | CCP7IP<2:0> |        | >      | CCP7IS<1:0> |   | 0000 |   |            |   |        |        |      |

| F210                        | IPGZI                           | 15:0      | _     |       |       |             | CCT6IP<2:0> |             | CCT6IS | S<1:0>      |      | _           | _    | CCP6IP<2:0> |            | CCP6IS<1:0> |        | 0000   |             |   |      |   |            |   |        |        |      |

| F220                        | IPC22                           | 31:16     |       | -     | -     |             | CCT9IP<2:0> | <b>`</b>    | CCT9IS | S<1:0>      | -    | —           | _    | C           | CCP9IP<2:0 | >           | CCP9IS | S<1:0> | 0000        |   |      |   |            |   |        |        |      |

| F220                        | IFUZZ                           | 15:0      | _     | -     |       |             | CCT8IP<2:0> |             | CCT8IS | S<1:0>      |      | —           | _    | C           | CCP8IP<2:0 | >           | CCP8IS | S<1:0> | 0000        |   |      |   |            |   |        |        |      |

| F230                        | IPC23                           | 31:16     | _     |       |       |             | CPCIP<2:0>  |             | CPCIS  | <1:0>       |      | _           | _    | I           | NVMIP<2:0> | •           | NVMIS  | <1:0>  | 0000        |   |      |   |            |   |        |        |      |

| F230                        | IP025                           | 15:0      |       | -     | -     | —           | -           |             | —      |             | -    | —           | _    |             | FSTIP<2:0> |             | FSTIS  | <1:0>  | 0000        |   |      |   |            |   |        |        |      |

| F240                        | IPC24                           | 31:16     | _     | _     |       | DMA1IP<2:0> |             | DMA1IP<2:0> |        | DMA1IP<2:0> |      | DMA1IP<2:0> |      | DMA1IP<2:0> |            | DMA1IP<2:0> |        | S<1:0> |             | _ | _    | C | 0MA0IP<2:0 | > | DMA0IS | S<1:0> | 0000 |

| F240                        | IP024                           | 15:0      |       | -     | -     |             | ECCBEIP<2:0 | >           | ECCBEI | S<1:0>      | -    | —           | _    | -           | _          | -           | _      | _      | 0000        |   |      |   |            |   |        |        |      |

| F250                        | IPC25                           | 31:16     | _     | _     | _     | _           | _           | _           | _      | _           | _    | _           | _    | _           | _          | _           |        | _      | 0000        |   |      |   |            |   |        |        |      |

| F250                        | IF-625                          | 15:0      | _     | _     | _     |             | DMA3IP<2:0  | >           | DMA3IS | S<1:0>      | _    | —           |      | C           | MA2IP<2:0  | >           | DMA2IS | S<1:0> | 0000        |   |      |   |            |   |        |        |      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# TABLE 8-2: DMA CHANNELS 0-3 REGISTER MAP (CONTINUED)

| Ś                           |                                 |               |             |                   |       |       |             |       |      |             | D:4-             |                  |                 |                  |                  |        |             |             |              |

|-----------------------------|---------------------------------|---------------|-------------|-------------------|-------|-------|-------------|-------|------|-------------|------------------|------------------|-----------------|------------------|------------------|--------|-------------|-------------|--------------|

| ()                          | <b>b</b> -                      | Ð             |             |                   | 1     |       |             | 1     | 1    | 1           | Bits             |                  | 1               | 1                | 1                | 1      | 1           | 1           | - vi         |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14             | 29/13 | 28/12 | 27/11       | 26/10 | 25/9 | 24/8        | 23/7             | 22/6             | 21/5            | 20/4             | 19/3             | 18/2   | 17/1        | 16/0        | All Resets   |

| 8A50                        | DCH1SSA                         | 31:16<br>15:0 |             | CHSSA<31:0>       |       |       |             |       |      |             |                  |                  |                 | 0000             |                  |        |             |             |              |

| 8A60                        | DCH1DSA                         | 31:16<br>15:0 |             |                   |       |       |             |       |      | CHD         | SA<31:0>         |                  |                 |                  |                  |        |             |             | 0000         |

| 8A70                        | DCH1SSIZ                        | 31:16<br>15:0 | _           | _                 | _     | _     | _           | —     | _    | CHSS        | —<br>SIZ<15:0>   | _                | _               | _                | _                | _      | _           | _           | 0000         |

| 8A80                        | DCH1DSIZ                        | 31:16<br>15:0 | —           | _                 | —     | —     | _           | —     | —    | —<br>CHDS   | —<br>SIZ<15:0>   | —                | —               | —                | —                | —      | —           | —           | 0000         |

| 8A90                        | DCH1SPTR                        | 31:16<br>15:0 | _           | _                 | _     | —     | _           |       | _    | —<br>CHSP   | —<br>TR<15:0>    | —                | —               | —                | —                | —      | _           | —           | 0000         |

| 8AA0                        | DCH1DPTR                        | 31:16<br>15:0 | —           | —                 | _     | _     |             | —     | _    | —           | —<br>TR<15:0>    | —                | —               | —                | —                | —      | —           | _           | 0000         |

| 8AB0                        | DCH1CSIZ                        | 31:16<br>15:0 | —           | —                 | —     | —     | —           | —     | —    | _           | —<br>SIZ<15:0>   | —                | —               | —                | —                | —      | —           | —           | 0000         |

| 8AC0                        | DCH1CPTR                        | 31:16<br>15:0 | _           | _                 | —     | —     | —           | —     | —    | —           | <br>TR<15:0>     | _                | _               | _                | _                | _      | _           | _           | 0000         |

| 8AD0                        | DCH1DAT                         | 31:16<br>15:0 | _           | _                 |       | _     | _           | —     | _    | _           | _                | —                | _               | —<br>CHPDA       | —<br>T<7:0>      | _      | _           | —           | 0000         |

| 8AE0                        | DCH2CON                         | 31:16         | _           | _                 | _     |       |             | _     | _    |             | _                | _                | _               |                  | —                | _      | _           | _           | 0000         |

| 8AF0                        | DCH2ECON                        | 15:0<br>31:16 | CHBUSY<br>— | _                 |       |       | _           | _     | _    | CHCHNS<br>— | CHEN             | CHAED            | CHCHN           | CHAEN<br>CHAIR   |                  | CHEDET | CHPR        | 1<1:0>      | 0000<br>00FF |

| 8B00                        | DCH2INT                         | 15:0<br>31:16 | _           | _                 | _     |       | Q<7:0><br>— | —     | —    | _           | CFORCE<br>CHSDIE | CABORT<br>CHSHIE | PATEN<br>CHDDIE | SIRQEN<br>CHDHIE | AIRQEN<br>CHBCIE |        | —<br>CHTAIE | —<br>CHERIE | FF00<br>0000 |

| 8B10                        | DCH2SSA                         | 15:0<br>31:16 |             |                   |       |       |             |       |      |             |                  | 0000             |                 |                  |                  |        |             |             |              |

| 8B20                        | DCH233A                         | 15:0<br>31:16 |             | 00                |       |       |             |       |      |             |                  |                  | 0000            |                  |                  |        |             |             |              |

|                             |                                 | 15:0<br>31:16 | 0000        |                   |       |       |             |       |      |             | 0000             |                  |                 |                  |                  |        |             |             |              |

| 8B30                        | DCH2SSIZ                        | 15:0          |             | CHSSIZ<15:0> 0000 |       |       |             |       |      |             |                  |                  |                 |                  |                  |        |             |             |              |

PIC32MM0256GPM064 FAMILY

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 10.1 "CLR, SET and INV Registers" for more information.

## TABLE 10-9: PERIPHERAL PIN SELECT REGISTER MAP (CONTINUED)

| ess                         |                                 | n         |       | Bits  |       |       |            |            |      |      |      |      |      |            |      | ú          |      |      |           |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|------------|------------|------|------|------|------|------|------------|------|------------|------|------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11      | 26/10      | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4       | 19/3 | 18/2       | 17/1 | 16/0 | All Reset |

| 00.40                       | 00000                           | 31:16     | _     | —     | —     |       | RP16R<4:0> |            |      |      |      | —    | —    |            |      | RP15R<4:0> | >    |      | 0000      |

| 2B40                        | RPOR3                           | 15:0      | _     | _     | —     |       |            | RP14R<4:0> |      |      | _    | _    | _    | RP13R<4:0> |      |            | 0000 |      |           |

| 0050                        | 00004                           | 31:16     | _     | _     | —     |       |            | RP20R<4:0> |      |      | _    | _    | _    | RP19R<4:0> |      |            |      | 0000 |           |

| 2B50                        | RPOR4                           | 15:0      | _     | _     | —     |       | RP18R<4:0> |            |      |      |      | _    | _    | RP17R<4:0> |      |            | 0000 |      |           |

| 2060                        | RPOR5                           | 31:16     | _     | _     | —     |       | RP24R<4:0> |            |      |      |      | _    | _    | RP23R<4:0> |      |            | 0000 |      |           |

| 2B60                        | RPURD                           | 15:0      | _     |       | —     |       | RP22R<4:0> |            |      |      |      |      | _    |            | _    | —          | _    | _    | 0000      |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

| Bit Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1           | Bit<br>24/16/8/0 |  |  |

|-----------|-----------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|----------------------------|------------------|--|--|

| 04.04     | R/W-0                 | R/W-0             | R/W-0             | R/W-0                 | U-0               | R/W-0             | R/W-0                      | R/W-0            |  |  |

| 31:24     | 31:24 OETRIG OSCNT<2: |                   |                   |                       | —                 | (                 | )                          |                  |  |  |

| 00.40     | U-0                   | U-0               | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0                      | R/W-0            |  |  |

| 23:16     | —                     | —                 | POLACE            | POLBDF <sup>(1)</sup> | PSSAC             | E<1:0>            | PSSBDF<1:0> <sup>(1)</sup> |                  |  |  |

| 45.0      | U-0                   | U-0               | U-0               | U-0                   | U-0               | U-0               | U-0                        | U-0              |  |  |

| 15:8      | —                     | —                 |                   | —                     |                   |                   |                            | —                |  |  |

| 7.0       | U-0                   | U-0               | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0                      | R/W-0            |  |  |

| 7:0       | _                     | _                 | DT<5:0>(1)        |                       |                   |                   |                            |                  |  |  |

## REGISTER 14-3: CCPxCON3: CAPTURE/COMPARE/PWMx CONTROL 3 REGISTER

| Legend: |

|---------|

|---------|

| Logonal                           |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31 **OETRIG:** PWM Dead-Time Select bit

1 = For Triggered mode (TRIGEN = 1), the module does not drive enabled output pins until triggered 0 = Normal output pin operation

### bit 30-28 **OSCNT<2:0>:** One-Shot Event Count bits

Extends the duration of a one-shot trigger event by an additional n clock cycles (n + 1 total cycles).

- 111 = 7 timer count periods (8 cycles total)

- 110 = 6 timer count periods (7 cycles total)

- 101 = 5 timer count periods (6 cycles total)

- 100 = 4 timer count periods (5 cycles total)

- 011 = 3 timer count periods (4 cycles total)

- 010 = 2 timer count periods (3 cycles total)

- 001 = 1 timer count period (2 cycles total)

- 000 = Does not extend the one-shot trigger event (the event takes 1 timer count period)

### bit 27 Unimplemented: Read as '0'

- bit 26-24 **OUTM<2:0>:** PWMx Output Mode Control bits<sup>(1)</sup>

- 111 = Reserved

- 110 = Output Scan mode

- 101 = Brush DC Output mode, forward

- 100 = Brush DC Output mode, reverse

- 011 = Reserved

- 010 = Half-Bridge Output mode

- 001 = Push-Pull Output mode

- 000 = Steerable Single Output mode

- bit 23-22 Unimplemented: Read as '0'

- bit 21 **POLACE:** CCPx Output Pins, OCxA, OCxC and OCxE, Polarity Control bit

- 1 = Output pin polarity is active-low

- 0 = Output pin polarity is active-high

- bit 20 **POLBDF:** CCPx Output Pins, OCxB, OCxD and OCxF, Polarity Control bit<sup>(1)</sup>

- 1 = Output pin polarity is active-low

- 0 = Output pin polarity is active-high

- **Note 1:** These bits are implemented in MCCP modules only.

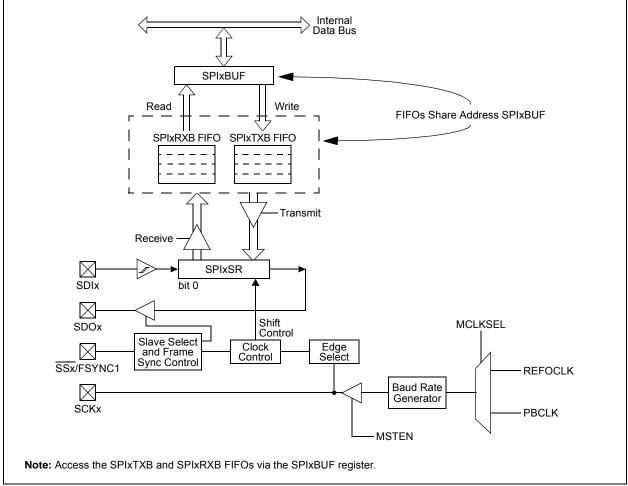

# 15.0 SERIAL PERIPHERAL INTERFACE (SPI) AND INTER-IC SOUND (I<sup>2</sup>S)

Note: This data sheet summarizes the features of the PIC32MM0256GPM064 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS61106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The information in this data sheet supersedes the information in the FRM.

The SPI/I<sup>2</sup>S module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices, as well

as digital audio devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, Analog-to-Digital Converters (ADC), etc.

The SPI/I<sup>2</sup>S module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

Some of the key features of the SPI module are:

- · Master and Slave modes Support

- Four Different Clock Formats

- Enhanced Framed SPI Protocol Support

- User-Configurable 8-Bit, 16-Bit and 32-Bit Data Width

- Separate SPI FIFO Buffers for Receive and Transmit:

FIFO buffers act as 4/8/16-level deep FIFOs

- FIFO buffers act as 4/8/10-level deep FIFOs based on 32/16/8-bit data width

- Programmable Interrupt Event on every 8-Bit, 16-Bit and 32-Bit Data Transfer

- Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

# PIC32MM0256GPM064 FAMILY

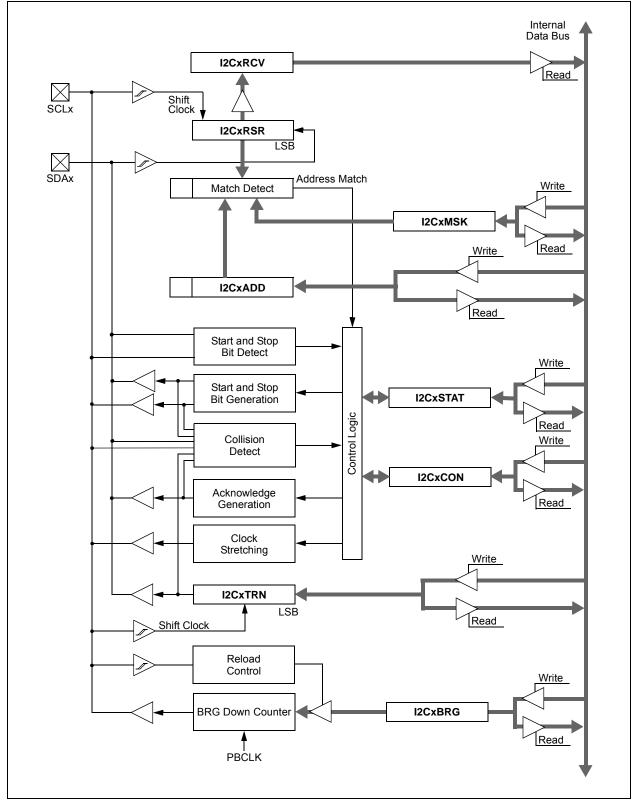

# FIGURE 16-1: I2Cx BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | -                | _                |

| 00.40        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | r-0              | r-0              |

| 23:16        | —                 | PCIE              | SCIE              | BOEN              | SDAHT             | SBCDE             | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON                | _                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

### REGISTER 16-1: I2CxCON: I2Cx CONTROL REGISTER

| Legend:           | r = Reserved bit | HC = Hardware Clear  | able bit           |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-23 Unimplemented: Read as '0'

| bit 22 | PCIE: Stop Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                  |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | <ul> <li>1 = Enables interrupt on detection of Stop condition</li> <li>0 = Stop detection interrupts are disabled</li> </ul>                                                                                                                                                                  |

| bit 21 | SCIE: Start Condition Interrupt Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                 |

|        | <ul> <li>1 = Enables interrupt on detection of Start or Restart conditions</li> <li>0 = Start detection interrupts are disabled</li> </ul>                                                                                                                                                    |

| bit 20 | <b>BOEN:</b> Buffer Overwrite Enable bit (I <sup>2</sup> C Slave mode only)                                                                                                                                                                                                                   |

|        | <ul> <li>1 = I2CxRCV is updated and an ACK is generated for a received address/data byte, ignoring the state of the I2COV bit (I2CxSTAT&lt;6&gt;) only if the RBF bit (I2CxSTAT&lt;1&gt;) = 0</li> <li>0 = I2CxRCV is only updated when the I2COV bit (I2CxSTAT&lt;6&gt;) is clear</li> </ul> |

| bit 19 | SDAHT: SDAx Hold Time Selection bit                                                                                                                                                                                                                                                           |

|        | 1 = Minimum of 300 ns hold time on SDAx after the falling edge of SCLx                                                                                                                                                                                                                        |

- 0 = Minimum of 100 ns hold time on SDAx after the falling edge of SCLx

- bit 18 **SBCDE:** Slave Mode Bus Collision Detect Enable bit (I<sup>2</sup>C Slave mode only)

- 1 = Enables slave bus collision interrupts

- 0 = Slave bus collision interrupts are disabled

- bit 17-16 **Reserved:** Maintain as '0'

- bit 15 ON: I2Cx Enable bit

- 1 = Enables the I2Cx module and configures the SDAx and SCLx pins as serial port pins

- 0 = Disables the I2Cx module; all I<sup>2</sup>C pins are controlled by port functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** I2Cx Stop in Idle Mode bit

- 1 = Discontinues module operation when device enters Idle mode

- 0 = Continues module operation in Idle mode

- bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Releases SCLx clock

- 0 = Holds SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware is clear at the beginning of slave transmission. Hardware is clear at the end of slave reception.

If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware is clear at the beginning of slave transmission.

# PIC32MM0256GPM064 FAMILY

### REGISTER 18-4: U1OTGCON: USB OTG CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   |                   |                   |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

### Legend:

| 3                 |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **DPPULUP:** D+ Pull-Up Enable bit

- 1 = D+ data line pull-up resistor is enabled

- 0 = D+ data line pull-up resistor is disabled

### bit 6 DMPULUP: D- Pull-Up Enable bit

- 1 = D- data line pull-up resistor is enabled

- 0 = D- data line pull-up resistor is disabled

### bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D+ data line pull-down resistor is enabled

- 0 = D+ data line pull-down resistor is disabled

### bit 4 DMPULDWN: D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

### bit 3 VBUSON: VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

- bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

### TABLE 20-1: ADC REGISTER MAP

| sse                         |                                 |               |       |                |       |       |       |       |      | Bits    | 6       |      |      |      |      |      |      |      |            |

|-----------------------------|---------------------------------|---------------|-------|----------------|-------|-------|-------|-------|------|---------|---------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(2)</sup> | Bit Range     | 31/15 | 30/14          | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2100                        | ADC1BUF0                        | 31:16<br>15:0 |       | ADC1BUF0<31:0> |       |       |       |       |      |         |         |      |      |      | 0000 |      |      |      |            |

| 2110                        | ADC1BUF1                        | 31:16<br>15:0 |       |                |       |       |       |       | ۵    | DC1BUF  | 1<31:0> |      |      |      |      |      |      |      | 0000       |

| 2120                        | ADC1BUF2                        | 31:16<br>15:0 |       |                |       |       |       |       | م    | DC1BUF  | 2<31:0> |      |      |      |      |      |      |      | 0000       |

| 2130                        | ADC1BUF3                        | 31:16<br>15:0 |       |                |       |       |       |       | A    | DC1BUF  | 3<31:0> |      |      |      |      |      |      |      | 0000       |

| 2140                        | ADC1BUF4                        | 31:16<br>15:0 |       |                |       |       |       |       | Α    | DC1BUF  | 4<31:0> |      |      |      |      |      |      |      | 0000       |

| 2150                        | ADC1BUF5                        | 31:16<br>15:0 |       |                |       |       |       |       | Δ    | DC1BUF  | 5<31:0> |      |      |      |      |      |      |      | 0000       |

| 2160                        | ADC1BUF6                        | 31:16<br>15:0 |       |                |       |       |       |       | ٨    | DC1BUF  | 6<31:0> |      |      |      |      |      |      |      | 0000       |

| 2170                        | ADC1BUF7                        | 31:16<br>15:0 |       |                |       |       |       |       | A    | DC1BUF  | 7<31:0> |      |      |      |      |      |      |      | 0000       |

| 2180                        | ADC1BUF8                        | 31:16<br>15:0 |       |                |       |       |       |       | Α    | DC1BUF  | 8<31:0> |      |      |      |      |      |      |      | 0000       |

| 2190                        | ADC1BUF9                        | 31:16<br>15:0 |       |                |       |       |       |       | Α    | DC1BUF  | 9<31:0> |      |      |      |      |      |      |      | 0000       |

| 21A0                        | ADC1BUF10                       | 31:16<br>15:0 |       |                |       |       |       |       | A    | DC1BUF1 | 0<31:0> |      |      |      |      |      |      |      | 0000       |

| 21B0                        | ADC1BUF11                       | 31:16<br>15:0 |       |                |       |       |       |       | A    | DC1BUF1 | 1<31:0> |      |      |      |      |      |      |      | 0000       |

| 21C0                        | ADC1BUF12                       | 31:16<br>15:0 |       |                |       |       |       |       | A    | DC1BUF1 | 2<31:0> |      |      |      |      |      |      |      | 0000       |

| 21D0                        | ADC1BUF13                       | 31:16<br>15:0 |       |                |       |       |       |       | A    | DC1BUF1 | 3<31:0> |      |      |      |      |      |      |      | 0000       |

| 21E0                        | ADC1BUF14                       | 31:16<br>15:0 |       |                |       |       |       |       | A    | DC1BUF1 | 4<31:0> |      |      |      |      |      |      |      | 0000       |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The CSS<19:12> bits are not implemented in 28-pin devices. The CSS<19:15> bits are not implemented in 36-pin and 40-pin devices. The CSS<17:14> bits are not implemented in 48-pin devices.

2: All registers in this table have corresponding CLR, SET and INV registers at their virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively.

# 25.5 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not take effect and read values are invalid.

To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). To prevent accidental configuration changes under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK bit in the PMDCON register (PMDCON<11>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes. To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 26.4 "System Registers Write Protection"** for details.

Table 25-1 lists the module disable bits locations for all modules.

| Peripheral                                               | PMDx Bit Name | Register Name and Bit Location |

|----------------------------------------------------------|---------------|--------------------------------|

| Analog-to-Digital Converter (ADC)                        | ADCMD         | PMD1<0>                        |

| Voltage Reference (VR)                                   | VREFMD        | PMD1<12>                       |

| High/Low-Voltage Detect (HLVD)                           | HLVDMD        | PMD1<20>                       |

| Comparator 1 (CMP1)                                      | CMP1MD        | PMD2<0>                        |

| Comparator 2 (CMP2)                                      | CMP2MD        | PMD2<1>                        |

| Comparator 3 (CMP3)                                      | CMP3MD        | PMD2<2>                        |

| Configurable Logic Cell 1 (CLC1)                         | CLC1MD        | PMD2<24>                       |

| Configurable Logic Cell 2 (CLC2)                         | CLC2MD        | PMD2<25>                       |

| Configurable Logic Cell 3 (CLC3)                         | CLC3MD        | PMD2<26>                       |

| Configurable Logic Cell 4 (CLC4)                         | CLC4MD        | PMD2<27>                       |

| Multiple Outputs Capture/Compare/PWM/<br>Timer1 (MCCP1)  | CCP1MD        | PMD3<8>                        |

| Multiple Outputs Capture/Compare/PWM/<br>Timer2 (MCCP2)  | CCP2MD        | PMD3<9>                        |

| Multiple Outputs Capture/Compare/PWM/<br>Timer3 (MCCP3)  | CCP3MD        | PMD3<10>                       |

| Single Output Capture/Compare/PWM/<br>Timer4 (SCCP4)     | CCP4MD        | PMD3<11>                       |

| Single Output Capture/Compare/PWM/<br>Timer5 (SCCP5)     | CCP5MD        | PMD3<12>                       |

| Single Output Capture/Compare/PWM/<br>Timer6 (SCCP6)     | CCP6MD        | PMD3<13>                       |

| Single Output Capture/Compare/PWM/<br>Timer7 (SCCP7)     | CCP7MD        | PMD3<14>                       |

| Single Output Capture/Compare/PWM/<br>Timer8 (SCCP8)     | CCP8MD        | PMD3<15>                       |

| Single Output Capture/Compare/PWM/<br>Timer9 (SCCP9)     | CCP9MD        | PMD3<16>                       |

| Timer1 (TMR1)                                            | T1MD          | PMD4<0>                        |

| Timer2 (TMR2)                                            | T2MD          | PMD4<1>                        |

| Timer3 (TMR3)                                            | T3MD          | PMD4<2>                        |

| Universal Asynchronous Receiver<br>Transmitter 1 (UART1) | U1MD          | PMD5<0>                        |

### TABLE 25-1: PERIPHERAL MODULE DISABLE BITS AND LOCATIONS

# 27.0 INSTRUCTION SET

The PIC32MM0256GPM064 family instruction set complies with the MIPS<sup>®</sup> Release 3 instruction set architecture. Only microMIPS32<sup>™</sup> instructions are supported. The PIC32MM0256GPM064 family does not have the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

| Note: | Refer to the "MIPS® Architecture for |  |  |  |  |  |  |  |  |

|-------|--------------------------------------|--|--|--|--|--|--|--|--|

|       | Programmers Volume II-B: The         |  |  |  |  |  |  |  |  |

|       | microMIPS32™ Instruction Set" at     |  |  |  |  |  |  |  |  |

|       | www.imgtec.com for more information. |  |  |  |  |  |  |  |  |

| АС СНА       | RACTERIST             | rics                                                  | Standard Operating Conditions:2.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |                        |      |       |                    |  |  |

|--------------|-----------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|

| Param<br>No. | Symbol                | Characteristics <sup>(1)</sup>                        | Min.                                                                                                                             | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP70         | TscL                  | SCKx Input Low Time <sup>(3)</sup>                    | Tsck/2                                                                                                                           | _                      | _    | ns    |                    |  |  |

| SP71         | TscH                  | SCKx Input High Time <sup>(3)</sup>                   | Tsck/2                                                                                                                           | _                      |      | ns    |                    |  |  |

| SP72         | TscF                  | SCKx Input Fall Time                                  | _                                                                                                                                | _                      | 10   | ns    |                    |  |  |

| SP73         | TscR                  | SCKx Input Rise Time                                  | _                                                                                                                                | _                      | 10   | ns    |                    |  |  |

| SP30         | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>             | _                                                                                                                                | —                      | _    | ns    | See Parameter DO32 |  |  |

| SP31         | TDOR                  | SDOx Data Output Rise Time <sup>(4)</sup>             | _                                                                                                                                | _                      | _    | ns    | See Parameter DO31 |  |  |

| SP35         | TscH2doV,             | SDOx Data Output Valid after                          | _                                                                                                                                | —                      | 10   | ns    | VDD > 2.0V         |  |  |

|              | TscL2DoV              | SCKx Edge                                             | _                                                                                                                                | —                      | 15   | ns    | VDD < 2.0V         |  |  |

| SP40         | TDIV2sCH,<br>TDIV2sCL | Setup Time of SDIx Data Input to SCKx Edge            | 0                                                                                                                                | —                      | _    | ns    |                    |  |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge             | 7                                                                                                                                | —                      |      | ns    |                    |  |  |

| SP50         | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↓ or<br>SCKx ↑ Input                    | 88                                                                                                                               | _                      | _    | ns    |                    |  |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 2.5                                                                                                                              | —                      | 12   | ns    |                    |  |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                 | 10                                                                                                                               | —                      | _    | ns    |                    |  |  |

| SP60         | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge              | _                                                                                                                                | —                      | 12.5 | ns    |                    |  |  |

# TABLE 29-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in the "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

**4:** Assumes 10 pF load on all SPIx pins.

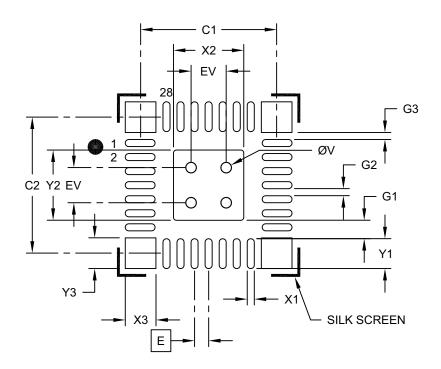

# 28-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M6) - 4x4x0.6 mm Body [UQFN] With Corner Anchors

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## **RECOMMENDED LAND PATTERN**

|                                 | MILLIMETERS |      |          |      |  |

|---------------------------------|-------------|------|----------|------|--|

| Dimension                       | MIN         | NOM  | MAX      |      |  |

| Contact Pitch                   | E           |      | 0.40 BSC |      |  |

| Center Pad Width                | X2          |      |          | 2.00 |  |

| Center Pad Length               | Y2          |      |          | 2.00 |  |

| Contact Pad Spacing             | C1          |      | 3.90     |      |  |

| Contact Pad Spacing             | C2          |      | 3.90     |      |  |

| Contact Pad Width (X28)         | X1          |      |          | 0.20 |  |

| Contact Pad Length (X28)        | Y1          |      |          | 0.85 |  |

| Contact Pad to Center Pad (X28) | G1          |      | 0.52     |      |  |

| Contact Pad to Pad (X24)        | G2          | 0.20 |          |      |  |

| Contact Pad to Corner Pad (X8)  | G3          | 0.20 |          |      |  |

| Corner Anchor Width (X4)        | X3          |      |          | 0.78 |  |

| Corner Anchor Length (X4)       | Y3          |      |          | 0.78 |  |

| Thermal Via Diameter            | V           |      | 0.30     |      |  |

| Thermal Via Pitch               | EV          |      | 1.00     |      |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2333-M6 Rev B

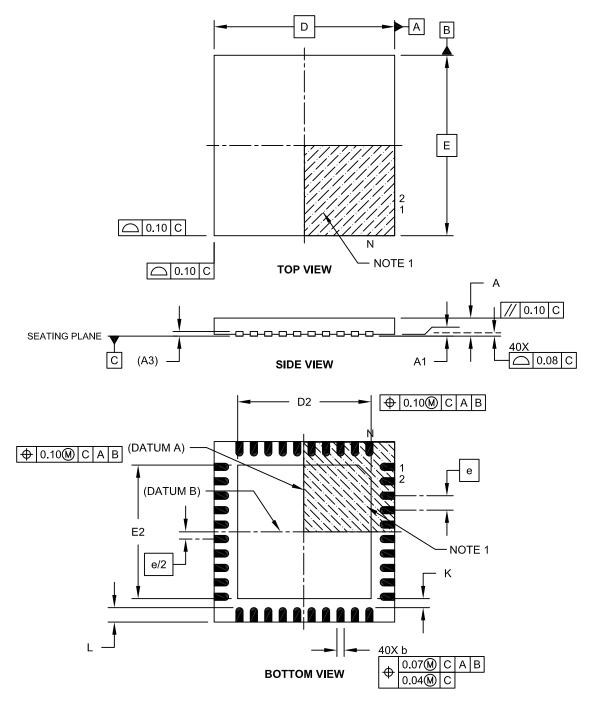

# 40-Lead Ultra Thin Plastic Quad Flat, No Lead Package (MV) – 5x5x0.5 mm Body [UQFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-156A Sheet 1 of 2

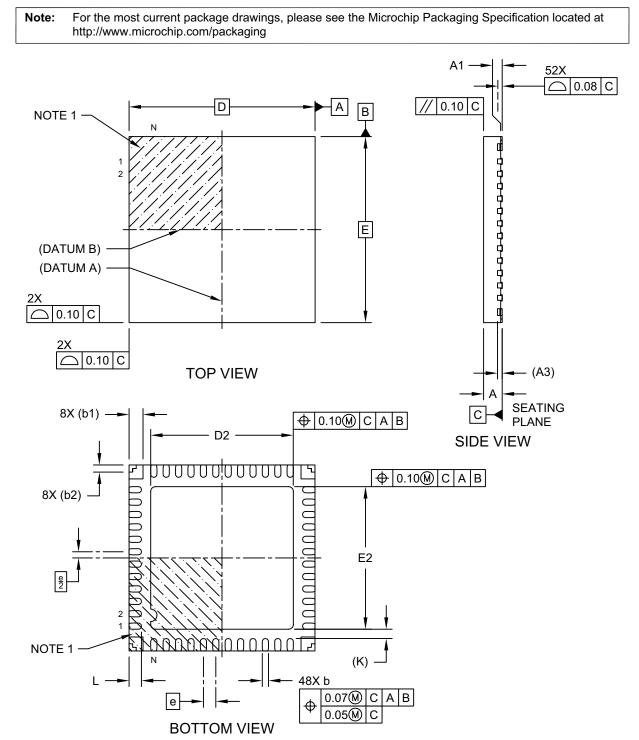

# 48-Lead Ultra Thin Plastic Quad Flat, No Lead Package (M4) - 6x6 mm Body [UQFN] With Corner Anchors and 4.6x4.6 mm Exposed Pad

Microchip Technology Drawing C04-442A-M4 Sheet 1 of 2